Fairchild SSN1N45B service manual

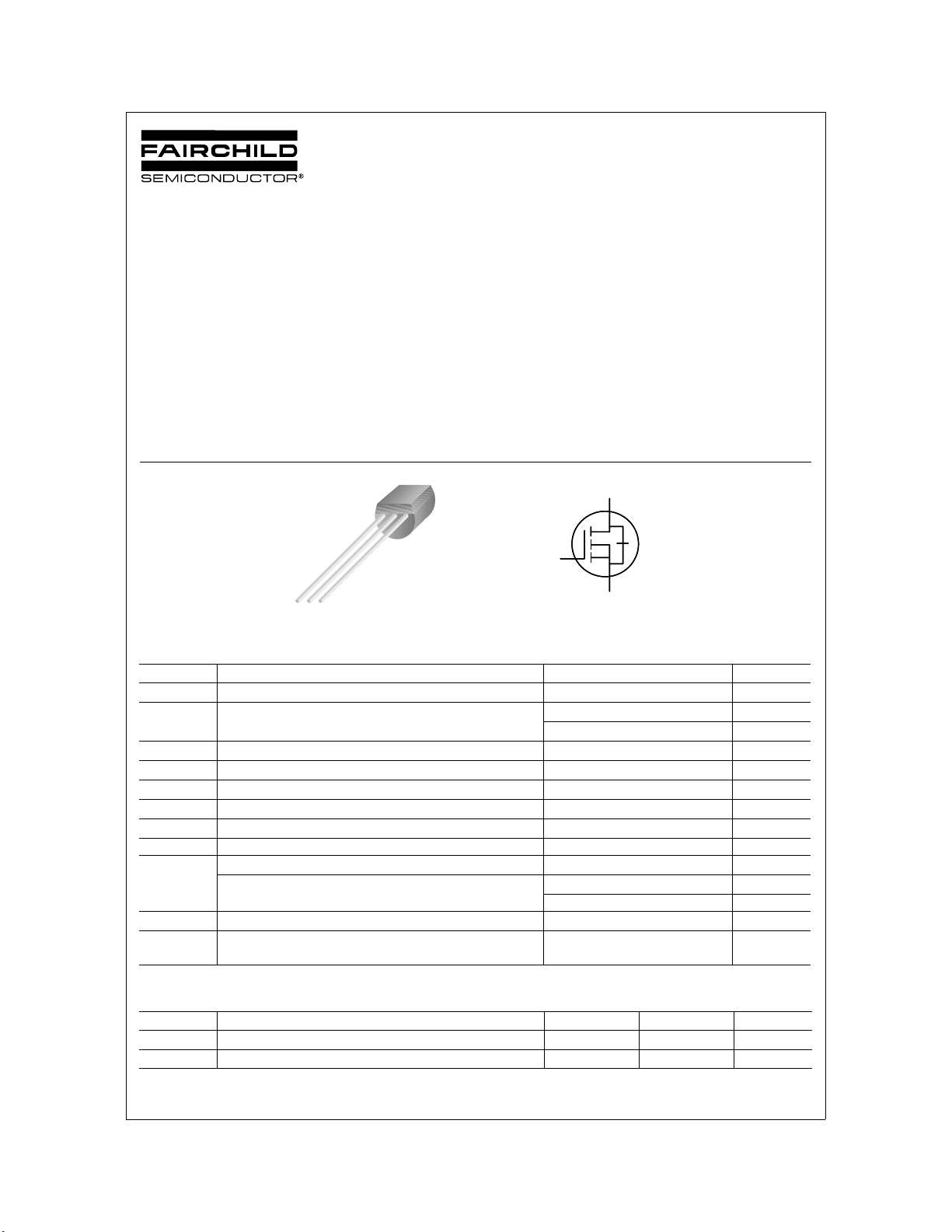

SSN1N45B

450V N-Channel MOSFET

SSN1N45B

General Description

These N-Channel enhancement mode power field effect

transistors are produced using Fairchild’s proprietary,

planar, DMOS technology.

This advanced technology has been especially tailored to

minimize on-state resistance, provide superior switching

performance, and withstand high energy pulse in the

avalanche and commutation mode. These devices are well

Features

• 0.5A, 450V, R

• Low gate charge ( typical 6.5 nC)

• Low Crss ( typical 6.5 pF)

• 100% avalanche tested

• Improved dv/dt capability

• Gate-Source Voltage ± 50V guaranteed

= 4.25Ω @VGS = 10 V

DS(on)

suited for electronic ballasts based on half bridge

configuration.

D

!!!!

!!!!

!!!!

!!!!

####

####

""""

""""

!!!!

!!!!

!!!!

!!!!

!!!!

!!!!

S

SDG

Absolute Maximum Ratings T

TO-92

SSN Series

= 25°C unless otherwise noted

C

!!!!

!!!!

G

Symbol Parameter SSN1N45B Units

V

DSS

I

D

I

DM

V

GSS

E

AS

I

AR

E

AR

dv/dt Peak Diode Recovery dv/dt

P

D

Drain-Source Voltage 450 V

Drain Current

- Continuous (T

- Continuous (T

Drain Current - Pulsed

= 25°C)

C

= 100°C)

C

(Note 1)

0.5 A

0.32 A

4.0 A

Gate-Source Voltage ± 50 V

Single Pulsed Avalanche Energy

Avalanche Current

Repetitive Avalanche Energy

Power Dissipation (TA = 25°C)

Power Dissipation (T

= 25°C)

L

(Note 2)

(Note 1)

(Note 1)

(Note 3)

108 mJ

0.5 A

0.25 mJ

5.5 V/ns

0.9 W

2.5 W

- Derate above 25°C 0.02 W/°C

, T

T

J

stg

T

L

Operating and Storage Temperature Range -55 to +150 °C

Maximum lead temperature for soldering purposes,

1/8" from case for 5 seconds

300 °C

Thermal Characteristics

Symbol Parameter Typ Max Units

R

θJL

R

θJA

©2002 Fairchild Semiconductor Corporation Rev. A, November 2002

Thermal Resistance, Junction-to-Lead

Thermal Resistance, Junction-to-Ambient

(Note 6a)

(Note 6b)

-- 50 °C/W

-- 140 °C/W

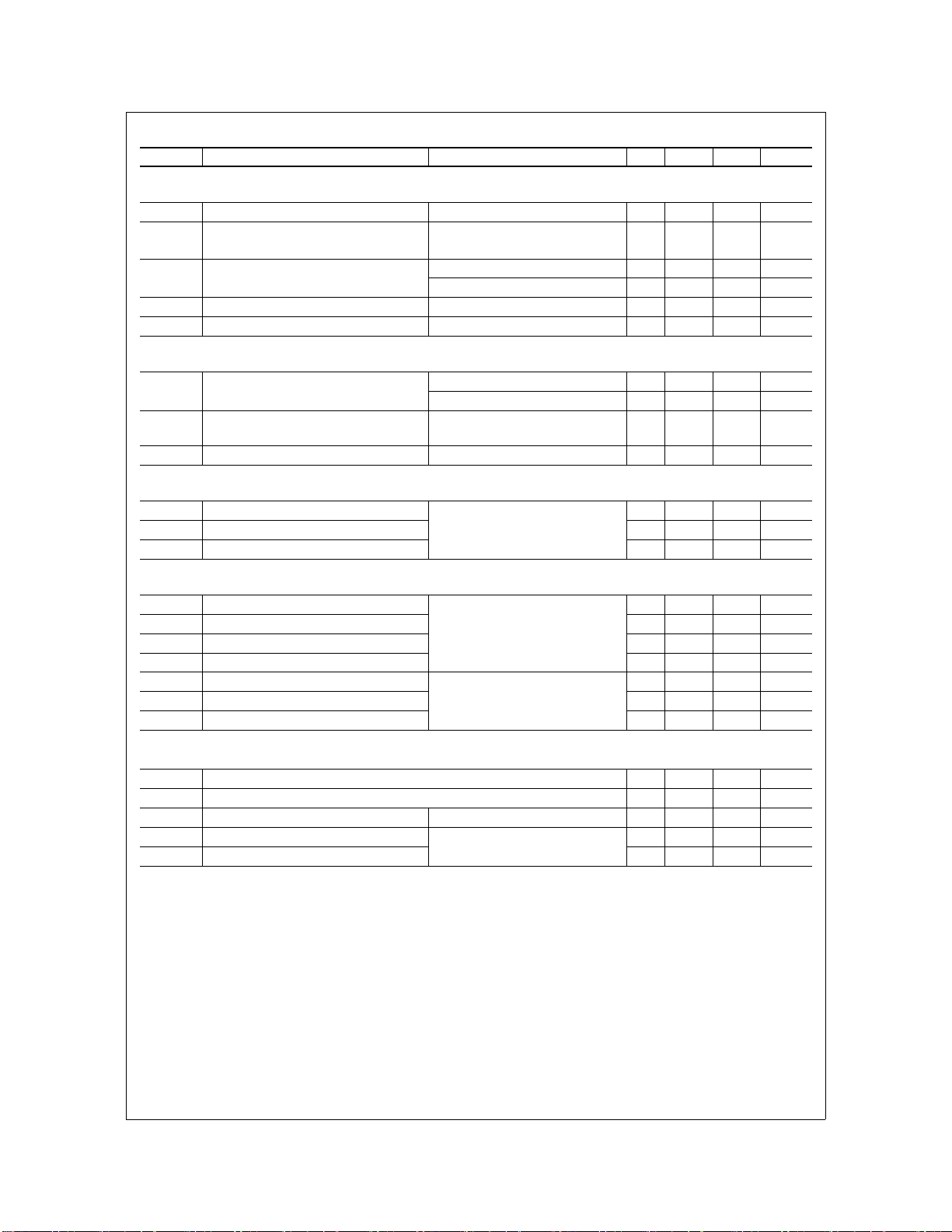

SSN1N45B

Electrical Characteristics T

= 25°C unless otherwise noted

C

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BV

DSS

∆BV

DSS

/ ∆T

I

DSS

I

GSSF

I

GSSR

Drain-Source Breakdown Voltage

Breakdown Voltage Temperature

Coefficient

J

Zero Gate Voltage Drain Current

Gate-Body Leakage Current, Forward

Gate-Body Leakage Current, Reverse

= 0 V, ID = 250 µA

V

GS

I

= 250 µA, Referenced to 25°C

D

V

= 450 V, VGS = 0 V

DS

V

= 360 V, TC = 125°C

DS

V

= 50 V, VDS = 0 V

GS

= -50 V, VDS = 0 V

V

GS

450 -- -- V

-- 0.5 -- V/°C

-- -- 10 µA

-- -- 100 µA

-- -- 100 nA

-- -- -100 nA

On Characteristics

V

R

g

FS

GS(th)

DS(on)

Gate Threshold Voltage

Static Drain-Source

On-Resistance

Forward Transconductance

V

= VGS, ID = 250 µA

DS

V

= VGS, ID = 250 mA

DS

= 10 V, ID = 0.25 A

V

GS

= 50 V, ID = 0.25 A

V

DS

2.3 3.0 3.7 V

3.5 4.2 4.9 V

-- 3.4 4.25 Ω

-- 0.7 -- S

Dynamic Characteristics

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance -- 29 40 pF

Reverse Transfer Capacitance -- 6.5 8.5 pF

= 25 V, VGS = 0 V,

V

DS

f = 1.0 MHz

-- 185 240 pF

Switching Characteristics

t

d(on)

t

r

t

d(off)

t

f

Q

Q

Q

g

gs

gd

Turn-On Delay Time

Turn-On Rise Time -- 21 50 ns

Turn-Off Delay Time -- 23 55 ns

Turn-Off Fall Time -- 36 80 ns

Total Gate Charge

Gate-Source Charge -- 0.9 -- nC

Gate-Drain Charge -- 3.2 -- nC

= 225 V, ID = 0.5 A,

V

DD

= 25 Ω

R

G

(Note 4,5)

V

= 360 V, ID = 0.5 A,

DS

V

GS

(Note 4,5)

= 10 V

-- 7.5 25 ns

-- 6.5 8.5 nC

Drain-Source Diode Characteristics and Maximum Ratings

I

S

I

SM

V

SD

t

rr

Q

rr

Notes:

1. Repetitive Rating : Pulse width limited by maximum junction temperature

2. L = 75mH, IAS = 1.6A, VDD = 50V, RG = 25 Ω, Starting TJ = 25°C

3. ISD ≤ 0.5A, di/dt ≤ 300A/µs, VDD ≤ BV

4. Pulse Test : Pulse width ≤ 300µs, Duty cycle ≤ 2%

5. Essentially independent of operating temperature

6. a) Reference point of the R

b) When mounted on 3”x4.5” FR-4 PCB without any pad copper in a still air environment

(R

©2002 Fairchild Semiconductor Corporation

Maximum Continuous Drain-Source Diode Forward Current -- -- 0.5 A

Maximum Pulsed Drain-Source Diode Forward Current -- -- 4.0 A

V

Drain-Source Diode Forward Voltage

Reverse Recovery Time

Reverse Recovery Charge -- 0.26 -- µC

Starting TJ = 25°C

DSS,

is the drain lead

JL

θ

is the sum of the junction-to-case and case-to-ambient thermal resistance. R

JA

θ

= 0 V, IS = 0.5 A

GS

= 0 V, IS = 0.5 A,

V

GS

dI

/ dt = 100 A/µs

F

CA

θ

-- -- 1.4 V

-- 102 -- ns

(Note 4)

is determined by the user’s board design)

Rev. A, November 2002

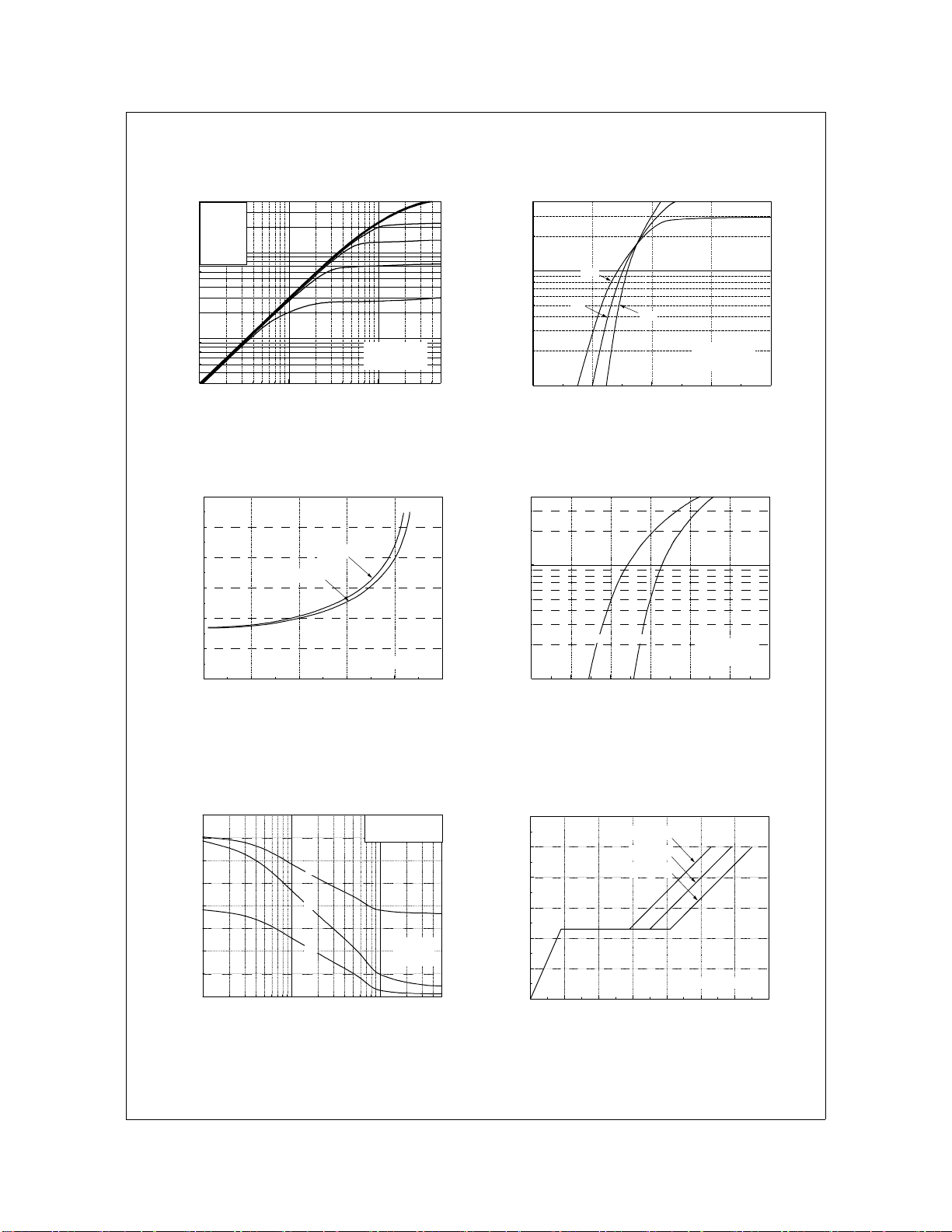

Typical Characteristics

SSN1N45B

V

GS

Top : 1 5 .0 V

10.0 V

8.0 V

6.0 V

5.5 V

0

5.0 V

10

Bottom : 4.5 V

, Dra in C u rr en t [A ]

D

I

-1

10

-1

10

0

10

$

Note s :

1. 250&s Pulse Tes t

%

= 25

2. T

C

1

10

VDS, Drain-Source Voltage [V]

VGS = 20V

VGS = 10V

$

Note : T

%

= 25

J

12

10

8

],

6

'

[

DS(ON)

R

4

2

Drain-Source On-Resistance

0

012345

ID, Drain Current [A]

0

10

, Dra in C u rr en t [A]

D

I

-1

10

246810

%

150

%

25

%

-55

$

Note s :

1. V

= 50V

DS

2. 250&s Pulse Test

VGS , Ga te -S o u rc e V o ltag e [V ]

Figure 2. Transfer CharacteristicsFigure 1. On-Region Char act er i stic s

0

10

%

, Reverse Drain Current [A]

DR

I

-1

10

0.2 0.4 0.6 0.8 1.0 1.2 1.4

150

%

25

$

Note s :

= 0V

1. V

GS

2. 25 0&s Pulse Test

VSD, Sou rc e -D r ain v olta g e [V ]

Figure 3. On-Resistance Variati on vs.

Drain Current and Gate Voltage

400

300

200

Capacitance [pF]

100

0

-1

10

Figure 5. Capacitance Characteristics Figure 6. Gate Charge Ch a ra ct eristics

©2002 Fairchild Semiconductor Corporation

C

iss

C

oss

C

rss

0

10

VDS, Drain-Source Voltage [V]

C

= Cgs + Cgd (Cds = shorted)

iss

= Cds + C

C

oss

gd

C

= C

rss

gd

$

Note ;

1. V

2. f = 1 MHz

1

10

Figure 4. Body Diode Forward Voltage

Variation with Source Current

and Temperature

VDS = 90V

VDS = 225V

VDS = 360V

$

Note : I

= 0.5 A

D

Rev. A, November 2002

12

10

8

= 0 V

GS

6

4

, Gate-Source Voltage [V]

GS

2

V

0

01234567

QG, Tota l G a te Charge [nC]

Loading...

Loading...