Fairchild SG6742 service manual

www.fairchildsemi.com

AN-6077

SG6742 — Highly Integrated Green-Mode PWM Controller

Abstract

This application note describes a detailed design strategy for

a high-efficiency, compact flyback converter. Design

considerations, mathematical equations, and guidelines for a

Printed-Circuit-Board (PCB) layout are presented.

Features

High-Voltage Startup

Low Operating Current: 2.7mA

Linearly Decreasing PWM Frequency to 22KHz

Frequency Hopping to Reduce EMI Emission

Fixed PWM Frequency:

ML and MR are 65KHz.

HL and HR are 100KHz.

Peak-Current-Mode Control

Cycle-by-Cycle Current Limiting

Leading-Edge Blanking (LEB)

Synchronized Slope Compensation

Internal Open-Loop Protection

Gate Output Maximum Voltage Clamp: 18V

V

V

Under-Voltage Lockout (UVLO)

DD

Over-Voltage Protection (OVP)

DD

Programmable Over-Temperature Protection (OTP)

Internal Latch Circuit (OVP, OTP)

Internal Sense Short-Circuit Protection

Built-In Soft-Start Function

ML and MR are 5ms.

HL and HR are 6ms.

Constant Power Limit (Full AC Input Range)

Internal OTP Sensor with Hysteresis

Applications

General-purpose, switch-mode power supplies and flyback

power converters, including:

Power Adapters

Open-Frame Switch-Mode Power Supply (SMPS)

Introduction

The highly integrated SG6742 series of PWM controllers

provides several features to enhance the performance of

flyback converters.

To minimize standby power consumption, a proprietary

green-mode function provides off-time modulation to

linearly decrease the switching frequency at light-load

conditions. To avoid acoustic-noise problems, the minimum

PWM frequency is set above 22KHz. This green-mode

function enables the power supply to meet international

power conservation requirements. With the internal highvoltage startup circuitry, the power loss due to bleeding

resistors is also eliminated. To further reduce power

consumption, SG6742 is manufactured using the BiCMOS

process, which allows an operating current of only 2.7mA.

Built-in synchronized slope compensation achieves stable

peak-current-mode control. The proprietary external line

compensation ensures a constant output-power limit over a

wide AC input voltage range, from 90V

SG6742 provides many protection functions. In addition to

cycle-by-cycle current limiting, the internal open-loop

protection circuit ensures safety should an open-loop or

output short-circuit failure occur.

SG6742ML Latch Latch Latch Auto Restart 65KHz

SG6742MR Latch Auto Restart Latch Auto Restart 65KHz

SG6742HL Latch Latch Latch Auto Restart 100KHz

SG6742HR Latch Auto Restart Latch Auto Restart 100KHz

OVP

(VDD)

GND

FB

NC

HV

Figure 1. Pin Configuration (Top View)

OLP (FB)

18

2

3

OTP

(RT)

SOP-8

7

6

54

to 264VAC.

AC

SCP

(SENSE)

GATE

VDD

SENSE

RT

Frequency

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.2 • 12/1/08 1

AN-6077 APPLICATION NOTE

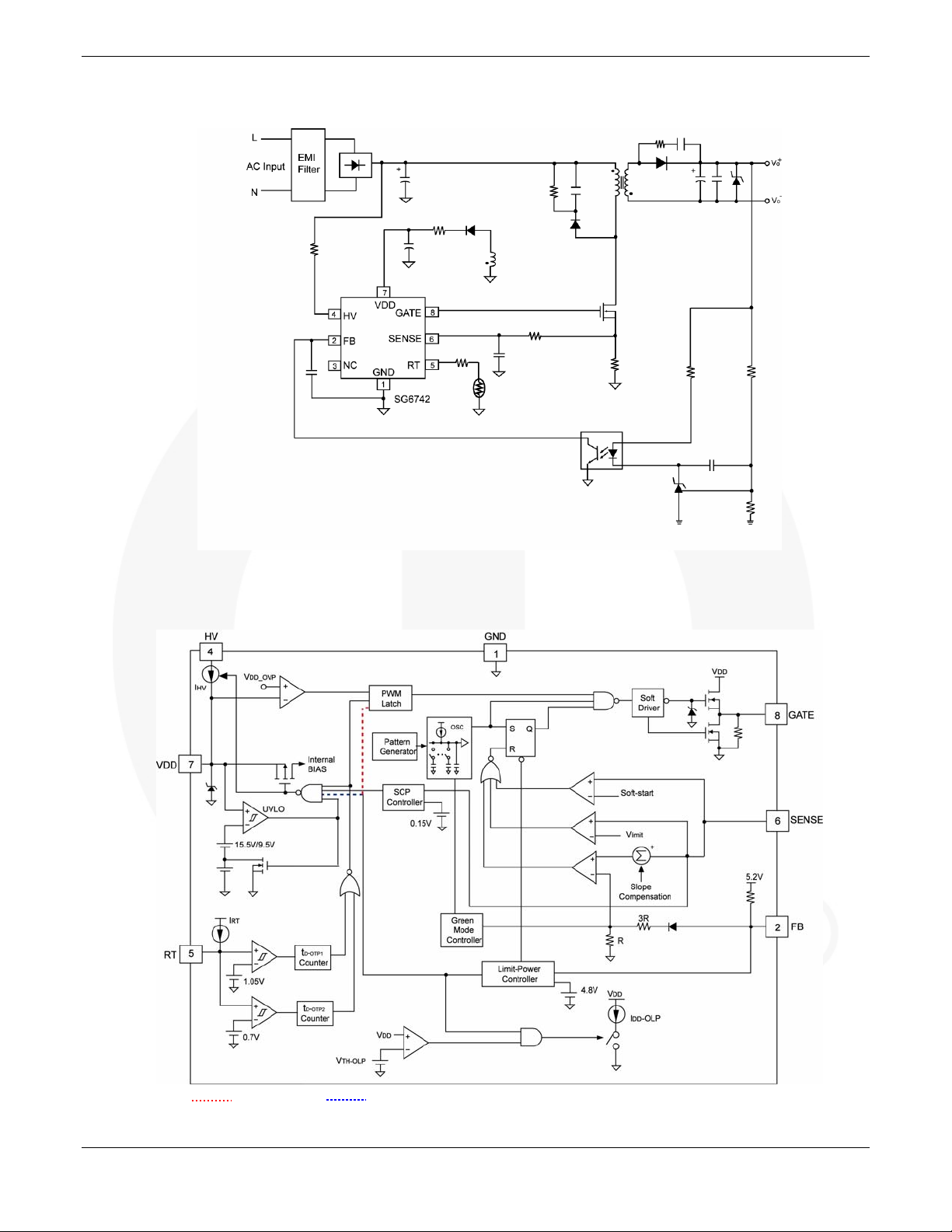

Typical Application

Block Diagram

Figure 2. Typical Application

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.2 • 12/1/08 2

SG6742ML/HL

SG6742MR/HR

Figure 3. Functional Block Diagram

AN-6077 APPLICATION NOTE

Internal Block Operation

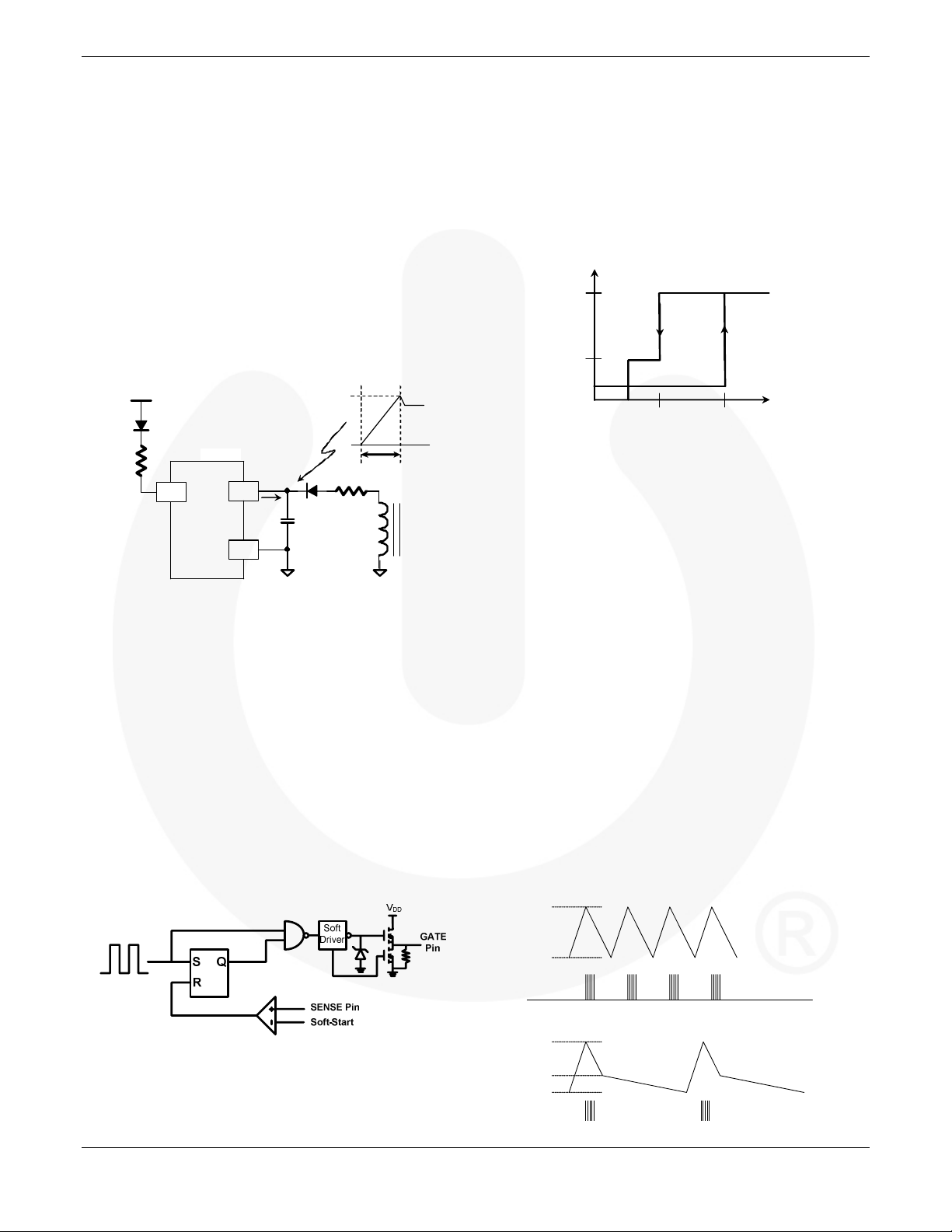

Startup Circuitry

When the power is turned on, the internal current source

(typically 2mA) charges the hold-up capacitor C

startup resistor R

. During the startup sequence, the V

HV

through a

1

BULK

provides a startup current of about 2.3mA and charges the

V

capacitor C1. RHV and D2 are series connections and

DD

can be directly connected by V

VDD pin reaches the start threshold voltage V

to the HV pin. As the

AC

DD-ON

, the

SG6742 activates and signals the MOSFET. The highvoltage source current is switched off and the supply current

is drawn from the auxiliary winding of the main transformer,

as shown in Figure 4.

R

D2

HV

VAC

HV

SG6742

VDD

GND

I

HV

C1

D1

V

DD- ON

t

D_O N

Figure 4. Startup Circuit for Power Transfer

When the supply current is drawn from the transformer, it

draws a leakage current of about 1µA from the HV pin. The

maximum power dissipation of the R

2

RIP ×=

HV

R

HV

where I

R

HV

HV-LC

.)Typ(LCHV

−

is the supply current drawn from HV pin.

2

WKAP

μμ

1.01001

≅Ω×=

Soft-Start

For many applications, it is necessary to minimize the inrush

current during the startup period. The built-in 5ms/6ms soft-

start circuit significantly reduces the startup current spike

and output-voltage overshoot.

HV

is:

(1)

(2)

Under-Voltage Lockout (UVLO)

The SG6742 has a voltage detector on the VDD pin to

ensure that the chip has enough power to drive the

MOSFET. Figure 6 shows a hysteresis of the turn-on and

turn-off threshold levels and an open-loop-release voltage.

I

DD

2.7mA

70µA

10µA

V

9.5V

15.5V 7.5V

Figure 6. UVLO Specification

The turn-on and turn-off thresholds are internally fixed at

15.5V and 9.5V. During startup, the V

DD

charged to 15.5V to enable the IC. The capacitor continues

to supply the V

until the energy can be delivered from the

DD

auxiliary winding of the main transformer. The V

drop below 9.5V during startup.

If the secondary output short circuits or the feedback loop is

open, the FB pin voltage rises rapidly toward the open-loop

voltage, V

and lasts for t

and enters latched-up mode until V

. If the FB voltage remains above V

FB-OPEN

, the SG6742 stops emitting output pulses

D-OLP

drops below 5V. To

DD

further limit the input power under a short-circuit or openloop condition, a special two-step UVLO mechanism

prolongs the discharge time of the V

DD

shows the traditional UVLO method, along with the special

two-step UVLO method. In the two-step UVLO mechanism,

an internal sinking current, I

toward the V

V

drops below V

DD

again charged towards V

. This sinking current is disabled after the

DD-OLP

; after which, the VDD voltage is

DD-OLP

DD-ON

, pulls the VDD voltage

DD-OLP

. With the two-step UVLO

mechanism, the average input power during a short-circuit

or open-loop condition is greatly reduced. As a result, over-

heating does not occur.

15.5V

V

DD

9.5V

Gate

DD

capacitor must be

must not

DD

capacitor. Figure 7

General UVLO

FB-OLP

Figure 5. Soft-Start Circuit

15.5V

9.5V

7.5V

V

DD

Gate

Two-Step UVLO

Figure 7. UVLO Effect

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.2 • 12/1/08 3

Loading...

Loading...