SG6741

Highly Integrated Green-Mode PWM Controller

SG6741 — Highly Integrated Green-Mode PWM Controller

June 2011

Features

High-Voltage Startup

Low Operating Current: 4mA

Linearly Decreasing PWM Frequency to 22kHz

Frequency Hopping to Reduce EMI Emission

Peak-Current-Mode Control

Cycle-by-Cycle Current Limiting

Leading-Edge Blanking

Synchronized Slope Compensation

Gate Output Maximum Voltage Clamp: 18V

VDD Over-Voltage Protection (Auto Restart)

VDD Under-Voltage Lockout (UVLO)

Internal Open-Loop Protection

Constant Power Limit (Full AC Input Range)

Applications

General-purpose switch-mode power supplies and

flyback power converters, including:

Power Adapters

Open-Frame SMPS

Description

The highly integrated SG6741 PWM controller provides

several features to enhance the performance of flyback

converters.

The highly integrated SG6741 series of PWM

controllers provides several features to enhance the

performance of flyback converters.

To minimize standby power consumption, a proprietary

green-mode function provides off-time modulation to

linearly decrease the switching frequency at light-load

conditions. To avoid acoustic-noise problems, the

minimum PWM frequency is set above 22KHz. This

green-mode function enables the power supply to meet

international power conservation requirements. W ith the

internal high-voltage startup circuitry, the power loss

due to bleeding resistors is also eliminated. To further

reduce power consumption, SG6741 is manufactured

using the BiCMOS process, which allows an operating

current of only 4mA.

SG6741 integrates a frequency-hopping function that

helps reduce EMI emission of a power supply with

minimum line filters. Its built-in synchronized slope

compensation achieves stable peak-current-mode

control. The proprietary internal line compensation

ensures constant output power limit over a wide range

of AC input voltages, from 90V

SG6741 provides many protection functions. In addition

to cycle-by-cycle current limiting, the internal open-loop

protection circuit ensures safety when an open-loop or

output short-circuit failure occurs. PWM output is

disabled until V

then the controller starts again. As long as V

about 26V, the internal OVP circuit is triggered.

SG6741 is available in an 8-pin SOP package.

drops below the UVLO lower limit;

DD

to 264VAC.

AC

exceeds

DD

Ordering Information

Operating

Part Number

SG6741SZ -40 to +105°C 8-Lead Small Outline Package (SOP) Tape & Reel

SG6741SY -40 to +105°C 8-Lead Small Outline Package (SOP) Tape & Reel

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

SG6741 • Rev. 1.3.4 1

Temperature

Range

Package Packing Method

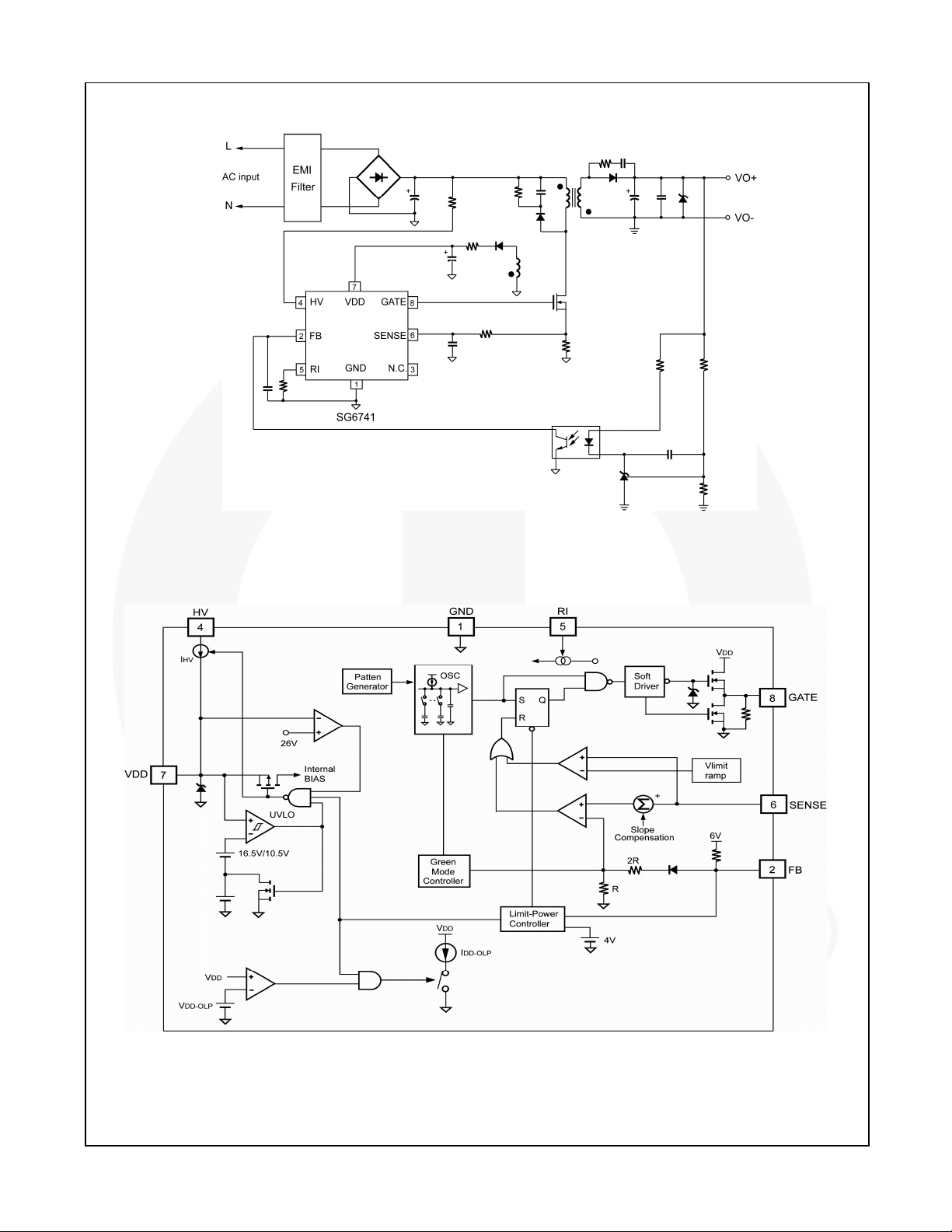

Application Diagram

SG6741 — Highly Integrated Green-Mode PWM Controller

Figure 1. Typical Application

Internal Block Diagram

Figure 2. Functional Block Diagram

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

SG6741 • Rev. 1.3.4 2

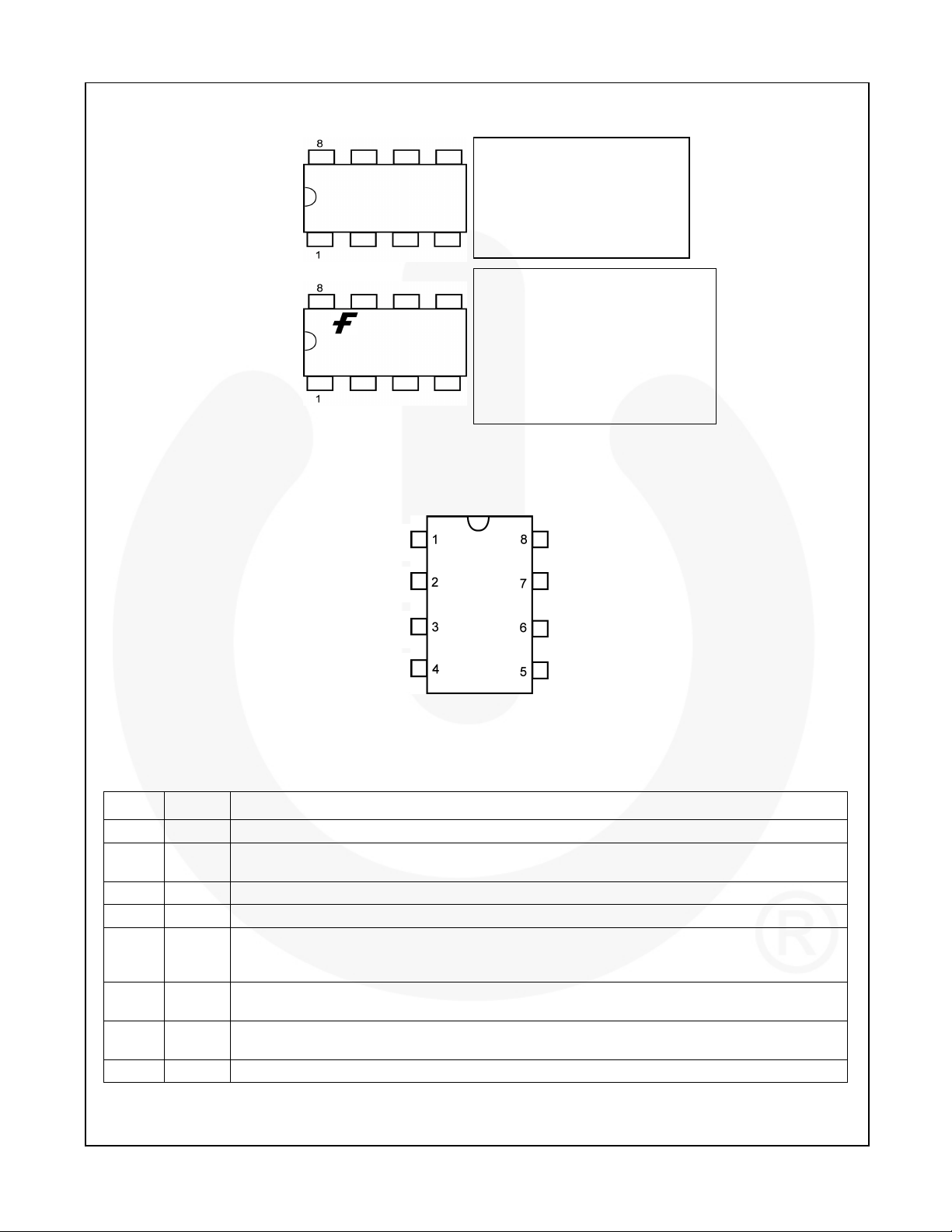

Marking Information

SG6741TP

XXXXXXXXYWWV

SG6741 — Highly Integrated Green-Mode PWM Controller

T: S = SOP

P: Z =Lead Free

Null=regular package

XXXXXXXX: Wafer Lot

Y: Year; WW: Week

V: Assembly Location

Marking for SG6741SZ

Marking for SG6741SY

Pin Configuration

ZXYTT

6741

TPM

GND

FB

NC

HV

F: Fairchild logo

Z: Plant code

X: 1 digit year code

Y: 1 digit week code

TT: 2 digits die run code

T: Package type (S = SOP)

P: Y=Green package

M: Manufacture flow code

Figure 3. Top Mark

GATE

VDD

SENSE

RI

Figure 4. Pin Configuration (Top View)

Pin Definitions

Pin # Name Description

1 GND Ground.

2 FB

3 NC No connection.

4 HV For startup, this pin is pulled high to the line input or bulk capacitor via resistors.

5 RI

6 SENSE

7 VDD

8 GATE The totem-pole output driver. Soft driving waveform is implemented for improved EMI.

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

SG6741 • Rev. 1.3.4 3

The signal from the external compensation circuit is fed into this pin. The PWM duty cycle is

determined in response to the signal on this pin and the current-sense signal on the SENSE pin.

A resistor connected from the RI pin to GND pin provides the SG6741 with a constant current

source. This determines the center PWM frequency. Increasing the resistance reduces PWM

frequency. Using a 26KΩ resistor (R

Current sense. The sensed voltage is used for peak-current-mode control and cycle-by-cycle

current limiting.

Power supply. The internal protection circuit disables PW M output as long as VDD exceeds the

OVP trigger point.

) results in a 65kHz center PWM frequency.

I

Loading...

Loading...