Fairchild RFD16N05, RFD16N05SM service manual

RFD16N05, RFD16N05SM

Data Sheet November 2003

16A, 50V, 0.047 Ohm, N-Channel Power

MOSFETs

The RFD16N05 and RFD16N05SM N-channel power

MOSFETs are manufactured using the MegaFET process.

This process, w hic h uses feature sizes approaching those o f

LSI integrated circuits, gives optimum utilization of silicon,

resulting in outstanding performance. They were designed

for use in applications such as switching regulators,

switching c on v erters, moto r driv ers , and relay drivers . Thes e

transistors can be operated directly from integrated circuits.

Formerly developmental type TA09771.

Ordering Information

PART NUMBER PACKAGE BRAND

RFD16N05 TO-251AA D16N05

RFD16N05SM TO-252AA D16N05

NOTE: When ordering, use the entire p art number. Add the suffix 9A to

obtain the TO -252AA variant in t he tape and reel , i.e., RF D16N05SM9A.

Packaging

Features

• 16A, 50V

•r

• Temperature Compensating PSPICE

DS(ON)

= 0.047Ω

®

Model

• Peak Current vs Pulse Width Curve

• UIS Rating Curve

o

•175

C Operating Temperature

• Related Literature

- TB334 “Guidelines for Soldering Surface Mount

Components to PC Boards”

Symbol

D

G

S

JEDEC TO-251AA JEDEC TO-252AA

DRAIN (FLANGE)

SOURCE

DRAIN

GATE

DRAIN (FLANGE)

GATE

SOURCE

©2003 Fairchild Semiconductor Corporation RFD16N05, RFD16N05SM Rev. B1

RFD16N05, RFD16N05SM

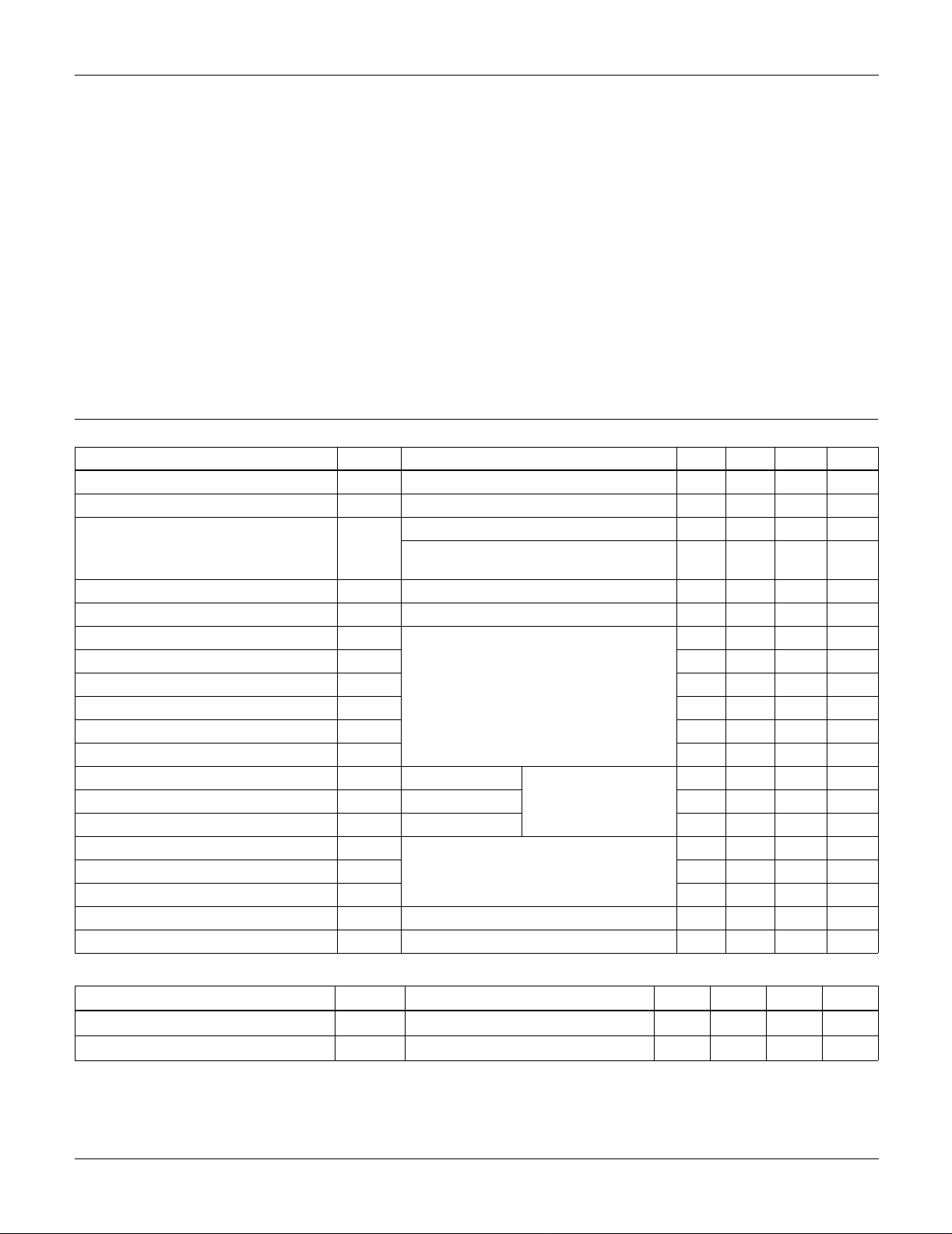

Absolute Maximum Ratings T

= 25oC, Unless Otherwise Specified

C

RFD16N05, RFD16N05SM, UNITS

Drain to Source Voltage (Note 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

Drain to Gate Voltage (Note 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

Continuous Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

Pulsed Drai n C u rr e n t (Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .V

Pulsed Avalanche Rating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .E

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . P

Derate above 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .T

DSS

DGR

DM

GS

AS

J, TSTG

D

Refer to Peak Current Curve

D

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

Package Body for 10s, See Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

CAUTION: Stresses above those listed in “A bsolute Maximu m Rating s” may cause per manent d amage to t he device. This is a str ess on ly rating and operation o f the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

L

pkg

50 V

50 V

16

±20 V

Refer to Figure 5

72

0.48

-55 to 175

300

260

A

W

W/oC

o

C

o

C

o

C

NOTE:

= 25oC to 150oC.

1. T

J

Electrical Specifications T

= 25oC, Unless Otherwise Specified

C

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Drain to Source Breakdown Voltage BV

Gate Threshold Voltage V

GS(TH)VGS

Zero Gate Voltage Drain Current I

Gate to Source Leakage Current I

Drain to Source On Resistance (Note 2) r

DS(ON)ID

Turn-On Time t

Turn-On Delay Time t

d(ON)

Rise Time t

Turn-Off Delay Time t

d(OFF)

Fall Time t

Turn-Off Time t

Total Gate Charge Q

(OFF)

g(TOT)VGS

Gate Charge at 10V Q

Threshold Gate Charge Q

Input Capacitance C

Output Capacitance C

Reverse Transfer Capacitance C

Thermal Resistance Junction to Case R

Thermal Resistance Junction to Ambient R

DSSID

DSS

GSSVGS

(ON)VDD

r

f

g(10)VGS

(TH)VGS

ISS

OSS

RSS

θJC

θJA

= 250µA, VGS = 0V (Figure 11) 50 - - V

= VDS, ID = 250µA2-4V

VDS = Rated BV

V

= 0.8 x Rated BV

DS

T

= 150oC

C

, VGS = 0V - - 1 µA

DSS

, VGS = 0V,

DSS

--25µA

= ±20V - - ±100 nA

= 16A, VGS = 10V (Figure 9) - - 0.047 Ω

= 25V, ID = 8A, RL = 3.125Ω,

= 10V, RGS = 25Ω

V

GS

(Figure 13)

- - 65 ns

-14- ns

-30- ns

-55- ns

-30- ns

- - 125 ns

= 0V to 20V VDD = 40V, ID ≈ 16A,

= 2.5Ω

R

= 0V to 10V - - 45 nC

= 0V to 2V - - 2.2 nC

L

= 0.8mA

I

g(REF)

(Figure 13)

VDS = 25V, VGS = 0V, f = 1MHz

(Figure 12)

- - 80 nC

- 900 - pF

- 325 - pF

- 100 - pF

- - 2.083oC/W

TO-251 and TO-252 - - 100

o

C/W

Source to Drain Diode Specifications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Source to Drain Diode Voltage V

Diode Reverse Recovery Time t

NOTES:

2. Pulse test: pulse width ≤ 250µs, duty cycle ≤ 2%.

3. Repetitive rating: pulse width limited by maximum junction temperature. See Transient Thermal Impedance curve (Figure 3) and Peak Current

Capability Curve (Figure 5).

©2003 Fairchild Semiconductor Corporation RFD16N05, RFD16N05SM Rev. B1

ISD = 16A - - 1.5 V

SD

ISD = 16A, dISD/dt = 100A/µs - - 125 ns

rr

RFD16N05, RFD16N05SM

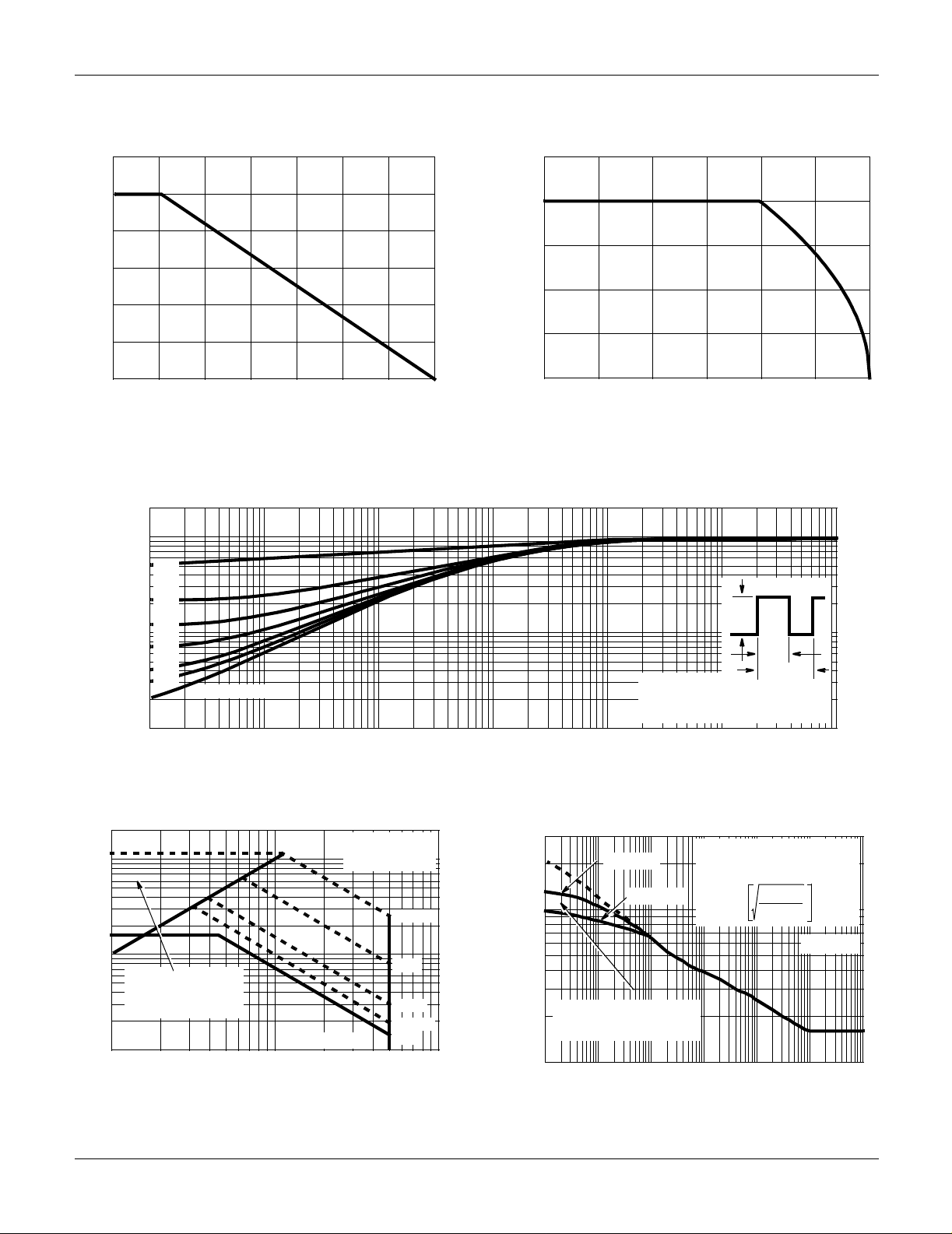

Typical Performance Curves Unless Otherwise Specified

1.2

1.0

0.8

0.6

0.4

0.2

POWER DISSIPATION MULTIPLIER

0

0 25 50 75 100 175

125

150

TC, CASE TEMPERATURE (oC)

FIGURE 1. NORMALIZED PO WER DISSIP ATION vs CASE

TENPERATURE

2

1

0.5

0.2

0.1

0.1

, NORMALIZED

0.05

JC

θ

Z

0.02

THERMAL IMPEDANCE

0.01

SINGLE PULSE

0.01

-5

10

-4

10

-3

10

t, RECTANGULAR PULSE DURATION (s)

20

16

12

8

, DRAIN CURRENT (A)

D

I

4

0

25 50 75 100

125

TC, CASE TEMPERATURE (oC)

FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

CASE TEMPERATURE

P

DM

t

1

NOTES:

DUTY FA CTOR: D = t

PEAK TJ = PDM x Z

-2

10

-1

10

1/t2

x R

JA

θ

0

10

150

t

2

+ T

JA

θ

175

A

1

10

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

100

10

OPERATION IN THIS

AREA MAY BE

, DRAIN CURRENT (A)

D

I

LIMITED BY r

1

1

SINGLE PULSE

T

= MAX RATED

J

DS(ON)

V

DSS(MAX)

= 50V

10

VDS, DRAIN TO SOURCE VOLTAGE (V)

TC = 25oC

100µs

1ms

10ms

100ms

DC

100

200

100

, PEAK CURRENT (A)

DM

TRANSCONDUCTANCE

I

MAY LIMIT CURRENT

IN THIS REGION

10

-5

10

VGS = 20V

-4

10

VGS = 10V

10

t, PULSE WIDTH (s)

FOR TEMPERAT URES

ABOVE 25

CURRENT AS FOLLOWS:

I = I

-3

-2

10

o

C DERATE PEAK

175 - T

25

150

-1

10

C

TC = 25oC

0

10

10

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA FIGURE 5. PEAK CURRENT CAPABILITY

©2003 Fairchild Semiconductor Corporation RFD16N05, RFD16N05SM Rev. B1

1

Loading...

Loading...