Fairchild ILC5062 service manual

查询ILC5062AIC23X供应商

www.fairchildsemi.com

ILC5062

SOT-23 Power Supply reset Monitor with 1% precision

Features

• All-CMOS design in SOT-23 or SC70 package

• A grade ±1% precision in Reset Detection

• Standard grade : ±2% precision in Reset Detection

• Only 1µA of Iq

• Over 2mA of sink current capability

• Built-in hysteresis of 5% of detection voltage

• Voltage options of 2.6, 2.7, 2.8, 2.9, 3.1, 4.4, and 4.6V fit

most supervisory applications

• Active low push-pull output

Applications

• Microprocessor reset circuits

• Memory battery back-up circuitry

• Power-on reset circuits

• Portable and battery powered electronics

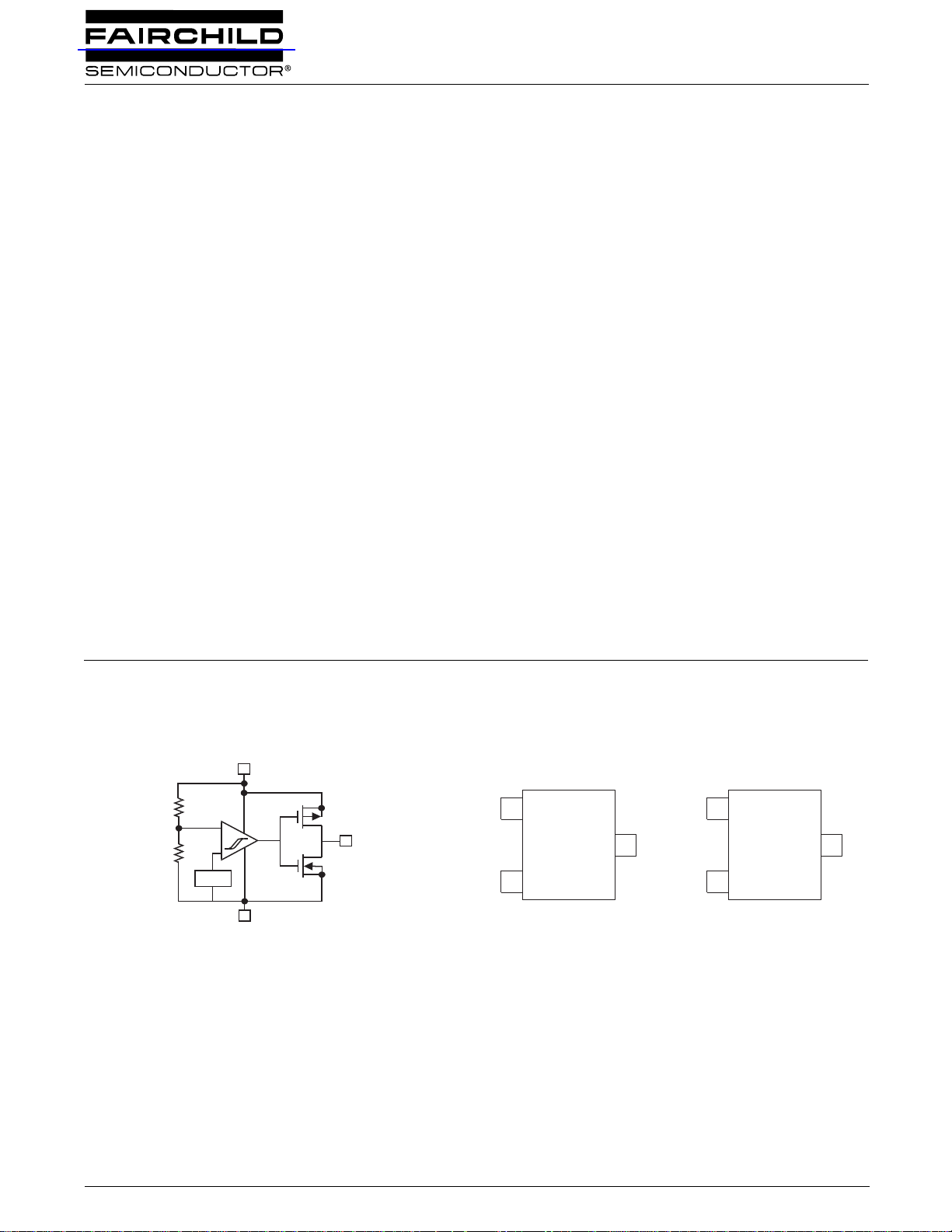

Block Diagram

Description

All-CMOS voltage monitoring circuit in either a 3-lead

SOT-23 or SC70 package offers the best performance in

power consumption and accuracy.

The ILC5062 is available in a series of ±1% (A-grade) or 2%

(standard grade) accurate trip voltages to fit most microprocessor applications. Even though its output can sink over

2mA, the device draws only 1µA in normal operation.

Additionally, a built-in hysteresis of 5% of detect voltage

simplifies system design.

Pin-Package Configurations

V

IN

V

REF

V

SS

Complementary CMOS Output

Top View

1

V

V

OUT

OUT

V

3

V

SC-70

2

SS

IN

1

V

OUT

3

V

SOT-23

2

V

SS

IN

Rev. 2.2 8/14/02

PRODUCT SPECIFICATION ILC5062

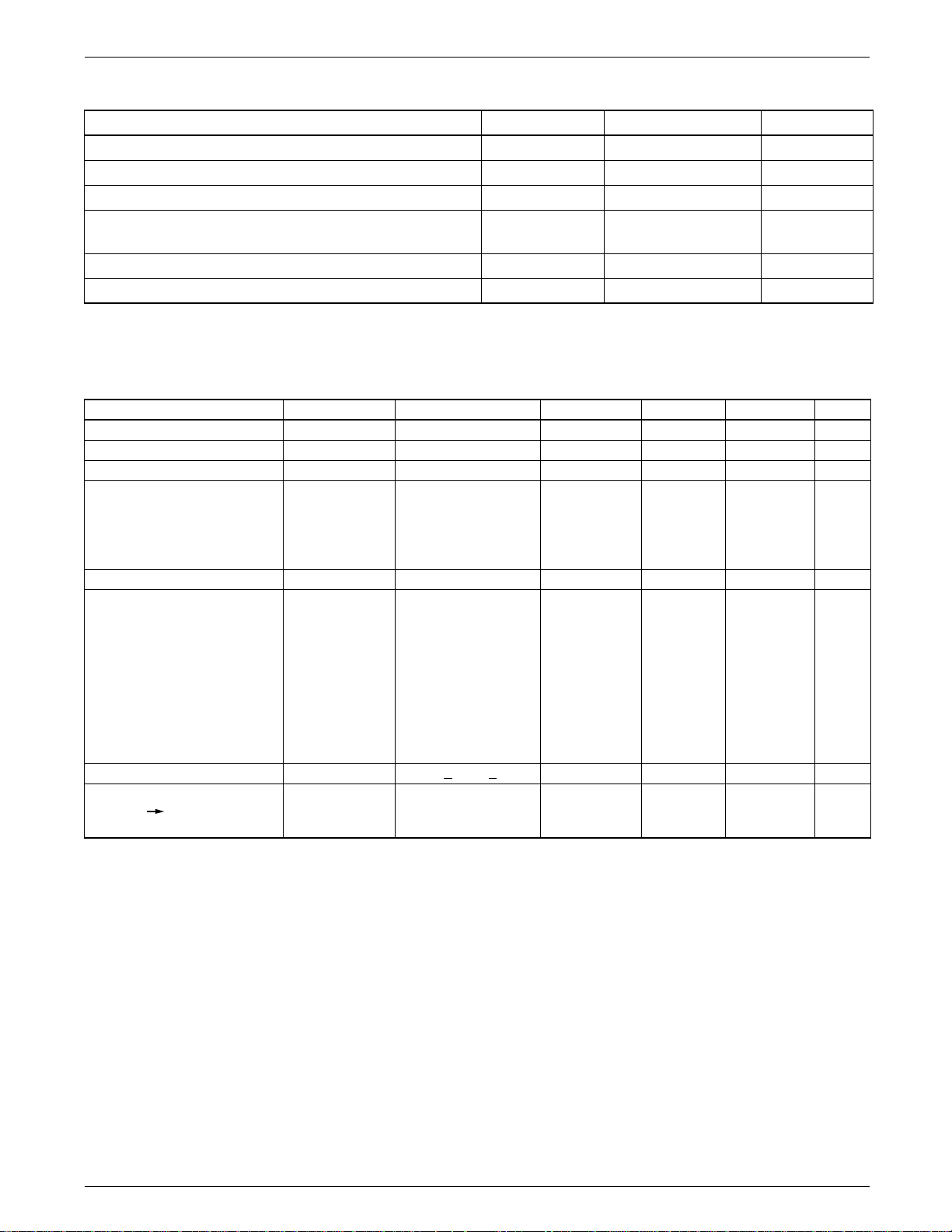

Absolute Maximum Ratings

Parameter Symbol Ratings Units

Input Voltage V

Output Current I

Output Voltage V

Continuous Total

Power Dissipation (SOT-23)

Operating Ambient Temperature T

Storage Temperature T

IN

OUT

OUT

P

D

opr

stg

VSS-0.3~VIN=+0.3 V

12 V

50 mA

150 mW

-30~+80 °C

-40~+125 °C

Electrical Characterisitcs ILC5062

Parameter Symbol Conditions Min. Typ. Max. Units

Detect Fail Voltage V

Detect Fail Voltage V

Hysteresis Range V

DF

DF

HYS

Supply Current

I

SS

Operating Voltage V

IN

Output Current

I

OUT

Temperature Characteristics ∆V

Delay Time (Release

Voltage Output Inversion)

/(∆T

DF

t

DLY

(VDR to V

opr•VDF

OUT

Inversion)

Note1: An additional resistor between the V

increasing of V

Note2: Vout=Gnd when 1V< V

Note3: Iout < 10uA when V

DR

.

<1.5V

IN

<1V

IN

A grade VDF X 0.99 V

Standard grade VDF X 0.98 V

VIN = 1.5V

= 2.0V

V

IN

V

= 3.0V

IN

= 4.0V

V

IN

= 5.0V

V

IN

VDF = 2.1 ~ 6.0V 1.5 10.0 V

N-ch VDS = 0.5V

= 1.0V

V

IN

= 2.0V

V

IN

V

= 3.0V

IN

= 4.0V

V

IN

V

IN

P-Ch VDS = 2.1V

= 8V

V

IN

) -30°C < Topr < 80°C -200 ±100 +200 ppm/°C

pin and supply voltage may cause deterioration of the characteristics due to

IN

(TA=25°C)

= 5.0V

DF

DF

VDF X 1.01 V

VDF X 1.02 V

VDF X 0.02 VDF X 0.05 VDF X 0.08 V

0.9

1.0

1.3

1.6

2.0

2.6

3.0

3.4

3.8

4.2

µA

2.2

7.7

10.1

11.5

mA

13.0

-10

0.1 ms

Rev. 2.2 8/14/02 2

PRODUCT SPECIFICATION ILC5062

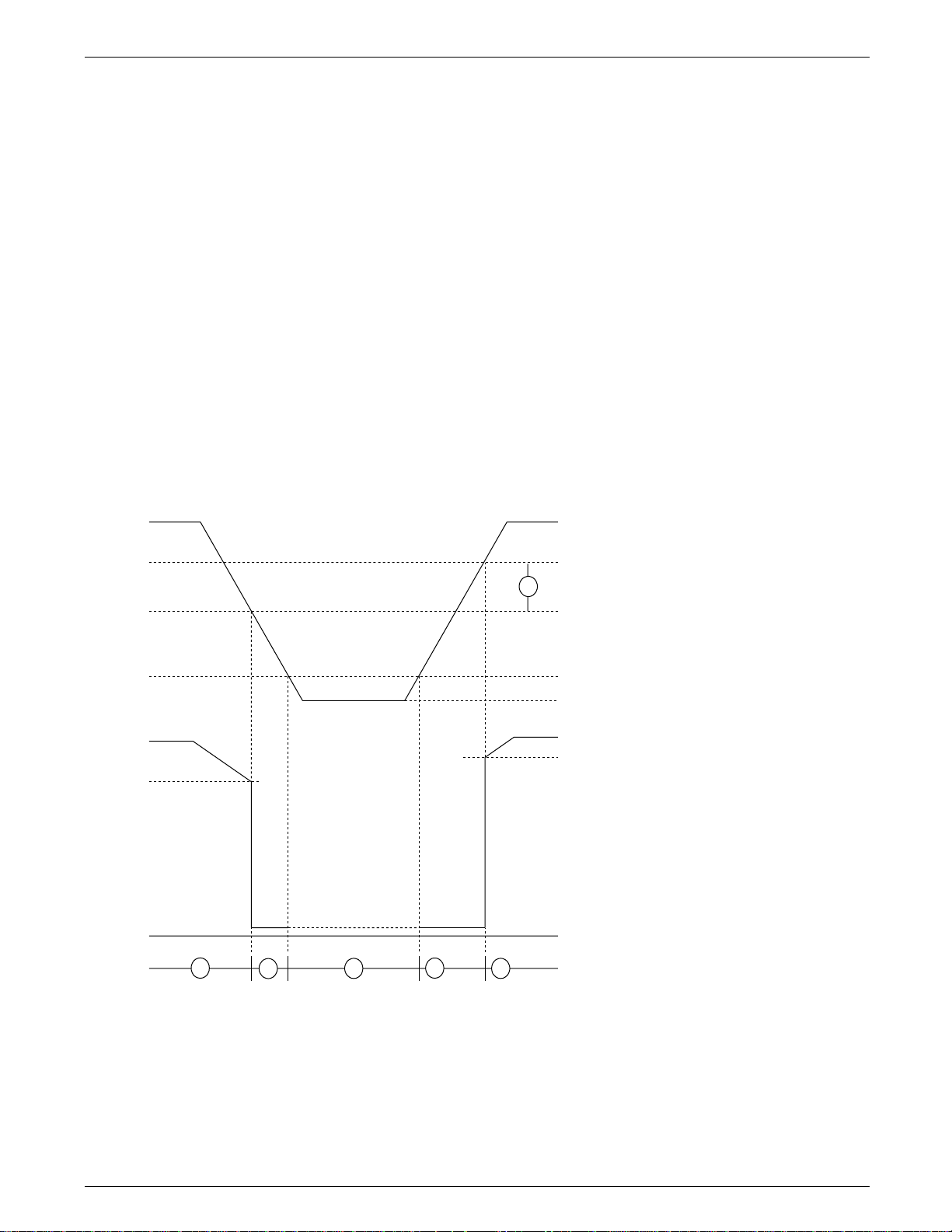

Functional Description

The following designators 1~6 refer to the timing diagram below.

1. While the input voltage (V

age at V

2. When the input V

IN

pin.

voltage falls lower than VDF, V

IN

3. If the input voltage decreases below the minimum operating voltage (V

4. During an increase of the input voltage from the V

V

level, the ouput stays at the ground level (VSS) between the minimum operating voltage (V

MIN

voltage (V

DR

).

5. If the input voltage increases more than V

6. The difference between V

) is higher than the detect voltage (VDF), the output voltage at V

IN

drops near ground voltage.

OUT

), the V

MIN

voltage, V

SS

, the output voltage at V

DR

and VDF is the hysteresis in the system.

DR

is undefined at the voltage below V

OUT

pin equals the input voltage at VIN pin.

OUT

INPUT VOLTAGE (V

DETECT RELEASE VOLTAGE (V

6

DETECT FAIL VOLTAGE (V

pin equals the input volt-

OUT

output voltage will be undefined.

OUT

. Exceeding the

MIN

) and the detect release

MIN

IN)

DR)

DF)

MINIMUM OPERATING VOLTAGE (V

GROUND VOLTAGE (V

OUTPUT VOLTAGE (V

GROUND VOLTAGE (V

1

2

3

4

5

SS)

OUT)

SS)

MIN)

Rev. 2.2 8/14/02 3

Loading...

Loading...