Page 1

tm

C

R

C

00

G

1

G

2

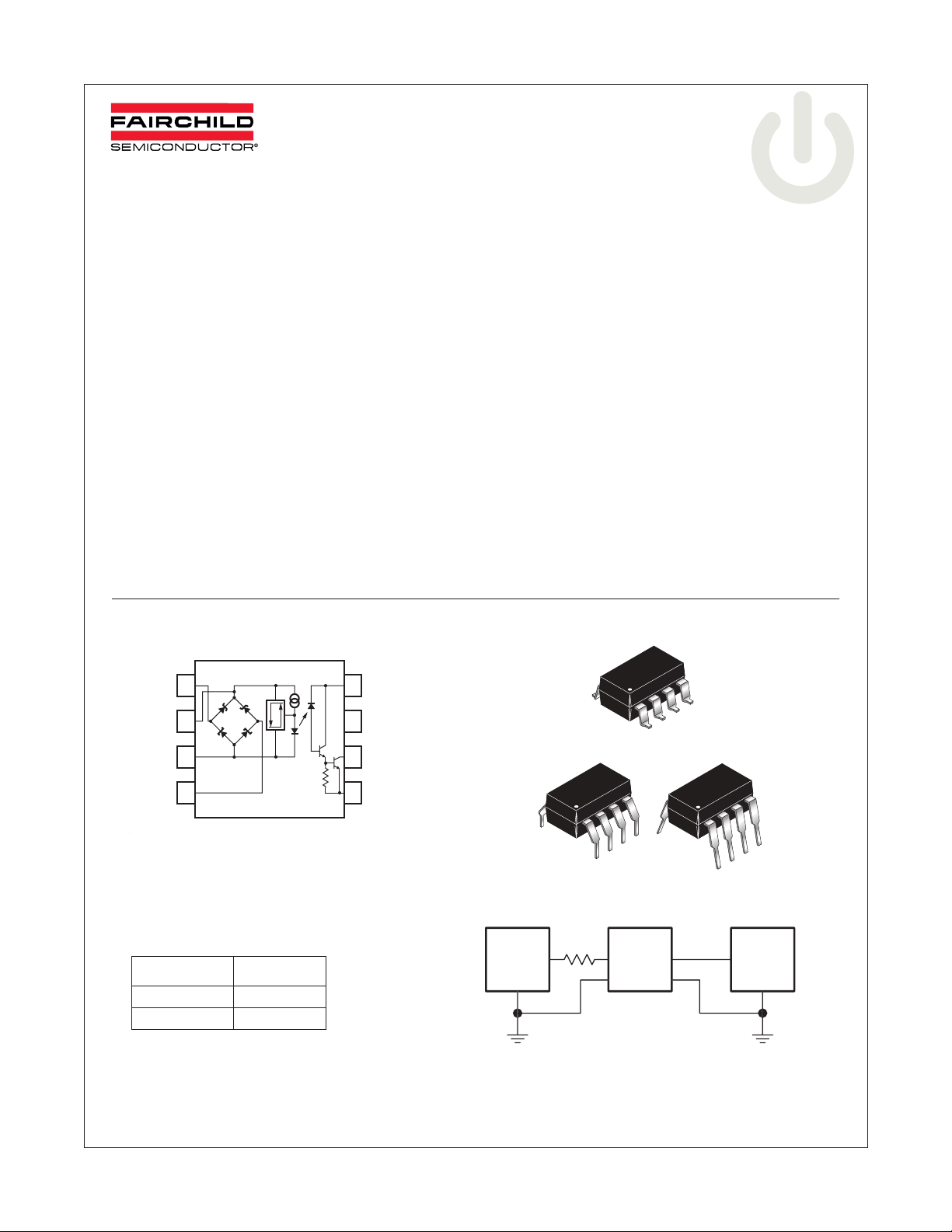

HCPL-3700 AC/DC to Logic Interface Optocoupler

April 2007

HCPL-3700

AC/DC to Logic Interface Optocoupler

Features

AC or DC input

■

■

Programmable sense voltage

Logic level compatibility

■

■

Threshold guaranteed over temperature (0°C to 70°C)

■

Optoplanar™ construction for high common mode

immunity

■

UL recognized (file # E90700)

VDE certified – ordering option ‘V’, e.g., HCPL3700V

■

Description

The HCPL-3700 voltage/current threshold detection

optocoupler consists of an AlGaAs LED connected to a

threshold sensing input buffer IC which are optically coupled to a high gain darlington output. The input buffer

chip is capable of controlling threshold levels over a wide

range of input voltages with a single resistor. The output

is TTL and CMOS compatible.

Applications

■

Low voltage detection

5 V to 240 V AC/DC voltage sensing

■

■

Relay contact monitor

■

Current sensing

Microprocessor Interface

■

■

Industrial controls

Schematic Package

AC

DC+

DC-

1

2

3

8

V

CC

7

NC

6

V

O

8

1

45

AC GND

8

1

8

1

TRUTH TABLE

(Positive Logic)

Input Output

HL

LH

A 0.1 µF bypass capacitor must

be connected between pins 8

AC/D

POWE

ND

HCPL-37

LOGI

ND

and 5.

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1

Page 2

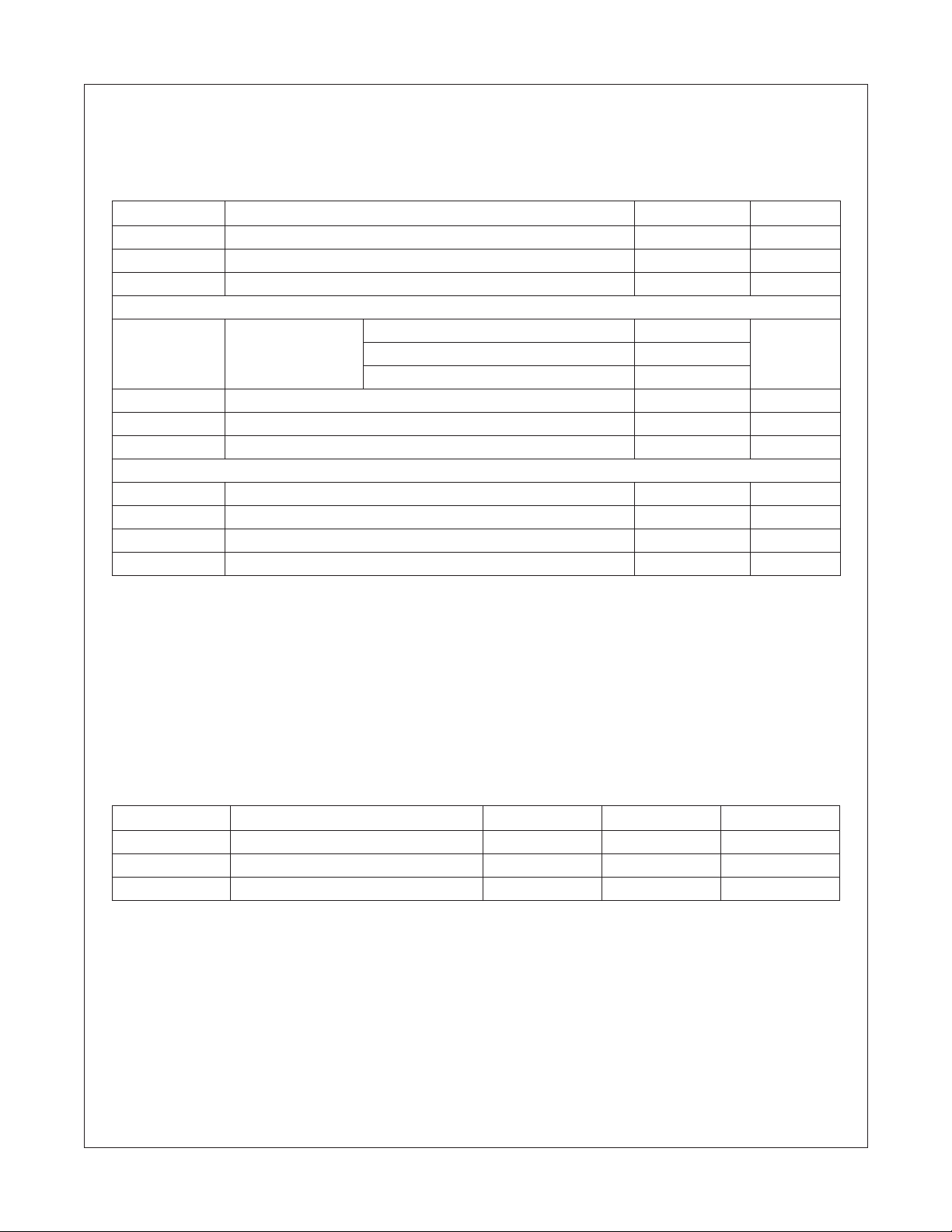

Absolute Maximum Ratings

(No derating required up to 70°C)

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Value Units

T

STG

T

OPR

T

SOL

EMITTER

I

IN

V

IN

P

IN

P

T

DETECTOR

I

O

V

CC

V

O

P

O

Storage Temperature -55 to +125 °C

Operating Temperature -40 to +85 °C

Lead Solder Temperature 260 for 10 sec °C

Input Current Average 50 (Max.) mA

Surge, 3ms, 120Hz Pulse Rate 140 (Max.)

Tr ansient, 10µs, 120Hz Pulse Rate 500 (Max.)

Input Voltage (Pins 2-3) -0.5 (Max.) V

Input Power Dissipation

Total Package Power Dissipation

Output Current (Average)

(1)

(3)

(2)

230 (Max.) mW

305 (Max.) mW

30 (Max.) mA

Supply Voltage (Pins 8-5) -0.5 to 20 V

Output Voltage (Pins 6-5) -0.5 to 20 V

Output Power Dissipation

(4)

210 (Max.) mW

HCPL-3700 AC/DC to Logic Interface Optocoupler

Notes:

1. Derate linearly above 70°C free-air temperature at a rate of 1.8 mW/°C.

2. Derate linearly above 70°C free-air temperature at a rate of 2.5 mW/°C.

3. Derate linearly above 70°C free-air temperature at a rate of 0.6 mA/°C.

4. Derate linearly above 70°C free-air temperature at a rate of 1.9 mW/°C.

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to absolute maximum ratings.

Symbol Parameter Min. Max. Units

V

CC

T

A

f Operating Frequency 0 4 kHz

Supply Voltage 2 18 V

Operating Temperature 0 70 °C

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 2

Page 3

≥

≤

≥

≥

≥

≥

≤

HCPL-3700 AC/DC to Logic Interface Optocoupler

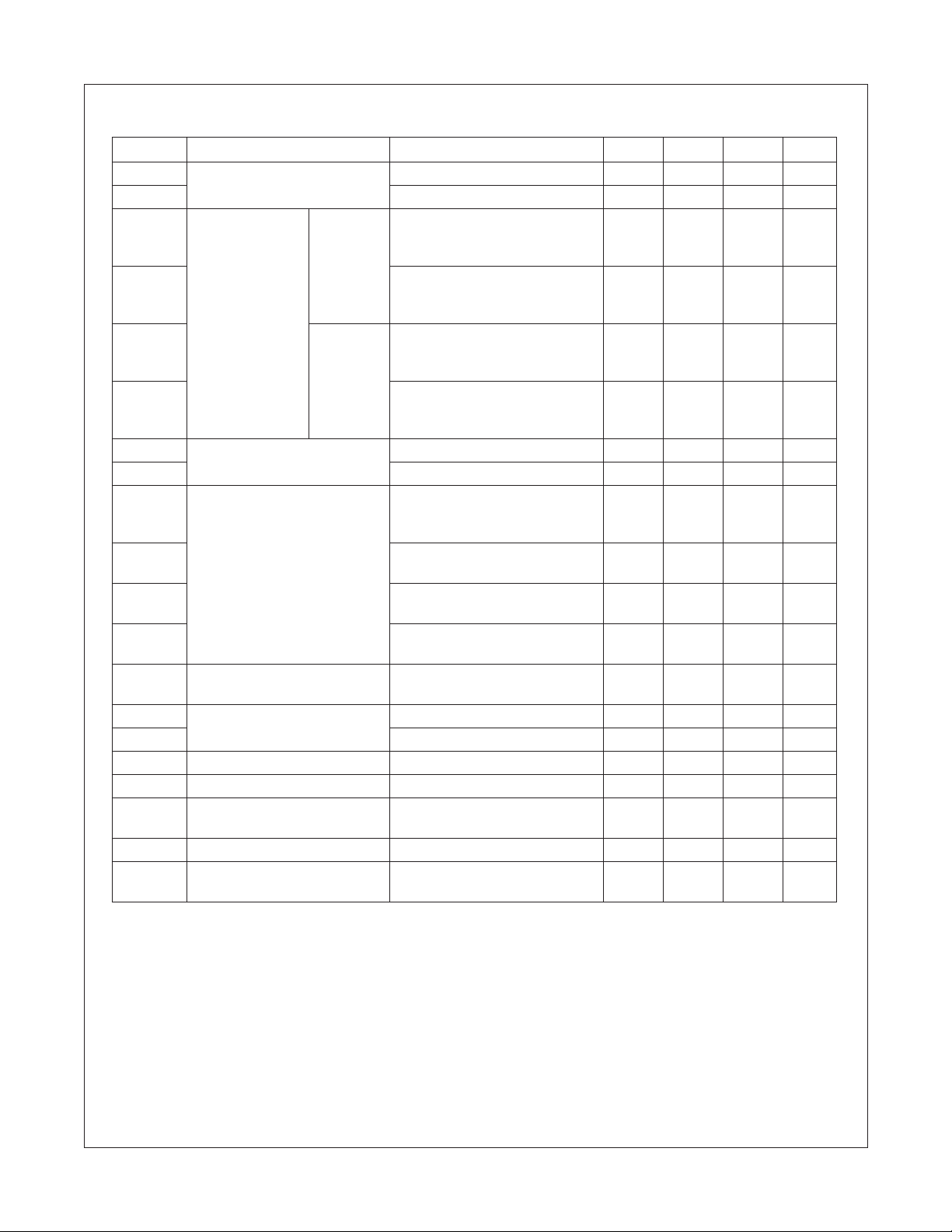

Electrical Characteristics

(T

= 0°C to 70°C Unless otherwise specified)

A

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

V

V

V

V

V

V

V

I

TH+

I

TH-

V

V

I

HYS

HYS

IHC1

IHC2

IHC3

V

I

D1,2

D3,4

V

I

OH

I

CCL

I

CCH

C

TH+

TH+

Input Threshold Current V

Input Threshold

Voltage

TH-

TH-

Hysteresis I

Input Clamp Voltage V

DC

(Pins 2,3)

AC

(Pins 1,4)

= V

IN

V

= 0.4 V, I

O

V

= V

IN

V

= 4.5 V, V

CC

I

4.2mA

O

V

= V

IN

V

= 4.5 V, V

CC

I

100µA

O

|V

= V

IN

V

= 4.5 V, V

CC

I

4.2 mA

O

|V

= |V

IN

V

= 4.5 V, V

CC

I

100µA

O

= I

HYS

V

= V

HYS

= V

IHC1

I

= 10 mA,

IN

, V

TH+

– V

2

- V

2

1

TH+

= 4.5 V 1.96 2.4 3.11 mA

CC

4.2mA

O

(Pins 1 & 4 Open)

3

= 0.4V

O

(Pins 1 & 4 Open)

3

= 2.4 V

O

– V

| (Pins 2 & 3 Open)

4

= 0.4 V

O

- V

| (Pins 2 & 3 Open)

1

4

= 2.4 V

O

– I

TH-

– V

TH+

2

- V

TH-

, V

3

3

(5)

(5)

(5)

(5)

(5)

= GND

1.00 1.2 1.62 mA

3.35 3.8 4.05 V

2.01 2.5 2.86 V

4.23 5.0 5.50 V

2.87 3.7 4.20 V

1.2 mA

1.3 V

5.4 6.3 6.6 V

Pins 1 & 4 connected to Pin 3

V

= |V

– V

|, |I

IHC2

4

| = 10mA

IN

1

6.1 7.0 7.3 V

(Pins 2 & 3 Open)

V

IHC3

I

= 15mA (Pins 1 & 4 Open)

IN

ILC

Input Current VIN = V2 – V3 = 5.0V

IN

V

ILC

I

= -10mA

IN

– V3, V3 = GND,

= V

2

= V2 – V3, V3 = GND,

12.5 13.4 V

-0.75 V

3.0 3.7 4.4 mA

(Pins 1 & 4 Open)

Bridge Diode

Forward Voltage

Logic LOW Output Voltage VCC = 4.5 V, IOL = 4.2mA

OL

Logic HIGH Output Current VOH = VCC = 18V

Logic LOW Supply Current V2 – V3 = 5.0V, VO = Open,

IIN = 3mA 0.65 V

IIN = 3mA 0.65 V

(5)

(5)

0.04 0.4 V

1.0 4 mA

V

= 5V

CC

Logic HIGH Supply Current VCC = 18V, VO = Open 0.01 4 µA

Input Capacitance f = 1MHz, VIN = 0V

IN

50 pF

(Pins 2 & 3, Pins 1 & 4 Open)

100 µA

Note:

5. Logic LOW output level at pin 6 occurs when V

Logic HIGH output level at pin 6 occurs when V

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 3

IN

IN

V

TH+

V

TH-

and when V

and when V

IN

IN

> V

< V

TH-

TH+

once V

once V

exceeds V

IN

decreases below V

IN

TH+

.

.

TH-

Page 4

HCPL-3700 AC/DC to Logic Interface Optocoupler

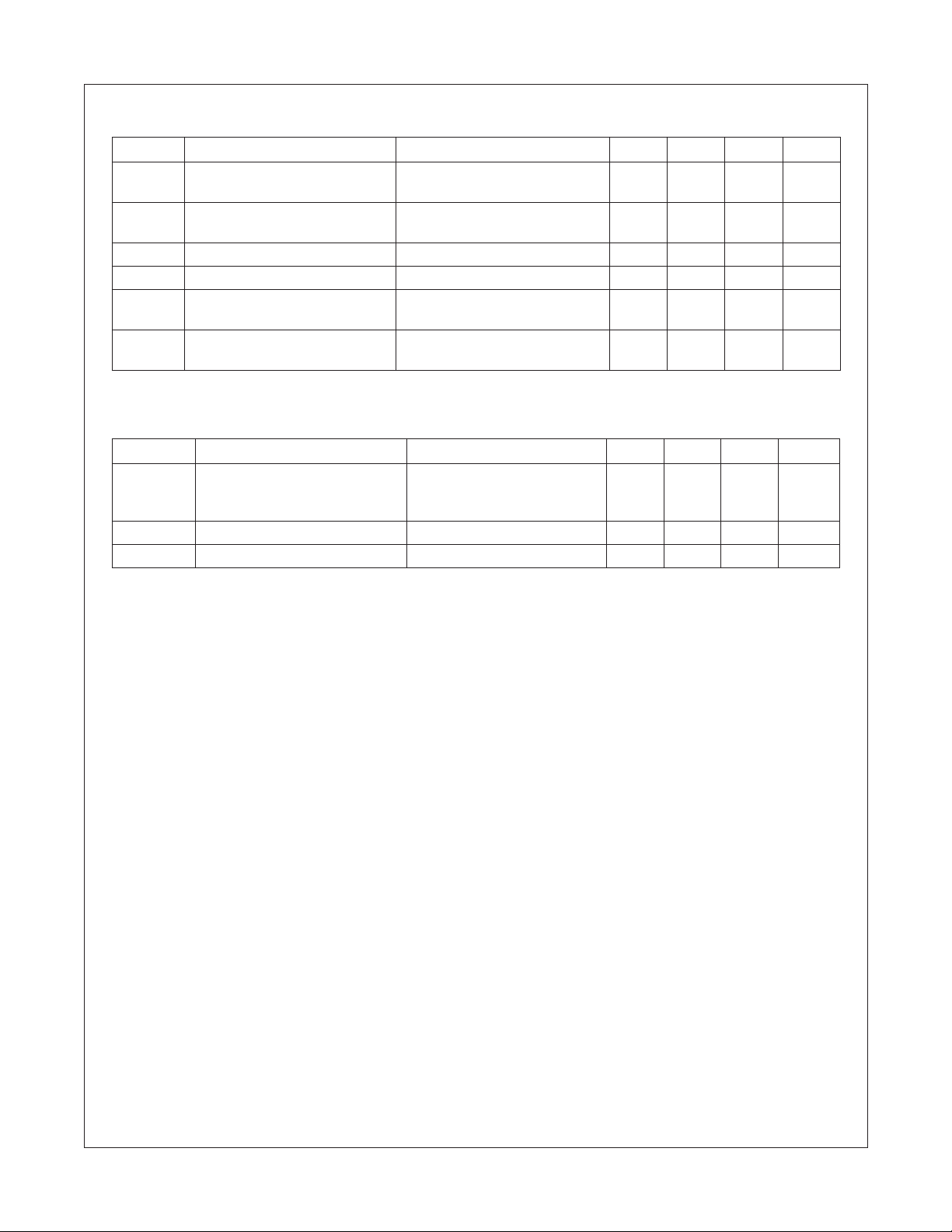

Switching Characteristics (T

= 25°C, VCC = 5 V Unless otherwise specified)

A

Symbol AC Characteristics Test Conditions Min. Typ. Max. Unit

T

PHL

Propagation Delay Time

(to Output Low Level)

T

PLH

Propagation Delay Time

(to Output High Level)

Output Rise Time (10–90%) RL = 4.7kΩ, CL = 30pF 45 µs

t

r

Output Fall Time (90–10%) RL = 4.7kΩ, CL = 30pF 0.5 µs

t

f

| Common Mode Transient

|CM

H

Immunity (at Output High Level)

| Common Mode Transient

|CM

L

Immunity (at Output Low Level)

Package Characteristics

RL = 4.7kΩ, CL = 30pF

RL = 4.7kΩ, CL = 30pF

IIN = 0 mA, RL = 4.7kΩ,

V

= 2.0 V, VCM = 1400V

O min

IN = 3.11mA, RL = 4.7kΩ,

V

= 0.8V, VCM = 140V

O max

(TA = 0°C to 70°C Unless otherwise specified)

(6)

(6)

(7)(8)

(7)(8)

6.0 15 µs

25.0 40 µs

4000 V/µs

600 V/µs

Symbol Characteristics Test Conditions Min. Typ. Max. Unit

V

ISO

R

I-O

C

I-O

Withstand Insulation Voltage Relative humidity < 50%,

T

= 25°C, t = 1 min,

A

I

I-O

Resistance (input to output) VIO = 500Vdc

≤ 2µA

(9)(10)

(9)

2500 V

12

10

Capacitance (input to output) f = 1MHz, VIO = 0Vdc 0.6 pF

RMS

Ω

Notes:

6. T

propagation delay is measured from the 2.5V level of the leading edge of a 5.0V input pulse (1µs rise time) to

PHL

the 1.5 V level on the leading edge of the output pulse. T

propagation delay is measured on the trailing edges

PLH

of the input and output pulse. (Refer to Fig. 9)

7. Common mode transient immunity in logic high level is the maximum tolerable (positive) dV

edge of the common mode pulse signal V

, to assure that the output will remain in a logic high state (i.e., VO >

CM

2.0 V). Common mode transient immunity in logic low level is the maximum tolerable (negative) dV

trailing edge of the common mode pulse signal, V

(i.e., V

8. In applications where dV

< 0.8 V). Refer to Fig. 10.

O

cm

/dt may exceed 50,000 V/µs (Such as static discharge), a series resistor, RCC,

, to assure that the output will remain in a logic low state

CM

/dt on the leading

cm

/dt on the

cm

should be included to protect the detector chip from destructive surge currents. The recommended value for

R

is 240V per volt of allowable drop in VCC (between pin 8 and VCC) with a minimum value of 240Ω.

CC

9. Device is considered a two terminal device: Pins 1, 2, 3 and 4 are shorted together and Pins 5, 6, 7 and 8 are

shorted together.

10. The 2500 V

/1 min. capability is validated by a 3.0 kV

RMS

11. AC voltage is instantaneous voltage for V

12. All typicals at T

= 25°C, VCC = 5V unless otherwise specified.

A

TH+

& V

TH-

.

/1 sec. dielectric voltage withstand test.

RMS

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 4

Page 5

Typical Performance Curves

HCPL-3700 AC/DC to Logic Interface Optocoupler

Fig. 1 Logic Low Supply Current vs. Operating Supply Voltage

4.0

3.5

3.0

2.5

2.0

1.5

1.0

- LOGIC LOW SUPPLY CURRENT (mA)

0.5

CCL

I

0.0

4681012 14 16 18 20

VCC - OPERATING SUPPLY VOLTAGE (V)

Fig. 3 Input Current/Low Level Output Voltage

4.2

4.0

3.8

3.6

3.4

(mA)

IN

3.2

3.0

2.8

2.6

Input Current, I

2.4

2.2

2.0

1.8

-40 -20 0 25 45 65 85

vs. Temperature

I

IN

VIN = 5.0 V

(PINS 2 and 3)

= 5.0 V

V

CC

V

OL

V = 5.0 V

CC

I

= 4.2 mA

OL

TA - TEMPERATURE (°C)

120

110

100

90

80

70

60

50

40

30

20

10

0

(mV)

OL

V

(DC) - VOLTAGE THRESHOLD (V)

V

Fig. 2 Input Current vs. Input Voltage

50

DC (Pins 1,2 shorted together

45

pins 3,4 shorted together)

40

35

mA)

30

25

20

15

10

- INPUT CURRENT (

5

IN

I

0

-5

-10

02468101214

VIN - INPUT VOLTAGE (V)

Fig. 4 Current Threshold/Voltage Threshold

4.2

4.0

3.8

3.6

3.4

3.2

3.0

2.8

2.6

2.4

2.2

TH

2.0

1.8

-40 -20 0 25 45 65 85

vs. Temperature

TH+

V

I

TH+

TH-

V

TH-

I

TA - TEMPERATURE (°C)

DC (Pins 1 & 4 Open)

AC (pins 2 & 3 Open)

3.2

3.0

2.8

2.6

2.4

2.2

2.0

1.8

1.6

1.4

1.2

(DC) - CURRENT THRESHOLD (mA)

TH

1.0

I

0.8

Fig. 5 Propagation Delay vs. Temperature

70

60

µs)

50

40

30

20

- PROPAGATION DELAY (

P

T

10

0

-60 -40 -20 0 20 40 60 80 100

TPLH

TPHL

TA - TEMPERATURE (°C)

µs)

- RISE TIME (

r

T

Fig. 6 Rise and Fall Time vs. Temperature

100

90

80

70

60

50

40

30

20

10

0

-40 -20 0 25 45 65 85

Tf

Tr

TA - TEMPERATURE (°C)

0.8

0.7

0.6

µs)

0.5

0.4

0.3

- FALL TIME (

f

T

0.2

0.1

0.0

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 5

Page 6

HCPL-3700 AC/DC to Logic Interface Optocoupler

Fig. 7 Logic High Supply Current

vs. Temperature

1000

nA)

V

= 18 V

CC

VO = OPEN

I

= 0 mA

IN

100

10

- LOGIC HIGH SUPPLY CURRENT (

CCH

I

1

-60 -40 -20 0 20 40 60 80 100

TA - TEMPERATURE (°C)

Fig. 8 External Threshold Characteristics V+/V- vs. Rx

300

250

200

150

100

50

V+/V- -EXTERNAL THRESHOLD VOLTAGE (V)

0

04080120 160 200 240

V+ (AC)

RX - EXTERNAL SERIES RESISTOR (KΩ)

V- (AC)

V+ (DC)

V- (DC)

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 6

Page 7

HCPL-3700 AC/DC to Logic Interface Optocoupler

+5V

5V

AC

V

1

Pulse

Generator

tr = 5ns

Z = 50

Ω

O

V

Pulse Amplitude = 50 V

Pulse Width = 1 ms

f = 100 Hz

T = T = 1.0 µs (10 - 90%)

I

IN

A

B

V

FF

IN

rf

DC+

2

DC-

3

AC GND

4

AC

1

DC+

2

DC-

3

AC

4

Pulse Gen

8

CC

.1uf

7

bypass

V

6

O

5

R

L

Output

(V )

O

Input

(V )

IN

t

PHL

Output

90%

(V )

O

10% 10%

tt

r

t

PLH

2.5V

0V

V

O

90%

1.5 V

V

OL

f

Fig. 9. Switching Test Circuit

V

CM

H

R *

CCV

8

.1uf

7

bypass

O

6

GNDV5

V

CM

-

+

CC

+5V

R

L

Output

(V )

O

C **

L

* SEE NOTE 8

V

CM

V

O

Switching Pos. (A)

I = 0 mA

IN

V (Min)

O

V

CM

L

5V

5V

CM

H

V (Max)

** C IS 30 pF, WHICH INCLUDES PROBE

L

AND STRAY WIRING CAPACITANCE

V V

O

O

Switching Pos. (B)

I = 3.11 mA

IN

Fig. 10. Test Circuit for Common Mode Transient Immunity and Typical Waveforms

OL

CM

L

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 7

Page 8

Package Dimensions

HCPL-3700 AC/DC to Logic Interface Optocoupler

Through Hole

56 7

0.390 (9.91)

0.370 (9.40)

0.200 (5.08)

0.140 (3.55)

SEATING PLANE

0.022 (0.56)

0.016 (0.41)

Surface Mount

0.390 (9.91)

0.370 (9.40)

3214

3

241

8

0.070 (1.78)

0.045 (1.14)

0.100 (2.54) TYP

PIN 1

ID.

0.270 (6.86)

0.250 (6.35)

0.020 (0.51) MIN

0.154 (3.90)

0.120 (3.05)

PIN 1

ID.

0.016 (0.40)

0.008 (0.20)

15° MAX

0.300 (7.62)

TYP

0.4" Lead Spacing

PIN 1

0.270 (6.86)

0.250 (6.35)

8

0.070 (1.78)

0.045 (1.14)

0.154 (3.90)

0.120 (3.05)

ID.

0.004 (0.10) MIN

0.016 (0.40)

0.008 (0.20)

0° to 15°

0.400 (10.16)

TYP

0.200 (5.08)

0.140 (3.55)

SEATING PLANE

0.022 (0.56)

0.016 (0.41)

3

241

56 7

0.390 (9.91)

0.370 (9.40)

0.100 (2.54) TYP

Recommended Pad Layout for Surface Mount

Leadforms

0.070 (1.78)

0.270 (6.86)

0.250 (6.35)

0.022 (0.56)

0.016 (0.41)

0.100 (2.54)

TYP

8

0.070 (1.78)

0.045 (1.14)

0.020 (0.51)

0.300 (7.62)

MIN

0.045 [1.14]

0.315 (8.00)

0.405 (10.30)

567

Lead Coplanarity : 0.004 (0.10) MAX

Note:

All dimensions are in inches (millimeters)

TYP

MIN

MIN

0.016 (0.41)

0.008 (0.20)

0.415 (10.54)

0.060 (1.52)

0.100 (2.54)

0.295 (7.49)

0.030 (0.76)

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 8

Page 9

Ordering Information

Option Example Part Number Description

No Suffix HCPL3700 Shipped in Tubes

S HCPL3700S Surface Mount Lead Bend

SD HCPL3700SD Surface Mount; Tape and Reel

W HCPL3700W 0.4" Lead Spacing

V HCPL3700V VDE0884

WV HCPL3700WV VDE0884; 0.4” Lead Spacing

SV HCPL3700SV VDE0884; Surface Mount

SDV HCPL3700SDV VDE0884; Surface Mount; Tape and Reel

Marking Information

HCPL-3700 AC/DC to Logic Interface Optocoupler

1

3700

43

Definitions

1Fairchild logo

2Device number

VDE mark (Note: Only appears on parts ordered with VDE

3

option – See order entry table)

4Two digit year code, e.g., ‘07’

5Two digit work week ranging from ‘01’ to ‘53’

6 Assembly package code

2

T1YYXXV

5

6

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 9

Page 10

Carrier Tape Specifications

0

HCPL-3700 AC/DC to Logic Interface Optocoupler

12.0 ±0.1

4.90 ±0.20

13.2 ±0.2

Reflow Profile

0.30 ±0.05

0.1 MAX

4.0 ±0.1

10.30 ±0.20

User Direction of Feed

300

250

Temperature (°C)

200

150

100

50

0

0

• Peak reflow temperature: 225 C (package surface temperature)

• Time of temperature higher than 183 C for 60–150 seconds

• One time soldering reflow is recommended

Ramp up = 3

0.5 1 1.5 2 2.5 3 3.5 4 4.5

4.0 ±0.1

225 C peak

Time above 183 C, 60–150 sec

C/sec

Time (Minute)

Ø1.55 ±0.05

1.75 ±0.10

7.5 ±0.1

16.0 ±

10.30 ±0.20

Ø1.6 ±0.1

215 C, 10–30 s

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 10

Page 11

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an

exhaustive list of all such trademarks.

®

ACEx

Across the board. Around the world.™

ActiveArray™

Bottomless™

Build it Now™

CoolFET™

CROSSVOLT™

CTL™

Current Transfer Logic™

DOME™

2

CMOS™

E

EcoSPARK

®

EnSigna™

FACT Quiet Series™

®

FACT

®

FAST

FASTr™

FPS™

®

FRFET

GlobalOptoisolator™

GTO™

HiSeC™

i-Lo™

ImpliedDisconnect™

IntelliMAX™

ISOPLANAR™

MICROCOUPLER™

MicroPak™

MICROWIRE™

Motion-SPM™

MSX™

MSXPro™

OCX™

OCXPro™

OPTOLOGIC

OPTOPLANAR

®

®

PACMAN™

PDP-SPM™

POP™

Power220

Power247

®

®

PowerEdge™

PowerSaver™

PowerTrench

Programmable Active Droop™

QFET

®

®

QS™

QT Optoelectronics™

Quiet Series™

RapidConfigure™

RapidConnect™

ScalarPump™

SMART START™

®

SPM

STEALTH™

SuperFET™

SuperSOT™-3

SuperSOT™-6

SuperSOT™-8

SyncFET™

TCM™

The Power Franchise

™

®

TinyBoost™

TinyBuck™

TinyLogic

®

TINYOPTO™

TinyPower™

TinyWire™

TruTranslation™

µSerDes™

®

UHC

UniFET™

VCX™

Wire™

HCPL-3700 AC/DC to Logic Interface Optocoupler

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS

HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE

APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER

ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S

WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body or

(b) support or sustain life, and (c) whose failure to perform

when properly used in accordance with instructions for use

2. A critical component in any component of a life support,

device, or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to

result in a significant injury of the user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In Design This datasheet contains the design specifications for product

development. Specifications may change in any manner without notice.

Preliminary First Production This datasheet contains preliminary data; supplementary data will be

published at a later date. Fairchild Semiconductor reserves the right to

make changes at any time without notice to improve design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild Semiconductor

reserves the right to make changes at any time without notice to improve

design.

Obsolete Not In Production This datasheet contains specifications on a product that has been

discontinued by Fairchild Semiconductor. The datasheet is printed for

reference information only.

Rev. I25

©2005 Fairchild Semiconductor Corporation www.fairchildsemi.com

HCPL-3700 Rev. 1.0.1 11

Loading...

Loading...