Fairchild FOD852 service manual

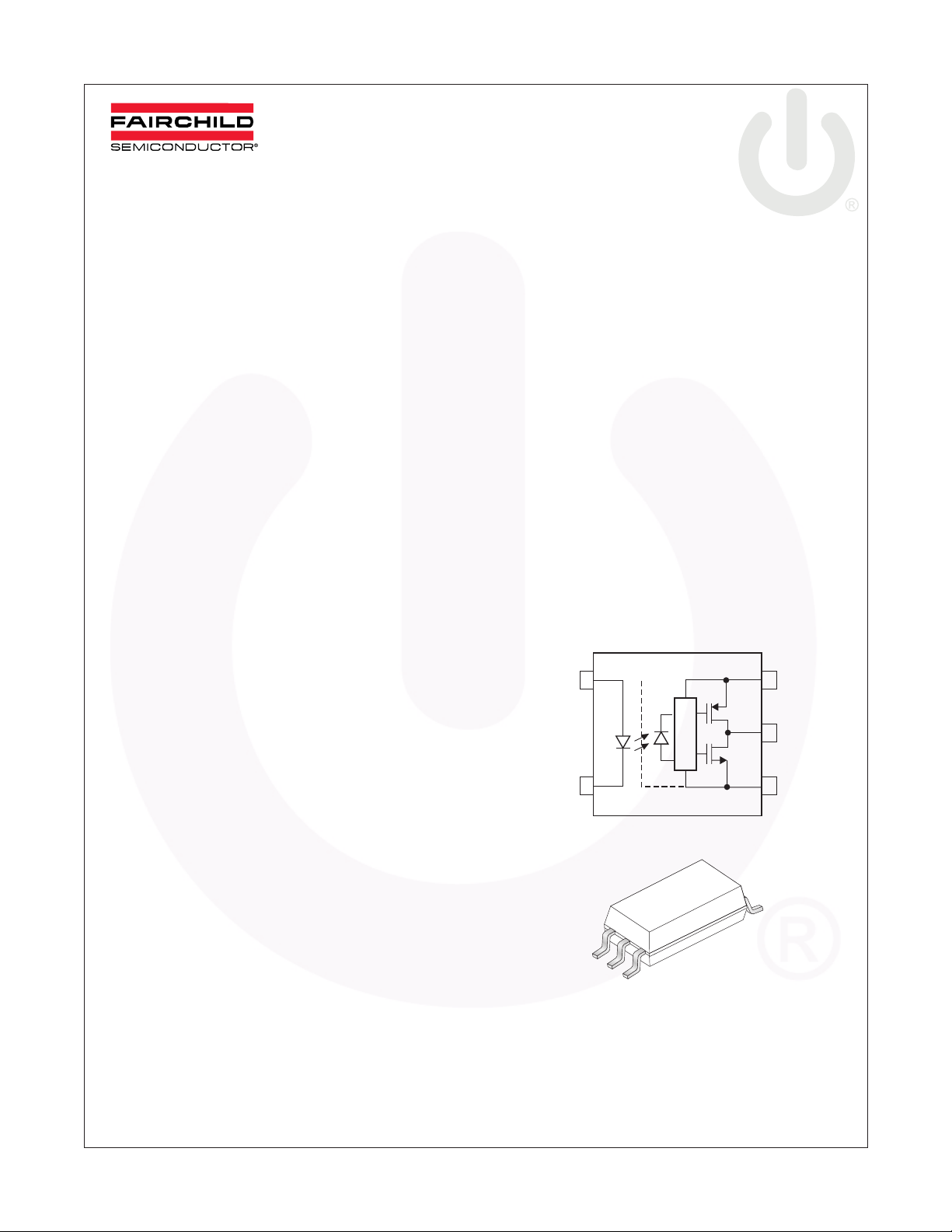

FOD8321 — 2.5A Output Current, Gate Drive Optocoupler in Optoplanar

May 2012

FOD8321

2.5A Output Current, Gate Drive Optocoupler in

®

Optoplanar

Wide Body SOP 5-Pin

Features

Fairchild’s Optoplanar

■

provides reliable and high voltage insulation with

greater than 8mm creepage and clearance distance,

and 0.5mm internal insulation distance while still

offering a compact footprint

2.5A output current driving capability for medium

■

power IGBT/MOSFET

– Use of P-Channel MOSFETs at output stage

enables output voltage swing close to the supply

rail

■

20kV/µs Minimum Common Mode Rejection

Wide Supply Voltage range from 15V to 30V

■

■

Fast Switching Speed over full operating temperature

range

– 500ns max. propagation delay

– 300ns max. pulse width distortion

UnderVoltage LockOut (UVLO) with hysteresis

■

■

Extended industrial temperate range, -40 to 100°C

temperature range

■

Safety and regulatory approvals

– UL1577, 5,000V

– DIN EN/IEC60747-5-5, 1,414V peak working

insulation voltage

®

packaging technology

for 1 min.

RMS

Applications

■

AC and brushless DC motor drives

Industrial inverter

■

■

Uninterruptible power supply

Induction heating

■

■

Isolated IGBT/Power MOSFET gate drive

Description

The FOD8321 is a 2.5A Output Current Gate Drive

Optocoupler, capable of driving medium power IGBT/

MOSFETs. It is ideally suited for fast switching driving of

power IGBT and MOSFETs used in motor control

inverter applications, and high performance power

systems.

It utilizes Fairchild’s coplanar packaging technology,

Optoplanar

high insulation voltage and high noise immunity.

It consists of a aluminum gallium arsenide (AlGaAs) light

emitting diode optically coupled to an integrated circuit

with a high-speed driver for push-pull MOSFET output

stage. The device is housed in a wide body 5-pin small

outline plastic package.

®

, and optimized IC design to achieve reliably

Functional Schematic

ANODE

CATHODE V

1

3

V

6

DD

5

V

O

4

SS

®

Wide Body SOP 5-Pin

Related Resources

■

FOD3120, High Noise Immunity, 2.5A Output Current,

Gate Drive Optocoupler Datasheet

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8321 Rev. 1.0.4

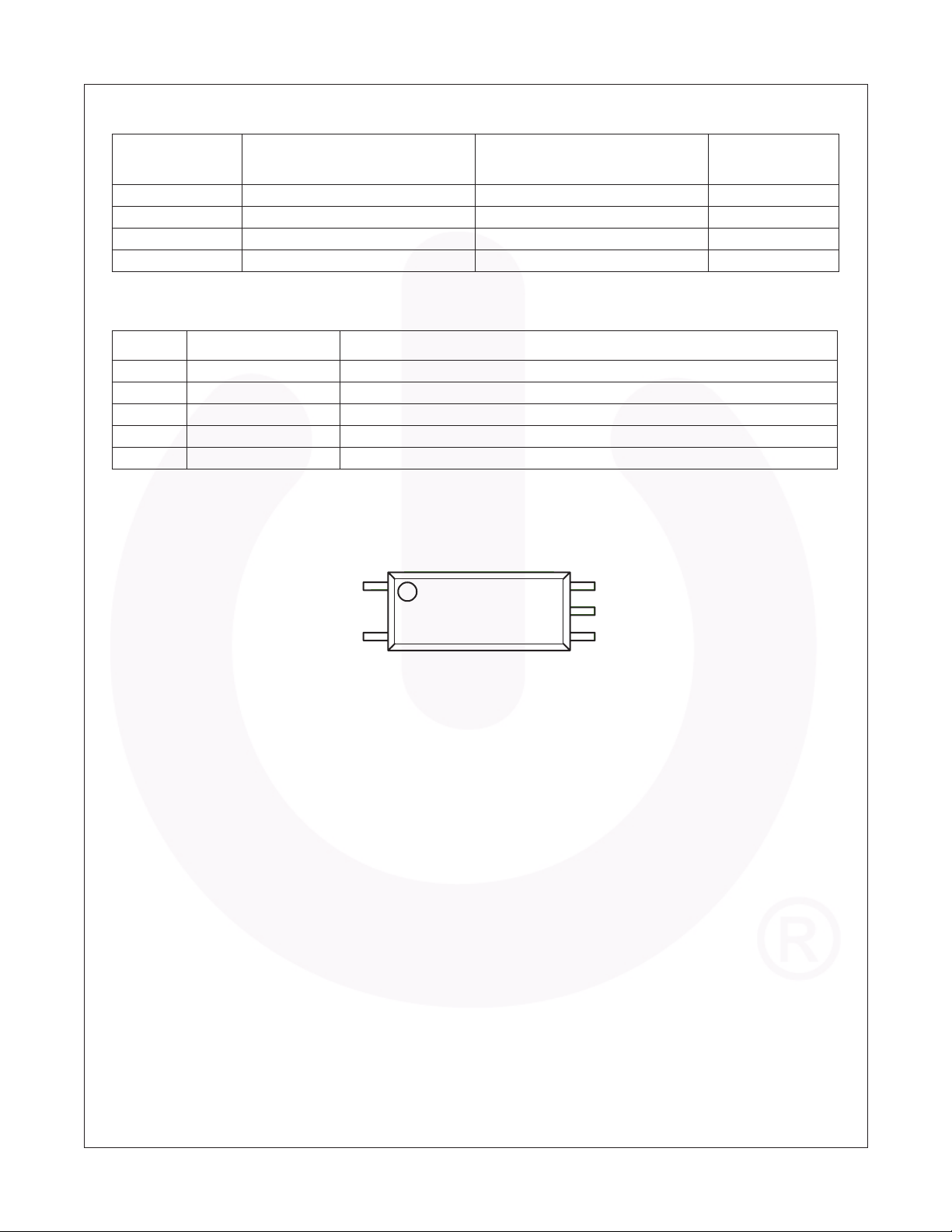

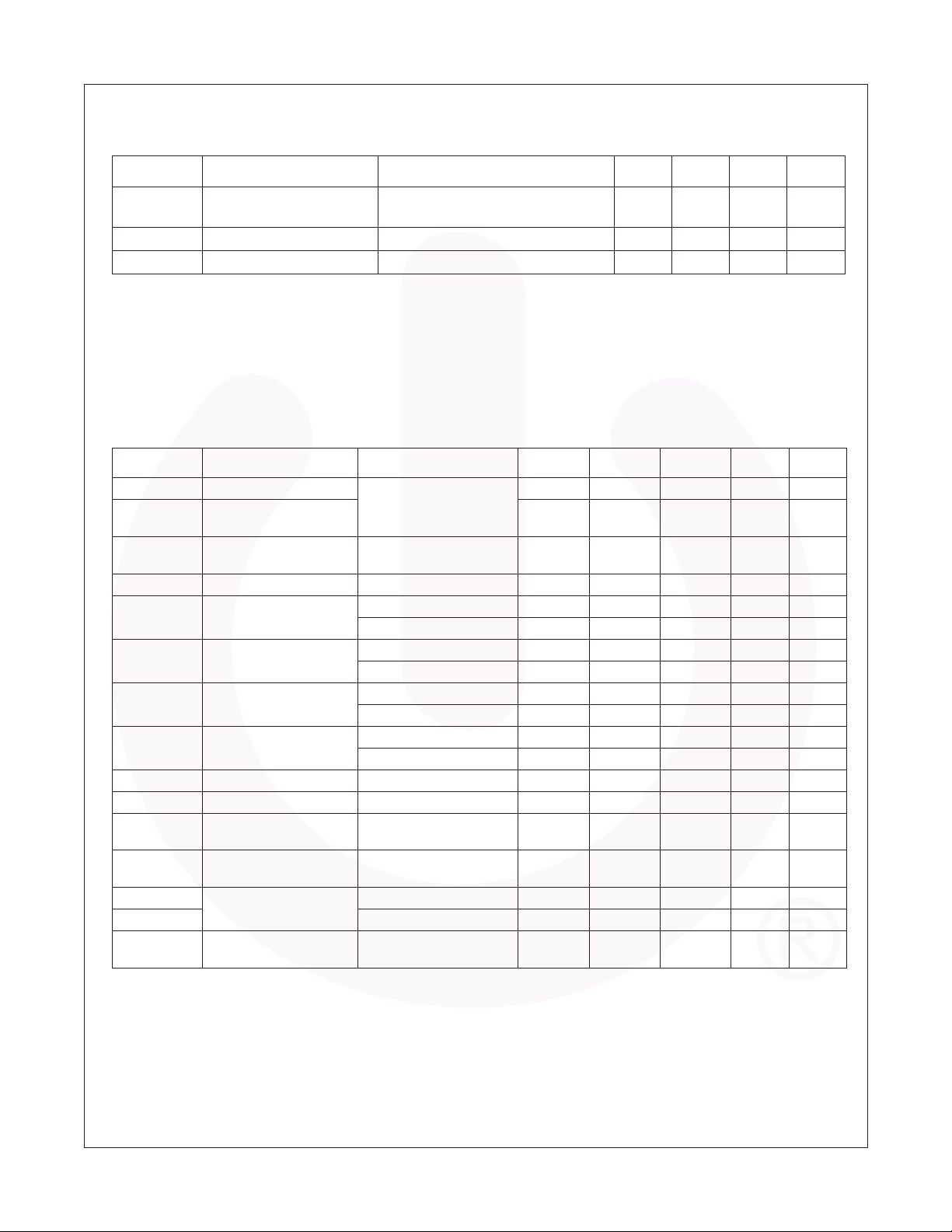

Truth Table

V

V

DD–

LED

Off 0V to 30V 0V to 30V Low

On 0V to 11.5V 0V to 10V Low

On 11.5V to 14.5V 10V to 13V Transition

On 14.5V to 30V 13V to 30V High

“Positive Going”

SS

(Turn-on)

V

DD–

V

“Positive Going”

SS

(Turn-off)

Pin Definitions

Pin # Name Description

1 Anode LED Anode

3 Cathode LED Cathode

4V

5V

6V

SS

O

DD

Negative Supply Voltage

Output Voltage

Positive Supply voltage

FOD8321 — 2.5A Output Current, Gate Drive Optocoupler in Optoplanar

V

O

Pin Configuration

ANODE

CATHODE

1

3

6

V

DD

5

V

O

4

V

SS

®

Wide Body SOP 5-Pin

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8321 Rev. 1.0.4 2

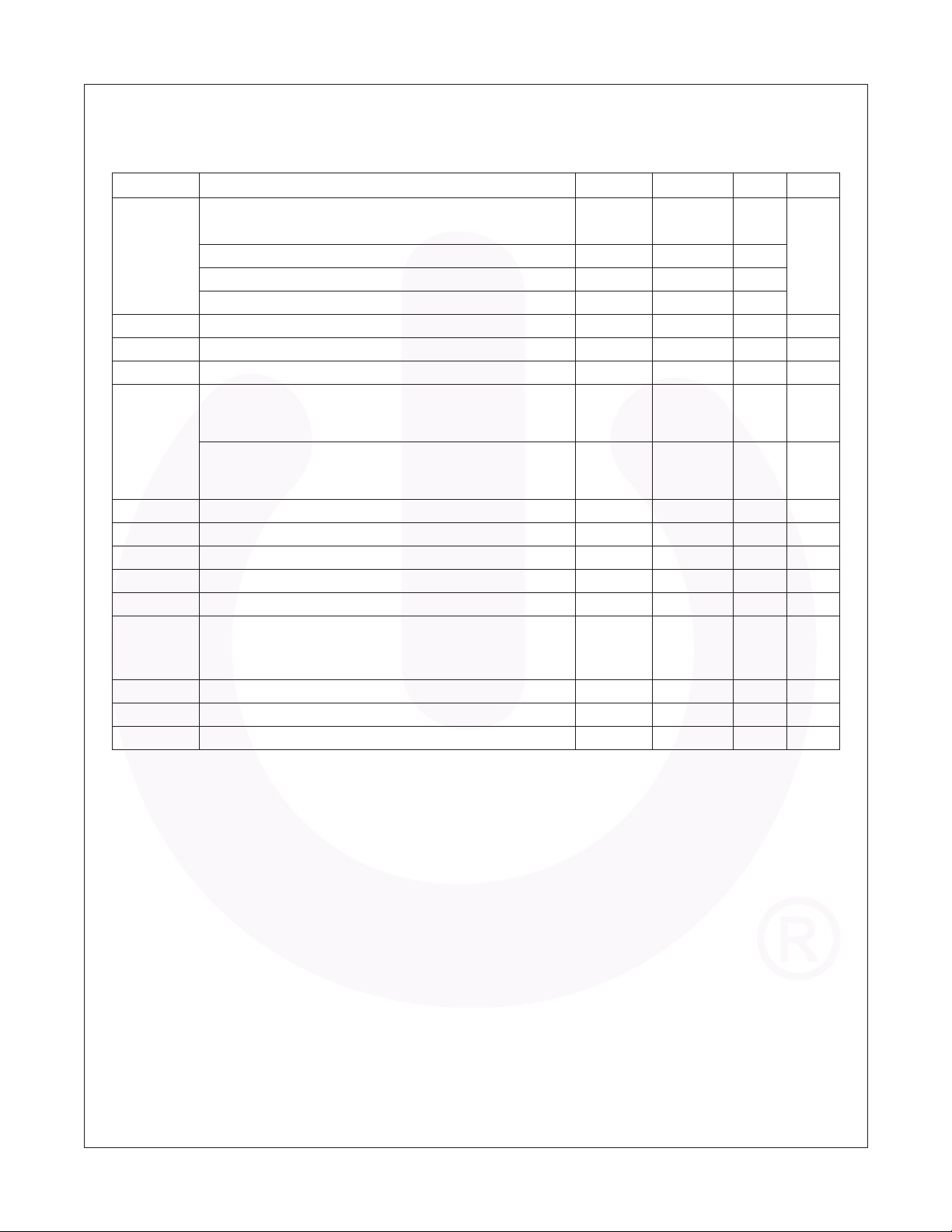

Safety and Insulation Ratings

As per DIN EN/IEC60747-5-5. This optocoupler is suitable for “safe electrical insulation” only within the safety limit

data. Compliance with the safety ratings shall be ensured by means of protective circuits.

Symbol Parameter Min. Typ. Max. Unit

Pollution Degree (DIN VDE 0110/1.89) 2

CTI Comparative Tracking Index 175

V

PR

V

IORM

V

IOTM

External Creepage 8.0 mm

External Clearance 8.0 mm

Insulation Thickness 0.5 mm

T

S

I

S,INPUT

P

S,OUTPUT

R

IO

Installation Classifications per DIN VDE 0110/1.89 Table 1

For Rated Mains Voltage < 150Vrms I–IV

For Rated Mains Voltage < 300Vrms I–IV

For Rated Mains Voltage < 450Vrms I–IIII

For Rated Mains Voltage < 600Vrms I–III

Climatic Classification 40/100/21

Input to Output Test Voltage, Method b,

V

x 1.875 = V

IORM

t

= 1 sec., Partial Discharge < 5pC

m

, 100% Production Test with

PR

Input to Output Test Voltage, Method a,

V

x 1.5 = V

IORM

t

= 60 sec.,Partial Discharge < 5 pC

m

, Type and Sample Test with

PR

Max Working Insulation Voltage 1,414 V

Highest Allowable Over Voltage 6000 V

2651

2121

peak

peak

Safety Limit Values – Maximum Values Allowed in the

Event of a Failure

Case Temperature 150 °C

Input Current 200 mA

Output Power 600 mW

Insulation Resistance at T

, V

= 500V 10

S

IO

9

Ω

FOD8321 — 2.5A Output Current, Gate Drive Optocoupler in Optoplanar

®

Wide Body SOP 5-Pin

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8321 Rev. 1.0.4 3

FOD8321 — 2.5A Output Current, Gate Drive Optocoupler in Optoplanar

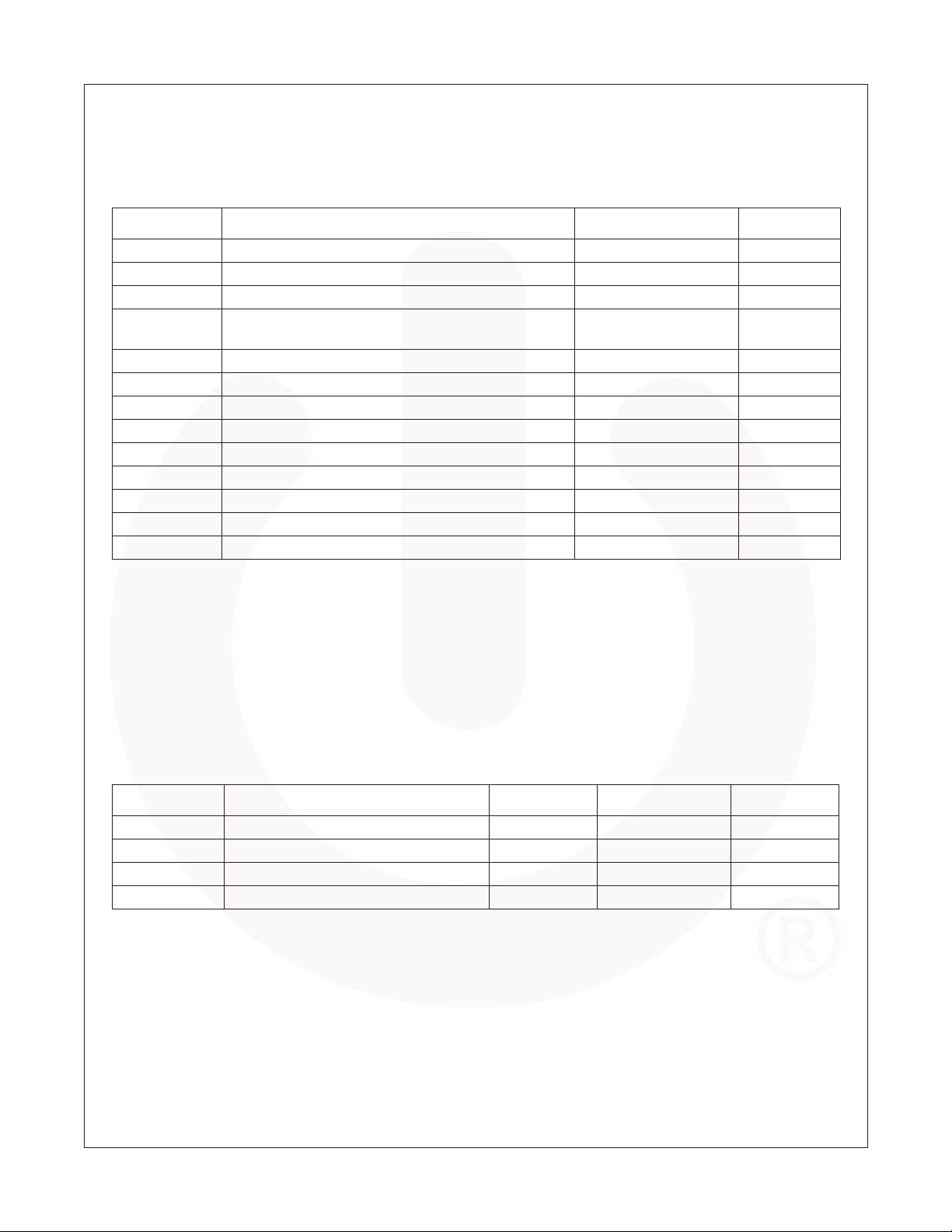

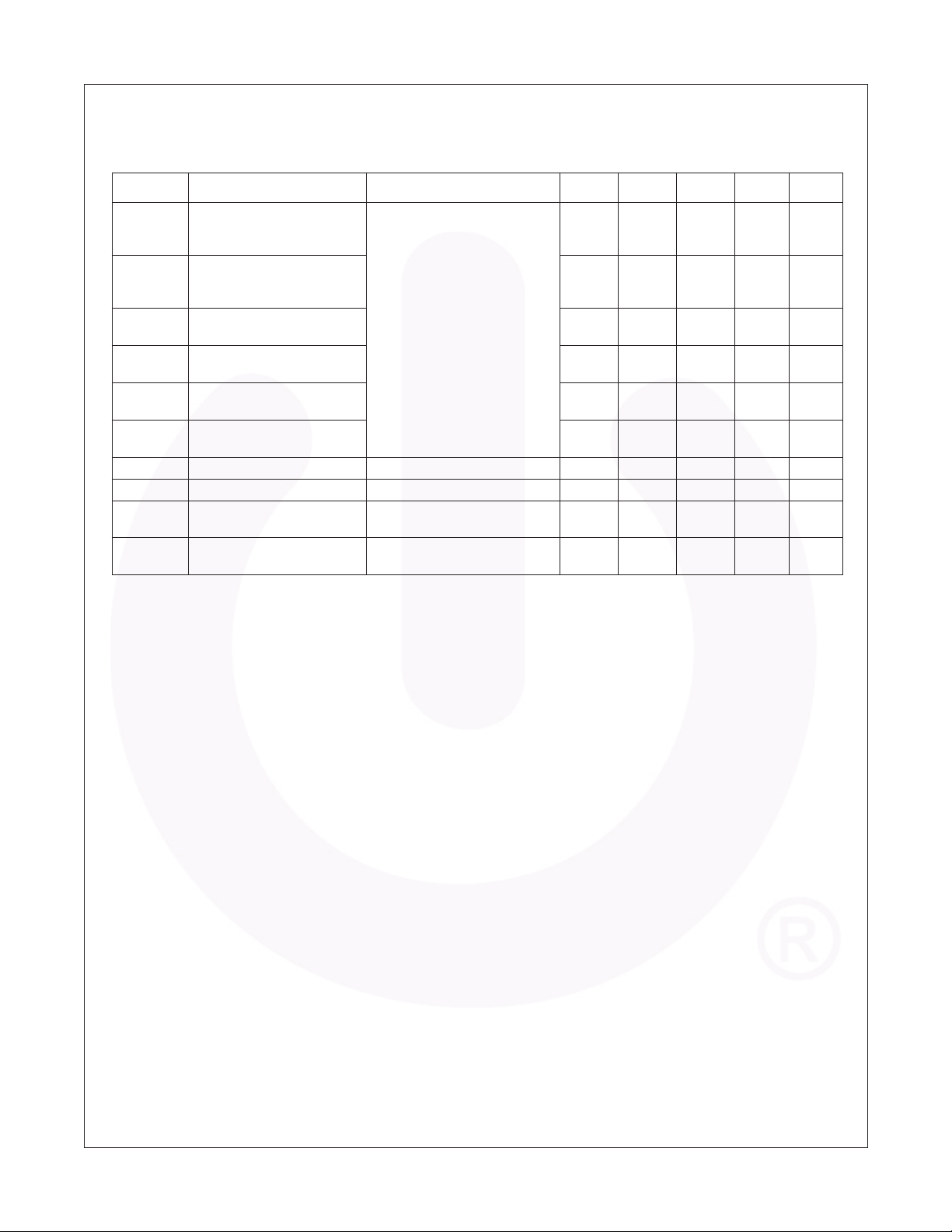

Absolute Maximum Ratings

(T

= 25ºC unless otherwise specified)

A

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Value Units

T

STG

T

OPR

T

J

T

SOL

I

F(AVG)

F

V

R

I

O(PEAK)

V

DD

V

O(PEAK)

, t

t

R(IN)

F(IN)

PD

I

PD

O

Notes:

1. Maximum pulse width = 10µs, maximum duty cycle = 0.2%.

2.

No derating required across operating temperature range.

3.

Derate linearly from 25°C at a rate of 5.2mW/°C

4.

Functional operation under these conditions is not implied. Permanent damage may occur if the device is subjected

to conditions outside these ratings.

Storage Temperature

Operating Temperature

Junction Temperature

Lead Solder Temperature (Refer to Reflow Temperature

Profile)

Average Input Current

Operating Frequency

Reverse Input Voltage

Peak Output Current

(1)

Supply Voltage

Peak Output Voltage

Input Signal Rise and Fall Time

Input Power Dissipation

Output Power Dissipation

(2)(4)

(3)(4)

-40 to +125 °C

-40 to +100 °C

-40 to +125 °C

260 for 10 sec °C

25 mA

50 kHz

5.0 V

3.0 A

0 to 35 V

0 to V

DD

V

500 ns

45 mW

500 mW

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to absolute maximum ratings.

Symbol Parameter Min. Max. Unit

V

T

– V

DD

I

F(ON)

V

F(OFF)

A

Ambient Operating Temperature

Supply Voltage

SS

Input Current (ON)

Input Voltage (OFF)

-40 100 °C

16 30 V

10 16 mA

0 0.8 V

®

Wide Body SOP 5-Pin

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8321 Rev. 1.0.4 4

Isolation Characteristics

Apply over all recommended conditions, typical value is measured at T

Symbol Parameter Conditions Min. Typ. Max. Units

= 25ºC

A

≤

Ω

FOD8321 — 2.5A Output Current, Gate Drive Optocoupler in Optoplanar

V

ISO

R

ISO

C

ISO

Input-Output Isolation

Voltage

Isolation Resistance V

Isolation Capacitance V

T

= 25ºC, R.H. < 50%, t = 1.0min,

A

I

20µA, 50Hz

I-O

= 500V

I-O

= 0V, Freq = 1.0MHz

I-O

(5)(6)

(5)

(6)

5,000 V

11

10

1pF

Notes:

5. Device is considered a two terminal device: Pins 1 and 3 are shorted together and Pins 4, 5 and 6 are shorted

together.

6. 5,000 VAC

for 1 minute duration is equivalent to 6,000 VAC

RMS

for 1 second duration.

RMS

Electrical Characteristics

Apply over all recommended conditions, typical value is measured at V

otherwise specified.

Symbol Parameter Conditions Min. Typ. Max. Units Figure

V

F

Δ(VF / TA) Temperature Coefficient of

BV

C

IN

I

OH

I

OL

V

OH

V

OL

I

DDH

I

DDL

I

FLH

V

FHL

V

UVLO+

V

UVLO-

UVLO

Input Forward Voltage IF = 10mA 1.1 1.5 1.8 V 16

Forward Voltage

Input Reverse Breakdown

R

Voltage

Input Capacitance f = 1MHz, VF = 0V 60 pF

High Level Output

(1)

Current

Low Level Output

(1)

Current

High Level Output

(7)(8)

Voltage

Low Level Output

(7)(8)

Voltage

High Level Supply Current VO Open, IF = 10 to 16mA 2.9 5 mA 7, 8, 22

Low Level Supply Current VO Open, VF = 0 to 0.8V 2.8 5 mA 7, 8, 23

Threshold Input Current

Low to High

Threshold Input Voltage

High to Low

UnderVoltage Lockout

Threshold

UnderVoltage Lockout

HYS

Threshold Hysteresis

IR = 10µA 5 V

V

= VDD – 3V 1.0 2.0 2.5 A 1, 3

OH

V

= VDD – 6V 2.0 2.5 A 1, 3, 19

OH

V

= V

OL

V

OL

IF = 10mA, IO = -2.5A VDD – 6.25 VDD – 2.5 V 1

IF = 10mA, IO = -100mA VDD – 0.5 VDD – 0.1 V 1, 2, 20

IF = 10mA, IO = 2.5A VSS + 2.5 VSS + 6.25 V 4

IF = 0mA, IO = 100mA VSS + 0.1 VSS + 0.5 V 5, 21

IO = 0mA, VO > 5V 2.4 7.5 mA 9, 15, 24

IO = 0mA, VO < 5V 0.8 V 25

IF = 10mA, VO > 5V 11.5 12.7 14.5 V 17, 26

IF = 10mA, VO < 5V 10.0 11.2 13.0 V 17, 26

+ 3V 1.0 2.0 2.5 A 4, 6

SS

= VSS+ 6V 2.0 2.5 A 4, 6, 18

= 30V, V

DD

= Ground, T

SS

-1.8 mV/°C

1.5 V

= 25°C unless

A

RMS

®

Wide Body SOP 5-Pin

Notes:

7. In this test, V

as I

approaches zero amps.

OH

is measured with a dc load current of 100mA. When driving capacitive load V

OH

will approach V

OH

DD

8. Maximum pulse width = 1ms, maximum duty cycle = 20%.

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8321 Rev. 1.0.4 5

Switching Characteristics

Apply over all recommended conditions, typical value is measured at VDD = 30V, VSS = Ground, TA = 25°C unless

otherwise specified.

Symbol Parameter Conditions Min. Typ. Max. Units Figure

t

PHL

t

PLH

PWD Pulse Width Distortion

PDD

(Skew)

t

t

t

ULVO ON

t

ULVO OFF

|CMH| Common Mode Transient

|CML| Common Mode Transient

Propagation Delay Time to

Logic Low Output

Propagation Delay Time to

Logic High Output

|t

– t

PHL

PLH

Propagation Delay Difference

Between Any Two Parts

Output Rise Time

R

(10% to 90%)

Output Fall Time

F

(90% to 10%)

ULVO Turn On Delay IF = 10mA, VO > 5V 0.8 µs

ULVO Turn Off Delay IF = 10mA, VO < 5V 0.4 µs

Immunity at Output High

Immunity at Output Low

(9)

(10)

(11)

|

(12)

IF = 10mA to 16mA, Rg = 10Ω,

Cg =10nF, f = 10kHz,

Duty Cycle = 50%

TA = 25°C, VDD = 30V,

IF = 10 to 16mA, VCM = 2000V

TA = 25°C, VDD = 30V, VF = 0V,

VCM = 2000V

(14)

100 285 500 ns 10, 11,

100 260 500 ns 10, 11,

25 300 ns

-350 350

60 ns 27

60 ns 27

20 50 kV/µs 28

(13)

20 50 kV/µs 28

12, 13,

14, 27

12, 13,

14, 27

FOD8321 — 2.5A Output Current, Gate Drive Optocoupler in Optoplanar

Notes:

9. t

10. t

11. PWD is defined as | t

12. The difference between t

propagation delay is measured from the 50% level on the falling edge of the input pulse to the 50% level of the

PHL

falling edge of the V

propagation delay is measured from the 50% level on the rising edge of the input pulse to the 50% level of the

PLH

rising edge of the V

signal.

O

signal.

O

PHL

– t

| for any given device.

PLH

PHL

and t

between any two FOD8321 parts under same operating conditions, with equal

PLH

loads.

13. Common mode transient immunity at output high is the maximum tolerable negative dVcm/dt on the trailing edge of

the common mode impulse signal, Vcm, to assure that the output will remain high (i.e. V

> 15.0V).

O

14. Common mode transient immunity at output low is the maximum tolerable positive dVcm/dt on the leading edge of

the common pulse signal, Vcm, to assure that the output will remain low (i.e. V

< 1.0V).

O

®

Wide Body SOP 5-Pin

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8321 Rev. 1.0.4 6

Loading...

Loading...