Fairchild FOD8012 service manual

FOD8012 — High CMR, Bi-Directional, Logic Gate Optocoupler

November 2010

FOD8012

High CMR, Bi-Directional, Logic Gate Optocoupler

Features

■

Full Duplex, Bi-Directional

20kV/µs Minimum Common Mode Rejection

■

■

High Speed:

– 15Mbit/sec Data Rate (NRZ)

– 60ns max. Propagation Delay , and opti– 15ns max. Pulse Width Distortion

– 30ns max. Propagation Delay Skew

3.3V and 5V CMOS Compatibility

■

■

Extended industrial temperate range, -40 to +110˚C

temperature range

■

Safety and regulatory approvals

– UL1577, 3750 VAC

– DIN EN/IEC60747-5-2 (approval pending)

RMS

for 1 min.

Applications

■

Industrial fieldbus communications

– DeviceNet, CAN, RS485, RS232

■

Microprocessor System Interface

2

– SPI, I

■

Programmable Logic Control

Isolated Data Acquisition System

■

■

Voltage Level Translator

C

Description

The FOD8012 is a full duplex, bi-directional, high-speed

logic gate Optocoupler, which supports isolated communications allowing digital signals to communicate

between systems without conducting ground loops or

hazardous voltages. It utilizes Fairchild’s proprietary co-

planar packaging technology, Optoplanar

IC design to achieve minimum 20kV/µs Common Mode

Noise Rejection (CMR) rating.

This high-speed logic gate optocoupler is highly integrated with 2 optically coupled channels arranged in

bi-directional configuration, and housed in a compact

8-pin small outline package. Each optocoupler channel

consists of a high-speed AlGaAs LED driven by a CMOS

buffer IC coupled to a CMOS detector IC. The detector

IC comprises of an integrated photodiode, a high-speed

trans-impedance amplifier and a voltage comparator

with an output driver. The CMOS technology coupled to

the high efficiency of the LED achieves low power consumption as well as very high speed (60ns propagation

delay, 15ns pulse width distortion).

®

Related Resources

■

FOD8001, High Noise Immunity, 3.3V/5V Logic Gate

Optocoupler Datasheet

■

www.fairchildsemi.com/products/opto/

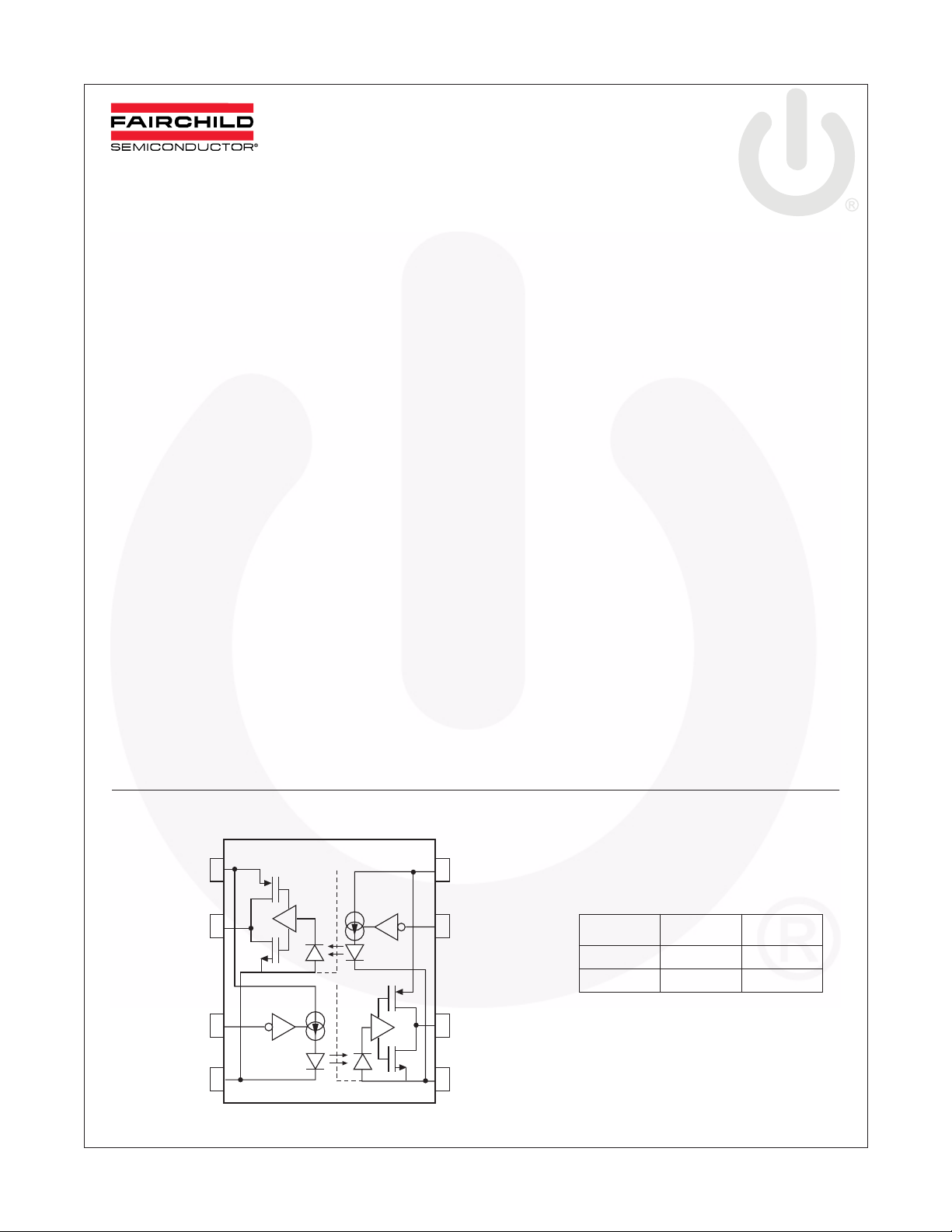

Functional Schematic

1

V

DD1

V

2

OA

V

3

INB

GND

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8012 Rev. 1.0.5

45

1

0.1µF bypass capacitor required from V

8

7

6

V

DD2

V

INA

V

OB

GND

to GND

DD

Truth Table

VIN LED VO

High OFF

Low ON

2

High

Low

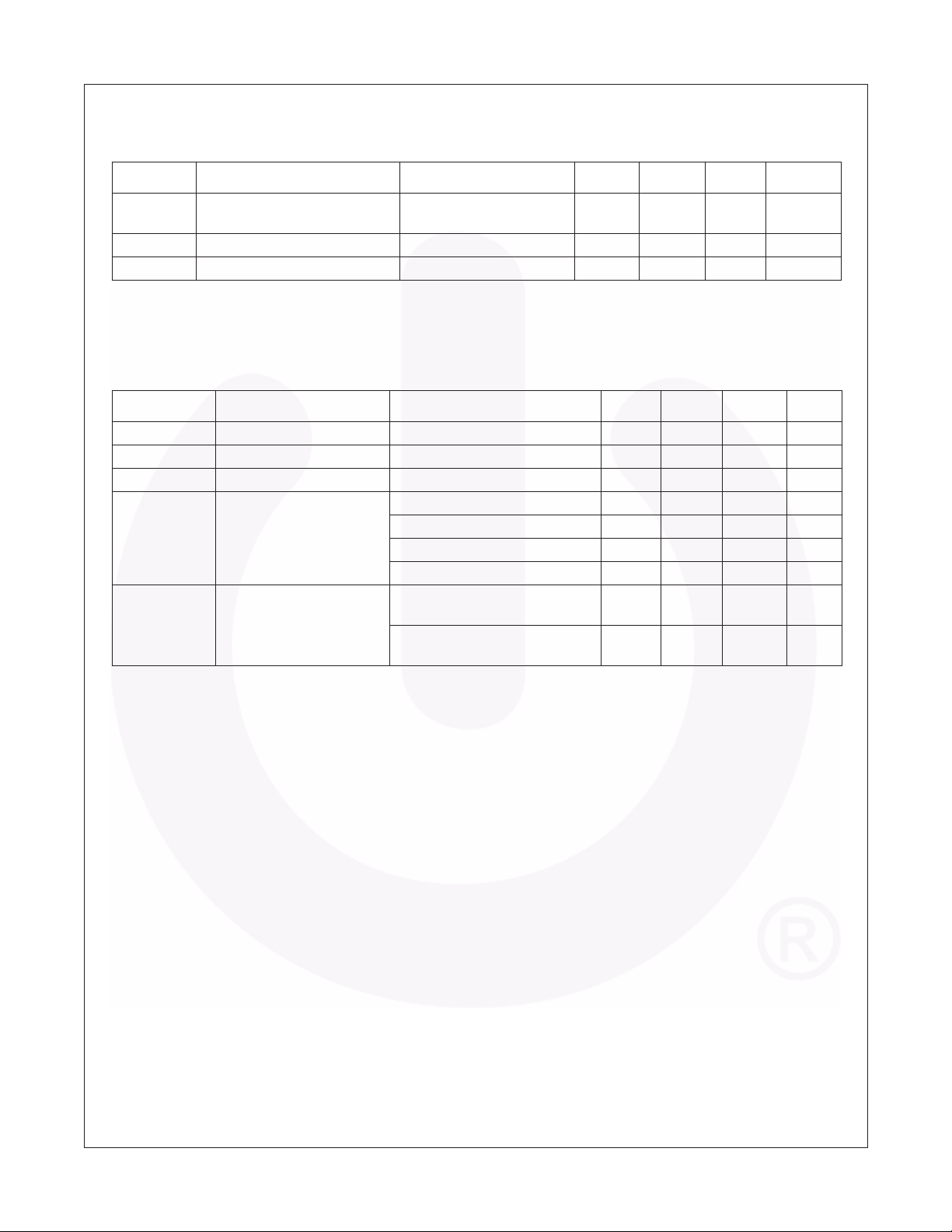

Pin Definitions

FOD8012 — High CMR, Bi-Directional, Logic Gate Optocoupler

Pin

Number

1V

2V

3V

4 GND

5 GND

6V

7V

8V

Absolute Maximum Ratings

Pin

Name Description

DD1

OA

INB

OB

INA

DD2

Supply V oltage to Channel-A detector IC and Channel-B buffer IC

Output V oltage from Channel-A detector IC

Input V oltage to Channel-B buffer IC

Ground for Channel-A detector IC and Channel-B buffer IC

1

Ground for Channel-A buffer IC and Channel-B detector IC

2

Output V oltage from Channel-B detector IC

Input V oltage to Channel-A buffer IC

Supply V oltage to Channel-A buffer IC and Channel-B detector IC

(T

=25ºC unless otherwise specified)

A

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Value Units

V

DD1

V

V

I

T

T

T

I

OA

OA

OPR

T

IA

IA

PD

PD

STG

J

SOL

, V

, V

, I

, V

, I

DD2

IB

IB

OB

OB

I

O

Storage Temperature -40 to +125 ºC

Operating Temperature -40 to +110 ºC

Junction Temperature -40 to +130 ºC

Lead Solder Temperature

260 for 10sec ºC

(Refer to Reflow Temperature Profile)

Supply Voltage 0 to 6.0 V

Input Voltage -0.5 to VDD+0.5 V

Input DC Current -10 to +10 µA

Output Voltage -0.5 to VDD+0.5 V

Average Output Current 10 mA

Input Power Dissipation

Output Power Dissipation

(1)

(1)

60 mW

60 mW

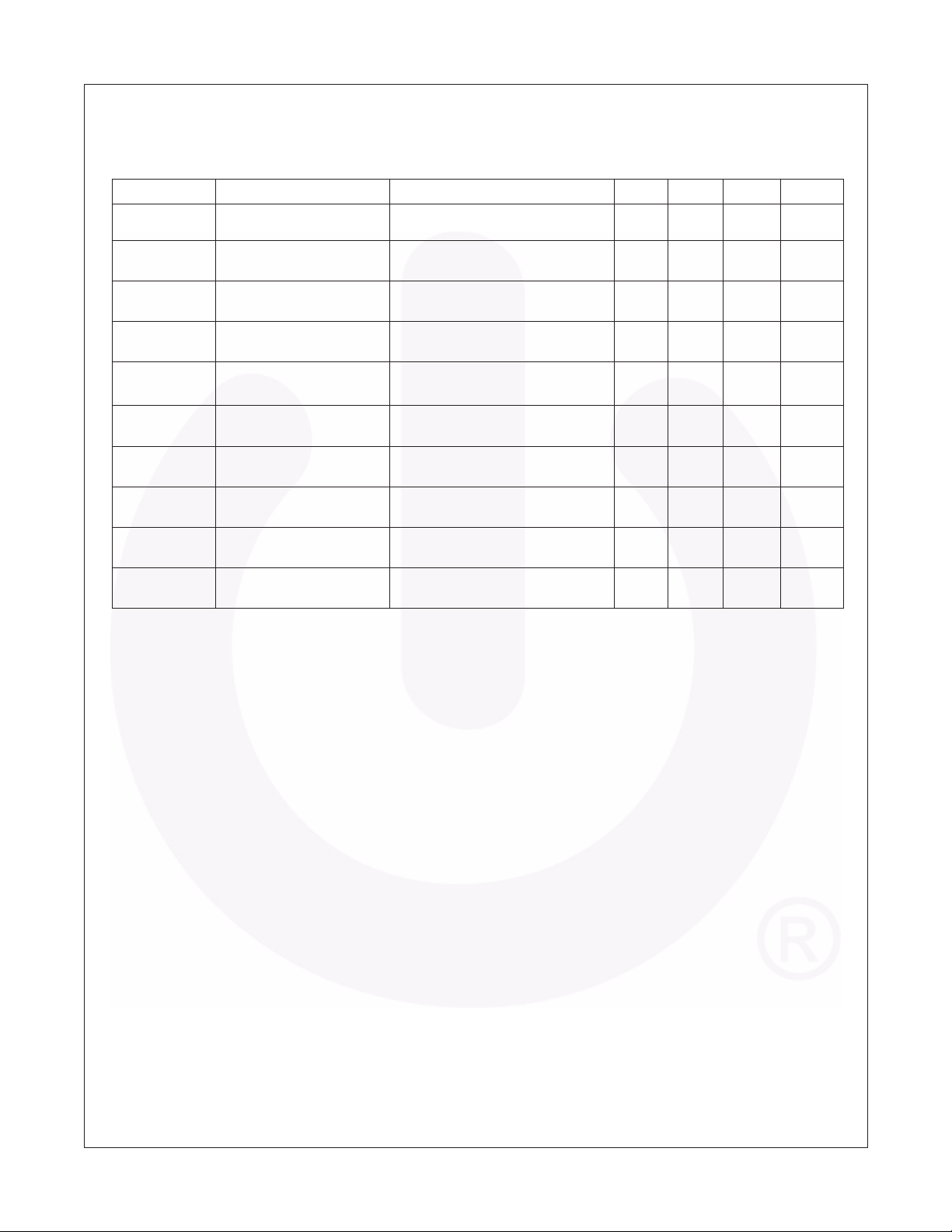

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol Parameter Min. Max. Unit

T

A

V

, V

DD1

V

IH

V

IL

t

, t

r

f

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8012 Rev. 1.0.5 2

Ambient Operating Temperature

Supply Voltages (3.3V Operation)

DD2

Supply Voltages (5.0V Operation)

Logic High Input Voltage

Logic Low Input Voltage

Input Signal Rise and Fall Time

(2)

(2)

-40 +110 ºC

3.0 3.6 V

4.5 5.5 V

2.0

V

DD

0 0.8 V

1.0 ms

V

Isolation Characteristics

Apply over all recommended conditions, typical value is measured at T

Symbol Parameter Conditions Min. Typ. Max. Units

= 25ºC

A

FOD8012 — High CMR, Bi-Directional, Logic Gate Optocoupler

V

ISO

R

ISO

C

ISO

Input-Output Isolation Voltage freq = 60Hz, t = 1.0min,

I

I-O

Isolation Resistance V

Isolation Capacitance V

I-O

I-O

(3)(4)

≤

10µA

= 500V

(3)

= 0V, freq = 1.0MHz

3750 Vac

11

10

(3)

0.2 pF

Electrical Characteristics

T

= -40ºC to +110ºC, 3.0V

A

Apply over all recommended conditions, typical value is measured at V

Symbol Parameter Conditions Min. Typ. Max. Units

I

DD1L

I

DD1H

, I

DD2L

, I

DD2H

I

, I

IA

IB

V

OH

V

OL

Logic Low Supply Current V

Logic High Supply Current V

Input Current

Logic High Output Voltage I

Logic Low Output Voltage I

≤

V

≤

5.5V, unless otherwise specified.

DD

, V

= 0V

IA

IB

, V

= V

IA

IB

DD

DD1

= V

= +3.3V, T

DD2

= 25ºC

A

5.8 8.0 mA

2.5 4.0 mA

-10 +10 µA

= –20µA, V

O

I

= –4mA, V

O

I

= –20µA, V

O

I

= –4mA, V

O

= 20µA, V

O

V

= V

I

= 4mA, VDD = 3.3V or 5V,

I

O

V

= V

I

DD

= 3.3V, V

DD

= 3.3V, V

DD

= 5V, V

= 5V, V

DD

= 3.3V or 5V,

DD

IL

= V

I

= V

I

= V

I

= V

I

3.2 3.3 V

IH

3.0 3.1 V

IH

IH

IH

4.9 5.0 V

4.7 4.8 V

0 0.1 V

0.26 0.6 V

IL

RMS

Ω

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8012 Rev. 1.0.5 3

Switching Characteristics

T

= -40ºC to +110ºC, 3.0V ≤ VDD ≤ 5.5V, unless otherwise specified.

A

Apply over all recommended conditions, typical value is measured at V

Symbol Parameter Conditions Min. Typ. Max. Units

Data Rate 15 Mbit/s

DD1

= V

= +3.3V, TA=25ºC

DD2

FOD8012 — High CMR, Bi-Directional, Logic Gate Optocoupler

t

PHL

Propagation Delay Time

PW = 66.7ns, CL = 15pF 37 60 ns

to Logic Low Output

t

PLH

Propagation Delay Time

PW = 66.7ns, CL = 15pF 40 60 ns

to Logic High Output

PWD Pulse Width Distortion,

| t

– t

PLH

|

t

PSK(CC)

t

PSK(PP)

t

R

PHL

Channel-Channel Skew PW = 66.7ns, CL = 15pF

Part-Part Skew PW = 66.7ns, CL = 15pF

Output Rise Time

PW = 66.7ns, C

= 15pF

L

PW = 66.7ns, CL = 15pF 6.5 ns

(5)

(6)

(7)

315ns

12 25 ns

30 ns

(10% to 90%)

t

F

Output Fall Time

PW = 66.7ns, CL = 15pF 6.5 ns

(90% to 10%)

| Common Mode Transient

|CM

H

Immunity at Output High

| Common Mode Transient

|CM

L

Immunity at Output Low

VI = V

V

CM

VI = 0V, VO < 0.8V,

V

CM

, VO > 0.8V

DD1

= 1000V

= 1000V

(8)

(8)

DD1

,

20 40 kV/µs

20 40 kV/µs

Notes:

1. No derating required.

2. 0.1µF bypass capacitor must be connected between Pin 1 and 4, and 5 and 8. The capacitors should be kept close

to the supply pins.

3. Device is considered a two terminal device: Pins 1, 2, 3 and 4 are shorted together and Pins 5, 6, 7 and 8 are shorted

together.

4. 3,750 VAC

for 1 minute duration is equivalent to 4,500 VAC

RMS

5. PWD is equal to the magnitude of the worst case difference in t

for 1 second duration.

RMS

PHL

and/or t

that will be seen for one channel

PLH

switching, while holding the other channel output at a low or high state, or while both channels are in synchronous

data transmission mode.

6. t

is equal to the magnitude of the worst case difference in t

PSK(CC)

PHL

and/or t

that will be seen between the two

PLH

channels within a single device.

7. t

is equal to the magnitude of the worst case difference in t

PSK(PP)

PHL

and/or t

that will be seen between any two

PLH

units from the same manufacturing date code that are operated at same case temperature, at same operating

conditions, with equal loads.

8. Common mode transient immunity at output high is the maximum tolerable positive dVcm/dt on the leading edge of

the common mode impulse signal, Vcm, to assure that the output will remain high. Common mode transient

immunity at output low is the maximum tolerable negative dVcm/dt on the trailing edge of the common pulse signal,

Vcm, to assure that the output will remain low.

©2010 Fairchild Semiconductor Corporation www.fairchildsemi.com

FOD8012 Rev. 1.0.5 4

Loading...

Loading...