FDMS3602S

Q

Q

G1

D1

D1

D1

G2

S2

S2

S2

D1

PHASE

(S1/D2)

S2

S2

S2

G2

D1

D1

D1

G1

PHASE

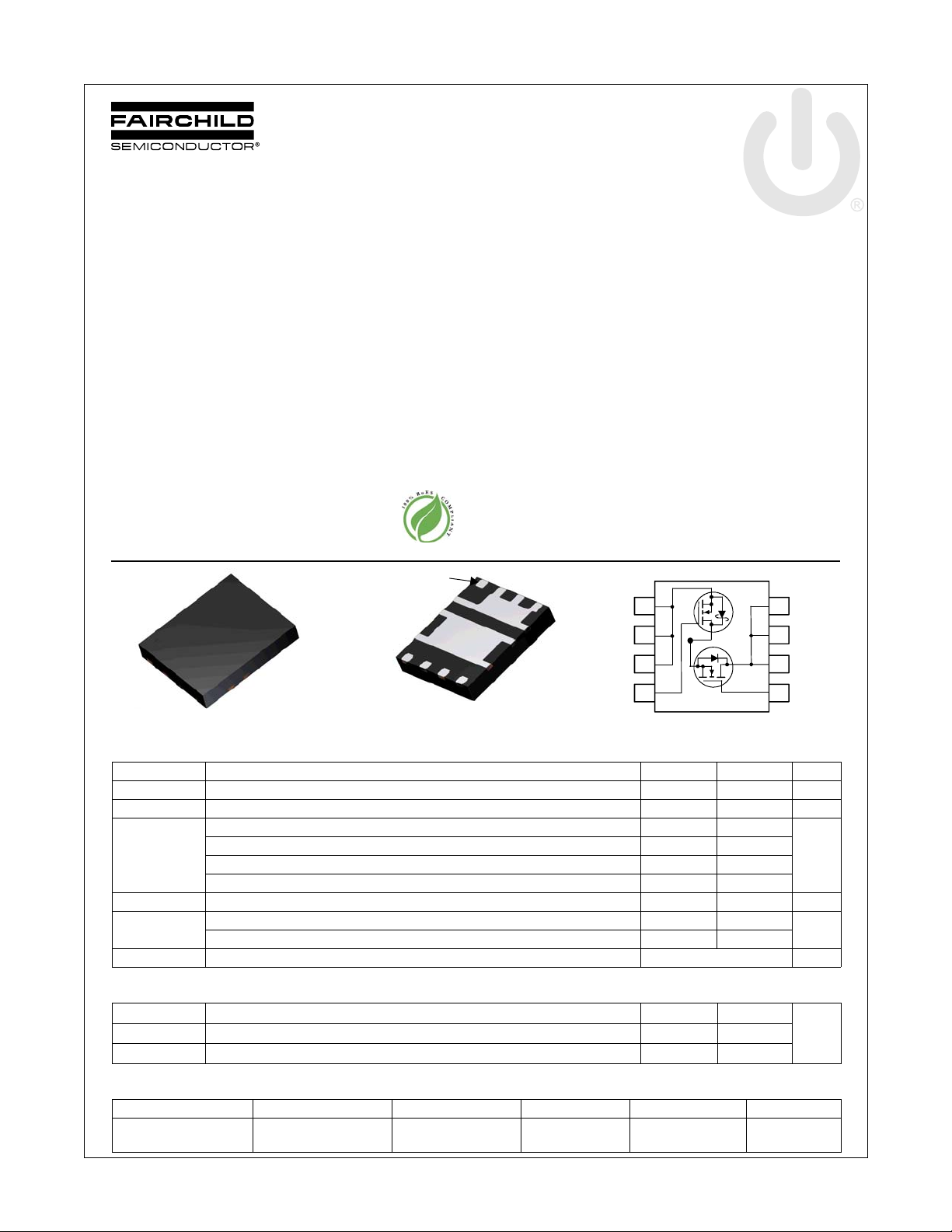

Power 56

Top Bottom

Pin 1

PowerTrench® Power Stage

25 V Asymmetric Dual N-Channel MOSFET

FDMS3602S PowerTrench

August 2011

Features

Q1: N-Channel

Max r

Max r

Q2: N-Channel

Max r

Max r

Low inductance packaging shortens rise/fall times, resulting in

lower switching losses

MOSFET integration enables optimum layout for lower circuit

inductance and reduced switch node ringing

RoHS Compliant

= 5.6 mΩ at VGS = 10 V, ID = 15 A

DS(on)

= 8.1 mΩ at VGS = 4.5 V, ID = 14 A

DS(on)

= 2.2 mΩ at VGS = 10 V, ID = 26 A

DS(on)

= 3.4 mΩ at VGS = 4.5 V, ID = 22 A

DS(on)

General Description

This device includes two specialized N-Channel MOSFETs in a

dual PQFN package. The switch node has been internally

connected to enable easy placement and routing of synchronous

buck converters. The control MOSFET (Q1) and synchronous

SyncFET (Q2) have been designed to provide optimal power

efficiency.

Applications

Computing

Communications

General Purpose Point of Load

Notebook VCORE

Server

2

5

6

7

8

4

3

2

1

1

®

Power Stage

MOSFET Maximum Ratings T

Symbol Parameter Q1 Q2 Units

V

DS

V

GS

I

D

E

AS

P

D

TJ, T

STG

Drain to Source Voltage 25 25 V

Gate to Source Voltage (Note 3) ±20 ±20 V

Drain Current -Continuous (Package limited) TC = 25 °C 30 40

-Continuous (Silicon limited) T

-Continuous T

-Pulsed 40 100

Single Pulse Avalanche Energy 50

Power Dissipation for Single Operation TA = 25°C 2.2

Power Dissipation for Single Operation T

Operating and Storage Junction Temperature Range -55 to +150 °C

= 25°C unless otherwise noted

A

= 25 °C 65 135

C

= 25 °C 15

A

= 25°C 1.0

A

1a

4

1a

1c

26

144

2.5

1.0

1b

5

1b

1d

A

mJ

W

Thermal Characteristics

R

θJA

θJA

R

θJC

Package Marking and Ordering Information

©2011 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDMS3602S Rev.C5

Device Marking Device Package Reel Size Tape Width Quantity

Thermal Resistance, Junction to Ambient 57

Thermal Resistance, Junction to Ambient 125

Thermal Resistance, Junction to Case 3.5 2

22OA

N7OC

FDMS3602S Power 56 13” 12

1a

1c

mm 3000 units

50

120

1b

1d

°C/WR

FDMS3602S PowerTrench

Electrical Characteristics T

= 25°C unless otherwise noted

J

Symbol Parameter Test Conditions Type Min Typ Max Units

Off Characteristics

BV

ΔBV

ΔT

I

DSS

I

GSS

DSS

DSS

J

Drain to Source Breakdown Voltage

Breakdown Voltage Temperature

Coefficient

Zero Gate Voltage Drain Current V

Gate to Source Leakage Current,

Forward

= 250 μA, VGS = 0 V

D

I

= 1 mA, VGS = 0 V

D

I

= 250 μA, referenced to 25°C

D

I

= 10 mA, referenced to 25°C

D

= 20 V, V

DS

V

= 20 V, V

GS

GS

DS

= 0 V

= 0 V

Q1Q225

25

Q1

Q2

Q1

Q2

Q1

Q2

V

20

20

mV/°C

1

500

100

100nAnA

I

On Characteristics

V

V

GS(th)

ΔV

ΔT

r

DS(on)

g

FS

GS(th)

J

Gate to Source Threshold Voltage

Gate to Source Threshold Voltage

Temperature Coefficient

Static Drain to Source On Resistance

Forward Transconductance

= VDS, I

GS

V

= VDS, I

GS

I

= 250 μA, referenced to 25°C

D

I

= 10 mA, referenced to 25°C

D

= 10 V, ID = 15 A

V

GS

V

= 4.5 V, ID = 14 A

GS

V

= 10 V, ID = 15 A, T

GS

V

= 10 V, ID = 26 A

GS

V

= 4.5 V, ID = 22 A

GS

V

= 10 V, ID = 26 A, T

GS

V

= 5 V, ID = 15 A

DD

V

= 5 V, ID = 26 A

DD

= 250 μA

D

= 1 mA

D

= 125°C

J

= 125°C

J

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

1

1.8

1

1.9

-6

-5

4.4

6.2

5.9

1.7

2.6

2.5

3

3

mV/°C

5.6

8.1

8.7

2.2

3.4

3.9

67

132

μA

V

mΩ

S

®

Power Stage

Dynamic Characteristics

C

iss

C

oss

C

rss

R

g

Input Capacitance

Output Capacitance

Reverse Transfer Capacitance

Gate Resistance

Switching Characteristics

t

d(on)

t

r

t

d(off)

t

f

Q

g(TOT)

Q

g(TOT)

Q

gs

Q

gd

Turn-On Delay Time

Rise Time

Turn-Off Delay Time

Fall Time

Total Gate Charge V

Total Gate Charge V

Gate to Source Charge

Gate to Drain “Miller” Charge

1264

Q1

= 13 V, VGS = 0 V, f = 1 MHZ

V

DS

Q2

= 13 V, VGS = 0 V, f = 1 MHZ

V

DS

Q1

Q2

Q1

Q2

Q1

Q2

Q1Q20.2

0.2

1680

3097

4120

340

450

847

1130

58

13890210

0.6

0.9

pF

pF

pF

2

Ω

3

Q1

V

= 13 V, ID = 15 A, R

DD

Q2

V

= 13 V, ID = 26 A, R

DD

= 0V to 10 V

GS

= 0V to 4.5 V

GS

Q1

V

DD

I

= 15 A

D

Q2

V

DD

I

= 26 A

D

= 6 Ω

GEN

= 6 Ω

GEN

= 13 V,

= 13 V,

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

7.91216

22

2

4.21010

19

34

31

50

1.8

3.21010

19

27

45

64

9

13

21

30

3.9

9.1

2.4

5.3

ns

ns

ns

ns

nC

nC

nC

nC

©2011 Fairchild Semiconductor Corporation 2 www.fairchildsemi.com

FDMS3602S Rev.C5

Electrical Characteristics T

= 25°C unless otherwise noted

J

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Diode Characteristics

0.8

V

= 0 V, IS = 15 A (Note 2)

V

SD

t

rr

Q

rr

Notes:

1. R

is determined with the device mounted on a 1 in2 pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. R

θJA

by the user's board design.

Source-Drain Diode Forward Voltage

Reverse Recovery Time

Reverse Recovery Charge

GS

V

= 0 V, IS = 26 A (Note 2)

GS

Q1

I

= 15 A, di/dt = 100 A/s

F

Q2

I

= 26 A, di/dt = 300 A/s

F

Q1

Q2

Q1

Q2

Q1

Q2

is guaranteed by design while R

θJC

1.2

0.8

1.2

21

34

28

44

6.62813

44

θCA

is determined

ns

nC

FDMS3602S PowerTrench

V

®

Power Stage

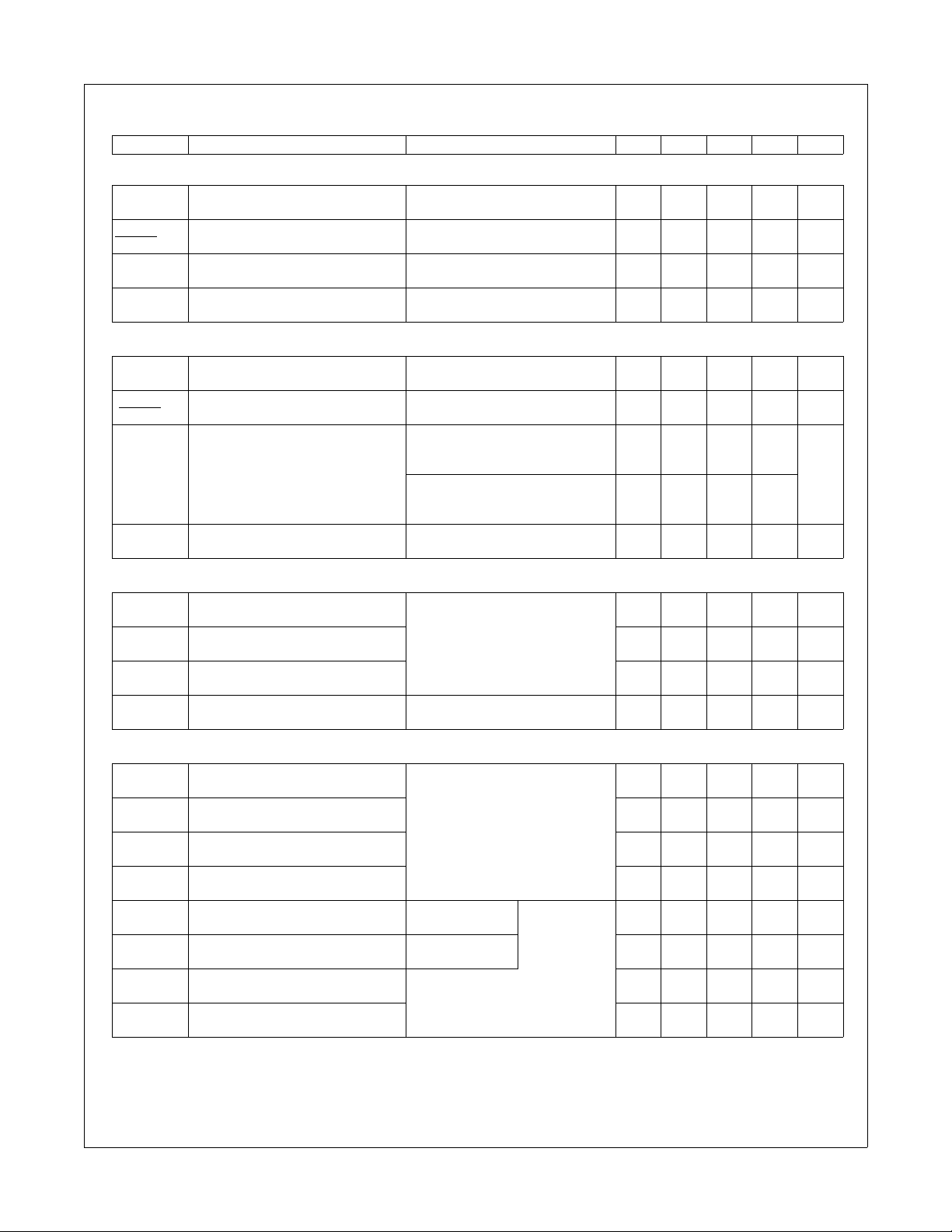

a. 57 °C/W when mounted on

a 1 in2 pad of 2 oz copper

c. 125 °C/W when mounted on a

minimum pad of 2 oz copper

2. Pulse Test: Pulse Width < 300 μs, Duty cycle < 2.0%.

3. As an N-ch device, the negative Vgs rating is for low duty cycle pulse ocurrence only. No continuous rating is implied.

4. EAS of 50 mJ is based on starting TJ = 25 oC; N-ch: L = 1 mH, IAS = 10 A, VDD = 23 V, VGS = 10 V. 100% test at L= 0.3 mH, IAS = 15 A.

5. EAS of 144 mJ is based on starting TJ = 25 oC; N-ch: L = 1 mH, IAS = 17 A, VDD = 23 V, VGS = 10 V. 100% test at L= 0.3 mH, IAS = 25 A.

b. 50 °C/W when mounted on

a 1 in2 pad of 2 oz copper

d. 120 °C/W when mounted on a

minimum pad of 2 oz copper

©2011 Fairchild Semiconductor Corporation 3 www.fairchildsemi.com

FDMS3602S Rev.C5

FDMS3602S PowerTrench

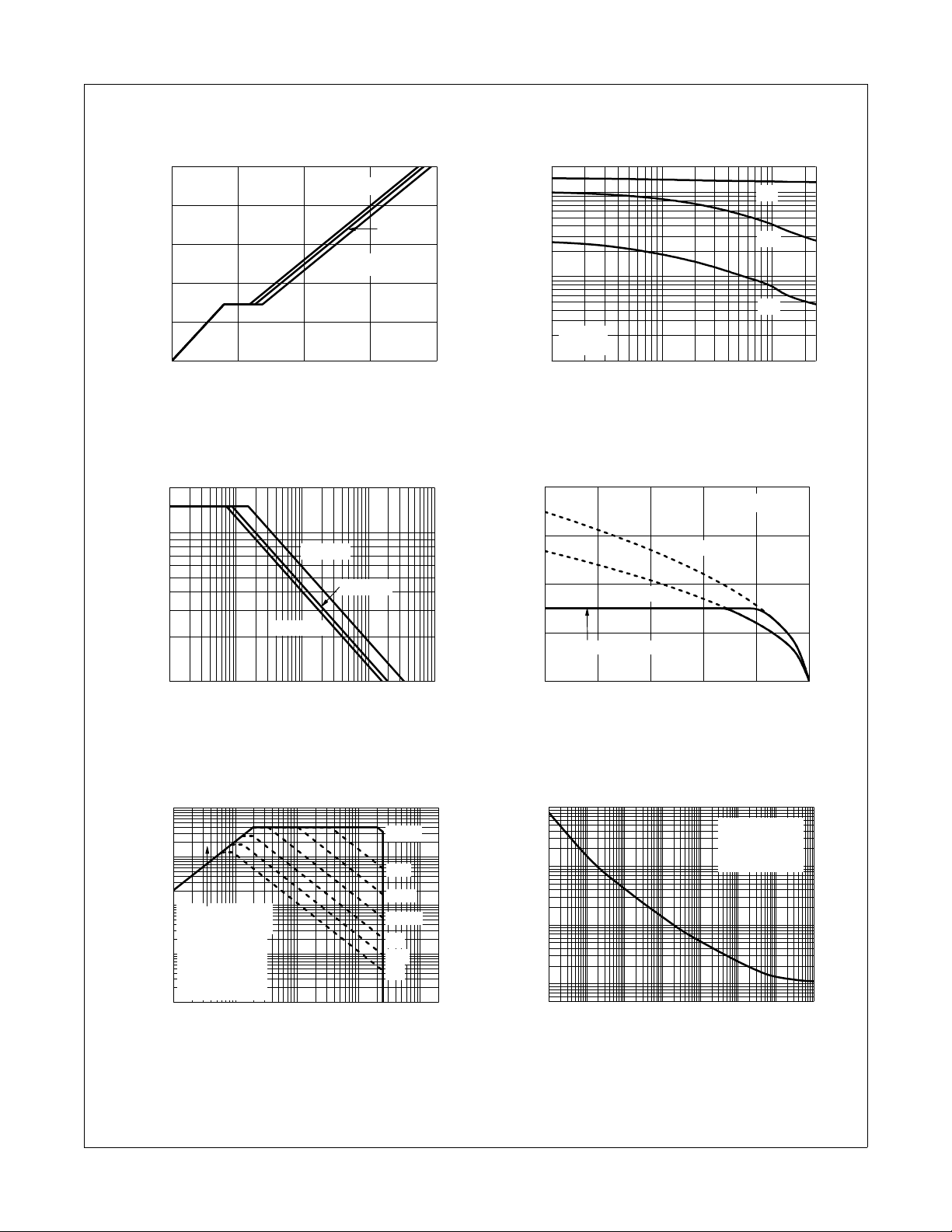

0.0 0.2 0.4 0.6 0.8 1.0

0

10

20

30

40

VGS = 4.5 V

VGS = 3.5 V

V

GS

= 3 V

VGS = 4 V

PULSE DURATION = 80 μs

DUTY CYCLE = 0.5% MAX

VGS = 10 V

I

D

, DRAIN CURRENT (A)

V

DS

, DRAIN TO SOURCE VOLTAGE (V)

0 10203040

0

1

2

3

4

5

6

VGS = 3 V

VGS = 3.5 V

PULSE DURA TION = 80 μs

DUTY CYCLE = 0.5% MAX

NORMALIZED

DRAIN TO SOURCE ON-RESISTA NCE

I

D

, DRAIN CURRENT (A)

V

GS

= 4 V

VGS = 4.5 V

V

GS

= 10 V

-75 -50 -25 0 25 50 75 100 125 150

0.6

0.8

1.0

1.2

1.4

1.6

ID = 15 A

V

GS

= 10 V

NORMALIZED

DRAIN TO SOURCE ON-RESISTANCE

T

J

, JUNCTION TE MPERATURE (

o

C)

246810

0

5

10

15

20

25

TJ = 125 oC

ID = 15 A

TJ = 25 oC

V

GS

, GATE TO SOURCE VOLTA GE (V)

r

DS(on)

,

DRAIN TO

SOURCE ON-RESISTANCE

(mΩ)

PULSE DURATION = 80 μs

DUTY CYCLE = 0.5% MAX

1234

0

10

20

30

40

TJ = 150 oC

V

DS

= 5 V

PULSE DURATION = 80 μs

DUTY CYCLE = 0.5% MAX

TJ = -55 oC

TJ = 25 oC

I

D

, DRAIN CURRENT (A)

VGS, GATE TO SOURCE VOLTAGE (V)

0.0 0.2 0.4 0.6 0.8 1.0 1.2

0.001

0.01

0.1

1

10

40

TJ = -55 oC

TJ = 25 oC

TJ = 150 oC

V

GS

= 0 V

I

S

, REVERSE DRAIN CURRENT (A)

VSD, BODY DIODE FORWARD VOLTAGE (V)

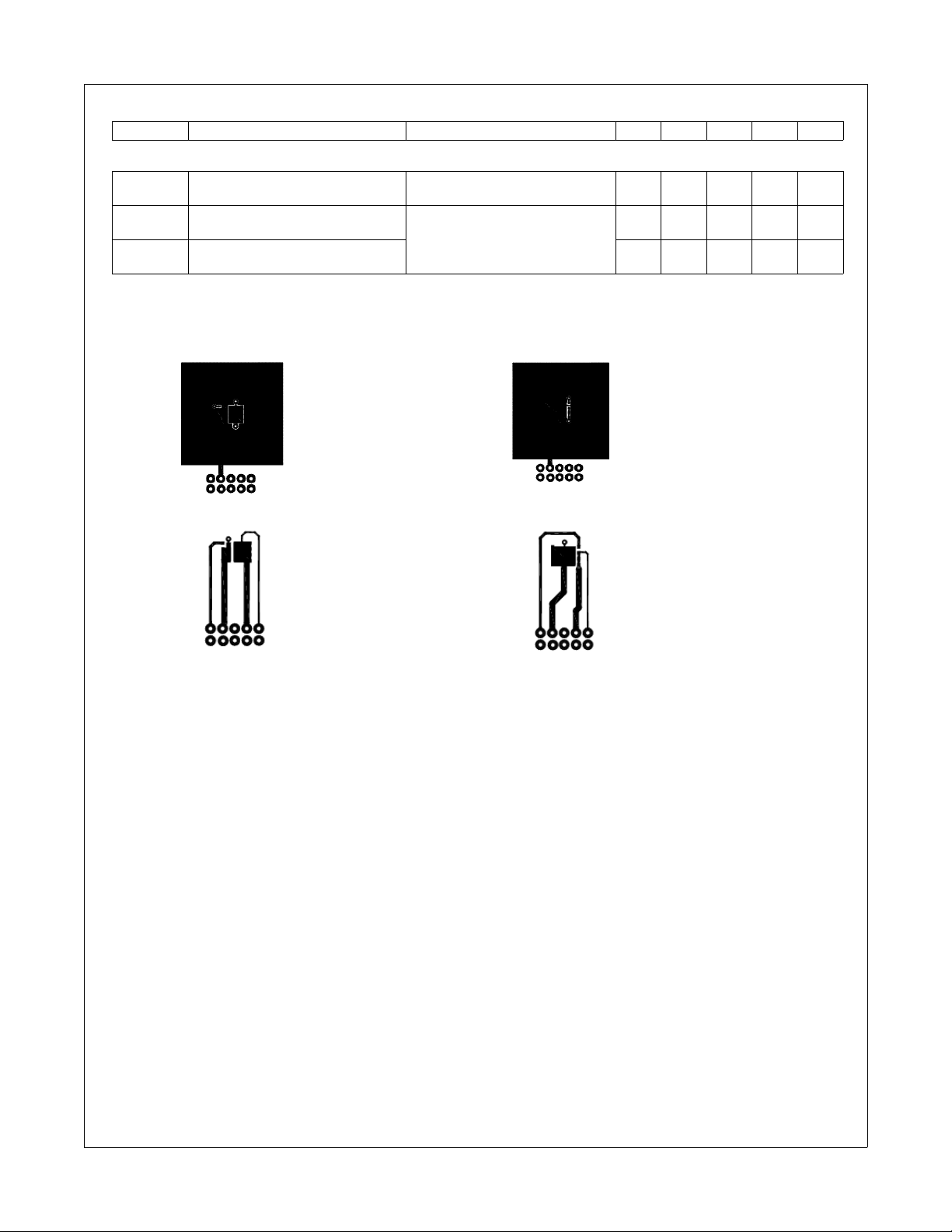

Typical Characteristics (Q1 N-Channel) T

Figure 1.

On Region Characteristics Figure 2.

= 25°C unless otherwise noted

J

Nor ma liz ed On- Res is tan ce

vs Drain Current and Gate Voltage

®

Power Stage

Fi gu re 3. No rmalized On Resistance

vs Junction Temperature

©2011 Fairchild Semiconductor Corporation 4 www.fairchildsemi.com

FDMS3602S Rev.C5

Figure 5. Transfer Characteristics

Figure 4.

On-Resistance vs Gate to

Source Voltage

Figure 6.

Source to Drain Diode

Forward Voltage vs Source Current

FDMS3602S PowerTrench

0 5 10 15 20

0

2

4

6

8

10

ID = 15 A

V

DD

= 16 V

V

DD

= 13 V

V

GS

, GATE TO SOURCE VOLTAGE (V)

Qg, GATE CHARGE (nC)

VDD = 10 V

0.1 1 10

10

100

1000

2000

25

f = 1 MHz

V

GS

= 0 V

CAPACITANCE (pF)

VDS, DRAIN TO SOURCE VOLTAGE (V)

C

rss

C

oss

C

iss

0.01 0.1 1 10 100

1

10

20

TJ = 100 oC

TJ = 25 oC

T

J

= 125

o

C

t

AV

, TIME IN AVALANCHE (ms)

I

AS

, AVALANCHE CURRENT (A)

25 50 75 100 125 150

0

20

40

60

80

Limited by Pack ag e

V

GS

= 4.5 V

R

θJC

= 3.5 oC/W

V

GS

= 10 V

I

D

, DRAIN CURRENT (A)

T

C

, CASE TEMPERATURE (

o

C)

0.01 0.1 1 10 100

0.01

0.1

1

10

100

DC

100 ms

10 ms

1 ms

1s

I

D

, DRAIN CURRENT (A)

VDS, DRAIN to SOURCE VOLTAGE (V)

THIS AREA IS

LIMITED BY r

DS(on)

SINGLE PULSE

T

J

= MAX RATED

R

θJA

= 125

o

C/W

T

A

= 25

o

C

10s

100 μs

200

10-410-310-210

-1

110

100 1000

0.5

1

10

100

1000

SINGLE PULSE

R

θJA

= 125

o

C/W

T

A

= 25

o

C

P(

PK

), PEAK TRANSIENT POWER (W)

t, PULSE WIDTH (sec)

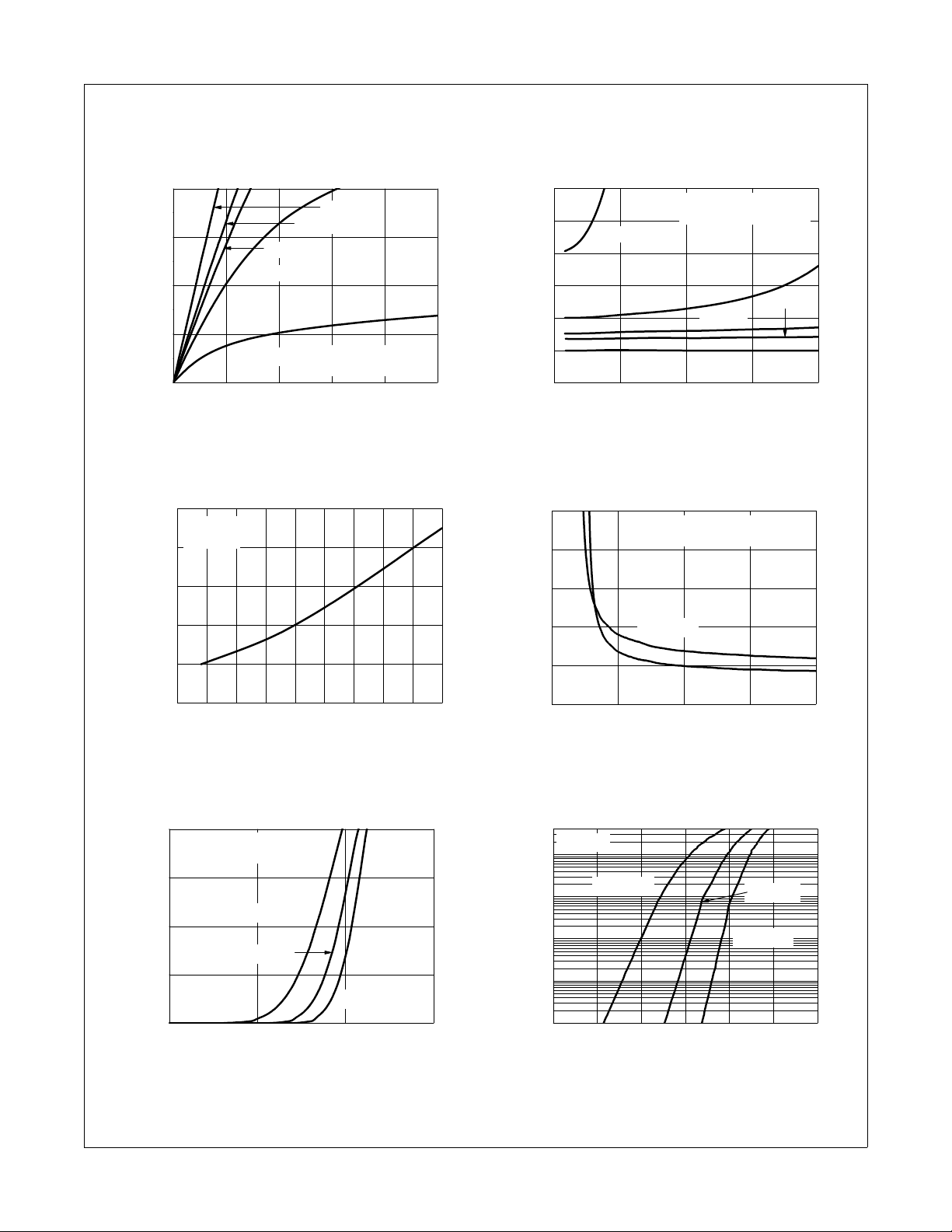

Typical Characteristics (Q1 N-Channel) T

Figure 7.

Gate Charge Characteristics Figure 8.

= 25°C unless otherwise noted

J

Cap aci tan ce v s Dr ain

to Source Voltage

®

Power Stage

Figure 9.

Unc l amp ed I n duc t iv e

Switching Capability

©2011 Fairchild Semiconductor Corporation 5 www.fairchildsemi.com

FDMS3602S Rev.C5

Figure 11. Forward Bias Safe

Op

erating Area

Figure 10.

Ma ximum Conti nuous Drain

Current vs Case Temperature

Figure 12.

Single Pu lse Maxim um

Power Dissipation

Loading...

Loading...