Fairchild FDMF6704 service manual

tm

August 2009

FDMF6704

FDMF6704 - XSTM DrMOS

The Xtra Small, High Performance, High Frequency DrMOS Module

Benefits

Ultra compact size - 6 mm x 6 mm MLP, 44 % space

saving compared to conventional MLP 8 mm x 8 mm

DrMOS packages.

Fully optimized system efficiency.

Clean voltage waveforms with reduced ringing.

High frequency operation.

Compatible with a wide variety of PWM controllers in the

market.

Features

Ultra- compact thermally enhanced 6 mm x 6 mm MLP

package 84 % smaller than conventional discrete solutions.

Synchronous driver plus FET multichip module.

High current handling of 35 A.

Over 93 % peak efficiency.

Tri-State PWM input.

Fairchild's PowerTrench® 5 technology MOSFETs for clean

voltage waveforms and reduced ringing.

Optimized for high switching frequencies of up to 1 MHz.

Skip mode SMOD [low side gate turn off] input.

Fairchild SyncFETTM [integrated Schottky diode] technology

in the low side MOSFET.

Integrated bootstrap Schottky diode.

Adaptive gate drive timing for shoot-through protection.

Driver output disable function [DISB# pin].

Undervoltage lockout (UVLO).

Fairchild Green Packaging and RoHS

compliant. Low profile SMD package.

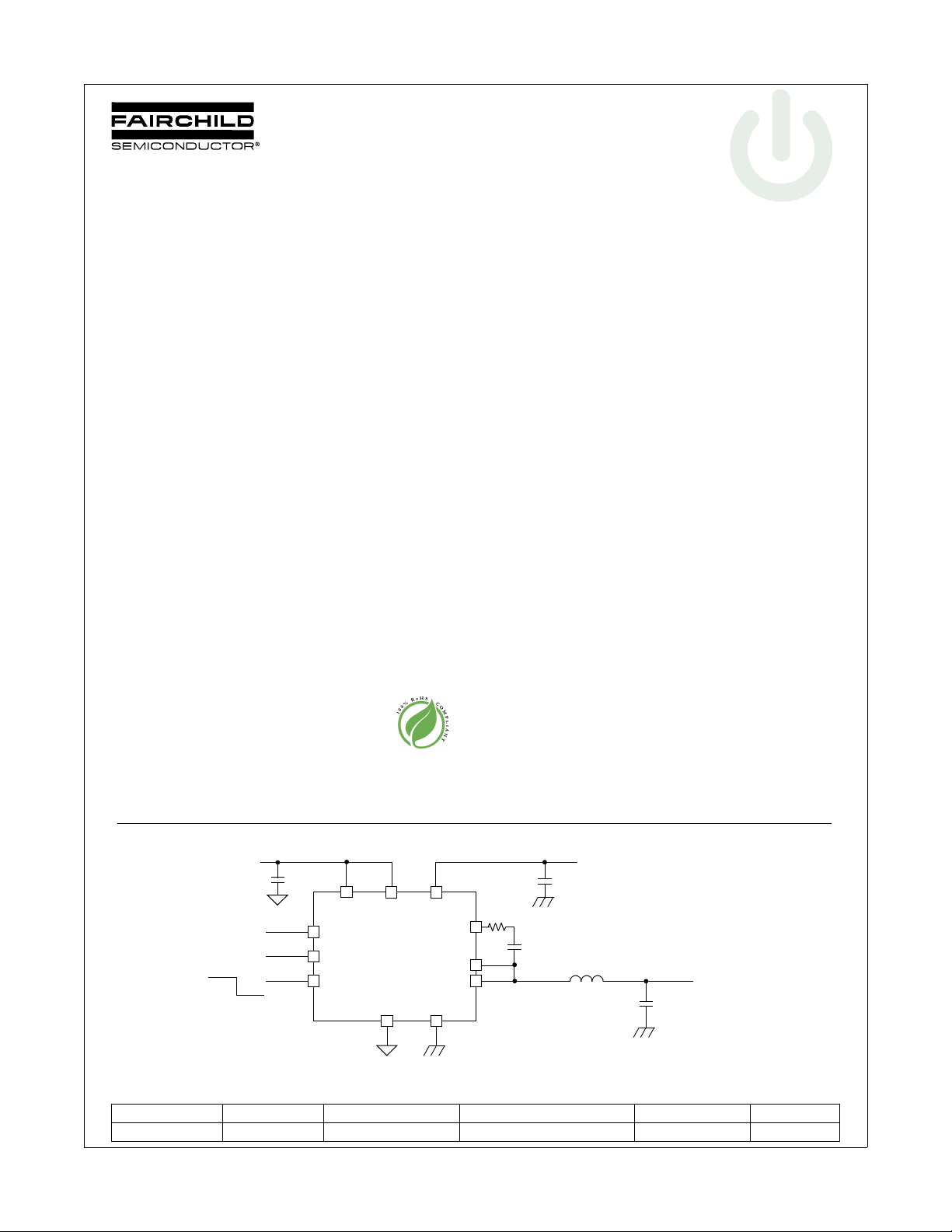

Power Train Application Circuit

5 V

C

VDRV

VCIN VIN

VDRV

DISB#

PWM Input

OFF

ON

DISB#

PWM

SMOD#

BOOT

PHASE

VSWH

CGND PGND

General Description

The XSTM DrMOS family is Fairchild’s next-generation fullyoptimized, ultra-compact, integrated MOSFET plus driver power

stage solutions for high current, high frequency synchronous

buck DC-DC applications. The FDMF6704 XSTM DrMOS

integrates a driver IC, two power MOSFETs and a bootstrap

Schottky diode into a thermally enhanced, ultra compact 6 mm x

6 mm MLP package. With an integrated approach, the complete

switching power stage is optimized with regards to driver and

MOSFET dynamic performance, system inductance and

R

. This greatly reduces the package parasitics and layout

DS(ON)

challenges associated with conventional discrete solutions.

TM

XS

DrMOS uses Fairchild's high performance

PowerTrenchTM 5 MOSFET technology, which dramatically

reduces ringing in synchronous buck converter applications.

PowerTrenchTM 5 can eliminate the need for a snubber circuit in

buck converter applications. The driver IC incorporates

advanced features such as SMOD for improved light load

efficiency and a Tri-State PWM input for compatibility with a

wide range of PWM controllers. A 5 V gate drive and an

improved PCB interface optimized for a maximum low side FET

exposed pad area, ensure higher performance. This product is

compatible with the new Intel 6 mm x 6 mm DrMOS

specification.

Applications

Compact blade servers V-core, non V-core and VTT DC-DC

converters.

Desktop computers V-core, non V-core and VTT DC-DC

converters.

Workstations V-core, non V-core and VTT DC-DC

converters.

Gaming Motherboards V-core, non V-core and VTT DC-DC

converters.

Gaming consoles.

High-current DC-DC Point of Load (POL) converters.

Networking and telecom microprocessor voltage regulators.

12 V

C

VIN

R

BOOT

C

BOOT

L

OUT

OUTPUT

C

OUT

The Xtra Small, High Performance, High Frequency DrMOS Module

Figure 1. Power Train Application Circuit

Ordering Information

Order Number Marking Temperature Range Device Package Packing Method Quantity

FDMF6704 FDMF6704_1 -55 °C to 150 °C 40 Pin, 3 DAP, MLP 6x6 mm Tape and Reel 3000

©2008 Fairchild Semiconductor Corporation

FDMF6704 Rev. G

1

www.fairchildsemi.com

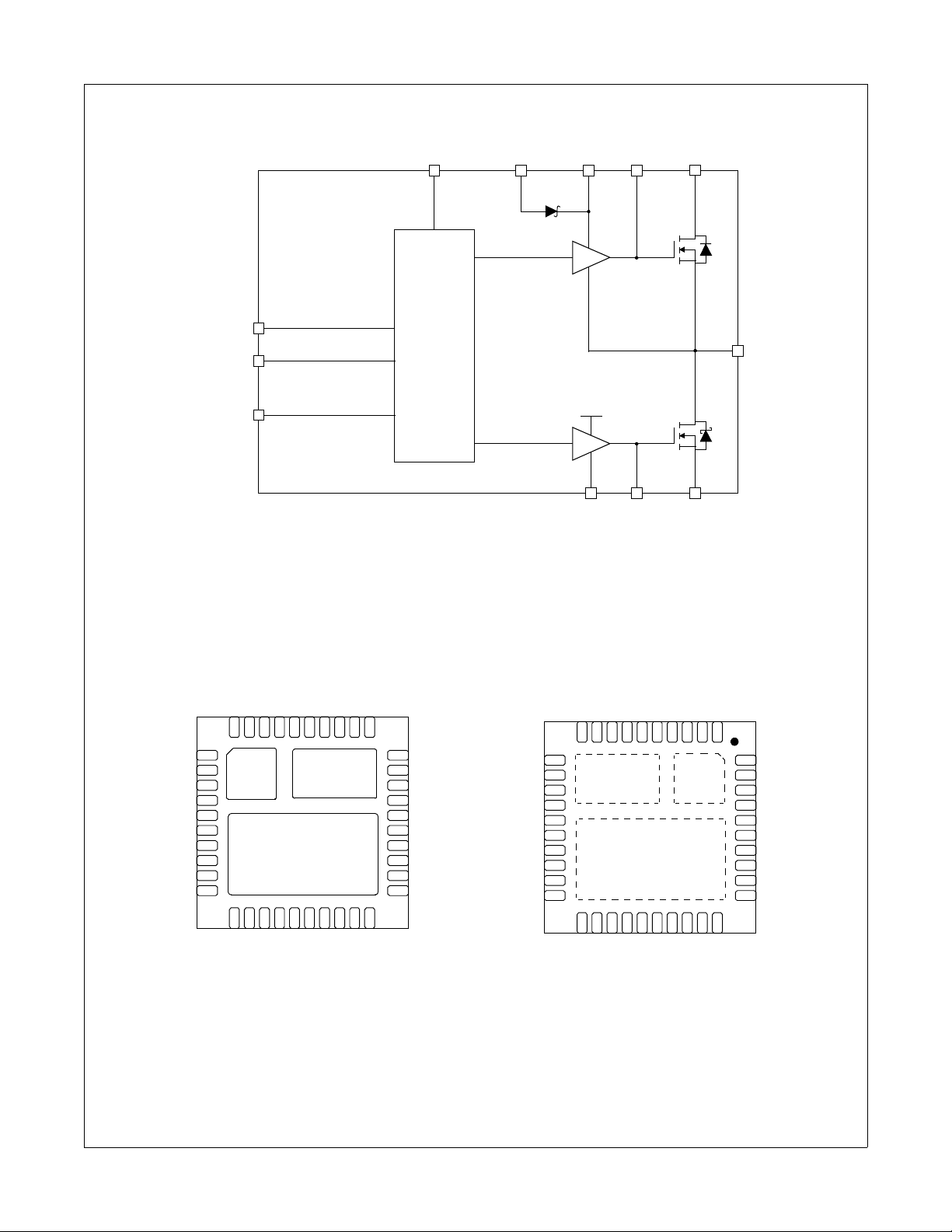

Functional Block Diagram

Figure 2. Functional Block Diagram

CGND

PGND

VSWH

VIN

BOOT

VCIN

VDRV

GH

GL

VDRV

PWM

DISB#

Overlap

Control

SMOD#

Q1

Q2

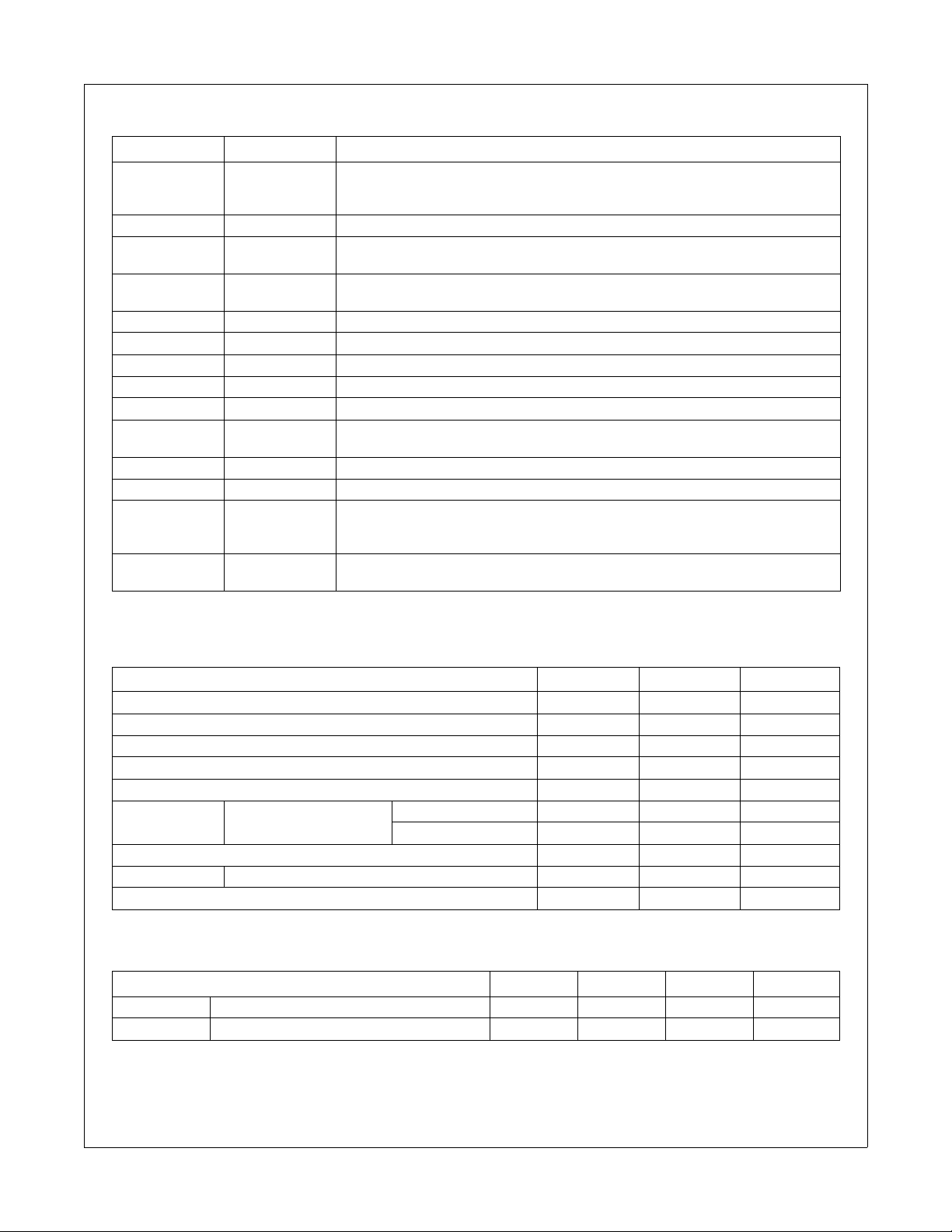

Figure 3. 6mm x 6mm, 40L MLP

CGND

VIN

VSWH

CGND

VIN

VSWH

PWM

SMOD#

DISB#

NC

CGND

GL

VSWH

VSWH

VSWH

VSWH

VSWH

VCIN

VDRV

BOOT

CGND

GH

NC

VIN

VIN

VIN

VIN

VIN

VIN

VSWH

PGND

VSWH

VSWH

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PHASE

PGND

PGND

PGND

PGND

PGND

Bottom View

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

30

29

28

27

26

25

24

23

22

21

40

39

38

37

36

35

34

33

32

31

123456789

10

40

39

38

37

36

35

34

33

32

31

302928272625242322

21

11

12

13

14

15

16

17

18

19

20

SMOD#

VCIN

VDRV

BOOT

CGND

GH

NC

VIN

VIN

PHASE

VIN

VIN

VIN

VIN

VSWH

PGND

PGND

PGND

PGND

PGND

PGND

VSWH

VSWH

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PWM

DISB#

NC

CGND

GL

VSWH

VSWH

VSWH

VSWH

VSWH

41

42

43

41

42

43

FDMF6704

The Xtra Small, High Performance, High Frequency DrMOS Module

Pin Configuration

FDMF6704 Rev. G

2

www.fairchildsemi.com

Pin Description

Pin Name Function

When SMOD# = HI, low side driver is inverse of PWM input. When SMOD# = Low, low

1 SMOD#

2 VCIN IC bias supply. Minimum 1 F ceramic capacitor is recommended from this pin to CGND.

3 VDRV

4 BOOT

5, 37, 41 CGND IC ground. Ground return for driver IC.

6 GH For manufacturing test only. This pin must be floated. Must not be connected to any pin.

7 PHASE Switch node pin for easy bootstrap capacitor routing. Electrically shorted to VSWH pin.

8, 38 NC No connect.

9-14, 42 VIN Power input. Output stage supply voltage.

15, 29-35, 43 VSWH

16-28 PGND Power ground. Output stage ground. Source pin of low side MOSFET(s).

36 GL For manufacturing test only. This pin must be floated. Must not be connected to any pin.

39 DISB#

40 PWM

side driver is disabled. This pin has no internal pullup or pulldown. It should not be left

floating. Do not add noise filter cap.

Power for low side driver. Minimum 1 F ceramic capacitor is recommended to be

connected as close as possible from this pin to CGND.

Bootstrap supply input. Provides voltage supply to high-side MOSFET driver. Connect

bootstrap capacitor from this pin to PHASE.

Switch node input. Provides return for high-side bootstrapped driver and acts as a

sense point for the adaptive shoot-thru protection.

Output disable. When low, this pin disable FET switching (GH and GL are held low). This

pin has no internal pullup or pulldown. It should not be left floating. Do not add noise filter

cap.

PWM Signal Input. This pin accepts a Tri-state logic-level PWM signal from the controller.

Do not add noise filter cap.

FDMF6704

The Xtra Small, High Performance, High Frequency DrMOS Module

Absolute Maximum Rating

Parameter Min Max Units

VCIN, VDRV, DISB#, PWM, SMOD#, GL to CGND 6 V

VIN to PGND, CGND 27 V

BOOT, GH to VSWH, PHASE 6 V

BOOT, VSWH, PHASE, GH to GND 27 V

BOOT to VDRV 22 V

I

* V

O(AV)

I

* 80 A

O(peak)

R

θJPCB

Operating and Storage Junction Temperature Range -55 150 °C

* I

and I

O(AV)

O(peak)

= 12 V, VO = 1.3 V

IN

Junction to PCB Thermal Resistance 3.75 °C/W

are measured in FCS evaluation board. These ratings can be changed with different application setting.

fSW = 350 kHz 35 A

fSW = 1 MHz 32 A

Recommended Operating Range

Parameter Min Typ Max Units

V

CIN

V

IN

* May be operated at lower input voltage. See figure 10.

Control Circuit Supply Voltage 4.5 5 5.5 V

Output Stage Supply Voltage 3

*

12 14 V

FDMF6704 Rev. G

3

www.fairchildsemi.com

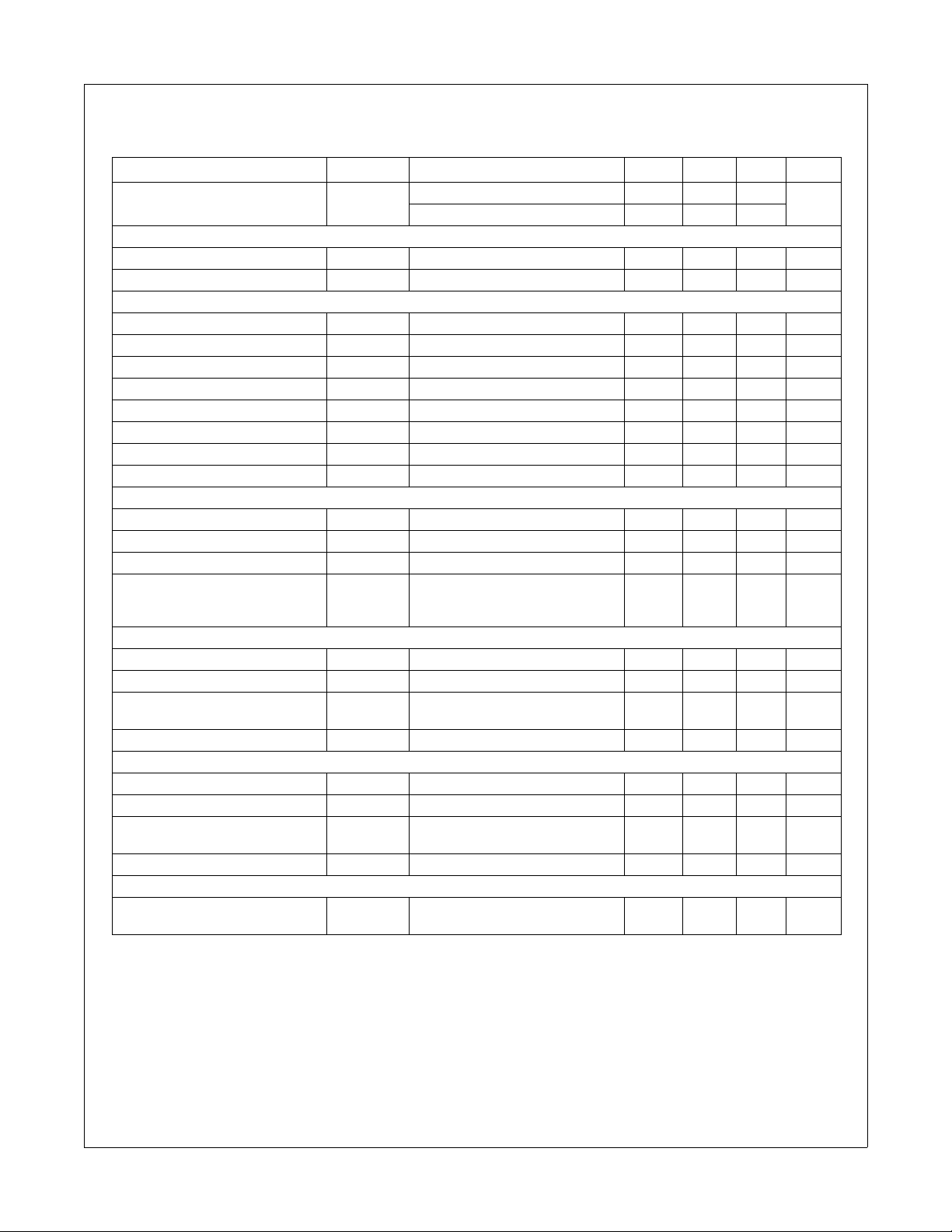

Electrical Characteristics

VIN = 12 V, TA = 25 °C unless otherwise noted.

Parameter Symbol Conditions Min Typ Max Units

Operating Quiescent Current IQ

VCIN UVLO

UVLO Threshold 3.0 3.2 3.4 V

UVLO COMP Hysteresis 0.2 V

PWM Input

Sink Impedance 10 k

Source Impedance 10 k

Tri-State Rising Threshold V

Hysteresis 100 mV

Tri-State Falling Threshold V

Hysteresis 100 mV

Tri-State Pin Open 2.5 V

Tri-State Shut Off Time 100 ns

SMOD# and DISB# Input

High Level Input Voltage 2 V

Low Level Input Voltage 0.8 V

Input Bias Current -2 2 A

Propagation Delay Time

High Side Driver

Rise Time 10 % to 90 % 25 ns

Fall Time 90 % to 10 % 20 ns

Deadband Time t

Propagation Delay t

Low Side Driver

Rise Time 10 % to 90 % 25 ns

Fall Time 90 % to 10 % 20 ns

Deadband Time t

Propagation Delay t

250 ns Time Out Circuit

250 ns Time Delay

DTHH

PDHL

DTLH

PDLL

PWM = GND 2

PWM = V

PWM = GND, delay between SMOD#

or DISB# from HI to LO to GL from HI

to LO.

GL going LO to GH going HI, 10 % to

10 %

PMW going LO to GH going LO 10 ns

VSWH going LO to GL going HI, 10

% to 10 %

PWM going HI to GL going LO 10 ns

Delay between GH from HI to LO and

GL from LO to HI.

CIN

= 5 V 3.2 3.4 3.6 V

CIN

= 5 V 1.2 1.4 1.6 V

CIN

15 ns

25 ns

20 ns

250 ns

2

mA

FDMF6704

The Xtra Small, High Performance, High Frequency DrMOS Module

FDMF6704 Rev. G

4

www.fairchildsemi.com

FDMF6704

Description of Operation

Circuit Description

The FDMF6704 is a driver plus FET module optimized for

synchronous buck converter topology. A single PWM input

signal is all that is required to properly drive the high-side and

the low-side MOSFETs. Each part is capable of driving speeds

up to 1 MHz.

PWM

When the PWM input goes high, the high side MOSFET turns

on. When it goes low, the low side MOSFET turns on. When it is

open, both the low side and high side MOFET will turn off.

The DISB# input is combined with the PWM signal to control the

driver output. In a typical multiphase design, DISB# will be a

shared signal used to turn on all phases. The individual PWM

signals from the controller will be used to dynamically enable or

disable individual phases.

Low-Side Driver

The low-side driver (GL) is designed to drive a ground

referenced low R

internally connected between VDRV and CGND. When the

driver is enabled, the driver's output is 180° out of phase with

the PWM input. When the driver is disabled (DISB# = 0 V), GL

is held low.

High-Side Driver

The high-side driver (GH) is designed to drive a floating

N-channel MOSFET. The bias voltage for the high-side driver is

developed by a bootstrap supply circuit, consisting of the

internal diode and external bootstrap capacitor (C

start-up, VSWH is held at PGND, allowing C

V

through the internal diode. When the PWM input goes

DRV

high, GH will begin to charge the high-side MOSFET's gate

(Q1). During this transition, charge is removed from C

delivered to Q1's gate. As Q1 turns on, VSWH rises to VIN,

forcing the BOOT pin to VIN +V

sufficient VGS enhancement for Q1. To complete the switching

cycle, Q1 is turned off by pulling GH to VSWH. C

recharged to VDRV when VSWH falls to PGND. GH output is in

phase with the PWM input. When the driver is disabled, the

high-side gate is held low.

N-channel MOSFET. The bias for GL is

DS(ON)

BOOT

, which provides

C(BOOT)

). During

BOOT

to charge to

and

BOOT

is then

BOOT

Adaptive Gate Drive Circuit

The driver IC embodies an advanced design that ensures

minimum MOSFET dead-time while eliminating potential

shoot-through (cross-conduction) currents. It senses the state of

the MOSFETs and adjusts the gate drive, adaptively, to ensure

they do not conduct simultaneously. Refer to Figure 4 for the

relevant timing waveforms.

To prevent overlap during the low-to-high switching transition

(Q2 OFF to Q1 ON), the adaptive circuitry monitors the voltage

at the GL pin. When the PWM signal goes HIGH, Q2 will begin

to turn OFF after some propagation delay (t

pin is discharged below 1 V, Q1 begins to turn ON after adaptive

delay t

To preclude overlap during the high-to-low transition (Q1 OFF to

Q2 ON), the adaptive circuitry monitors the voltage at the

VSWH pin. When the PWM signal goes LOW, Q1 will begin to

turn OFF after some propagation delay (t

VSWH pin falls below 1 V, Q2 begins to turn ON after adaptive

delay t

Additionally, VGS of Q1 is monitored. When V

discharged low, a secondary adaptive delay is initiated, which

results in Q2 being driven ON after 250 ns, regardless of VSWH

state. This function is implemented to ensure C

recharged each switching cycle, particularly for cases where the

power convertor is sinking current and VSWH voltage does not

fall below the 1 V adaptive threshold. The 250 ns secondary

delay is longer than t

DTHH

DTLH

.

.

.

DTLH

). Once the GL

PDLL

). Once the

PDHL

GS(Q1)

BOOT

is

is

The Xtra Small, High Performance, High Frequency DrMOS Module

SMOD

The SMOD (Skip Mode) function allows for higher converter

efficiency under light load conditions. During SMOD, the LS

FET is disabled and it prevents discharging of output caps.

When the SMOD# pin is pulled high, the sync buck converter

will work in synchronous mode. When the SMOD# pin is pulled

low, the LS FET is turned off. The SMOD function does not have

internal current sensing. This SMOD# pin is connected to a

PWM controller which enables or disables the SMOD

automatically when the controller detects light load condition.

Normally this pin is Active Low.

FDMF6704 Rev. G

5

www.fairchildsemi.com

Loading...

Loading...