tm

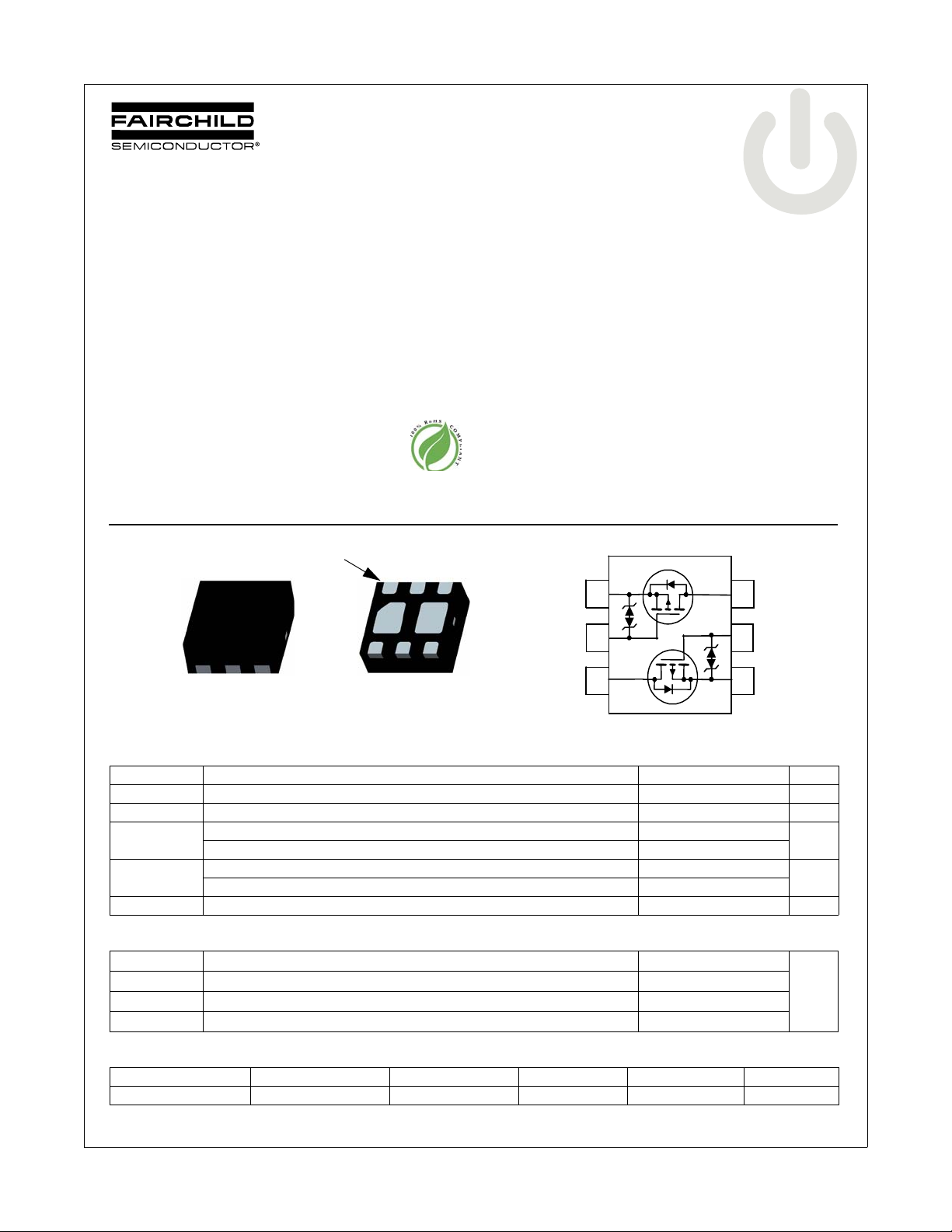

FDMA3023PZ

Dual P-Channel PowerTrench® MOSFET

-30 V, -2.9 A, 90 mΩ

Features

Max r

Max r

Max r

Max r

Low profile - 0.8 mm maximum - in the new package MicroFET

2x2 mm

HBM ESD protection level > 2 kV (Note 3)

RoHS Compliant

Free from halogenated compounds and antimony

oxides

= 90 mΩ at VGS = -4.5 V, ID = -2.9 A

DS(on)

= 130 mΩ at VGS = -2.5 V, ID = -2.6 A

DS(on)

= 170 mΩ at VGS = -1.8 V, ID = -1.7 A

DS(on)

= 240 mΩ at VGS = -1.5 V, ID = -1.0 A

DS(on)

General Description

This device is designed specifically as a single package solution

for the battery charge switch in cellular handset and other

ultra-portable applications. It features two independent

P-Channel MOSFETs with low on-state resistance for minimum

conduction losses. When connected in the typical common

source configuration, bi-directional current flow is possible.

The MicroFET 2X2 package offers exceptional thermal

performance for its physical size and is well suited to linear mode

applications.

FDMA3023PZ Dual P-Channel PowerTrench

December 2008

®

MOSFET

PIN 1

S1 G1 D2

1

S1

1

1

1

1

1

1

D1 D2

2

G1

2

2

2

2

2

2

D2

3

3

3

3

3

3

D1 G2

MicroFET 2x2

MOSFET Maximum Ratings T

Symbol Parameter Ratings Units

V

DS

V

GS

I

D

P

D

, T

T

J

STG

Drain to Source Voltage -30 V

Gate to Source Voltage ±8 V

Drain Current -Continuous (Note 1a) -2.9

-Pulsed -6

Power Dissipation (Note 1a) 1.4

Power Dissipation (Note 1b) 0.7

Operating and Storage Junction Temperature Range -55 to +150 °C

A

S2

= 25 °C unless otherwise noted

3

6

D1

6

6

6

6

6

6

G2

5

5

5

5

5

5

5

S2

4

4

4

4

4

4

4

Thermal Characteristics

R

θJA

R

θJA

R

θJA

R

θJA

Thermal Resistance for Single Operation, Junction to Ambient (Note 1a) 86

Thermal Resistance for Single Operation, Junction to Ambient (Note 1b) 173

Thermal Resistance for Dual Operation, Junction to Ambient (Note 1c) 69

Thermal Resistance for Dual Operation, Junction to Ambient (Note 1d) 151

Package Marking and Ordering Information

A

W

°C/W

Device Marking Device Package Reel Size Tape Width Quantity

323 FDMA3023PZ MicroFET 2X2 7 ’’ 8 mm 3000 units

©2008 Fairchild Semiconductor Corporation

FDMA3023PZ Rev.B1

1

www.fairchildsemi.com

FDMA3023PZ Dual P-Channel PowerTrench

Electrical Characteristics T

= 25 °C unless otherwise noted

J

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BV

∆BV

∆T

I

DSS

I

GSS

DSS

DSS

J

Drain to Source Breakdown Voltage ID = -250 µA, VGS = 0 V -30 V

Breakdown Voltage Temperature

Coefficient

Zero Gate Voltage Drain Current VDS = -24 V, V

Gate to Source Leakage Current VGS = ±8 V, V

I

= -250 µA, referenced to 25 °C -24 mV/°C

D

= 0 V -1 µA

GS

= 0 V ±100 nA

DS

On Characteristics

V

GS(th)

∆V

∆T

r

DS(on)

g

FS

GS(th)

J

Gate to Source Threshold Voltage VGS = VDS, ID = -250 µA -0.4 -0.6 -1.0 V

Gate to Source Threshold Voltage

Temperature Coefficient

Static Drain to Source On Resistance

I

= -250 µA, referenced to 25 °C 3 mV/°C

D

= -4.5 V, ID = -2.9 A 71 90

V

GS

V

= -2.5 V, ID = -2.6 A 97 130

GS

= -1.8 V, ID = -1.7 A 122 170

V

GS

= -1.5 V, ID = -1.0 A 151 240

V

GS

= -4.5 V, ID = -2.9 A, TJ = 125 °C 110 140

V

GS

Forward Transconductance VDS = -5 V, ID = -2.9 A 10 S

Dynamic Characteristics

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance 55 70 pF

Reverse Transfer Capacitance 45 65 pF

= -15 V, VGS = 0 V,

V

DS

f = 1 MHz

400 530 pF

mΩ

®

MOSFET

Switching Characteristics

t

d(on)

t

r

t

d(off)

t

f

Q

g(TOT)

Q

gs

Q

gd

Turn-On Delay Time

Rise Time 410ns

Turn-Off Delay Time 62 100 ns

Fall Time 18 33 ns

Total Gate Charge

Gate to Source Charge 0.9 nC

Gate to Drain “Miller” Charge 1.9 nC

Drain-Source Diode Characteristics

I

S

V

SD

t

rr

Q

rr

Maximum Continuous Drain-Source Diode Forward Current -1.1 A

Source to Drain Diode Forward Voltage V

Reverse Recovery Time

Reverse Recovery Charge 6.6 13 nC

510ns

= -15 V, ID = -1.0 A,

V

DD

V

= -4.5 V, R

GS

= -15 V, ID = -2.9 A

V

DD

V

= -4.5 V

GS

= 0 V, IS = -1.1 A (Note 2) -0.8 -1.2 V

GS

= -2.9 A, di/dt = 100 A/µs

I

F

GEN

= 6 Ω

7.9 11 nC

18 33 ns

©2008 Fairchild Semiconductor Corporation

FDMA3023PZ Rev.B1

2

www.fairchildsemi.com

Notes:

1. R

is determined with the dev ice mounted on a 1 in2 oz. copper pad on a 1.5 x 1.5 in. board of FR-4 material. R

θJA

user's board design.

(a) R

(b) R

(c) R

(d) R

2. Pulse Test : Pulse Width < 300 us, Duty Cycle < 2.0%

3. The diode connected between the gate and source serves only as protection against ESD. No gate overvoltage rating is implied.

= 86 °C/W when mounted on a 1 in2 pad of 2 oz copper, 1.5 " x 1.5 " x 0.062 " thick PCB. For single operation.

θJA

= 173 °C/W when mounted on a minimum pad of 2 oz copper. For single operation.

θJA

= 69 oC/W when mounted on a 1 in2 pad of 2 oz copper, 1.5 ” x 1.5 ” x 0.062 ” thick PCB. For dual operation.

θJA

= 151 oC/W when mounted on a minimum pad of 2 oz copper. For dual operation.

θJA

o

b)173

a)86 oC/W when

mounted on a 1

2

pad of 2 oz

in

copper.

C/W when

mounted on a

minimum pad of 2

oz copper.

is guaranteed by design while R

θJC

c)69 oC/W when

mounted on a 1 in

pad of 2 oz copper.

FDMA3023PZ Dual P-Channel PowerTrench

is determined by the

θJA

o

d)151

C/W when

2

mounted on a

minimum pad of 2 oz

copper.

®

MOSFET

©2008 Fairchild Semiconductor Corporation

FDMA3023PZ Rev.B1

3

www.fairchildsemi.com

Loading...

Loading...