Fairchild FAN3268 service manual

FAN3268

2A Low-Voltage PMOS-NMOS Bridge Driver

FAN3268 —2A Low-Voltage PMOS-NMOS Bridge Driver

July 2012

Features

4.5V to 18V Operating Range

Drives High-Side PMOS and Low-Side NMOS in

Motor Control or Buck Step-Down Applications

Inverting Channel B Biases High-Side PMOS

Device Off (with internal 100kΩ Resistor) when

V

is below UVLO Threshold

DD

TTL Input Thresholds

2.4A Sink / 1.6A Source at V

OUT

=6V

Internal Resistors Turn Driver Off If No Inputs

MillerDrive™ Technology

8-Lead SOIC Package

Rated from –40°C to +125°C Ambient

Applications

Motor Control with PMOS / NMOS Half-Bridge

Configuration

Buck Converters with High-Side PMOS Device;

100% Duty Cycle Operation Possible

Logic-Controlled Load Circuits with High-Side

PMOS Switch

Description

The FAN3268 dual 2A gate driver is optimized to drive a

high-side P-channel MOSFET and a low-side N-channel

MOSFET in motor control applications operating from a

voltage rail up to 18V. The driver has TTL input

thresholds and provides buffer and level translation

functions from logic inputs. Internal circuitry provides an

under-voltage lockout function that prevents the output

switching devices from operating if the V

voltage is below the operating level. Internal 100kΩ

resistors bias the non-inverting output low and the

inverting output to V

off during startup intervals when logic control signals

may not be present.

The FAN3268 driver incorporates MillerDrive™

architecture for the final output stage. This bipolarMOSFET combination provides high current during the

Miller plateau stage of the MOSFET turn-on / turn-off

process to minimize switching loss, while providing railto-rail voltage swing and reverse current capability.

The FAN3268 has two independent enable pins that

default to on if not connected. If the enable pin for noninverting channel A is pulled low, OUTA is forced low; if

the enable pin for inverting channel B is pulled low,

OUTB is forced high. If an input is left unconnected,

internal resistors bias the inputs such that the external

MOSFETs are off.

to keep the external MOSFETs

DD

supply

DD

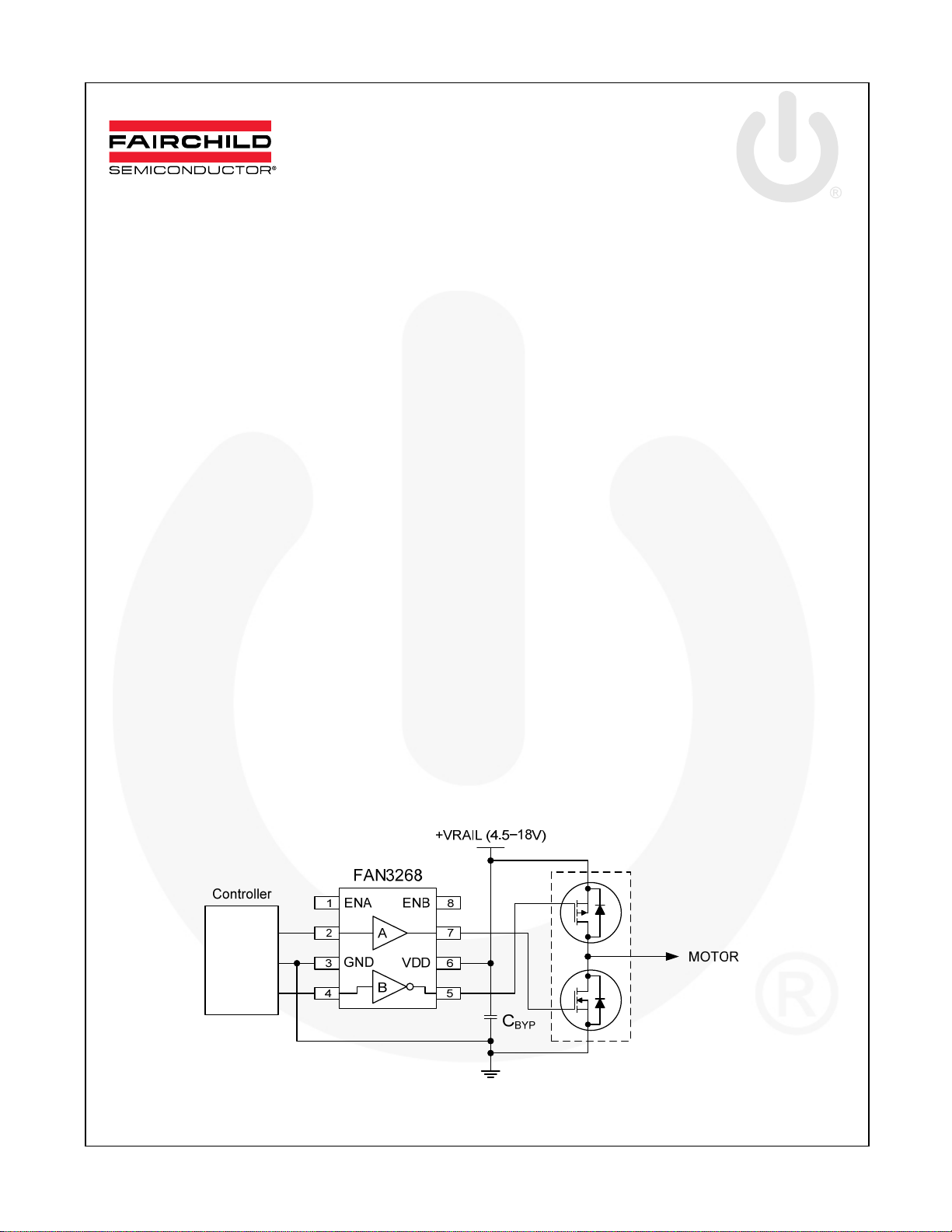

Figure 1. Typical Motor Drive Application

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN3268 • Rev. 1.0.2 1

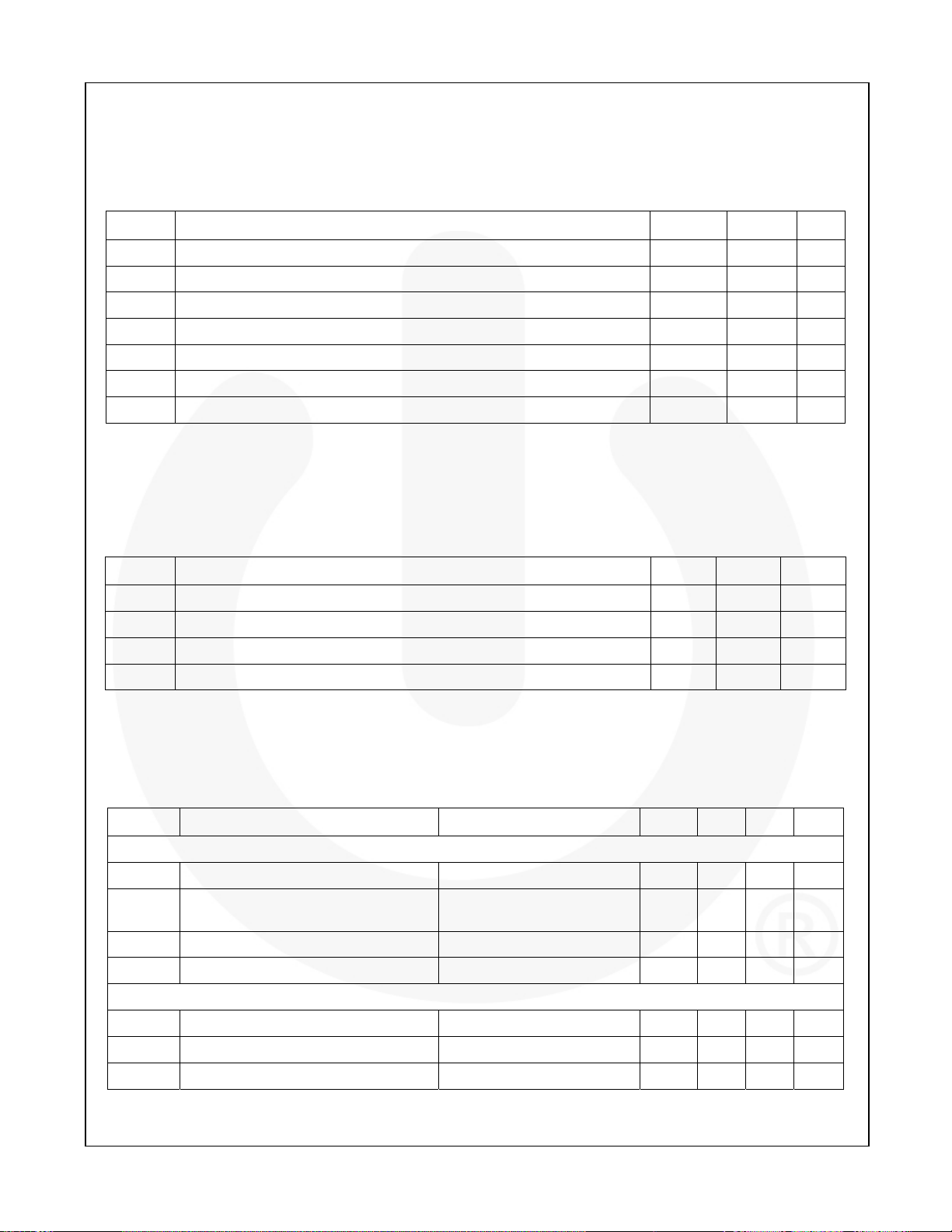

Ordering Information

Part Number Logic Input Threshold Packing Method

FAN3268TMX

Non-Inverting Channel and Inverting

Channel + Dual Enables

TTL

2,500 Units on

Tape & Reel

Package Outline

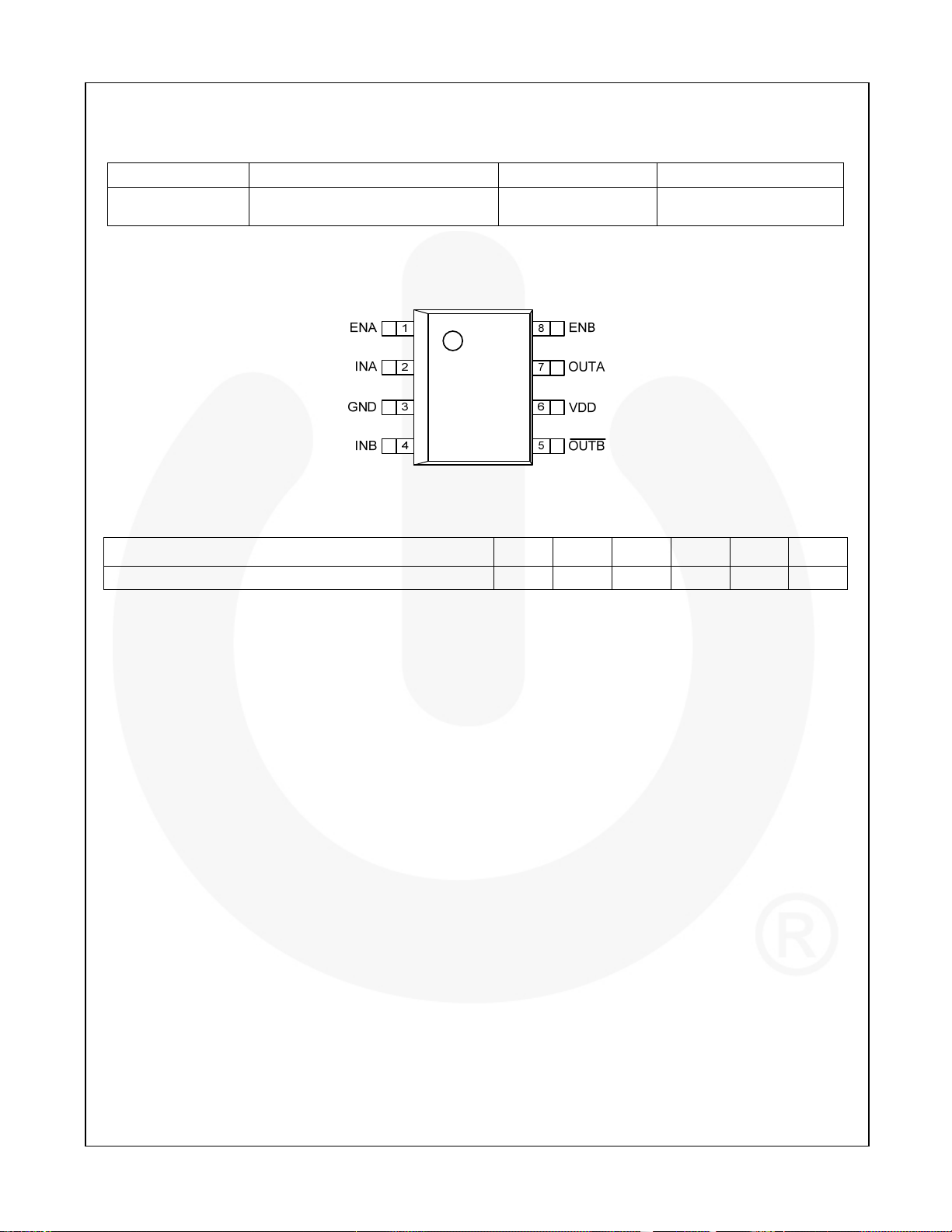

Figure 2. Pin Configuration (Top View)

FAN3268 —2A Low-Voltage PMOS-NMOS Bridge Driver

Thermal Characteristics

8-Pin Small Outline Integrated Circuit (SOIC)

(1)

Package

(2)

Θ

Θ

JL

40 31 89 43 3 °C/W

(3)

Θ

JT

JA

(4)

Ψ

JB

(5)

Ψ

JT

Notes:

1. Estimates derived from thermal simulation; actual values depend on the application.

2. Theta_JL (

thermal pad) that are typically soldered to a PCB.

3. Theta_JT (

held at a uniform temperature by a top-side heatsink.

4. Theta_JA (Θ

The value given is for natural convection with no heatsink using a 2S2P board, as specified in JEDEC standards JESD51-2,

JESD51-5, and JESD51-7, as appropriate.

5. Psi_JB (

application circuit board reference point for the thermal environment defined in Note 4. For the SOIC-8 package, the board

reference is defined as the PCB copper adjacent to pin 6.

6. Psi_JT (

the center of the top of the package for the thermal environment defined in Note 4.

Θ

): Thermal resistance between the semiconductor junction and the bottom surface of all the leads (including any

JL

Θ

): Thermal resistance between the semiconductor junction and the top surface of the package, assuming it is

JT

): Thermal resistance between junction and ambient, dependent on the PCB design, heat sinking, and airflow.

JA

Ψ

): Thermal characterization parameter providing correlation between semiconductor junction temperature and an

JB

Ψ

): Thermal characterization parameter providing correlation between the semiconductor junction temperature and

JT

(6)

Units

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN3268 • Rev. 1.0.2 2

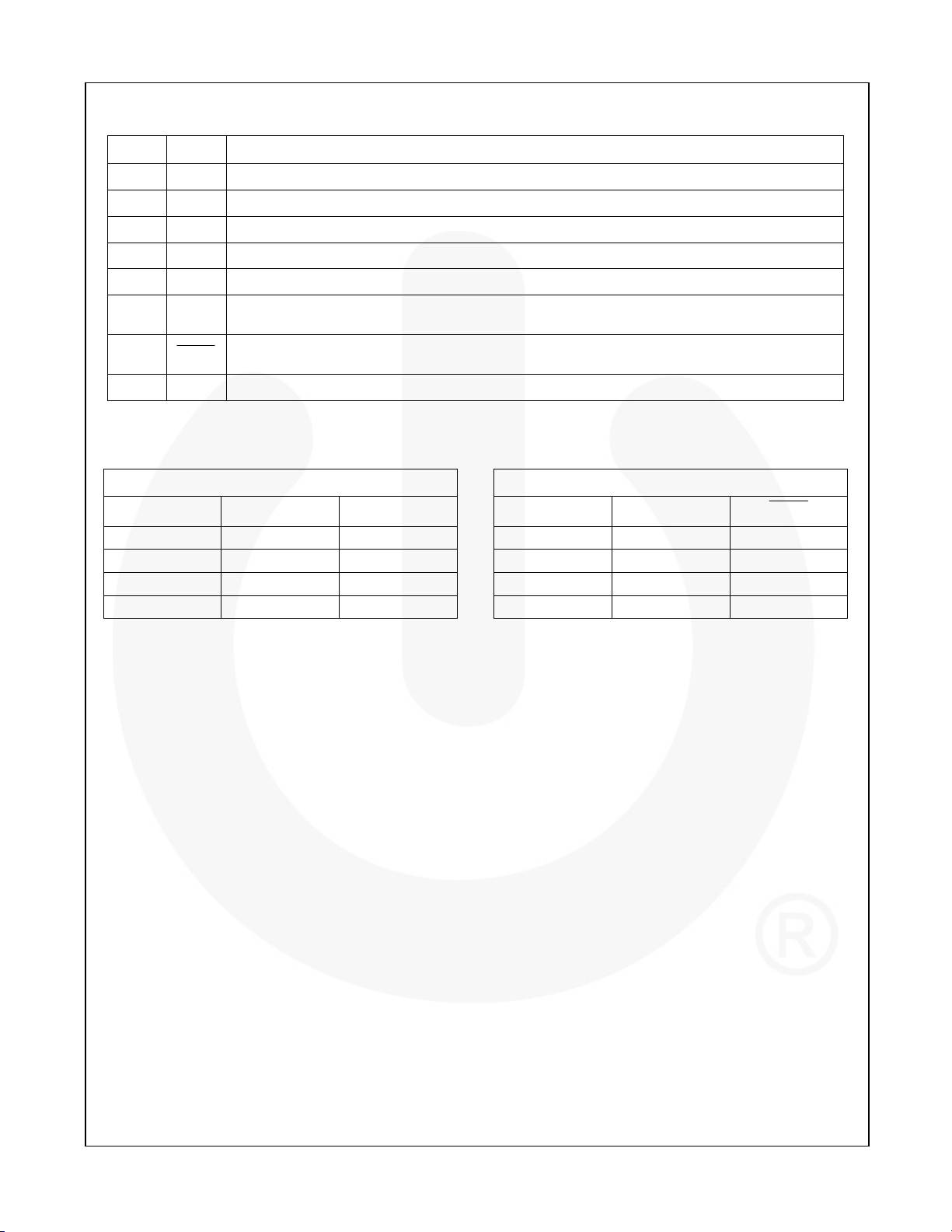

Pin Definitions

Pin# Name Description

FAN3268 —2A Low-Voltage PMOS-NMOS Bridge Driver

1 ENA

8 ENB

3 GND

2 INA

4 INB

7

OUTA

5

OUTB

6 VDD

Enable Input for Channel A. Pull pin low to inhibit driver A. ENA has TTL thresholds.

Enable Input for Channel B. Pull pin low to inhibit driver B. ENB has TTL thresholds.

Ground. Common ground reference for input and output circuits.

Input to Channel A.

Input to Channel B.

Gate Drive Output A: Held low unless required input(s) are present and V

DD

threshold.

Gate Drive Output B (inverted from the input): Held high unless required input is present and V

is above UVLO threshold.

Supply Voltage. Provides power to the IC.

Output Logic

FAN3268 (Channel A) FAN3268 (Channel B)

ENA INA OUTA ENB INB

0 0

(7)

0 0 0

0 1 0 0 1 1

(7)

1

0

(7)

1

1 1 1

(7)

0 1

Note:

7. Default input signal if no external connection is made.

(7)

0

(7)

1 0

(7)

1

(7)

1

is above the UVLO

OUTB

DD

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN3268 • Rev. 1.0.2 3

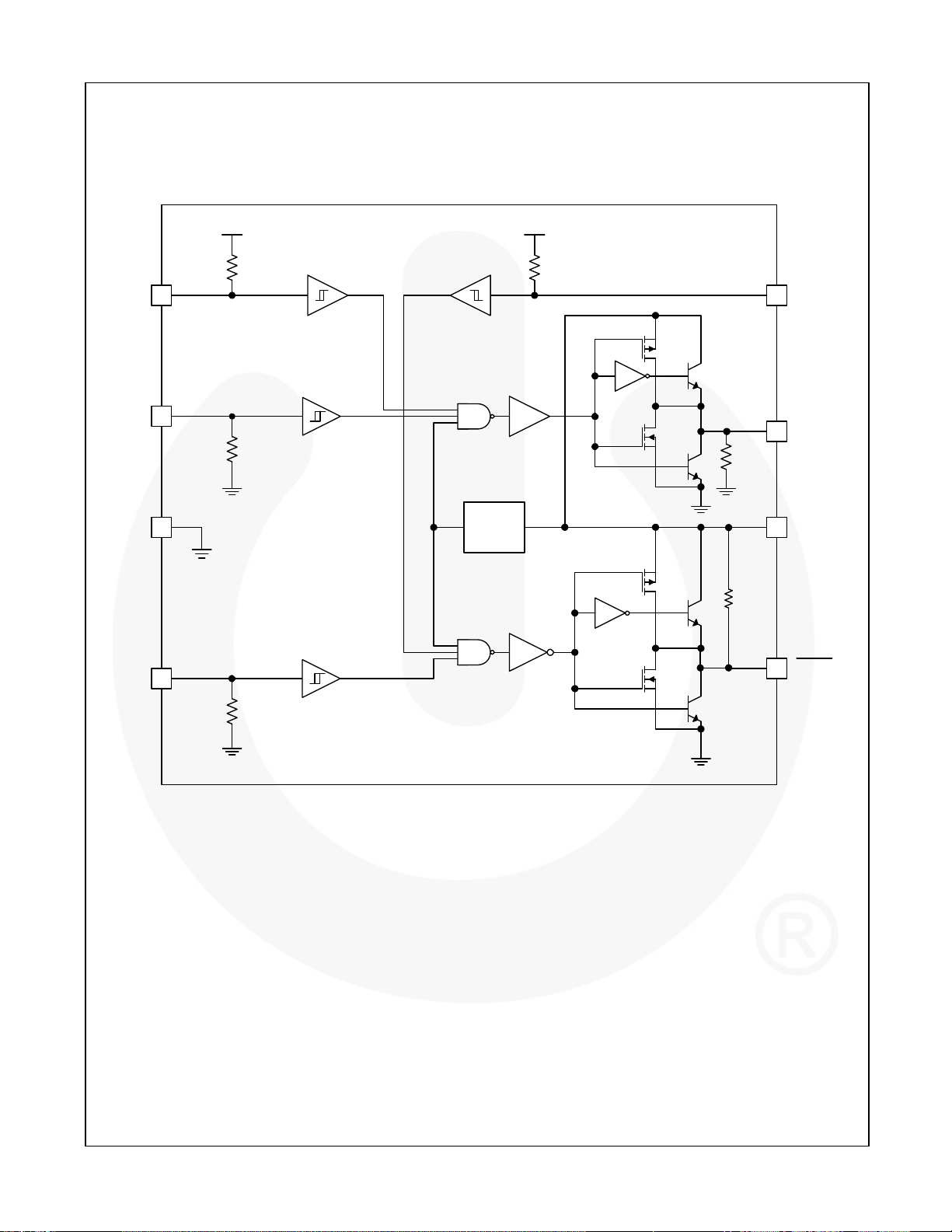

Block Diagram

FAN3268 —2A Low-Voltage PMOS-NMOS Bridge Driver

ENA

INA

GND

INB

VDD

100kΩ

1

2

100kΩ

3

V

DD_OK

4

UVLO

VDD

100kΩ

100kΩ

100kΩ

8

7

6

5

ENB

OUTA

VDD

OUTB

100kΩ

Figure 3. Block Diagram

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN3268 • Rev. 1.0.2 4

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Min. Max. Unit

VDD VDD to PGND -0.3 20.0 V

VEN ENA, ENB to GND GND - 0.3 VDD + 0.3 V

VIN INA, INB to GND GND - 0.3 VDD + 0.3 V

V

OUTA, OUTB to GND GND - 0.3 VDD + 0.3 V

OUT

TL Lead Soldering Temperature (10 Seconds) +260 ºC

TJ Junction Temperature -55 +150 ºC

T

Storage Temperature -65 +150 ºC

STG

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

FAN3268 —2A Low-Voltage PMOS-NMOS Bridge Driver

Symbol Parameter Min. Max. Unit

VDD Supply Voltage Range 4.5 18.0 V

VEN Enable Voltage (ENA, ENB) 0 VDD V

VIN Input Voltage (INA, INB) 0 VDD V

TA Operating Ambient Temperature -40 +125 ºC

Electrical Characteristics

Unless otherwise noted, VDD=12V and TJ=-40°C to +125°C. Currents are defined as positive into the device and

negative out of the device.

Symbol Parameter Conditions Min. Typ. Max. Unit

SUPPLY

VDD Operating Range 4.5 18.0 V

IDD

VON Turn-On Voltage INA=ENA=VDD, INB=ENB=0V 3.5 3.9 4.3 V

V

INPUT

VIL INx Logic Low Threshold 0.8 1.2 V

VIH INx Logic High Threshold 1.6 2.0 V

V

Supply Current Inputs / EN Not

Connected

Turn-Off Voltage INA=ENA=VDD, INB=ENB=0V 3.3 3.7 4.1 V

OFF

(8)

Logic Hysteresis Voltage 0.2 0.4 0.8 V

HYS

0.75 1.20 mA

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN3268 • Rev. 1.0.2 5

Loading...

Loading...