Fairchild FAN21SV06 service manual

September 2011

FAN21SV06 — TinyBuck™

6A, 24V Single-Input Integrated Synchronous Buck

Regulator with Synchronization Capability

FAN21SV06 — TinyBuck™ 6A, 24V Single-Input Integrated Synchronous Buck Regulator, Synchronization Capability

Features

Single-Supply Operation with 6A Output Current

Over 94% Efficiency

Fully Synchronous Operation with Integrated

Schottky Diode on Low-Side MOSFET Boosts

Efficiency

Single Supply Device for V

> 6.5V – 24V

IN

Programmable Frequency Operation (200-600KHz)

Externally Synchronizable Clock with Master/Slave

Provisions

Wide Input Range with Dual Supply: 3.0V to 24V

Output Voltage Range: 0.8V to 80%V

IN

Power-Good Signal

Accepts Ceramic Capacitors on Output

External Compensation for Flexible Design

Starts Up on Pre-Bias Outputs

Integrated Bootstrap Diode

Programmable Over-Current Protection

Under-Voltage, Over-Voltage, and Thermal-

Shutdown Protections

5x6mm, 25-pin, 3-pad MLP

Applications

Servers & Telecom

Graphics Cards & Displays

High-End Computing Systems

Set-Top Boxes & Game Consoles

Point-of-Load Regulation

Description

The FAN210SV06 TinyBuckTM is a highly efficient,

small-footprint, programmable-frequency, 6A integrated

synchronous buck regulator.

FAN21SV06 contains both synchronous MOSFETs and

a controller/driver with optimized interconnects in one

package, which enables designers to solve high-current

requirements in a small area with minimal external

components, thereby saving cost. On-board internal 5V

regulator enables single-supply operation for input

voltages >6.5V.

The FAN21SV06 can be configured to drive multiple

slave devices OR synchronize to an external system

clock. In slave mode, FAN21SV06 may be set up to be

free-running in the absence of a master clock signal.

External compensation, programmable switching

frequency, and current-limit features allow for design

optimization and flexibility. High-frequency operation

allows for all ceramic solutions.

Fairchild’s advanced BiCMOS power process combined

with low-R

efficient MLP package provide the ability to dissipate

high power in a small package. Integration helps to

minimize critical inductances making layout simpler and

more efficient compared to discrete solutions.

Output over-voltage, under-voltage, over-current and

thermal-shutdown protections help protect the device

from damage during fault conditions. FAN21SV06

prevents pre-biased output discharge during startup in

point-of-load applications.

internal MOSFETs and a thermally

DS(ON)

Related Resources

TinyCalc™ Calculator Design Tool

AN-6033 — FAN21SV06 Design Guide

AN-8022 — TinyCalc™ Calculator

Ordering Information

Operating

Part Number

FAN21SV06MPX -10°C to 85°C Molded Leadless Package (MLP) 5x6mm Tape and Reel

FAN21SV06EMPX -40°C to 85°C Molded Leadless Package (MLP) 5x6mm Tape and Reel

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN21SV06 Rev. 1.0.1

Temperature Range Package

Packing

Method

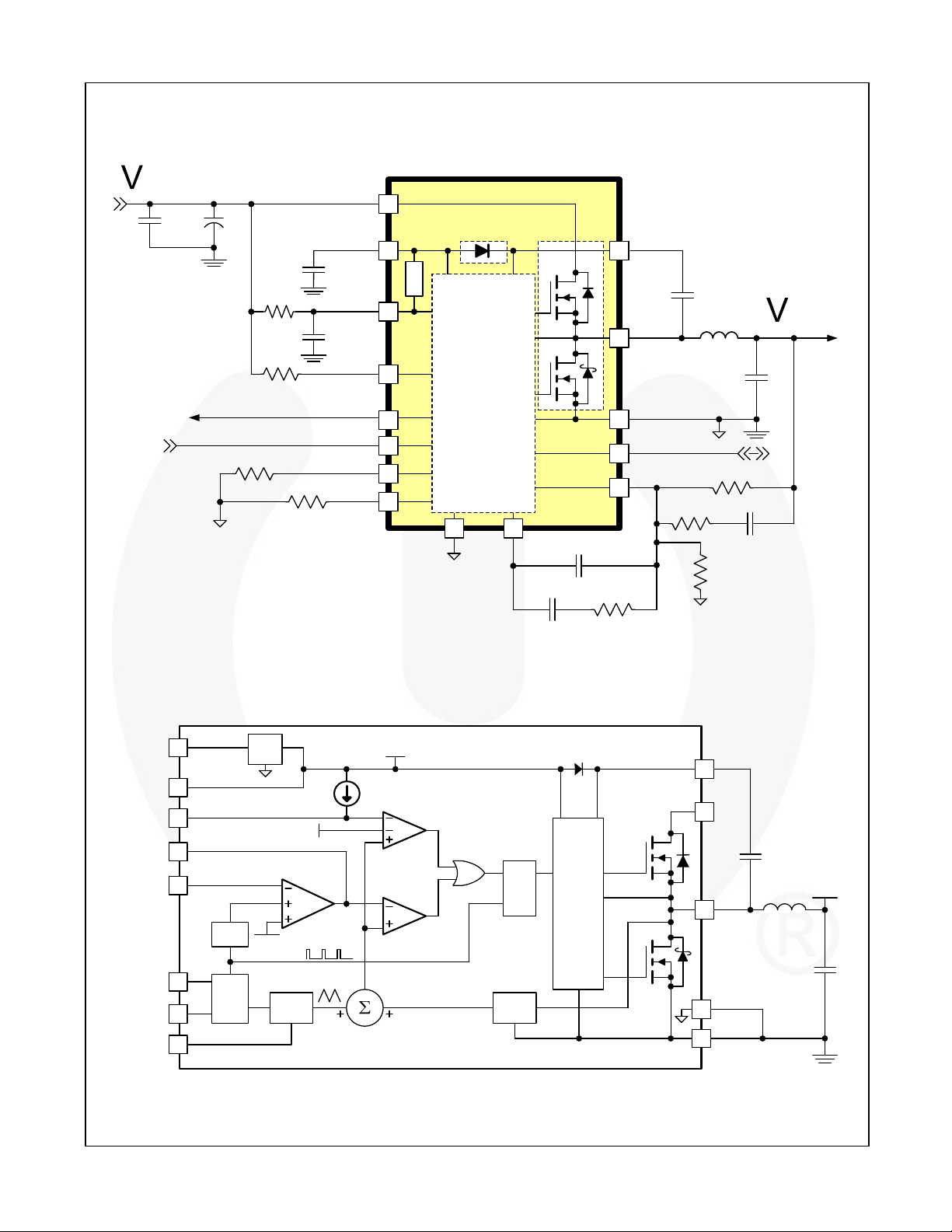

Typical Application Diagram

FAN21SV06 — TinyBuck™ 6A, 24V Single-Input Integrated Synchronous Buck Regulator, Synchronization Capability

IN

VIN

Boot

C

HF

Enable

Power

Good

C

IN

5V_Reg

C4

R5

VIN_Reg

Reg

C5

RAMP

R

RAMP

R

ILIM

R

EN

ILIM

T

R

T

AGND

Diode

PWM

+

DRIVER

Q1

Q2

MOSFETS

COMP

C2

POWER

C1

R2

BOOT

SW

PGND

CLK

FB

R3

C

BOOT

L

C

R

OUT

OUT

R1

C3

BIAS

Figure 1. Typical Application, Master, V

=6.5V to 24V

IN

Block Diagram

VIN_Reg

5V_Reg

ILIM

COMP

FB

CLK

EN

RAMP

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN21SV06 Rev. 1.0.1 2

SS

OSC

Reg

VREF

Int ref

Error

Amplifier

RAMP

GEN

IILIM

5V

Current Limit

Comparator

PWM

Comparator

Summing

Amplifier

Current

Sense

Figure 2. Block Diagram

RSQ

Boot

Diode

Gate

Drive

Circuit

BOOT

IN

V

SW

AGND

PGND

CBOOT

L

VOUT

C

OUT

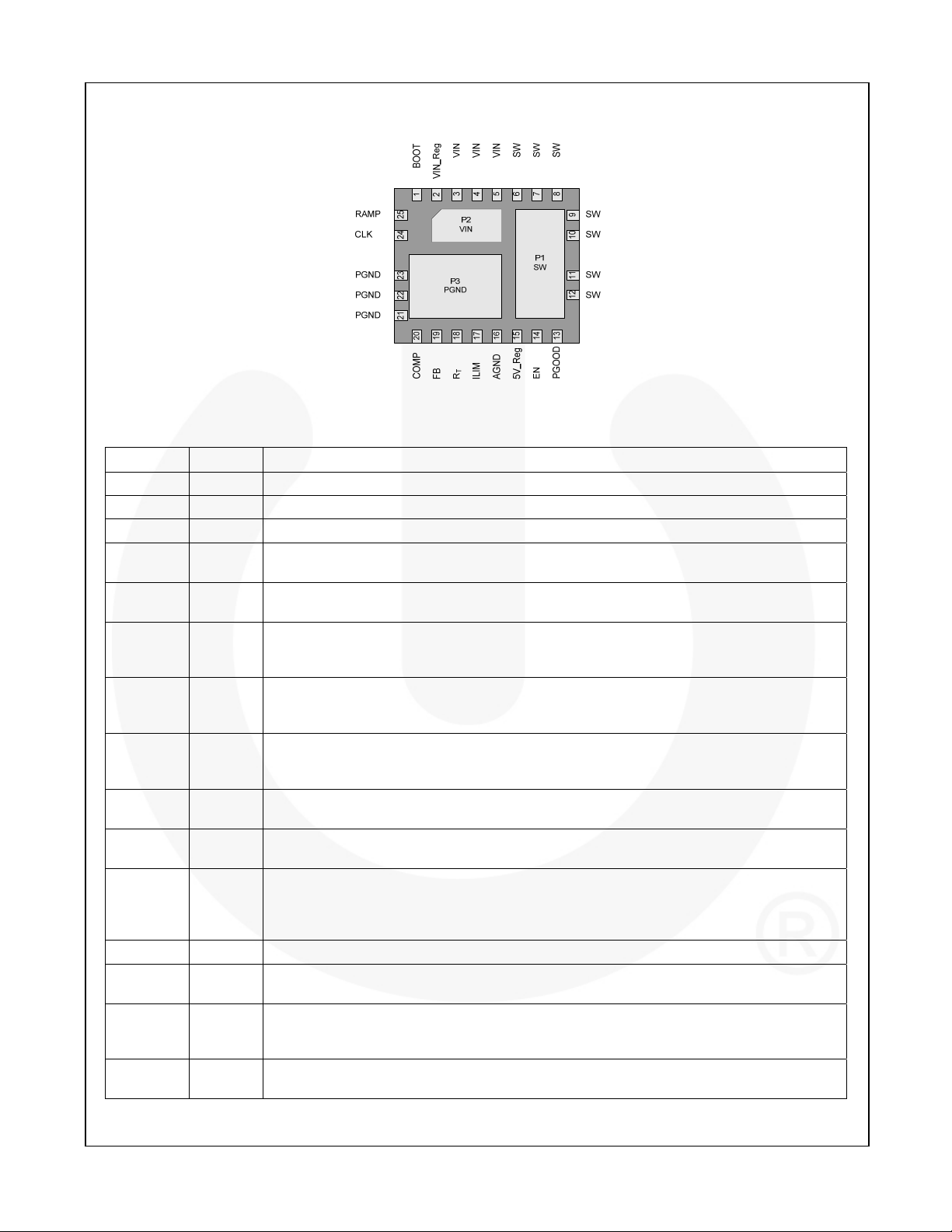

Pin Configuration

Figure 3. MLP 5x6mm Pin Configuration (Bottom View)

Pad / Pin Definitions

Pad / Pin Name Description

P1, 6-12 SW

P2, 3-5 VIN

P3, 21-23 PGND

1 BOOT

2 VIN_Reg

13 PGOOD

14 EN

15 5V_Reg

16 AGND

17 ILIM

18 RT

19 FB

20 COMP

24 CLK

25 RAMP

Switching Node. Junction of high-side and low-side MOSFETs.

Power Input Voltage. Supply voltage for the converter.

Power Ground. Power return and Q2 source.

High-Side Drive BOOT Voltage. Connect through capacitor (C

internal synchronous bootstrap diode to recharge the capacitor on this pin to 5V.

Regulator Input Voltage. Input voltage to the internal regulator. Connect to input voltage

>6.5V with 1µF bypass capacitor at the pin.

Power-Good. An open-drain output that pulls LOW when the voltage on the FB pin is

outside the limits specified in the electrical specs. PGOOD does not assert HIGH until the

fault latch is enabled.

ENABLE. Enables operation when pulled to logic HIGH or left open. Toggling EN resets the

regulator after a latched-fault condition. This input has an internal pull-up. When a latched

fault occurs, EN is discharged by a current sink.

5V Regulator Output. Internal regulator output that provides power for the IC’s logic and

analog circuitry. This pin should be connected to AGND through a >2.2µf X5R/X7R

capacitor.

Analog Ground. The signal ground for the IC. All internal control voltages are referred to

this pin. Tie this pin to the ground island/plane through the lowest impedance connection.

Current Limit. A resistor (R

limit trip threshold lower than the internal default setting.

Oscillator Frequency and Master/Slave Set. Connecting a resistor (R

oscillator frequency and configures the CLK pin as an output (master). Tying this pin to

5V_Reg through a resistor configures the CLK signal as an input (slave) and establishes

the free-running oscillator frequency.

Output Voltage Feedback. Connect through a resistor divider to the output voltage.

Compensation. Error amplifier output. Connect the external compensation network

between this pin and FB.

Clock. Bi-directional signal pin, depending on master/slave configuration. When configured

as a master, this pin represents the clock output that connects directly to the slave(s) for

synchronizing with 180° phase shift.

Ramp Amplitude. A resistor (R

amplitude and also provides voltage feedforward functionality.

) from this pin to AGND can be used to program the current-

ILIM

) connected from this pin to VIN sets the internal ramp

RAMP

) to SW. The IC has an

BOOT

) to AGND sets the

T

FAN21SV06 — TinyBuck™ 6A, 24V Single-Input Integrated Synchronous Buck Regulator, Synchronization Capability

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN21SV06 Rev. 1.0.1 3

FAN21SV06 — TinyBuck™ 6A, 24V Single-Input Integrated Synchronous Buck Regulator, Synchronization Capability

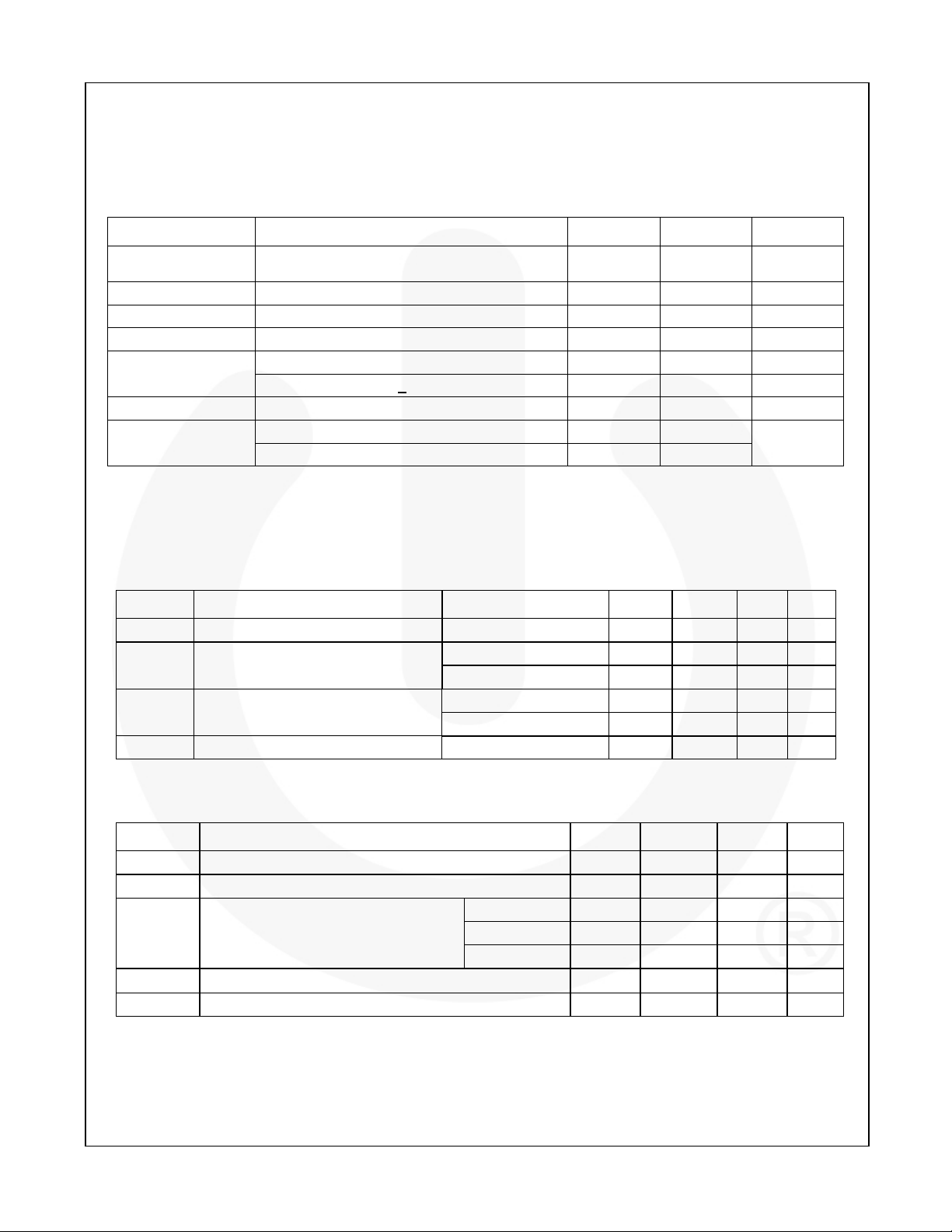

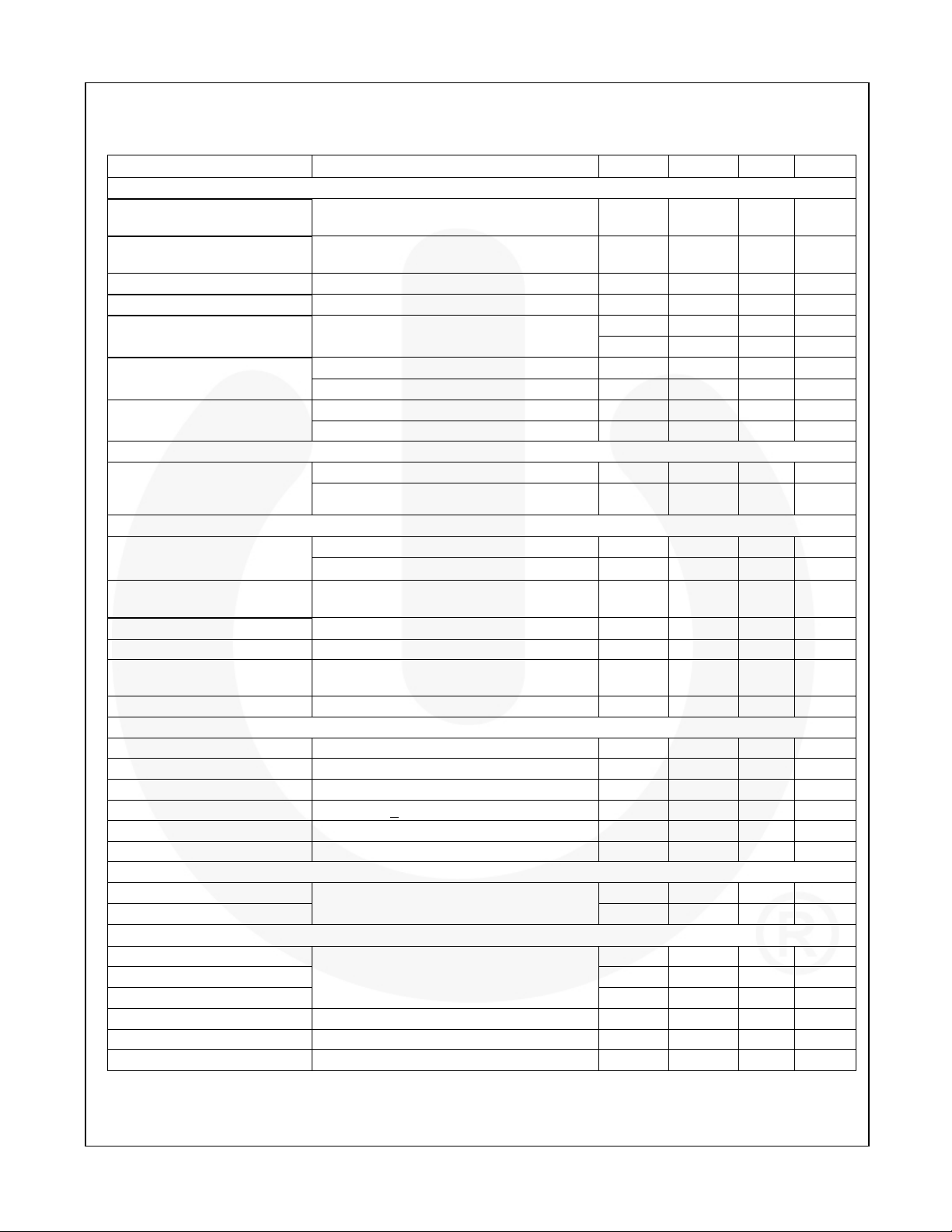

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Parameter Conditions Min. Max. Units

VIN, VIN_Reg to

AGND

5V_Reg to AGND AGND=PGND 6 V

BOOT to PGND 35 V

BOOT to SW -0.5 6.0 V

SW to PGND

All other pins -0.3 6.0 V

ESD

AGND=PGND 28 V

Continuous -0.5 24.0 V

Transient (t < 20ns, f < 600KHz) -5 30 V

Human Body Model, JESD22-A114 1.5

Charged Device Model, JESD22-C101 2.5

kV

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol Parameter Conditions Min. Typ. Max Units

fSW Switching Frequency 200 500 600 KHz

V

IN,

VIN_Reg

Supply Voltage for Power and Bias

TA Ambient Temperature

VIN to PGND 3.0 24.0 V

VIN_Reg to AGND 6.5 24.0 V

FAN21SV06MX -10 +85 °C

FAN21SV06EMX -40 +85 °C

TJ Junction Temperature +125 °C

Thermal Information

Symbol Parameter Min. Typ. Max. Units

T

Storage Temperature -65 +150 °C

STG

TL Lead Soldering Temperature, 30sec +300 °C

P1 (Q2) 4 °C/W

JC

J-PCB

Thermal Resistance: Junction-to-Case

Thermal Resistance: Junction-to-Mounting Surface

PD Total Power Dissipation in the package, TA=25°C

Note:

1. Typical thermal resistance when mounted on a four-layer, two-ounce PCB, as shown in Figure 37. Actual results

are dependent upon mounting method and surface related to the design.

P2 (Q1) 7 °C/W

P3 4 °C/W

(1)

35

(1)

2.8 W

(1)

°C/W

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN21SV06 Rev. 1.0.1 4

FAN21SV06 — TinyBuck™ 6A, 24V Single-Input Integrated Synchronous Buck Regulator, Synchronization Capability

Electrical Characteristics

Recommended operating conditions, using the circuit in Figure 1, with VIN, V

Parameter Conditions Min. Typ. Max. Units

Power Supplies

Operating Current

(VIN+VIN_Reg)

VIN_Reg Operating Current

VIN_Reg Quiescent Current EN=High, FB=0.9V 4 5 mA

VIN_Reg Standby Current EN=0, VIN=12V 1 mA

5V_Reg Output Voltage

5V_Reg Max Current Load

VIN_Reg UVLO Threshold

Reference

Reference Voltage measured

at FB (See Figure 4 for

Temperature Coefficient)

Oscillator

Frequency

Frequency in Slave Mode

compared to Master Mode

Minimum On-Time

(2)

40 65 ns

Duty Cycle VIN=6.5V, fSW=600KHz 80 85 %

Ramp Amplitude,

Peak–to-Peak

Minimum Off-Time

(2)

(2)

100 150 ns

Synchronization

CLK Output Pulse Width Master (RT to GND) 70 85 100 ns

CLK Output Sink Current Master, V

CLK Output Source Current Master, V

CLK Input Pulse Width Slave: V

CLK Input Source Current Slave: V

CLK Input Threshold, Rising Slave 1.73 1.83 1.93 V

Soft-Start

V

to Regulation (T

OUT

Fault Enable/SSOK (T

)

0.8

) 3.1 ms

1.0

Error Amplifier

DC Gain

Gain Bandwidth Product

Output Voltage Swing (V

(2)

(2)

COMP

Output Current, Sourcing 5V_Reg=5V, V

Output Current, Sinking 5V_Reg=5V, V

FB Bias Current VFB=0.8V, 25°C -850 -650 -450 nA

Note:

2. Specifications guaranteed by design and characterization; not production tested.

VIN=12V, 5V_Reg open, CLK open,

f

=500KHz, No Load

SW

EN=High, 5V_Reg open, CLK open,

=500KHz

f

SW

Internal VCC Regulator, No Load

(6.5V <VIN_Reg<24V)

VIN_Reg=12V) 5 mA

Rising V

, VIN=VIN_Reg 5.6 6.3 V

IN

Falling VIN, VIN=VIN_Reg 5 V

FAN21SV06M, 25°C 794 800 806 mV

FAN21SV06EM, 25°C 795 800 805 mV

=50k to GND (Master Mode)

R

T

RT=24k to GND (Master Mode)

RT=24 k to 50k to 5V_Reg

(Slave Mode)

16VIN, 1.8V

, RT=30k, R

OUT

=0.4V 0.25 0.35 mA

CLK

=2V -2.5 -2.0 mA

CLK

> 2V 50 ns

CLK

=1V -230 -200 -170 µA

CLK

RAMP

=200k

Frequency=500KHz

12 15 MHz

VIN_Reg > 6.5V

) 0.4 4.0 V

=2.2V 1.5 2.2 2.5 mA

COMP

=1.2V 0.8 1.2 1.5 mA

COMP

=12V, unless otherwise noted.

IN_Reg

22 30 mA

11 mA

4.7 5.0 5.3 V

255 300 345 KHz

540 600 660 KHz

-15 +15 %

0.5 V

2.5

80 85 dB

ms

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN21SV06 Rev. 1.0.1 5

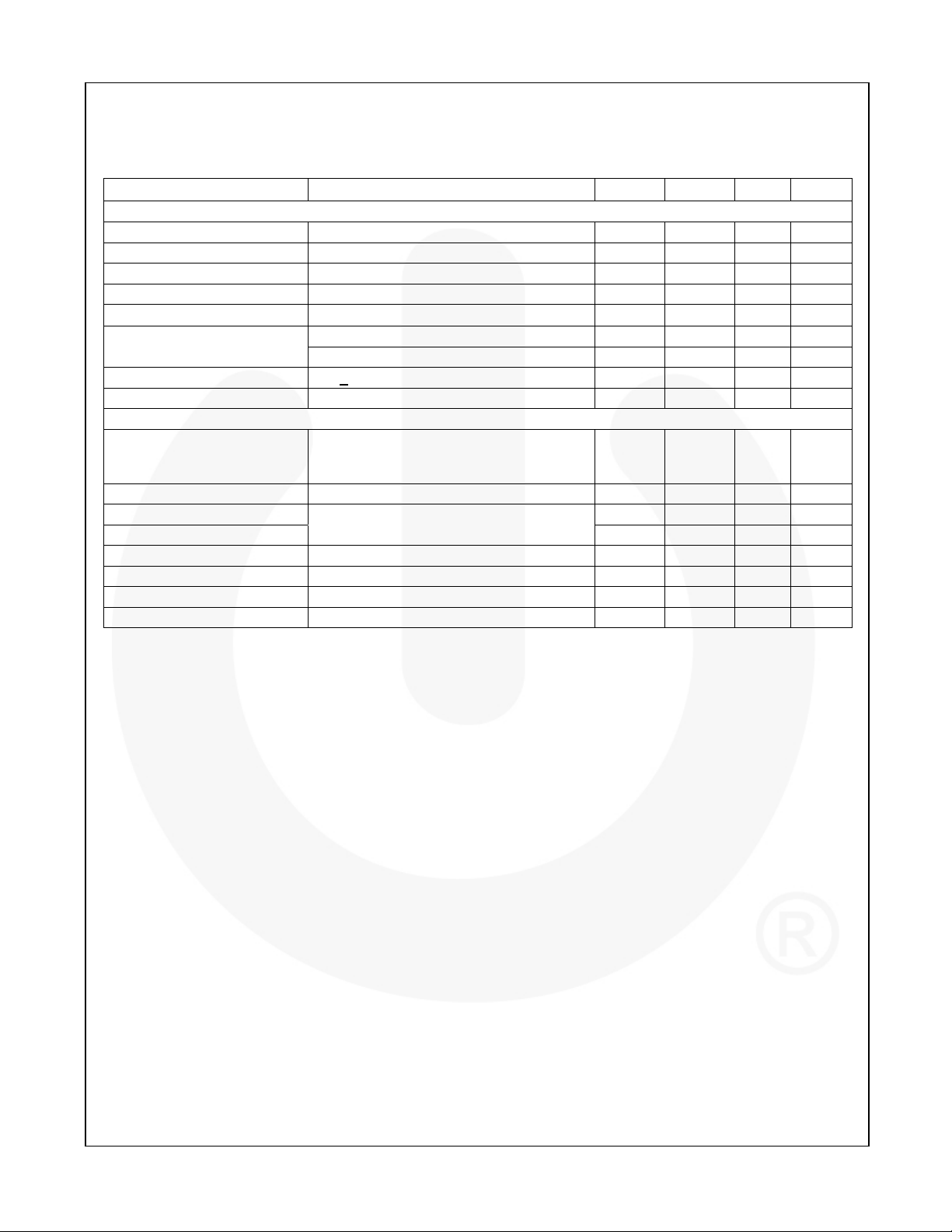

Electrical Characteristics (Continued)

Recommended operating conditions using the circuit in Figure 1 with V

Parameter Conditions Min. Typ. Max. Units

Control Functions

EN Threshold, Rising 1.35 2.00 V

EN Hysteresis 250 mV

EN Pull-Up Current VIN_Reg >6.5V -8 -6 -4 µA

EN Discharge Current Auto-Restart Mode, VIN_Reg>6.5V 1 µA

FB OK Drive Resistance 800 1000

PGOOD LOW Threshold

PGOOD Low Voltage I

PGOOD Leakage Current V

FB < V

FB > V

OUT

PGOOD

Protection and Shutdown

R

Current Limit

ILIM

Rramp=200k16 Consecutive Clock

Cycles

I

Current VIN_Reg > 6.5V, 25°C -11 -10 -9 µA

LIM

Over-Temperature Shutdown

Over-Temperature Hysteresis 30 °C

Internal Temperature

Over-Voltage Threshold 2 Consecutive Clock Cycles

Under-Voltage Shutdown 16 Consecutive Clock Cycles

Fault-Discharge Threshold Measured at FB pin 250 mV

Fault-Discharge Hysteresis Measured at FB pin (VFB ~500mV) 250 mV

Note:

3. Delay times are not tested in production. Guaranteed by design.

, 2 Consecutive Clock Cycles

REF

, 2 Consecutive Clock Cycles

REF

< 2mA 0.4 V

=5V 0.2 1.0 µA

open, fsw=500KHz,, V

(3)

=1.8V,

OUT

(3)

110 115 120 %V

(3)

68 73 78 %V

, VIN_Reg=12V, unless otherwise noted.

IN

(3)

-14.5 -11.0 -8.0 %V

(3)

+6.5 +10.0 +13.5 %V

7 9 11 A

155 °C

K

REF

REF

OUT

OUT

FAN21SV06 — TinyBuck™ 6A, 24V Single-Input Integrated Synchronous Buck Regulator, Synchronization Capability

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN21SV06 Rev. 1.0.1 6

Loading...

Loading...