查询DM74ALS521供应商

DM74ALS520 • DM74ALS521

8-Bit Comparator

DM74ALS520 • DM74ALS521 8-Bit Comparator

September 1986

Revised April 2000

General Description

These comparators per form an “equal to” comparison of

two 8-bit words with provision for expansion or external

enabling. The matc hing of the two 8-bit input plus a logic

LOW on the EN

DM74ALS520 and DM74ALS521. The DM74ALS520 and

DM74ALS521 have totem pole outputs for wire AND cascading. Additionally, the DM74ALS520 is provided with B

input pull up termination resistors for analog or switch data.

input produces t he output A = B on the

Features

■ Switching specifications at 50 pF

■ Switching specifications guaranteed over full tempera-

ture and V

■ Advanced oxide-isolated, ion-implanted Schottky TTL

process

■ Functionally and pin for pin compatible with LS fam ily

counterpart

■ Improved output transient handling capability

CC

range

Ordering Code:

Ordering Code Package Number Package Description

DM74ALS520WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74ALS520N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

DM74ALS521WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

SM74ALS521N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab l e in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

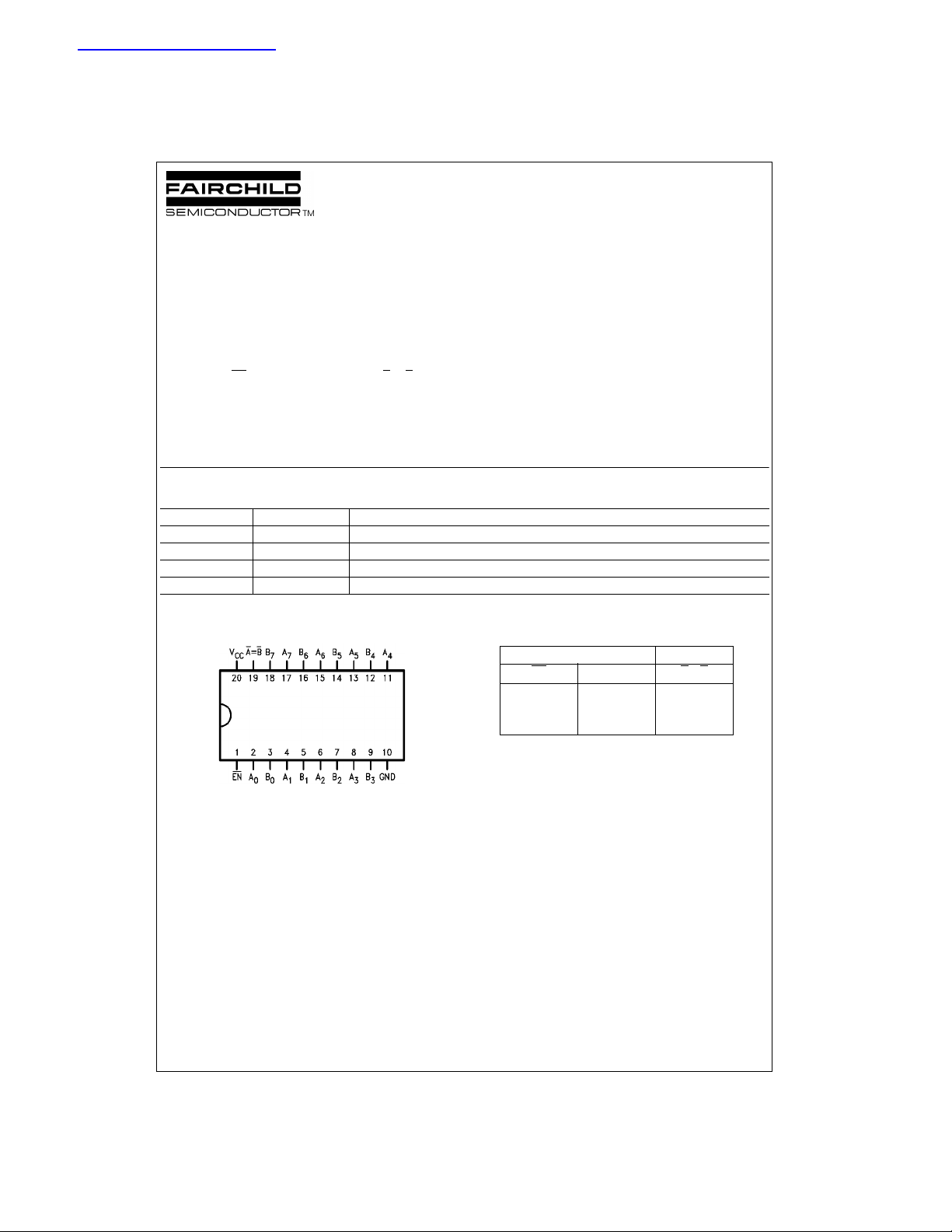

Connection Diagram Function Table

Inputs Output

EN

LA = BL

LA ≠ BH

H = HIGH Logic Level

L = LOW Logic Level

X = Don't Care

HXH

Data A = B

© 2000 Fairchild Semiconductor Corporation DS006114 www.fairchildsemi.com

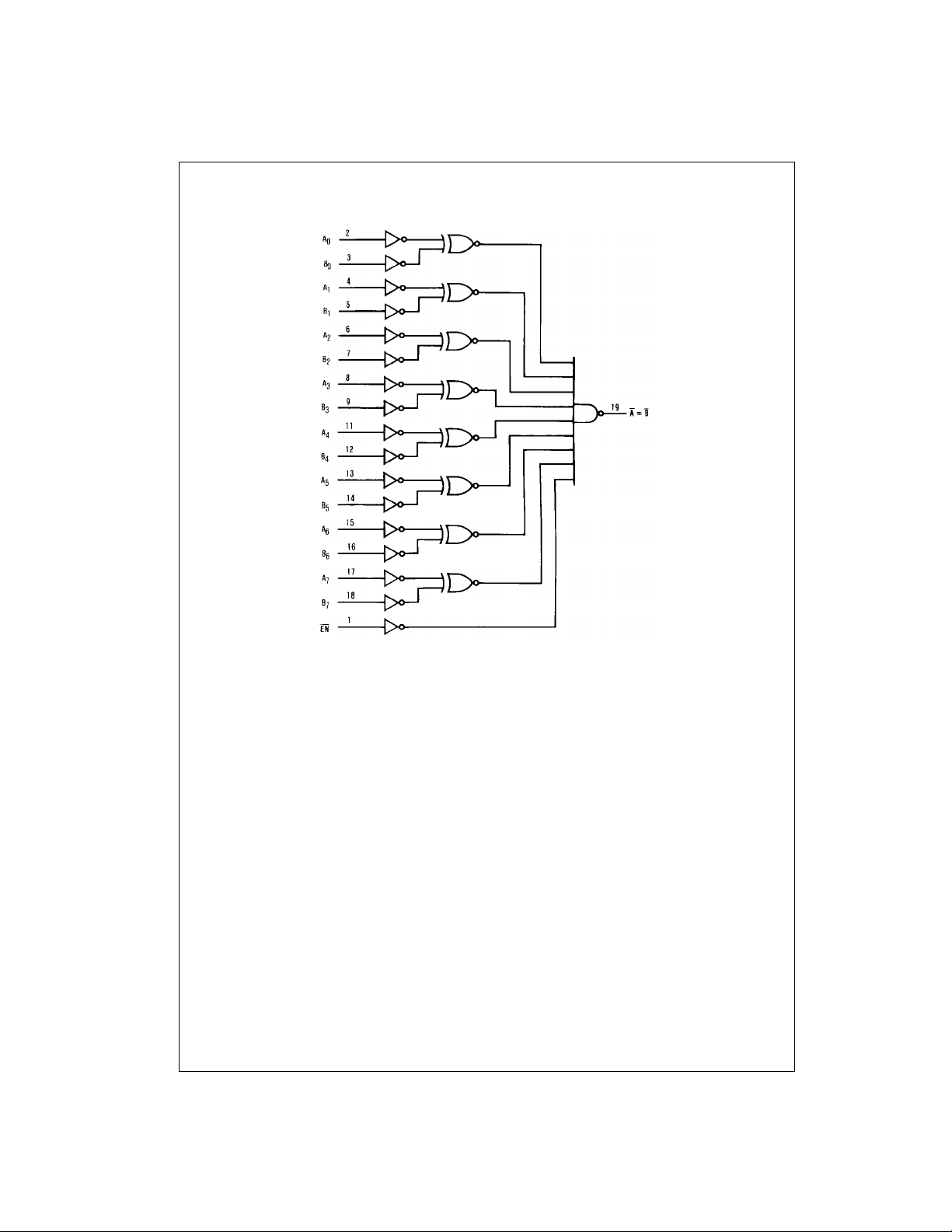

Logic Diagram

DM74ALS520 • DM74ALS521

www.fairchildsemi.com 2

Loading...

Loading...