Fairchild 74LVTH125 service manual

74LVTH125 — Low Voltage Quad Buffer with 3-STATE Outputs

January 2008

74LVTH125

Low Voltage Quad Buffer with 3-STATE Outputs

Features

■

Input and output interface capability to systems at

5V V

CC

■

Bushold data inputs eliminate the need for external

pull-up resistors to hold unused inputs

Live insertion/extraction permitted

■

■

Power Up/Down high impedance provides glitch-free

bus loading

Outputs source/sink –32mA/+64mA

■

■

Functionally compatible with the 74 series 125

Latch-up performance exceeds 500mA

■

■

ESD performance:

– Human-body model > 2000V

– Machine model > 200V

– Charged-device model> 1000V

General Description

The LVTH125 contains four independent non-inverting

buffers with 3-STATE outputs.

These buffers are designed for low-voltage (3.3V) V

applications, but with the capability to provide a TTL

interface to a 5V environment. The LVTH125 is fabricated with an advanced BiCMOS technology to achieve

high speed operation similar to 5V ABT while maintaining a low power dissipation.

Ordering Information

Package

Order Number

74LVTH125M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

74LVTH125SJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74LVTH125MTC MTC14 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number.

Number Package Description

Wide

CC

All packages are lead free per JEDEC: J-STD-020B standard.

©1998 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LVTH125 Rev. 1.4.0

H =

74LVTH125 — Low Voltage Quad Buffer with 3-STATE Outputs

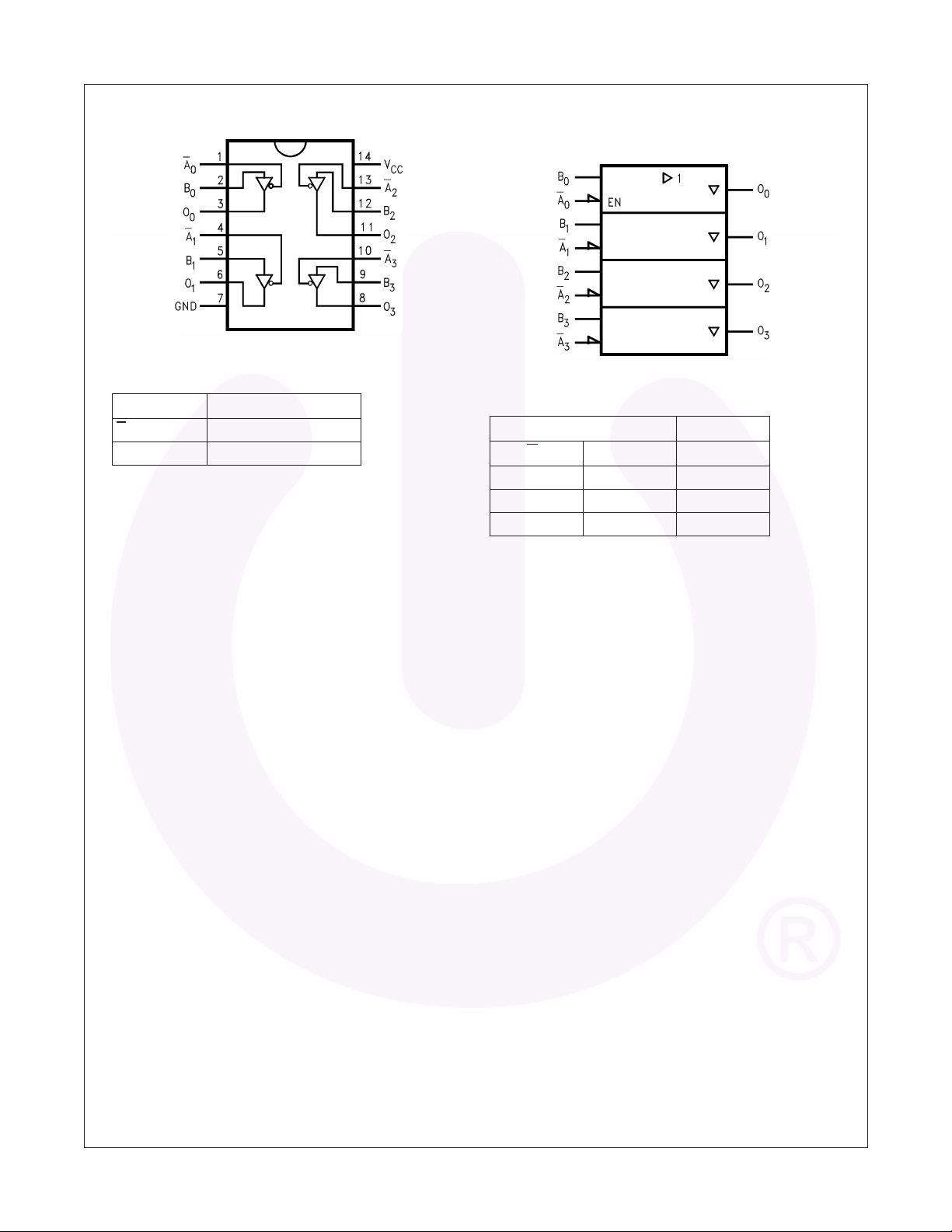

Connection Diagram

Pin Description

Pin Names Description

A

, B

n

n

O

n

Inputs

3-STATE Outputs

Logic Symbol

IEEE/IEC

Truth Table

Inputs Output

A

n

LLL

LHH

HXZ

HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = HIGH Impedance

B

n

O

n

©1998 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LVTH125 Rev. 1.4.0 2

<

<

>

∆

∆

=

=

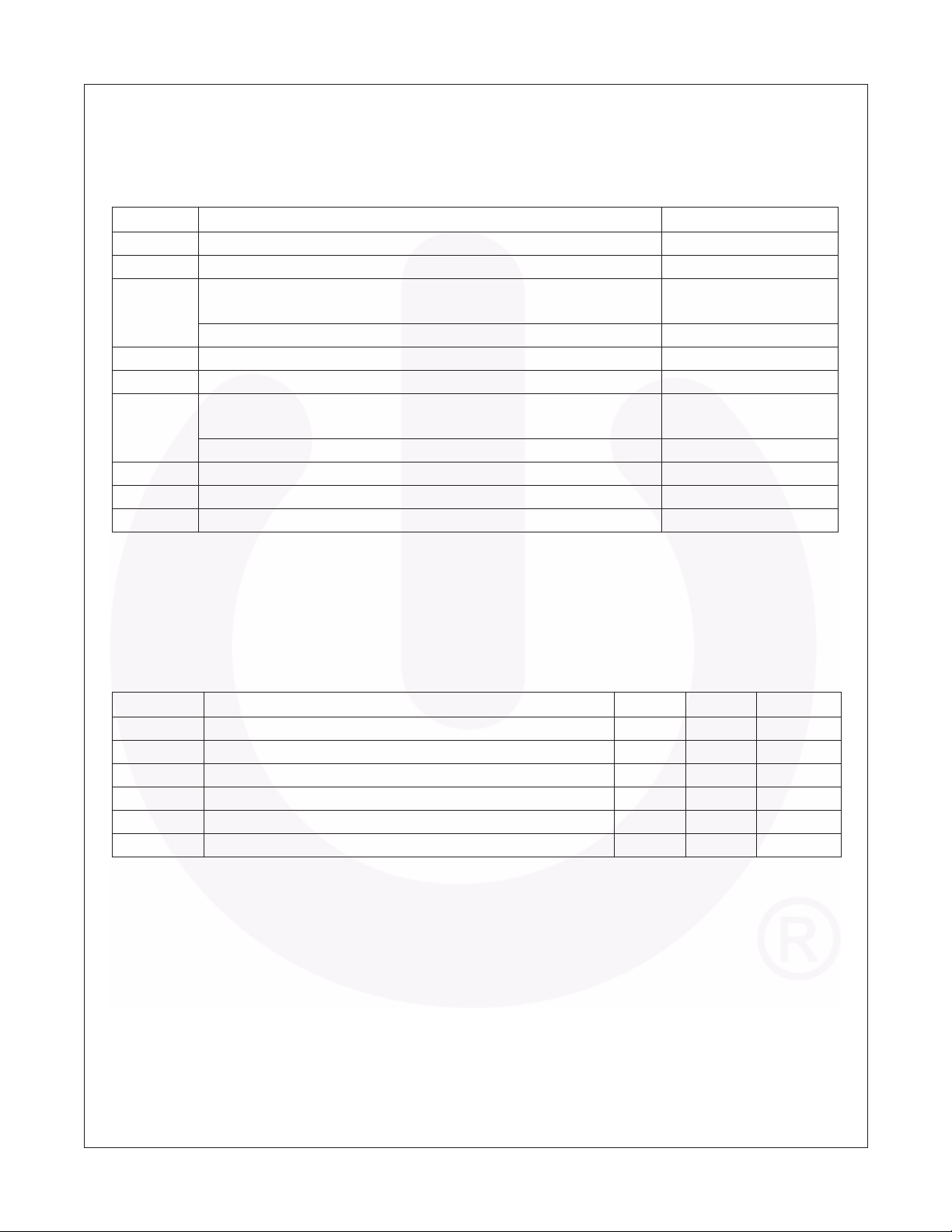

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Rating

V

CC

V

V

O

I

IK

I

OK

I

O

I

CC

I

GND

T

STG

Note:

1. I

Absolute Maximum Rating must be observed.

O

Supply Voltage –0.5V to +4.6V

DC Input Voltage –0.5V to +7.0V

I

DC Output Voltage

Output in 3-STATE –0.5V to +7.0V

Output in HIGH or LOW State

DC Input Diode Current, V

DC Output Diode Current, V

DC Output Current, V

V

O

(1)

GND –50mA

I

GND –50mA

O

CC

Output at HIGH State 64mA

Output at LOW State 128mA

DC Supply Current per Supply Pin ±64mA

DC Ground Current per Ground Pin ±128mA

Storage Temperature –65°C to +150°C

–0.5V to +7.0V

74LVTH125 — Low Voltage Quad Buffer with 3-STATE Outputs

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to absolute maximum ratings.

Symbol Parameter Min Max Units

V

CC

V

I

I

OH

I

OL

T

A

t

/

Supply Voltage 2.7 3.6 V

Input Voltage 0 5.5 V

HIGH-Level Output Current –32 mA

LOW-Level Output Current 64 mA

Free-Air Operating Temperature –40 85 °C

V Input Edge Rate, V

0.8V–2.0V, V

IN

3.0V 0 10 ns/V

CC

©1998 Fairchild Semiconductor Corporation www.fairchildsemi.com

74LVTH125 Rev. 1.4.0 3

Loading...

Loading...