Fairchild 74LVT162244 service manual

74LVT162244 • 74LVTH162244

Low Voltage 16-Bit Buffer/Line Driver

with 3-STAT E Outputs

and 25: Series Resistors in the Outputs

March 1999

Revised June 2005

74LVT162244 • 74LVTH162244 Low Voltage 16-Bit Buffer/Line Driver with 3-STATE Outputs and 25: Series

Resistors in the Outputs

General Description

The LVT162244 and LVTH162244 contain sixteen noninverting buffers with 3-STATE outputs designed to be

employed as a memor y an d ad dr ess d rive r, clock driver, or

bus oriented transm itter /re cei ve r. The device is n i bble co ntrolled. Individual 3-STATE control inputs can be shorted

together for 8-bit or 16-bit operation.

The LVT162244 and LVTH162244 are designed with

equivalent 25

LOW states of the output. This design reduces line noise in

applications such as memory address drivers, cl ock drivers, and bus transceivers/transmitters.

The LVTH162244 data inputs include bushold, eliminat ing

the need for external pull-up resistors to hold unused

inputs.

These buffers and line drivers are de signed for low-voltage

(3.3V) V

TTL interface to a 5V en vironment. The LVT162244 and

LVTH162244 are fabricated with an advanced BiCMOS

technology to achieve high speed ope ration similar to 5V

ABT while maintaining a low power dissipation.

:

series resistance in both the HIGH and

applications, but with the capability to provide a

CC

Features

■ Input and output interface capability to systems at

5V V

CC

■ Bushold data inputs elimina te the ne ed for externa l pull -

up resistors to hold unused inputs (74LVTH162244),

also available without bushold feature (74LVT162244).

■ Live insertion/extraction per mi tt ed

■ Power Up/Power Do wn high imp edance provid es gli tch-

free bus loading

■ Outputs include equiva lent series resistance of 25

make external termination resistors unnecessary and

reduce overshoot and undershoot

■ Functionally compatible with the 74 series 162244

■ Latch-up performance exce eds 500 mA

■ ESD performance:

Human-body model

Machine model

Charged-device

■ Also packaged in plastic Fine-Pitch Ball Grid Array

(FBGA)

!

200V

!

1000V

!

2000V

:

to

Ordering Code:

Order Number

74LVT162244G

(Note 1)(Note 2)

74LVT162244MEA

(Note 2)

74LVT162244MTD

(Note 2)

74LVTH162244G

(Note 1)(Note 2)

74LVTH162244MEA MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

74LVTH162244MEX MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

74LVTH162244MTD MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

74LVTH162244MTX MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Note 1: Ordering code “G” indicates Trays.

Note 2: Devices also available in Tape and Reel. Specify by appending the suffix let te r “X” to the ordering code.

Package

Number

BGA54A 54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

BGA54A 54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

[Tube]

[Tape and Reel]

[Tube]

[Tape and Reel]

Package Description

© 2005 Fairchild Semiconductor Corporation DS012445 www.fairchildsemi.com

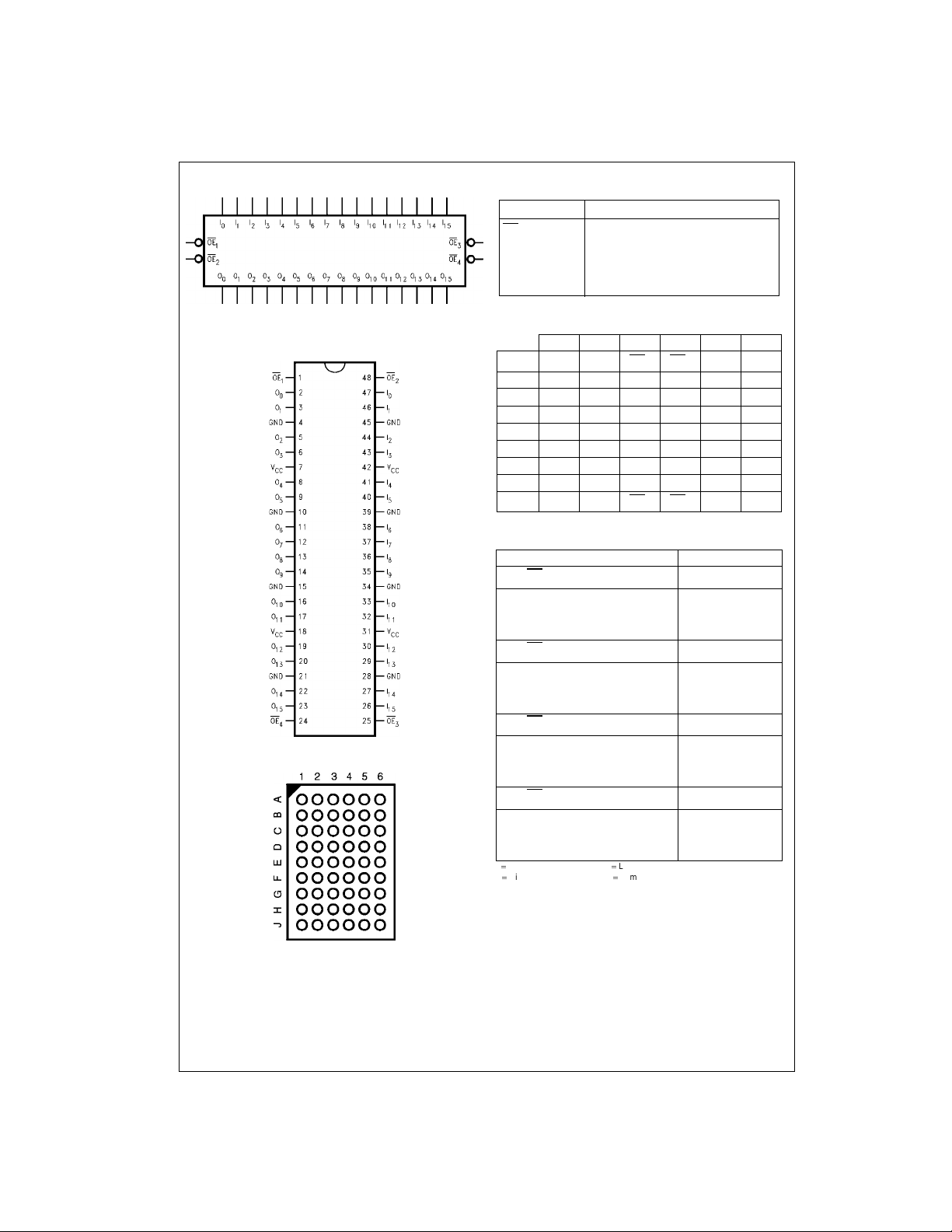

Logic Symbol

Pin Descriptions

Pin Names Description

OE

n

I

0–I15

O

0–O15

NC No Connect

Output Enable Inputs (Active LOW)

Inputs

Outputs

Connection Diagrams

Pin Assignment for SSOP and TSSOP

74LVT162244 • 74LVTH162244

Pin Assignment for FBGA

FBGA Pin Assignments

123456

A O

B O

C O

D O

E O

F O

G O

H O

J O

NC OE1OE2NC I

0

O1NC NC I

2

O3V

4

6

8

10

12O11VCCVCCI11

14O13

15

CCVCCI3

O5GND GND I

O7GND GND I

O9GND GND I

NC NC I

NC OE4OE3NC I

1

5

7

9

13I14

Truth Table

Inputs Outputs

OE

1

LL L

LH H

HX Z

OE

2

LL L

LH H

HX Z

OE

3

LL L

LH H

HX Z

OE

4

LL L

LH H

HX Z

H HIGH Voltage Level L LOW Voltage Level

High Impedance X Immaterial

Z

I0–I

I4–I

I8–I

I12–I

3

7

11

15

O0–O

O4–O

O8–O

O12–O

0

I

2

I

4

I

6

I

8

I

10

I

12

15

3

7

11

15

(Top Thru View)

www.fairchildsemi.com 2

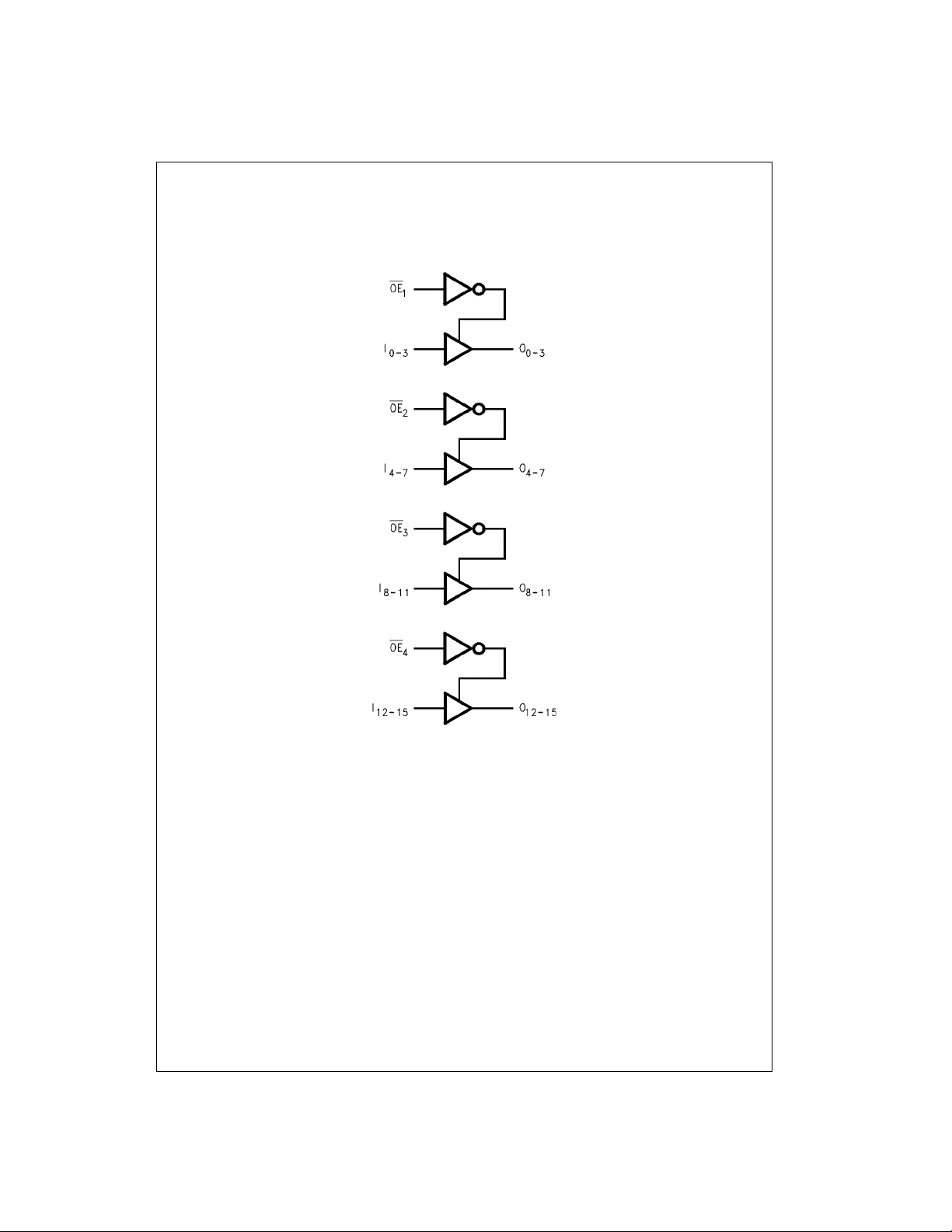

Functional Description

The LVT162244 and LVTH162244 contain sixteen non-inverting buffers with 3-STATE outputs. The device is nibble (4 bits)

controlled with each nibble functioning identically, but independent of the other. The control pins can be shorted together to

obtain full 16-bit operation.

Logic Diagram

74LVT162244 • 74LVTH162244

3 www.fairchildsemi.com