Fairchild 74F401 service manual

74F401

CRC Generator/Checker

74F401 CRC Generator/Checker

April 1988

Revised August 1999

General Description

The 74F401 Cycle Red undancy Check (CRC) Generato r/

Checker provides an advance d tool for implementing the

most widely used er ror detection scheme in serial digital

data handling systems. A 3-bit contr ol inpu t sele cts on e-o feight generator polynomials. The list of polynomials

includes CRC-16 and CRC-CCITT as well as their reciprocals (reverse polynomials). Automatic right justification is

incorporated for polynom ial s o f deg ree l ess th an 1 6. Sep arate clear and preset inpu ts are provided for floppy disk

and other applicat ions. Th e Error ou tput ind icates wheth er

or not a transmission error has occurred. An other control

input inhibits feedback during check word transmission.

The 74F401 is fully compatible with all TTL families.

Features

■ Eight selectable polynomials

■ Error indicator

■ Separate preset and clear controls

■ Automatic right justification

■ Fully compatible with all TTL logic families

■ 14-pin package

■ 9401 equivalent

■ Typical applications:

Floppy and other disk storage systems

Digital cassette and cartridge systems

Data communication systems

Ordering Code:

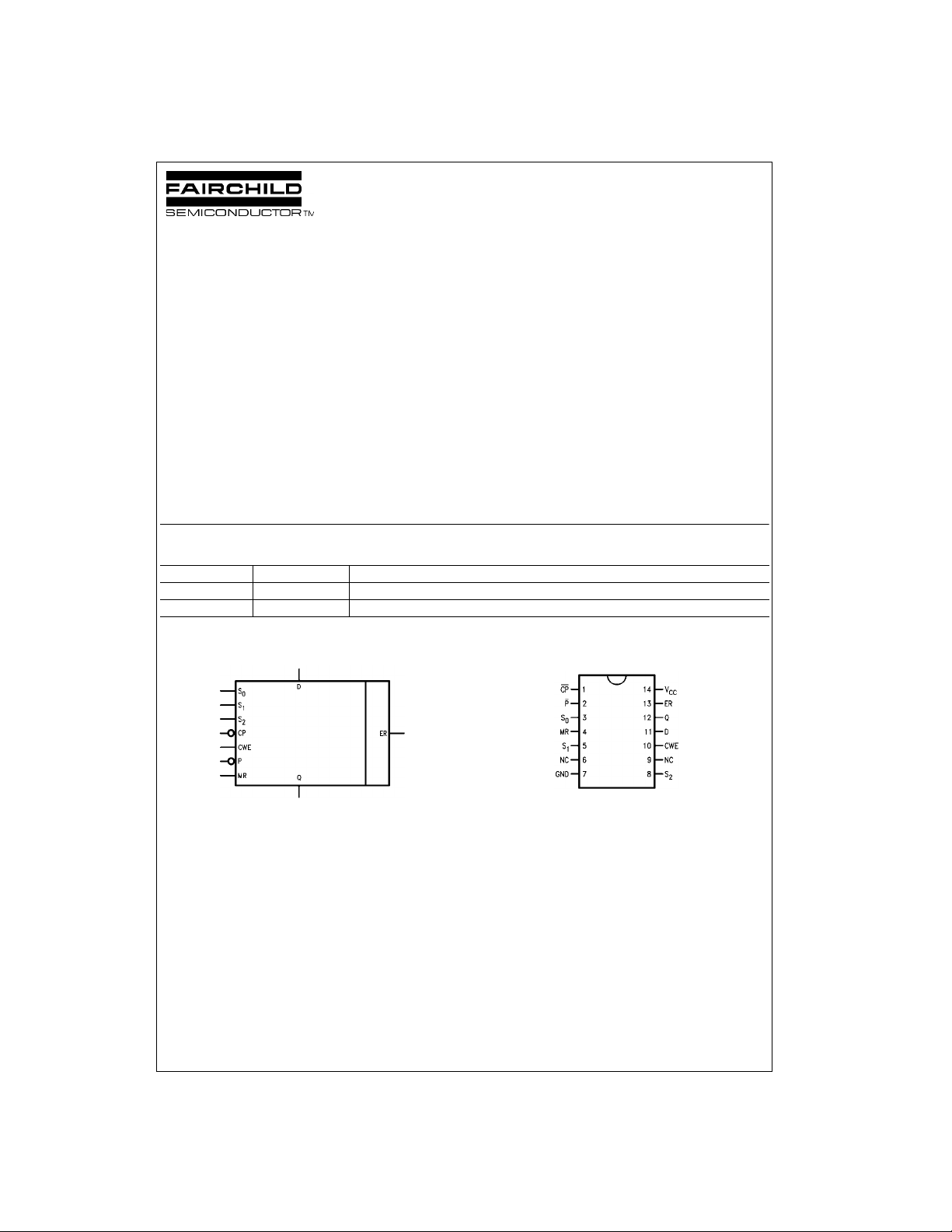

Order Number Package Number Package Description

74F401SC M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

74F401PC N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

Logic Symbol Connection Diagram

© 1999 Fairchild Semiconductor Corporation DS009534 www.fairchildsemi.com

Unit Loading/Fan Out

74F401

Pin Names Description

S0–S

2

Polynomial Select Inputs 1.0/1.0 20 µA/−0.6 mA

D Data Input 1.0/1.0 20 µA/−0.6 mA

CP

Clock Input (Operates on HIGH-to-LOW Transition) 1.0/1.0 20 µA/−0.6 mA

CWE Check Word Enable Input 1.0/1.0 20 µA/−0.6 mA

P

Preset (Active LOW) Input 1.0/1.0 20 µA/−0.6 mA

MR Master Reset (Active HIGH) Input 1.0/1.0 20 µA/−0.6 mA

Q Data Output 50/33.3 −1 mA/20 mA

ER Error Output 50/33.3 −1 mA/20 mA

Functional Description

The 74F401 is a 16-bit progr ammable device w hich operates on serial data streams and provides a means of

detecting transmission er rors. Cyclic encod ing and decoding schemes for err or detection are based on poly nomial

manipulation in m odulo arithmetic . For encoding , the data

stream (message polynomial) is divided by a selected polynomial. This division results in a remainder which is

appended to the messa ge as check bits. For err or checking, the bit stream conta ining both data and check bits is

divided by the same select ed polynomial. If there are no

detectable errors, this di vision results in a ze ro remainder.

Although it is possible to choose many generating polynomials of a given degree, standards exist that specify a

small number of useful polynomials. The 74F401 implements the polynomials listed in Table 1 by applying the

appropriate logic levels to the select pins S

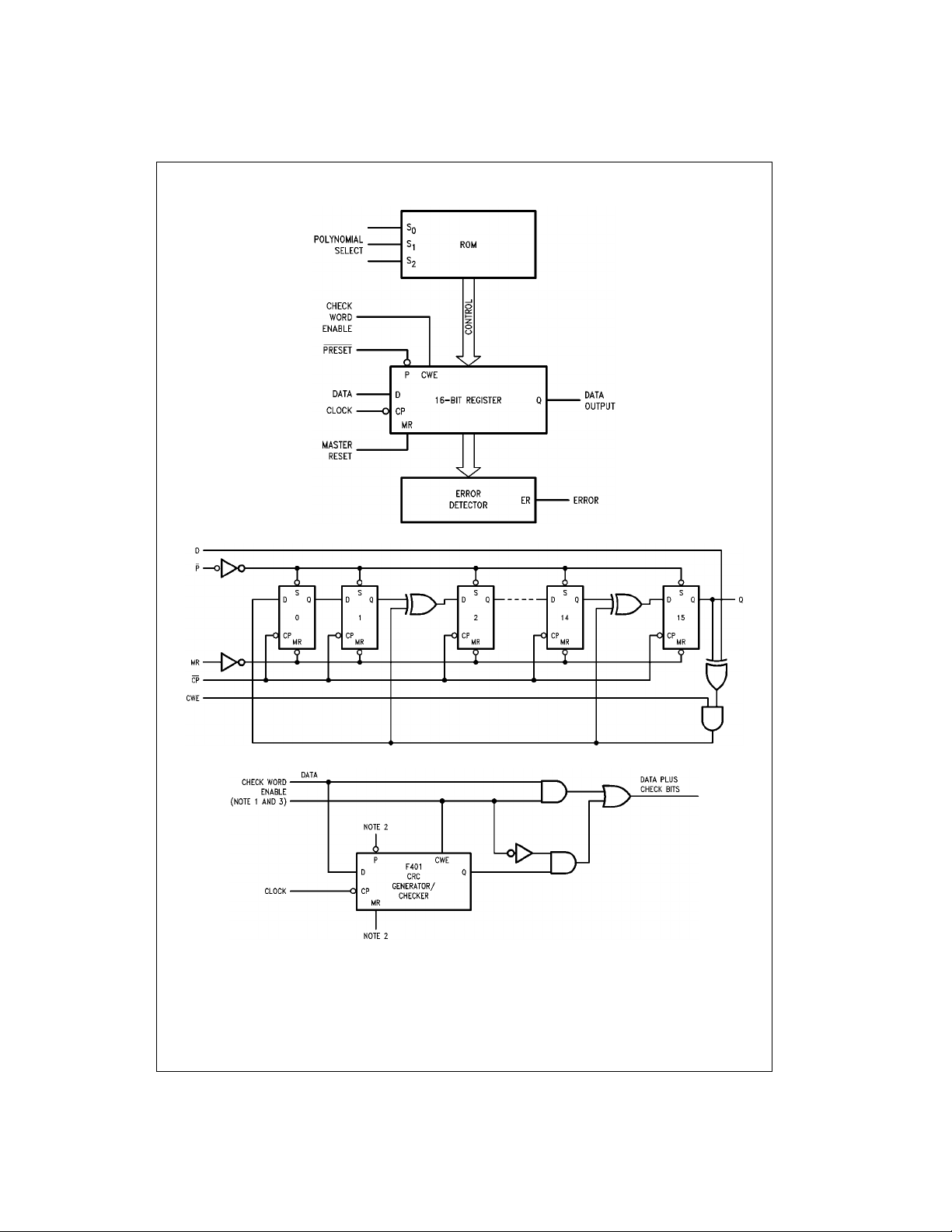

The 74F401 consists of a 16-bit register, a Read Only

Memory (ROM) and associated control circuitry as show n

in the block diagram. The polynomial control code presented at inputs S

, S1 and S2 is decoded by the ROM,

0

selecting the desired polynomial by establishing shift mode

operation on the register with Exclusive OR gates at appropriate inputs. To generate the check bits, the data stream is

entered via the Da ta inputs (D), using the HIGH- to-LOW

0, S1

and S2.

U.L.

HIGH/LOW

transition of the Clock inpu t (CP

Input I

IH/IIL

Output I

OH/IOL

). This data is gate d with

the most significant output (Q ) of the register, and controls

the Exclusive OR gates Figu re 1. Th e Ch eck Word Enabl e

(CWE) must be held HIGH wh i le th e da ta i s b ei ng en ter ed.

After the last data bit is entered, the CWE is brou ght LOW

and the check bits are shifted out of the register and

appended to the data bits using external gating Figure 2.

To check an incoming messa ge for errors, both the data

and check bits are e ntered through the D input w ith the

CWE input held HIGH. The 74F4 01 is not in the data path,

but only monitors the message. The Error Output becomes

valid after the last check bit has been entered into the

74F401 by a HIGH-to-LOW tra nsition of CP

. If no detectable errors have occurred during the data transmission, the

resultant internal reg ister bits are all LOW and the Error

Output (ER) is LOW. If a detectable error has occurred, ER

is HIGH.

A HIGH on the Master Reset input (MR) asynchronously

clears the register. A LOW on the Preset input (P

) asynchronously sets the entire register if the control code inputs

specify a 16-bit polynomial; in the case of 12- or 8-bit check

polynomials only th e most significa nt 12 or 8 regist er bits

are set and the remaining bits are cleared.

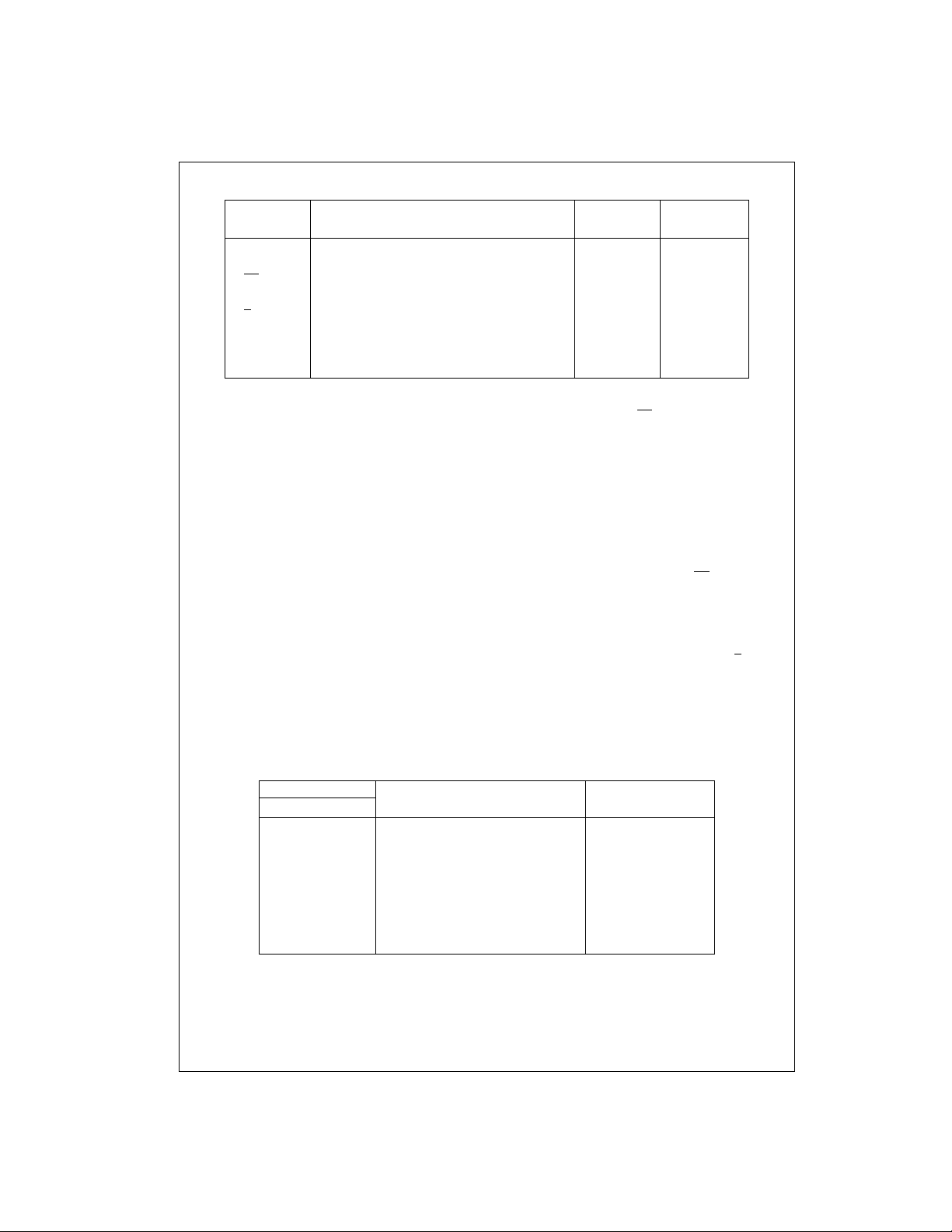

TABLE 1.

Select Code

S

2

S

S

1

0

Polynomial Remarks

LLLX16 + X15 + X2 + 1 CRC-16

16

LLHX

LHLX

LHHX

HLLX

HLHX

HHLX

HHHX

+ X14 + X + 1 CRC-16 REVERSE

16

+ X15 + X13 + X7 + X4 + X2 + X1 + 1

12

+ X11 + X3 + X2 + X + 1 CRC-12

8

+ X7 + X5 + X4 + X + 1

8

+ 1 LRC-8

16

+ X12 + X5 + 1 CRC-CCITT

16

+ X11 + X4 + 1 CRC-CCITT REVERSE

www.fairchildsemi.com 2

Block Diagram

74F401

FIGURE 1. Equivalent Circuit for X16 + X15 + X2 + 1

Note 1: Check word En able is HIGH while data is being clocked, LOW while transmission of ch ec k bit s .

Note 2: 74F401 must be reset or preset before each computation.

Note 3: CRC check bits are generated and appended to data bits.

FIGURE 2. Check Word Generation

3 www.fairchildsemi.com

Loading...

Loading...