Fairchild 74F157A service manual

查询74F157A供应商

74F157A

Quad 2-Input Multiplexer

General Description

The F157A is a high- speed quad 2-input mul tiplexer. Four

bits of data from two sources can be selected using the

common Select and Enable inputs. The four outputs

present the selected data in the true (non-inverted) form.

The F157A can also be used to generate any four of the 16

different functions to two variables.

Ordering Code:

Order Number Package Number Package Description

74F157ASC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F157ASJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F157APC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab le in Tape and Reel. Specify by appending the suffix letter “X” to the o rdering code.

74F157A Quad 2-Input Multiplexer

April 1988

Revised September 2000

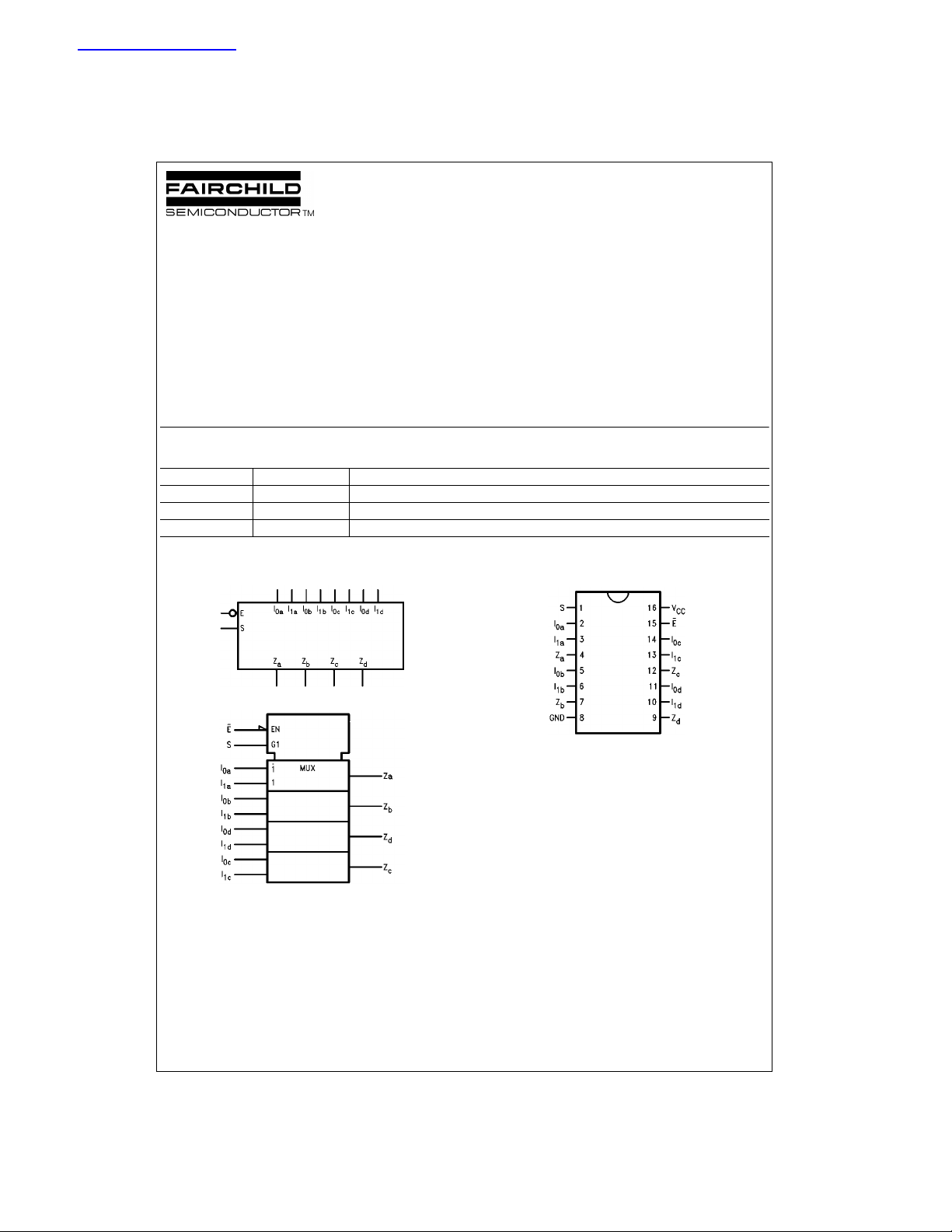

Logic Symbols

Connection Diagram

IEEE/IEC

© 2000 Fairchild Semiconductor Corporation DS009483 www.fairchildsemi.com

Unit Loading/Fan Out

74F157A

Pin Names Description

I0a–I

0d

I

1a–I1d

E

S Select Input 1.0/1.0 20

Z

a–Zd

U.L.

HIGH/LOW

Source 0 Data Inputs 1.0/1.0 20 µA/−0.6 mA

Source 1 Data Inputs 1.0/1.0 20 µA/−0.6 mA

Enable Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

Outputs 50/33.3 −1 mA/20 mA

Input I

Output I

µA/−0.6 mA

IH/IIL

OH/IOL

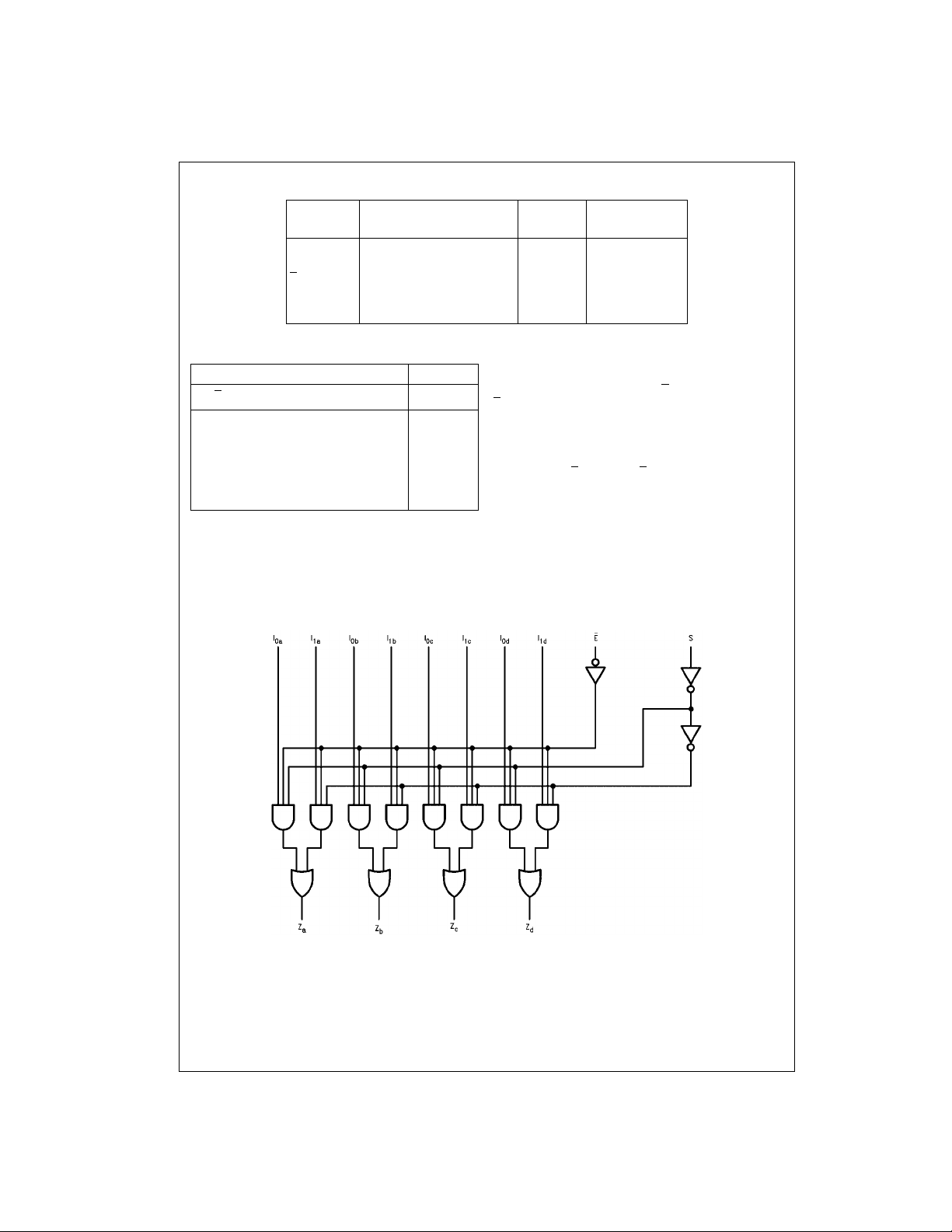

Truth Table

Inputs Output

E

HXXX L

LHXL L

LHXH H

LLLX L

LLHX H

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

S

I

0

I

1

Logic Diagram

Functional Description

The F157A is a quad 2-input mul tipl e xer. It selects four bits

of data from two sources under the contr ol of a common

Z

Select input (S). The Enable input (E

E

is HIGH, all of the outputs (Z) are forced LOW regardless

of all other inputs. The F157A is the logic implementation of

a 4-pole, 2-position swit ch whe re the po sition of th e switch

is determined by the logic levels supplied to the Select

input. The logic equations for the outputs are shown below:

Z

= E • (I1nS + I0n S)

A common use of the F157A is the moving of data from two

groups of registers to four common output busses. The

particular register from which the data comes is determined

by the state of t he S elect in put . A less obvi ous us e is as a

function generator. The F1 57A can generate any four of

the 16 different functions of two vari a bles wi th one var iable

common. This is usef ul for implementing highly irregular

logic.

n

) is active LOW. When

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com 2

Loading...

Loading...