Fairchild 74F148 service manual

查询74F148供应商

74F148

8-Line to 3-Line Priority Encoder

74F148 8-Line to 3-Line Priority Encoder

April 1988

Revised July 1999

General Description

The F148 provide s th re e b its of binary coded out put re presenting the positio n o f t he high est order active inp ut, alo ng

with an out p ut in di ca t i ng t he p re s en ce o f an y act i ve i np ut. I t

is easily expanded via i nput and o utput enable s to p rovi de

priority encoding over many bit s.

Features

■ Encodes eight data lines in priority

■ Provides 3-bit binary priority code

■ Input enable capability

■ Signals when data is p r esent on any input

■ Cascadable for priority encoding of n bits

Ordering Code:

Order Number Package Number Package Description

74F148SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F148SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F148PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

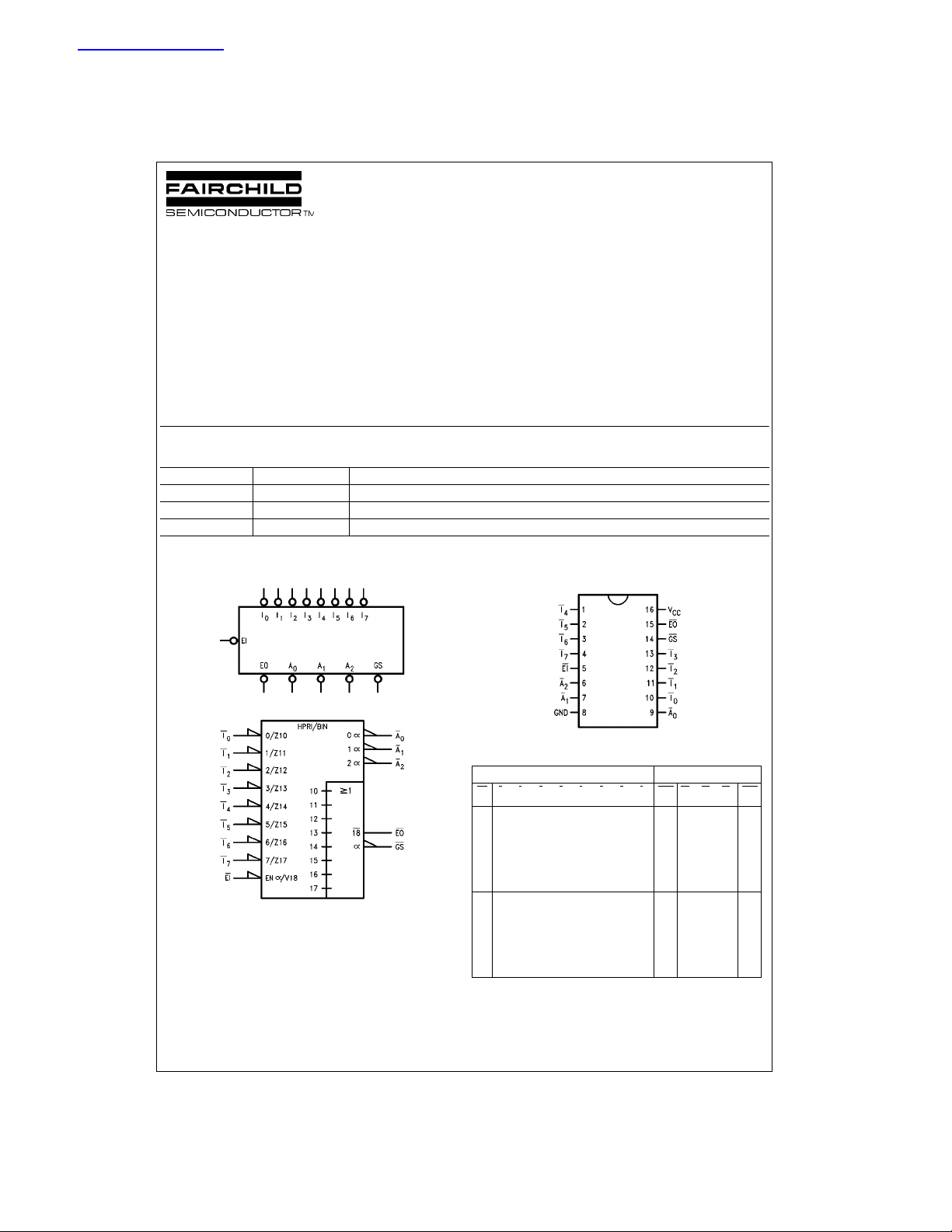

Logic Symbols

IEEE/IEC

Connection Diagram

Truth Table

Inputs Outputs

I0I1I2I3I4I5I6I7GS A0A1A2EO

EI

HXXXXXXXXHHHHH

LHHHHHHHHH HHH L

LXXXXXXXL LLLLH

LXXXXXXLH L HLL H

LXXXXXLHH L LHLH

LXXXXLHHHL HHLH

LXXXLHHHHL LLHH

LXXLHHHHH LHLHH

LXLHHHHHH L LHH H

LLHHHHHHH LHHH H

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

© 1999 Fairchild Semiconductor Corporation DS009480 www.fairchildsemi.com

Unit Loading/Fan Out

74F148

Pin Names Description

I

0

I

1–I7

EI

EO

GS

A

0–A2

Priority Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

Priority Inputs (Active LOW) 1.0/2.0 20 µA/−1.2 mA

Enable Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

Enable Output (Active LOW) 50/33.3 −1 mA/20 mA

Group Signal Output (Active LOW) 50/33.3 −1 mA/20 mA

Address Outputs (Active LOW) 50/33.3 −1 mA/20 mA

Functional Description

The F148 8-input priority e ncoder accept s data from eight

active LOW inputs (I

tation on the three active LOW outputs. A priority is

assigned to each input so that when two or more inputs are

simultaneously acti ve, the input with the hi ghest priority is

represented on the output, with input line 7 having the highest priority. A HIGH on the Enable Input (EI

outputs to the inactive ( HIGH) state and allow new data to

settle without pr oducing erroneous information at the out-

) and provides a binary repr esen-

0–I7

) will force all

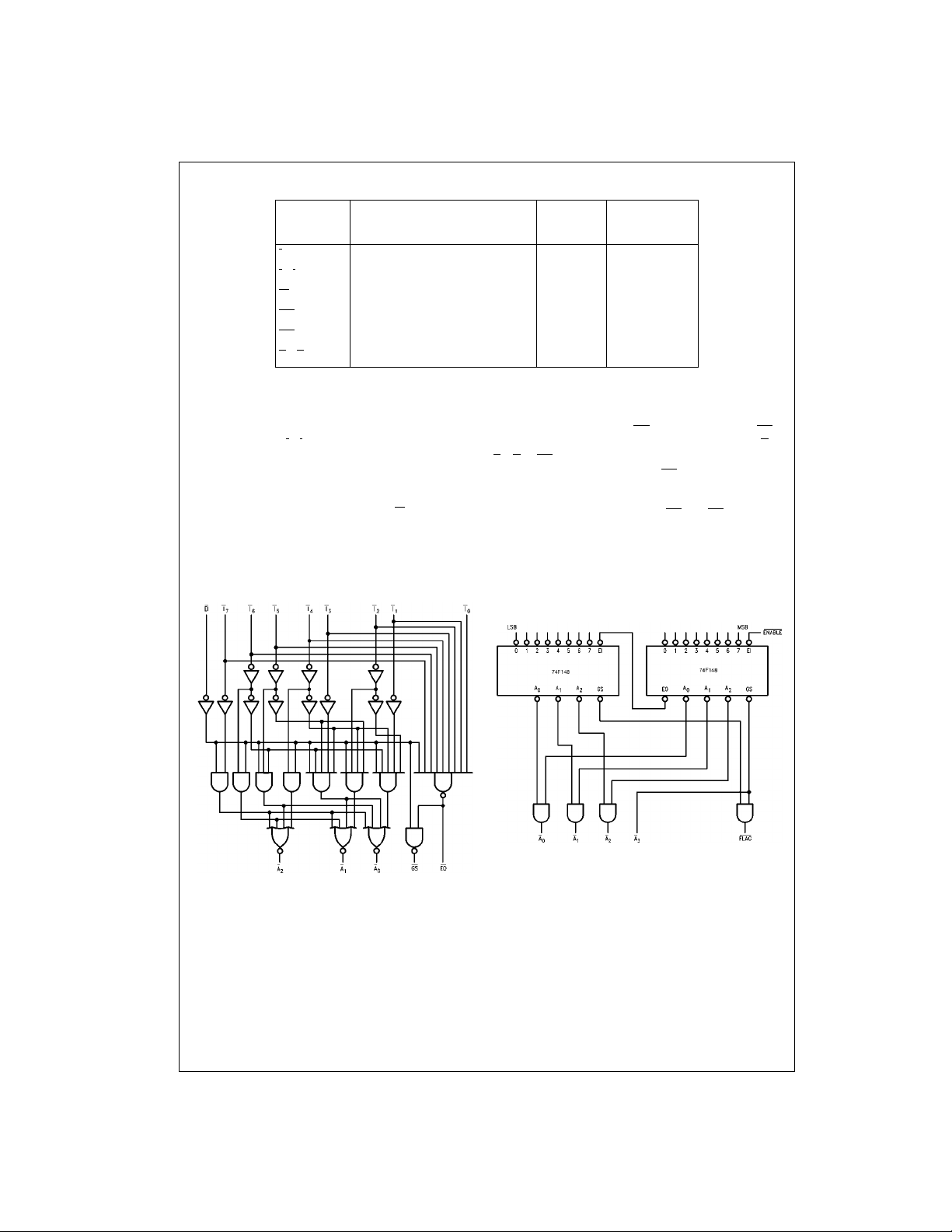

Logic Diagram

U.L.

HIGH/LOW

puts.A Group Signal outp ut (GS

are provided along with the three priority data outputs (A

, A0). GS is active LOW when any input is LOW: this

A

1

indicates when any input is active. EO

all inputs are HIGH. Us ing the Enable Output along with

the Enable Input allows cas cading for priority en coding on

any number of inp ut signals. Both EO

inactive HIGH state when the Enable Input is HIGH.

Input I

IH/IIL

Output I

OH/IOL

) and Enable Output ( EO)

is active LOW when

and GS are in the

Application

16-Input Priority Encoder

,

2

Please note that this diagram is provided only for the understanding of logic

operations and should not be used to est im at e propagation delays .

www.fairchildsemi.com 2

Loading...

Loading...