Fairchild 74F132 service manual

查询74F132供应商

74F132

Quad 2-Input NAND Schmitt Trigger

74F132 Quad 2-Input NAND Schmitt Trigger

April 1988

Revised July 1999

General Description

The F132 contains four 2-input NAND gates which accept

standard TTL input signal s and provide standard TTL ou tput levels. They are c apable o f transf orming slowly ch anging input signals into sharply defined, jitter-free output

signals. In addition, they have a gre ater noise mar gin than

conventional NAND gates.

Each circuit contains a 2-input Sch mitt Trigger fol lowed by

level shifting circuitry and a sta ndard FAST output struc-

ture. The Schmitt Trigger uses positive feedback to effectively speed-up slow inp ut t ran siti on s, an d p rov ide d ifferen t

input threshold voltages for positive and negative-going

transitions. This hyst ere sis b etw e en th e pos iti ve- goin g and

negative-going input threshold (ty pically 800 mV) is determined by resistor ratios and is essentially insensitive to

temperature and supply voltage variations.

Ordering Code:

Order Number Package Number Package Description

74F132SC M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

74F132SJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F132PC N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

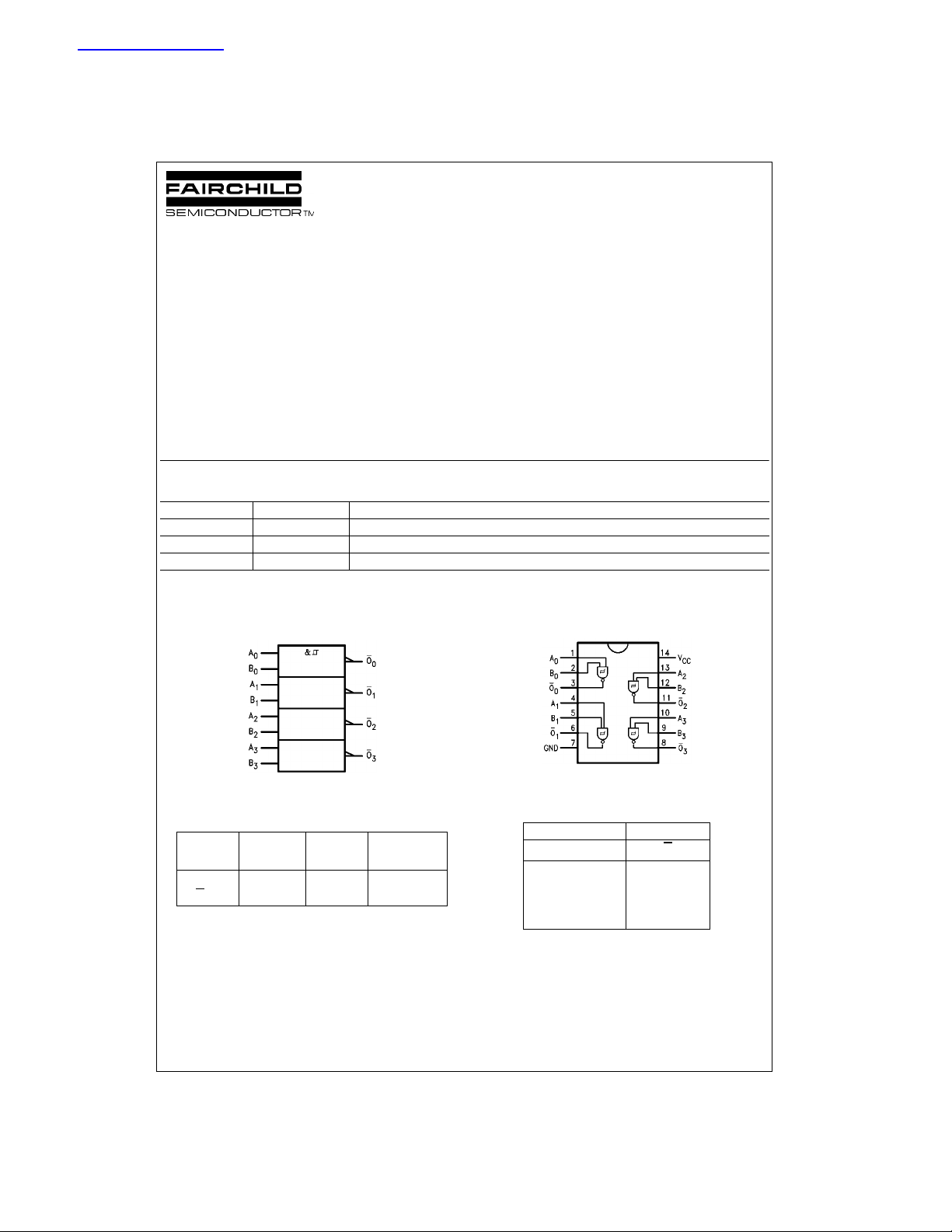

Logic Symbol

IEEE/IEC

Connection Diagram

Unit Loading/Fan Out

Pin Names Description

An, B

O

n

FAST is a regist ered trademark of Fair c hild Semiconductor Corporation

© 1999 Fairchild Semiconductor Corporation DS009477 www.fairchildsemi.com

Inputs 1.0/1.0 20 µA/−0.6 mA

n

Outputs 50/33.3 −1 mA/20 mA

U.L. Input I

HIGH/LOW Output IOH/I

IH/IIL

Function Table

OL

H = HIGH Voltage Level

L = LOW Voltage Level

Inputs Outputs

AB O

LL H

LH H

HL H

HH L

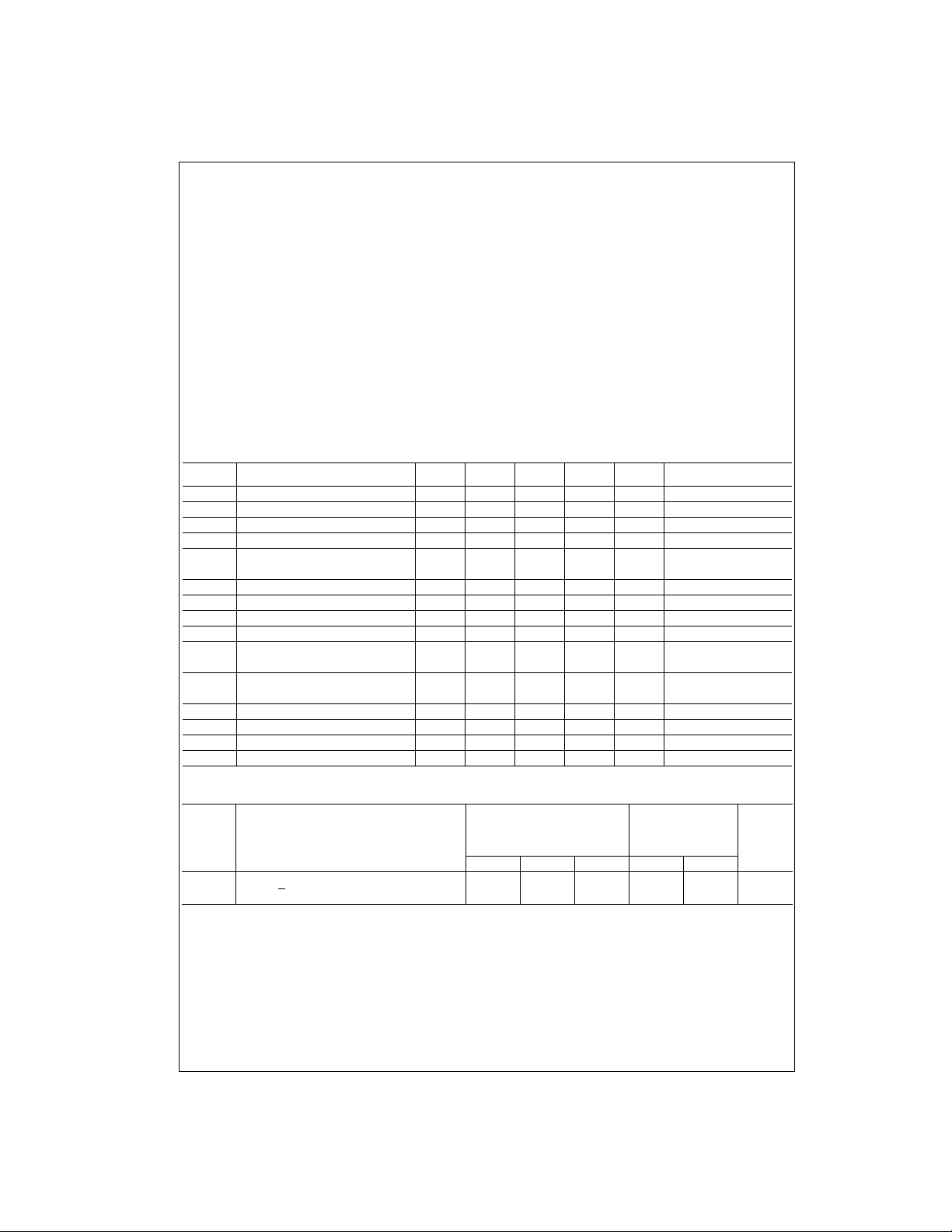

Absolute Maximum Ratings(Note 1) Recommended Operating

Storage Temperature −65°C to +150°C

74F132

Ambient Temperature under Bias −55°C to +125°C

Junction Temperature under Bias −55°C to +150°C

Pin Potential to Ground Pin −0.5V to +7.0V

V

CC

Input Voltage (Note 2) −0.5V to +7.0V

Input Current (Note 2) −30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with V

CC

= 0V)

Standard Output −0.5V to V

3-STATE Output −0.5V to +5.5V

Current Applied to Output

in LOW State (Max) twice the rated I

ESD Last Passing Voltage (Min) 4000V

OL

Conditions

Free Air Ambient Temperature 0°C to +70°C

Supply Voltage +4.5V to +5.5V

Note 1: Absolute maximum ratings are values beyond which the device

CC

may be damaged or have its useful life impaired. Functional operation

under these conditi ons is not implied.

Note 2: Either voltage limit or curren t limit is sufficient to protect in put s .

(mA)

DC Electrical Characteristics

Symbol Parameter Min Typ Max Units

V

V

∆V

V

V

V

I

I

I

V

I

I

I

I

I

T+

T−

CD

OH

OL

IH

BVI

CEX

ID

OD

IL

OS

CCH

CCL

Positive-going Threshold 1.5 2.0 V 5.0

Negative-going Threshold 0.7 1.1 V 5.0

Hysteresis (V

T

Input Clamp Diode Voltage −1.2 V Min IIN = −18 mA

Output HIGH 10% V

Voltage 5% V

Output LOW Voltage 10% V

Input HIGH Current 5.0 µAMaxVIN = 2.7V

Input HIGH Current Breakdown Test 7.0 µAMaxVIN = 7.0V

Output HIGH Leakage Current 50 µAMaxV

Input Leakage T est

Output Leakage Circuit Current

Input LOW Current −0.6 mA Max VIN = 0.5V

Output Short-Circuit Current −60 −150 mA Max V

Power Supply Current 17.0 mA Max VO = HIGH

Power Supply Current 18.0 mA Max VO = LOW

+

−

− V

)0.4 V5.0

T

T

2.5 V Min IOH = −1 mA

CC

CC

2.7 IOH = −1 mA

CC

4.75 V 0.0

0.5 V Min IOL = 20 mA

3.75 µA0.0

AC Electrical Characteristics

TA = +25°CT

Symbol Parameter

t

t

PLH

PHL

Propagation Delay 4.0 10.5 3.5 12.0

An, Bn to O

n

VCC = +5.0V VCC = +5.0V

CL = 50 pF CL = 50 pF

Min Typ Max Min Max

5.0 12.5 5.0 13.0

V

CC

OUT

IID = 1.9 µA

All Other Pins Grounded

V

IOD

All Other Pins Grounded

OUT

= 0°C to +70°C

A

Conditions

= V

CC

= 150 mV

= 0V

Units

ns

www.fairchildsemi.com 2

Loading...

Loading...