Fairchild 74F112 service manual

查询74F112供应商

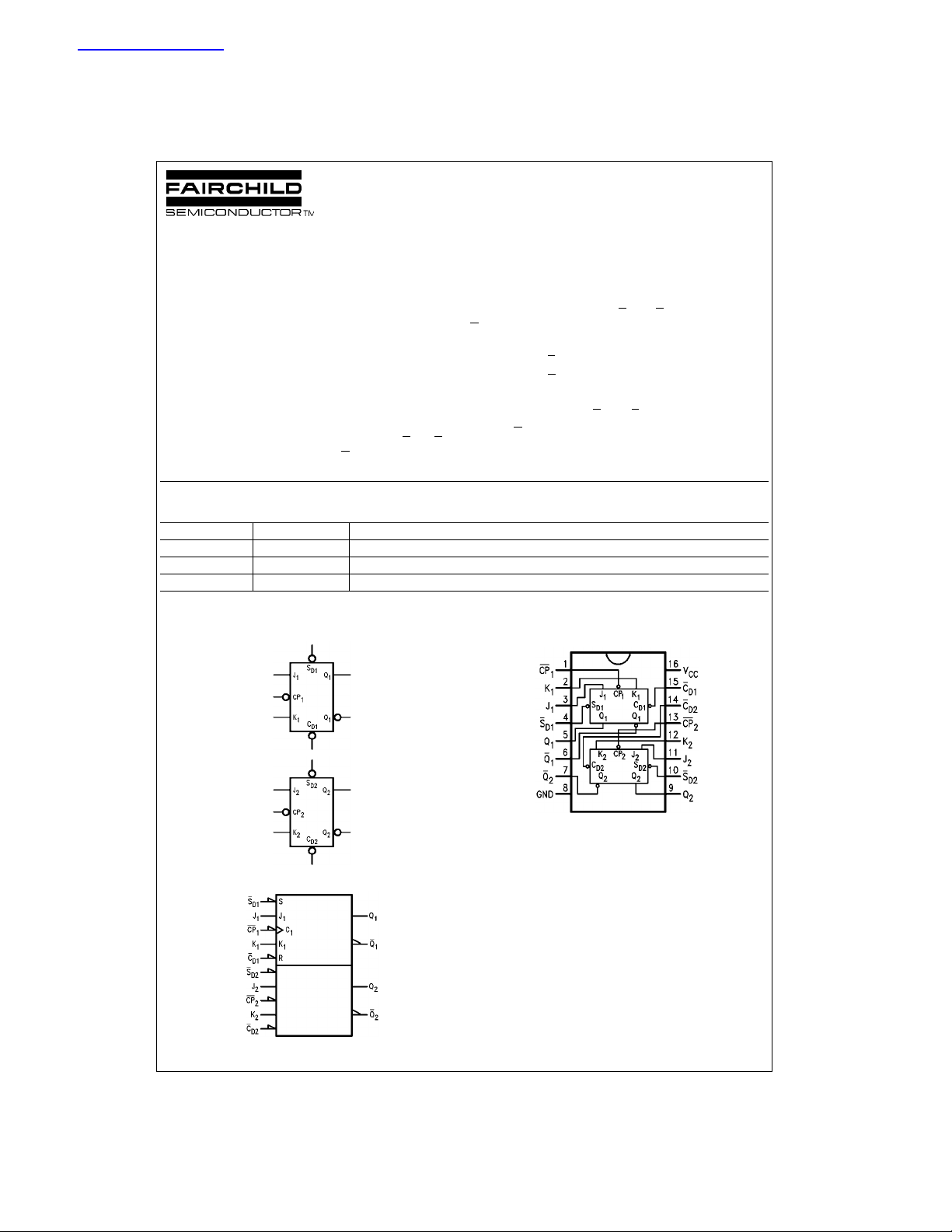

74F112

Dual JK Negative Edge-Triggered Flip-Flop

74F112 Dual JK Negative Edge-Triggered Flip-Flop

April 1988

Revised July 1999

General Description

The 74F112 contains two indepen dent, high -spee d JK flipflops with Direct S et and Clear inputs. Sy nchronous state

changes are in iti ated by th e fa ll ing edg e o f the cloc k. Triggering occurs at a voltage level of the clock and is not

directly related to t he transition time. The J an d K inputs

can change when the clock is in either stat e without affecting the flip-flop, provided that the y are in the desired st ate

during the recommen ded setup and ho ld times relative to

the falling edge of the clock. A LOW signal on S

prevents clocki ng and forces Q or Q HIGH, respectivel y.

or C

D

Simultaneous LOW signals on S

HIGH.

Q

Asynchronous Inputs:

LOW input to S

LOW input to C

Clear and Set are independent of clock

Simultaneous LOW on C

D

and Q

sets Q to HIGH level

D

sets Q to LOW level

D

HIGH

and CD force both Q and

D

and SD makes both Q

D

Ordering Code:

Order Number Package Number Package Description

74F112SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F112SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F112PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel . Specify by appending the suffix letter “X” to the ordering code.

Logic Symbols

Connection Diagram

IEEE/IEC

© 1999 Fairchild Semiconductor Corporation DS009472 www.fairchildsemi.com

Unit Loading/Fan Out

74F112

Pin Names Description

U.L.

HIGH/LOW

J1, J2, K1, K2Data Inputs 1.0/1.0 20 µA/−0.6 mA

CP

, CP

1

C

, C

D1

S

, S

D1

Q

, Q2, Q1, Q2Outputs 50/33.3 −1 mA/20 mA

1

Clock Pulse Inputs (Active Falling Edge) 1.0/4.0 20 µA/−2.4 mA

2

Direct Clear Inputs (Active LOW) 1.0/5.0 20 µA/−3.0 mA

D2

Direct Set Inputs (Active LOW) 1.0/5.0 20 µA/−3.0 mA

D2

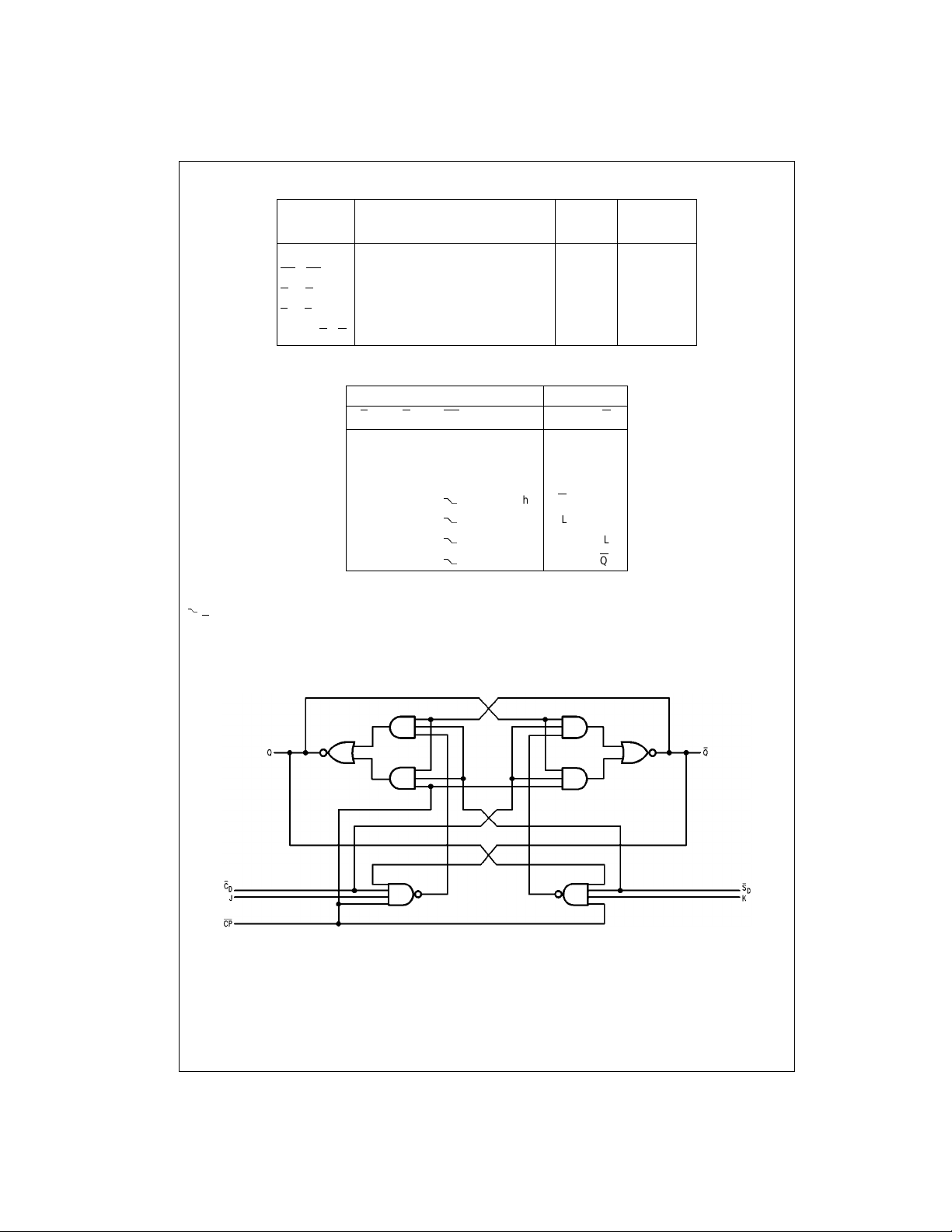

Tr uth Table

Inputs Outputs

C

S

D

LHXXXHL

HLXXXLH

LLXXXHH

HH

HH

HH

HH

H (h) = HIGH Voltage Level

L (l) = LOW Voltage Level

X = Immaterial

= HIGH-to-LOW Clock Transition

Q

) = Before HIGH-to-LOW Trans ition of Clock

0(Q0

Lower case letters indicate the state of the referenced input or output one setup time prior to the HIGH-to-LOW clock transition.

CP JKQ Q

D

hhQ0Q

lhL H

hlH L

llQ0Q

0

0

Input I

Output I

IH/IIL

OH/IOL

Logic Diagram

(One Half Shown)

Please not e that this diagram is provided only for the understanding of logic operations and should not be use d to estimate propagation delays.

www.fairchildsemi.com 2

Loading...

Loading...