74AC175 • 74ACT175

Quad D-Type Flip-Flop

74AC175 • 74ACT175 Quad D-Type Flip-Flop

November 1988

Revised November 1999

General Description

The AC/ACT175 is a hi g h-s pee d q uad D-type flip-flop . T he

device is useful for general flip-flop requirements where

clock and clear inputs are common. The information on the

D-type inputs is stored during the LOW-to-HIGH clock transition. Both true and comple mented outputs of each flipflop are provided. A Master Reset input resets all flip-flops,

independent of the Clock or D-type inputs, when LOW.

Features

■ ICC reduced by 50%

■ Edge-triggered D-type inputs

■ Buffered positive edge-triggered cl ock

■ Asynchronous common reset

■ True and complement output

■ Outputs source/sink 24 mA

■ ACT175 has TTL-compatible inputs

Ordering Code:

Order Number Package Number Package Description

74AC175SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

74AC175SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74AC175MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74AC175PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

74ACT175SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

74ACT175SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74ACT175MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74ACT175PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the or dering code.

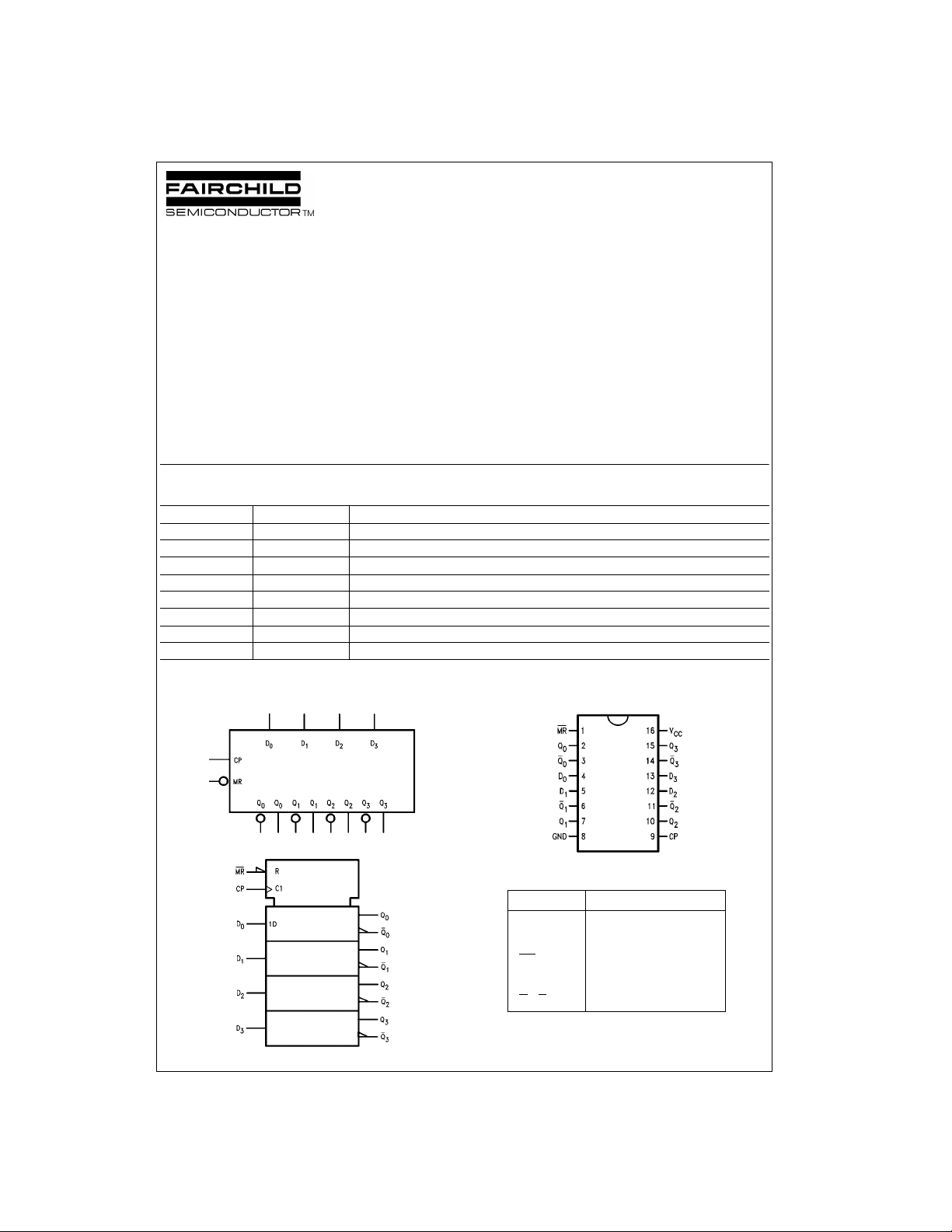

Logic Symbols

Connection Diagram

IEEE/IEC

Pin Descriptions

Pin Names Description

D

0–D3

CP Clock Pulse Input

MR

Q

0–Q3

Q

0–Q3

FACT is a trademark of Fairchild Semiconductor Corporation.

© 1999 Fairchild Semiconductor Corporation DS009936 www.fairchildsemi.com

Data Inputs

Master Reset Input

True Outputs

Complement Outputs

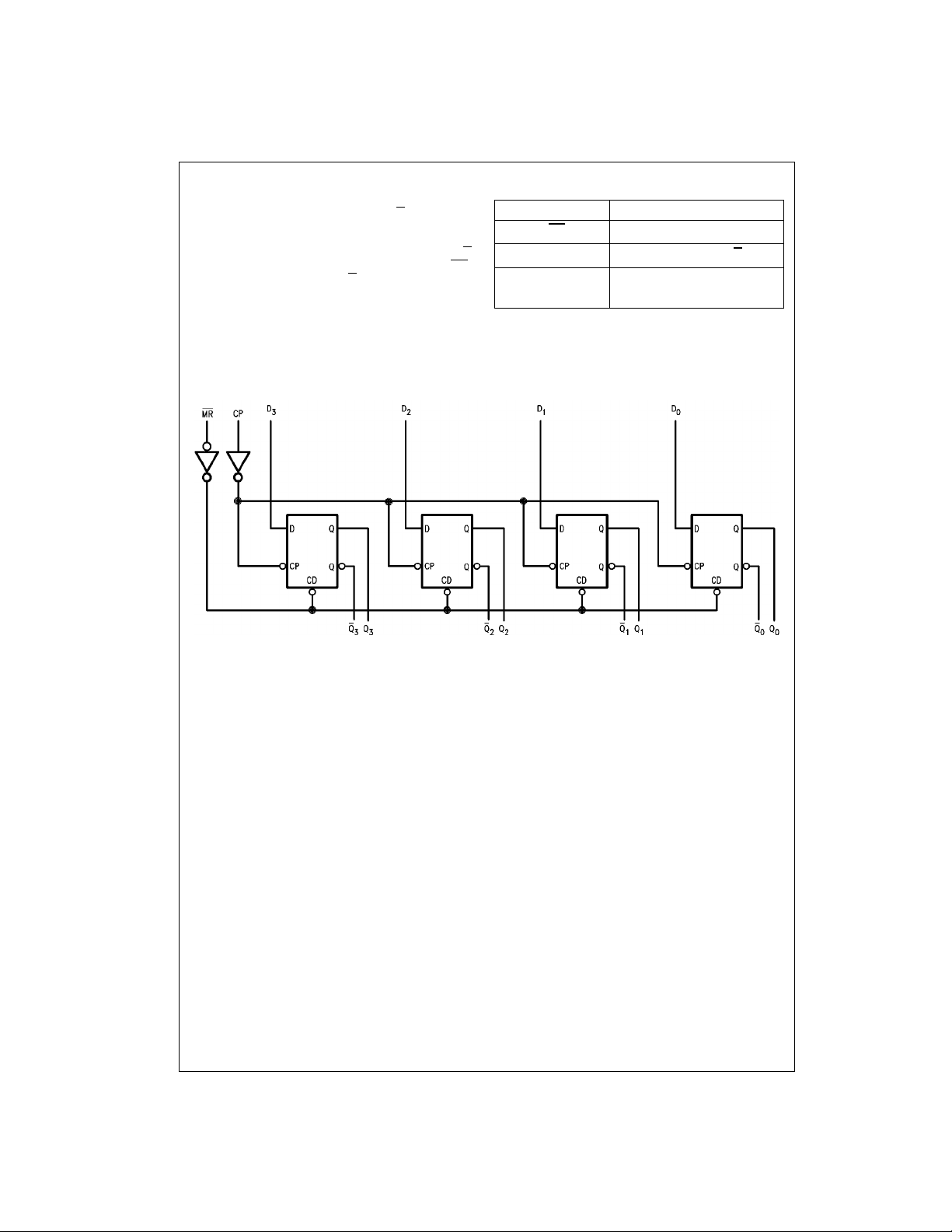

Functional Description

The AC/ACT175 consists of four edge-triggered D-type flipflops with individual D i nputs and Q and Q

outputs. The

Clock and Master Re set are common. The four f lip-flops

will store the state of their individual D inputs on th e LOWto-HIGH clock (CP) transi tion, causing ind ividual Q and Q

outputs to follow. A LOW input on the Master Reset (MR)

will force all Q outputs LOW and Q

outputs HIGH independent of Clock or Data inputs. The AC/ACT175 is useful for

general logic applic ations where a common Master R eset

and Clock are acceptab le.

74AC175 • 74ACT175

Logic Diagram

Truth Table

Inputs Outputs

@ t

, MR = H@ t

n

D

n

LLH

HHL

H = HIGH Voltage Level

L = LOW Voltage Level

= Bit Time before Clock Pulse

t

n

t

= Bit Time after Clock Pulse

n+1

n+1

Q

n

Q

n

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com 2

Absolute Maximum Ratings(Note 1) Recommended Operating

Supply Voltage (VCC) −0.5V to +7.0V

DC Input Diode Current (I

V

= −0.5V −20 mA

I

= VCC + 0.5V +20 mA

V

I

DC Input Voltage (V

DC Output Diode Current (I

= −0.5V −20 mA

V

O

V

= VCC + 0.5V +20 mA

O

DC Output Voltage (V

)

IK

) −0.5V to VCC + 0.5V

I

)

OK

) −0.5V to VCC + 0.5V

O

DC Output Source

or Sink Current (I

DC V

or Ground Current

CC

per Output Pin (I

Storage Temperature (T

Junction Temperature (T

) ± 50 mA

O

or I

CC

) ± 50 mA

GND

) −65°C to +150°C

STG

)

J

PDIP 140°C

Conditions

Supply Voltage (V

AC 2.0V to 6.0V

ACT 4.5V to 5.5V

Input Voltage (V

Output Voltage (VO)0V to V

Operating Temperature (TA) −40°C to +85°C

Minimum Input Edge Rate (∆V/∆t)

AC Devices

V

from 30% to 70% of V

IN

VCC @ 3.3V, 4.5V, 5.5V 125 mV/ns

Minimum Input Edge Rate (∆V/∆t)

ACT Devices

V

from 0.8V to 2.0V

IN

@ 4.5V, 5.5V 125 mV/ns

V

CC

Note 1: Absolute max imum ratings are those va lues beyond which damage

to the device may occu r. The databook spe cificatio ns shou ld be met, w ithout exception, to ensure that the system de sign is relia ble over its p ower

supply, temperature, and output/input loading variables. Fairchild does not

recommend operation of FACT circuits outside databook specif ic at ions

)

CC

)0V to V

I

CC

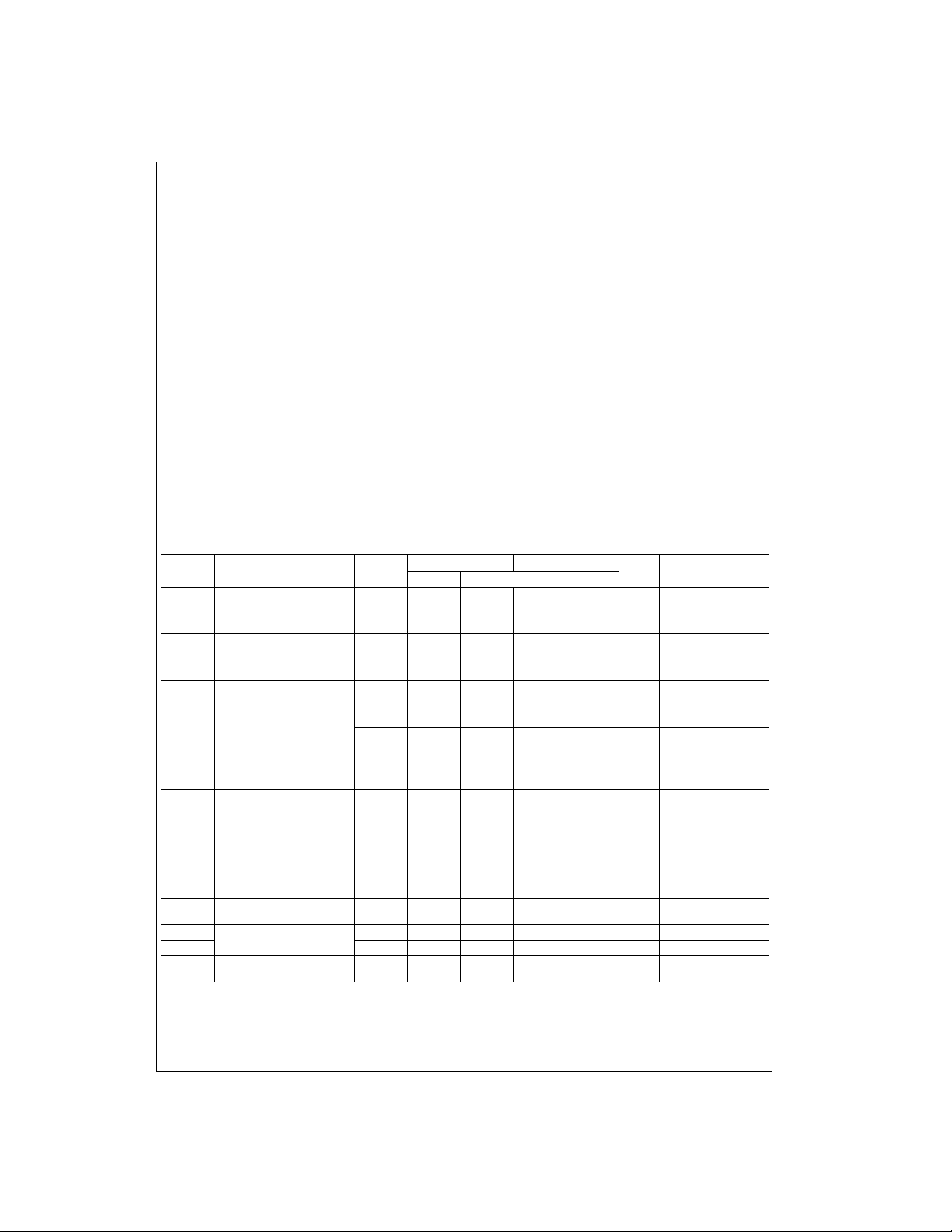

DC Electrical Characteristics for AC

V

Symbol Parameter

V

IH

V

IL

V

OH

V

OL

I

IN

(Note 4)

I

OLD

I

OHD

I

CC

(Note 4)

Note 2: All outputs loaded; thres holds on input associated with output under test.

Note 3: Maximum test duration 2.0 ms, one output loaded at a time.

Note 4: I

Minimum HIGH Level 3.0 1.5 2.1 2.1 V

Input Voltage 4.5 2.25 3.15 3.15 V or VCC − 0.1V

Maximum LOW Level 3.0 1.5 0.9 0.9 V

Input Voltage 4.5 2.25 1.35 1.35 V or VCC − 0.1V

Minimum HIGH Level 3.0 2.99 2.9 2.9

Output Voltage 4.5 4.49 4.4 4.4 V I

Maximum LOW Level 3.0 0.002 0.1 0.1

Output Voltage 4.5 0.001 0.1 0.1 V I

Maximum Input

Leakage Current

Minimum Dynamic 5.5 75 mA V

Output Current (Note 3) 5.5 −75 mA V

Maximum Quiescent

Supply Current

and ICC @ 3.0V are guaranteed to be less than or e qual to the respective lim it @ 5. 5V VCC.

IN

CC

(V) Typ Guaranteed Limits

5.5 2.75 3.85 3.85

5.5 2.75 1.65 1.65

5.5 5.49 5.4 5.4

3.0 2.56 2.46 IOH = −12 mA

4.5 3.86 3.76 V I

5.5 4.86 4.76 I

5.5 0.001 0.1 0.1

3.0 0.36 0.44 IOL = 12 mA

4.5 0.36 0.44 V IOL = 24 mA

5.5 0.36 0.44 IOL = 24 mA (Note 2)

5.5 ±0.1 ± 1.0 µAVI = VCC, GND

5.5 4.0 40.0 µAVIN = VCC or GND

TA = +25°CT

= −40°C to +85°C

A

Units Conditions

VIN = VIL or V

VIN = VIL or V

= 0.1V

OUT

= 0.1V

OUT

= −50 µA

OUT

IH

= −24 mA

OH

= −24 mA (Note 2)

OH

= 50 µA

OUT

IH

= 1.65V Max

OLD

= 3.85V Min

OHD

74AC175 • 74ACT175

CC

CC

3 www.fairchildsemi.com