ETRON EM658160TS-8, EM658160TS-7, EM658160TS-6, EM658160TS-5, EM658160TS-4 Datasheet

...

Etr onT ech

EM658160

4M x 16 DDR Synchronous DRAM (SDRAM)

Etron Confidential (Rev. 1.1 Jan./2002)

Features

•

Fast clock rate: 300/285/250/200/166/143/125MHz

•

Differential Clock CK & /CK

•

Bi-directional DQS

•

DLL enable/disable by EMRS

•

Fully synchronous operation

•

Internal pipeline architecture

•

Four internal banks, 1M x 16-bit for each bank

•

Programmable Mode and Extended Mode registers

- /CAS Latency: 2, 2.5, 3

- Burst length: 2, 4, 8

- Burst Type: Sequential & Interleaved

•

Individual byte write mask control

•

DM Write Latency = 0

•

Auto Refresh and Self Refresh

•

4096 refresh cycles / 64ms

•

Precharge & active power down

•

Power supplies: V

•

Interface: SSTL_2 I/O Interface

•

Package: 66 Pin TSOP II, 0.65mm pin pitch

= 3.3V ± 0.3V

DD

= 2.5V ± 0.2V

V

DDQ

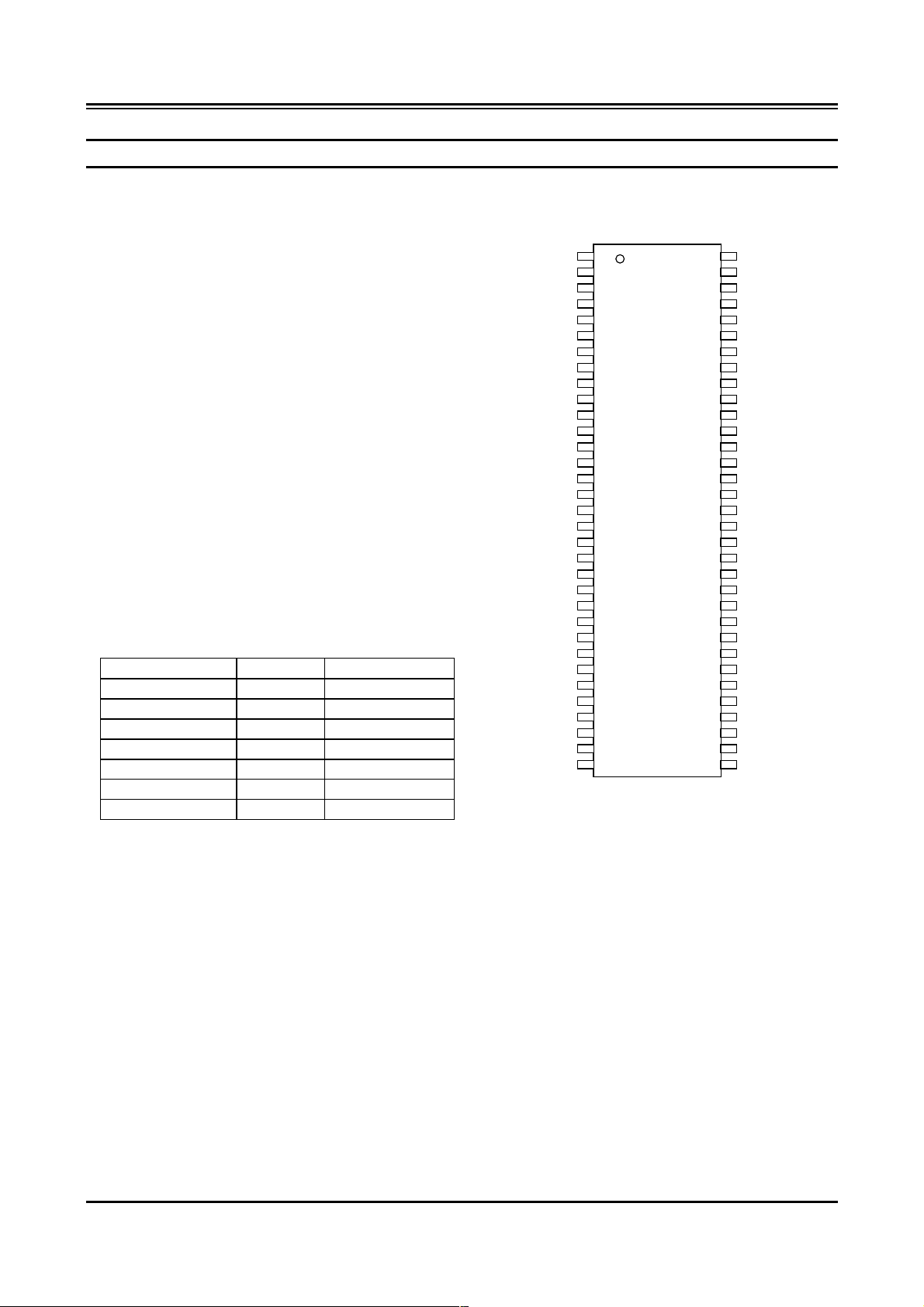

Ordering Information

Part Number Frequency Package

EM658160TS-3.3 300MHz TSOP II

EM658160TS-3.5 285MHz TSOP II

EM658160TS-4 250MHz TSOP II

EM658160TS-5 200MHz TSOP II

EM658160TS-6 166MHz TSOP II

EM658160TS-7 143MHz TSOP II

EM658160TS-8 125MHz TSOP II

Pin Assignment (Top View)

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

NC

VDDQ

LDQS

NC

VDD

NC

LDM

/WE

/CAS

/RAS

/CS

NC

BS0

BS1

A10/AP

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

A0

30

A1

31

A2

32

A3

33

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

NC

VSSQ

UDQS

NC

VREF

VSS

UDM

/CK

CK

CKE

NC

NC

A11

A9

A8

A7

A6

A5

A4

VSS

Overview

The EM658160 SDRAM is a high-speed CMOS

double data rate synchronous DRAM containing 64

Mbits. It is internally configured as a quad 1M x 16

DRAM with a synchronous interface (all signals are

registered on the positive edge of the clock signal, CK).

Data outputs occur at both rising edges of CK and /CK.

Read and write accesses to the SDRAM are burst

oriented; accesses start at a selected location and

continue for a programmed number of locations in a

programmed sequence. Accesses begin with the

registration of a BankActivate command which is then

followed by a Read or Write command. The EM658160

provides programmable Read or Write burst lengths of 2,

4, 8, full page.

An auto precharge function may be enabled to

provide a self-timed row precharge that is initiated at the

end of the burst sequence. The refresh functions, either

Auto or Self Refresh are easy to use. In addition,

EM658160 features programmable DLL option. By

having a programmable mode register and extended

mode register, the system can choose the most suitable

modes to maximize its performance. These devices are

well suited for applications requiring high memory

bandwidth, result in a device particularly well suited to

high performance main memory and graphics

applications.

Etron Technology, Inc.

No. 6, Technology Rd. V, Science-Based Industrial Park, Hsinchu, Taiwan 30077, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

Etron Technology, Inc., reserves the right to make changes to its products and specifications without notice.

Etr onT ech

h

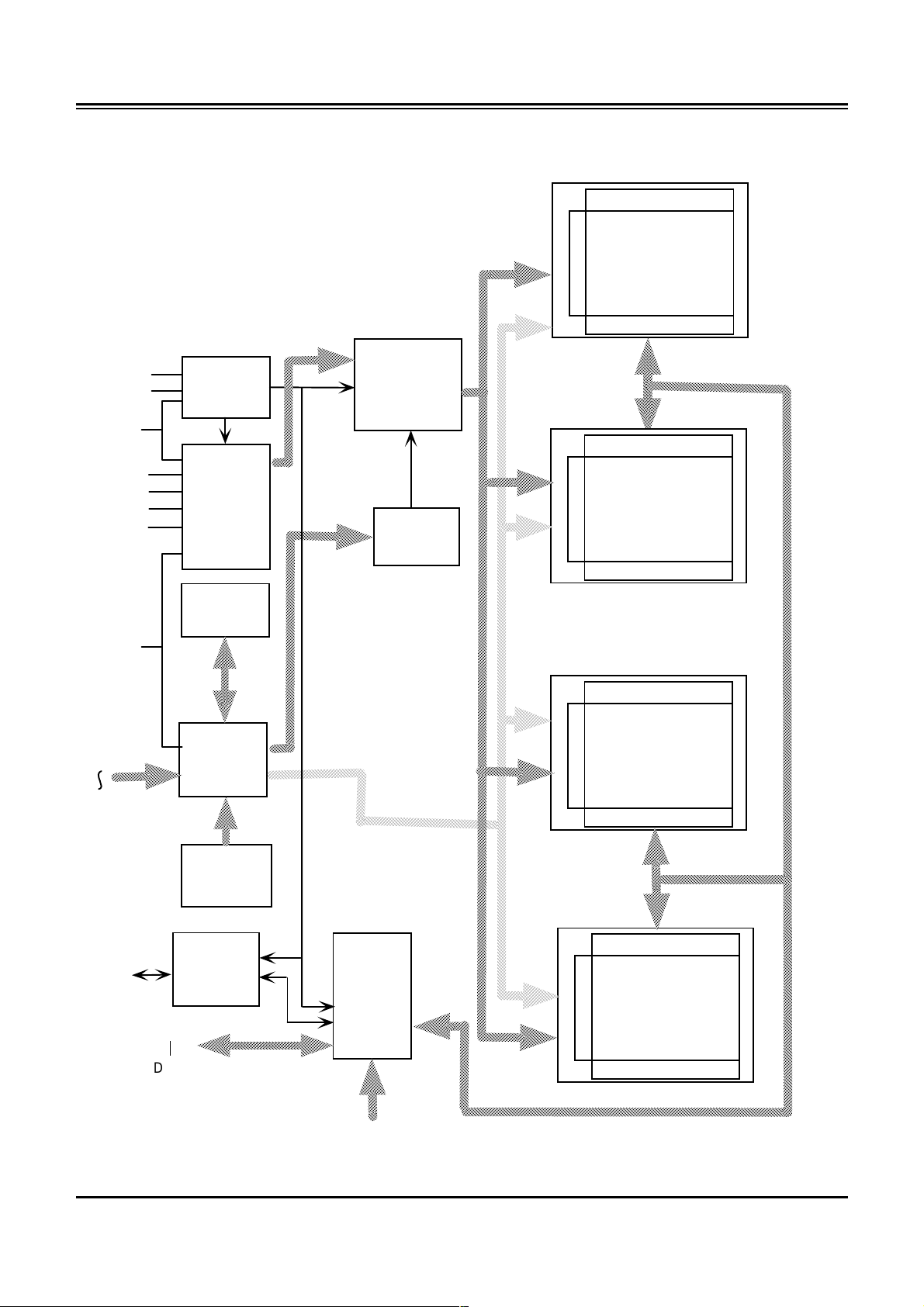

Block Diagram

4Mx16 DDR SDRAM

Row Decoder

EM658160

Column Decoder

1MX1 6

CELL ARRAY

(BANK #0)

Sense Amplifier

CK

/CK

CKE

/CS

/RAS

/CAS

/WE

A10/AP

A0

A11

BS0

BS1

DLL

CLOCK

BUFFER

COMMAND

DECODER

COLUMN

COUNTER

ADDRESS

BUFFER

CONTROL

SIGNAL

GENERATOR

MODE

REGISTER

Sense Amplifier

1MX16

CELL ARRAY

(BANK #1)

Row Decoder

Column Decoder

Column Decoder

1MX16

CELL ARRAY

(BANK #2)

Row Decoder

Sense Amplifier

REFRESH

COUNTER

Sense Amplifier

1MX1 6

CELL ARRAY

(BANK #3)

Row Decoder

Column Decoder

LDQS,

UDQS

DQ0

DQ15

DATA

STROBE

BUFFER

DQ

BUFFER

LDM, UDM

Etron Confidential 2 Rev. 1.1 Jan. 2002

Etr onT ech

4Mx16 DDR SDRAM

Pin Descriptions

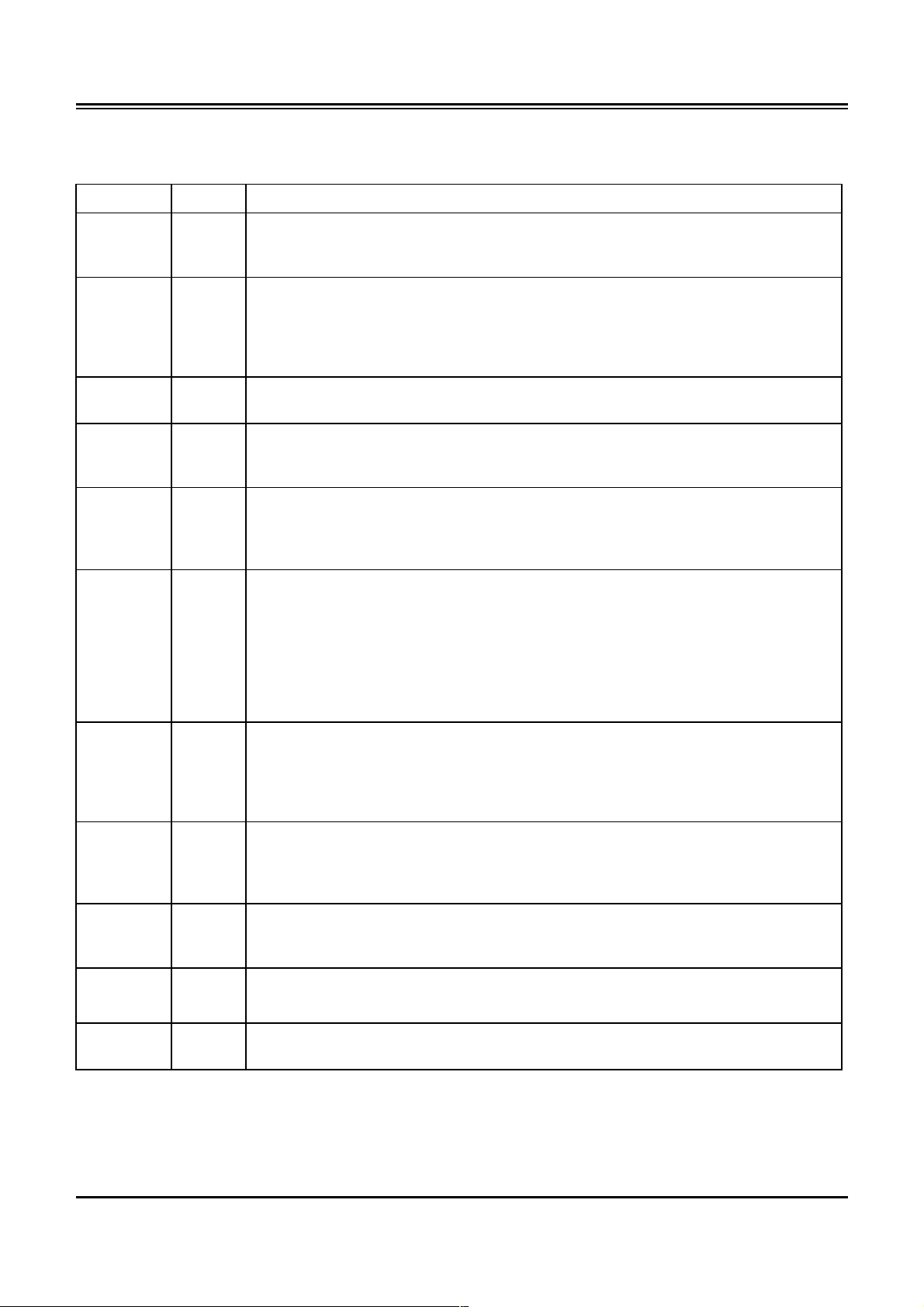

Table 1. Pin Details of EM658160

Symbol Type Description

EM658160

CK, /CK Input

CKE Input

BS0, BS1 Input

A0-A11 Input

/CS Input

/RAS Input

Differential Clock:

are sampled on the positive edge of CK. Both CK and /CK inc r ement the internal burst

counter and controls the output registers.

Clock Enable:

goes low synchronously with clock, the internal clock is suspended f r om the next clock

cycle and the state of output and burst address is f rozen as long as the CKE rem ains

low. When all bank s are in the idle state, deactivating the cloc k controls the entry to

the Power Down and Self Refresh modes.

Bank Select:

BankPrecharge command is being applied.

Address Inputs:

address A0-A11) and Read/W rite c omm and (column address A0-A7with A10 def ining

Auto Precharge).

Chip Select:

command decoder. All commands are masked when /CS is sampled HIGH. /CS

provides for external bank selection on systems with multiple banks. It is considered

part of the command code.

Row Address Strobe:

conjunction with the /CAS and /WE signals and is latched at the positive edges of CK.

When /RAS and /CS are asserted "LOW " and /CAS is asserted "HIGH," either the

BankActivate command or the Precharge command is selected by the /WE signal.

When the /W E is asserted "HIGH," the BankActivate command is selected and the

bank designated by BS is turned on to the active state. When the /W E is asserted

"LOW," the Precharge command is selected and the bank designated by BS is

switched to the idle state after the precharge operation.

CK, /CK are driven by the system clock. All SDRAM input signals

CKE activates(HIGH) and deactivates(LOW) the CK signal. If CKE

BS0 and BS1 defines to which bank the BankActivate, Read, W rite, or

A0-A11 are sampled during the BankActivate command (row

/CS enables (sampled LOW) and disables (sampled HIGH) the

The /RAS signal defines the operation commands in

/CAS Input

/WE Input

LDQS,

UDQS

LDM,

UDM

DQ0 - DQ15 Input /

Input /

Output

Input

Output

Column Address Strobe:

conjunction with the /RAS and /WE signals and is latched at the positive edges of CK.

When /RAS is held "HIGH" and /CS is asserted "LOW ," the colum n access is started

by asserting /CAS "LOW ." T hen, the Read or Write com m and is selected by asser ting

/WE "HIGH " or LOW"."

Write Enable:

the /RAS and /CAS signals and is latched at the positive edges of CK. T he /W E input

is used to select the BankActivate or Precharge command and Read or Write

command.

Bidirectional Data Strobe:

Strobe is edge triggered. W rite Data Strobe provides a setup and hold time for data

and DQM. LDQS is for DQ0~7, UDQS is for DQ8~15.

Data Input Mask:

cycle. LDM masks DQ0-DQ7, UDM masks DQ8-DQ15.

Data I/O:

edges of CK and /CK. The I/Os are byte-maskable during Writes.

The /W E signal defines the operation commands in conjunction with

Input data is masked when DM is s ampled HIGH during a write

The DQ0-DQ15 input and output data are synchronized with the positive

The /CAS signal defines the operation commands in

Specifies timing for Input and Output data. Read Data

Etron Confidential 3 Rev. 1.1 Jan. 2002

Etr onT ech

4Mx16 DDR SDRAM

EM658160

V

DD

V

SS

V

DDQ

V

SSQ

V

REF

NC -

Supply

Supply

Supply

Supply

Supply

Power Supply:

Ground

DQ Power:

DQ Ground:

Reference Voltage for Inputs:

No Connect:

+3.3V ±0.3V

+2.5V ±0.2V. Provide isolated power to DQs for improved noise immunity.

Provide isolated ground to DQs for improved noise immunity.

These pins should be left unconnected.

+0.5*V

DDQ

Etron Confidential 4 Rev. 1.1 Jan. 2002

Etr onT ech

4Mx16 DDR SDRAM

EM658160

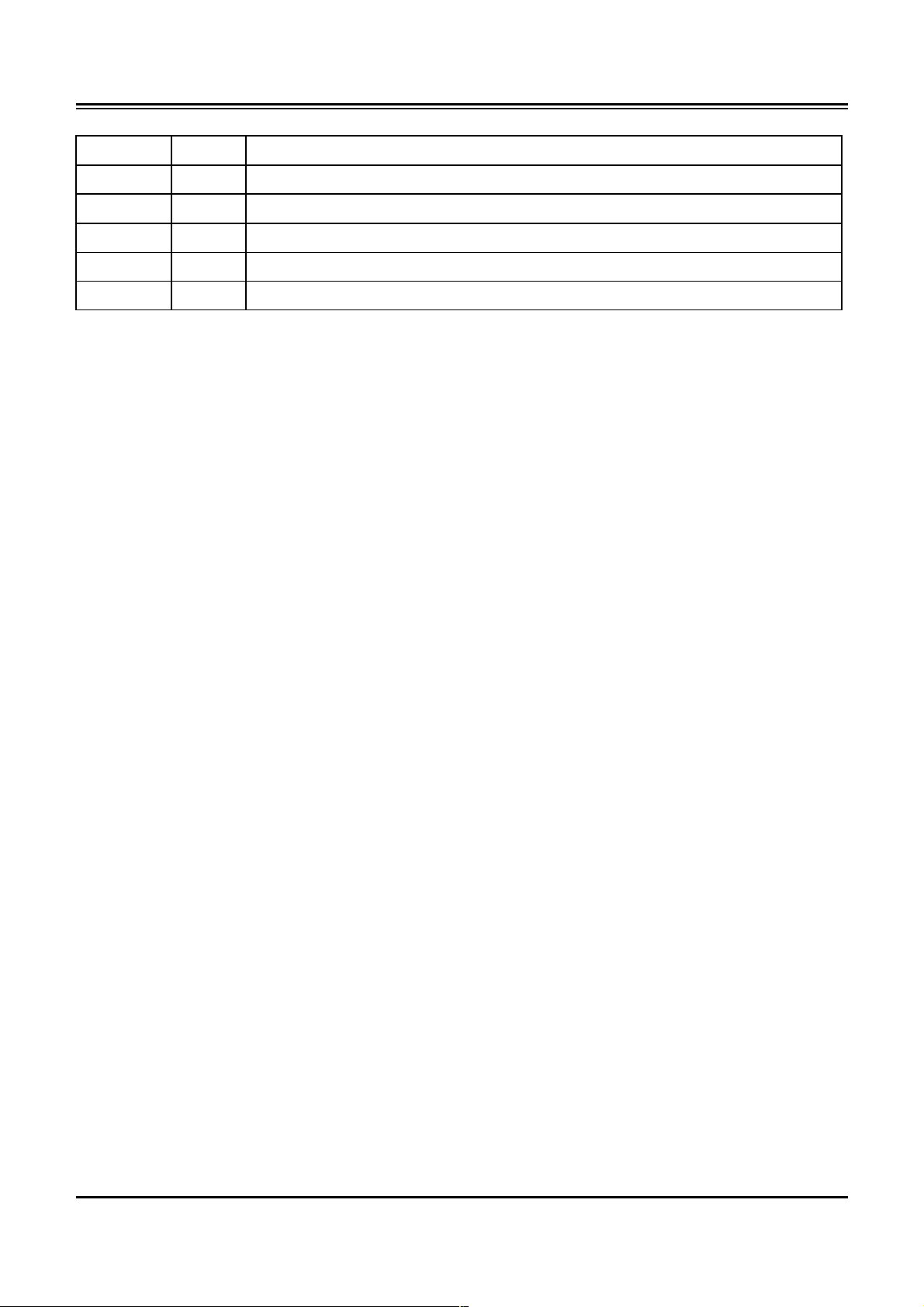

Operation Mode

Fully synchronous operations are performed to latch the com mands at the positive edges of CK. Table 2

shows the truth table for the operation commands.

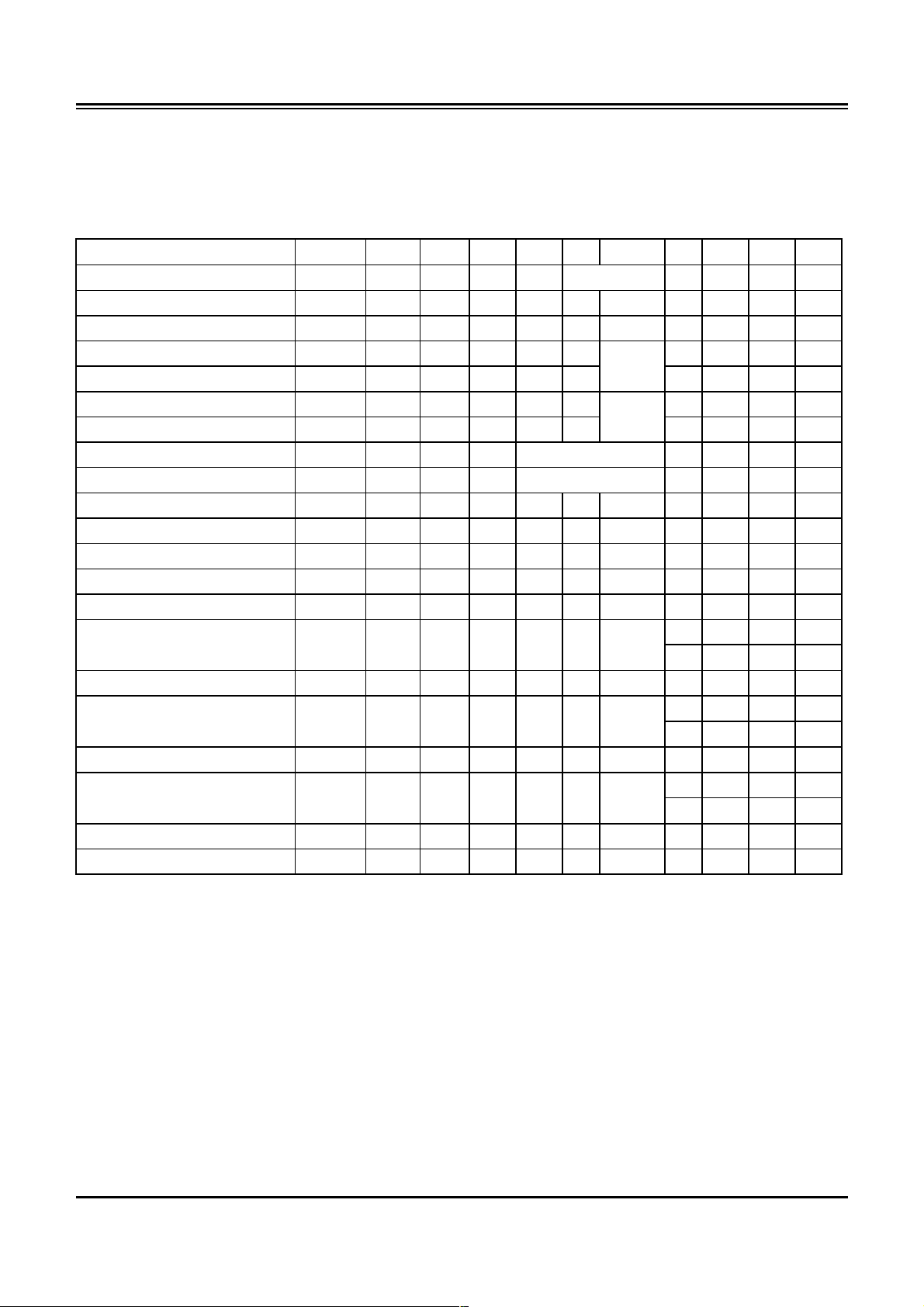

Table 2. Truth Table (Note (1), (2) )

Command State CKE

BankActivate

BankPrecharge

PrechargeAll

Write

Write and AutoP recharge

Read

Read and Autoprecharge

Mode Register Set

Extended MRS

No-Operation

Burst Stop

Device Deselect

AutoRefresh

SelfRefresh Entry

SelfRefresh Exit

Clock Suspend Mode Entry

Power Down Mode Entry

Clock Suspend Mode Exit

Power Down Mode Exit

Data Write/Out put Enable

Data Mask/Output Disable

Note:

1. V=Valid data, X=Don't Care, L=Low level, H=High level

2. CKE

signal is input level when commands are provided.

n

CKE

signal is input level one clock cycle before the commands are provided.

n-1

3. These are states of bank designated by BS signal.

4. Device state is 1, 2, 4, 8, and full page burst operation.

5. Power Down Mode can not enter in the burst operation.

When this command is asserted in the burst cycle, device state is clock suspend mode.

0,1A10A0-9,11

/CS /RAS /CAS /WE

Idle

(3)

CKEnDM BS

n-1

H X X V Row address L L H H

Any H X X V L X L L H L

Any H X X X H X L L H L

Active

Active

Active

Active

(3)

HXXVL LHLL

(3)

HXXVH

(3)

HXXVL LHLH

(3)

HXXVH

Column

address

(A0 ~ A7)

Column

address

(A0 ~ A7)

LH L L

LH L H

Idle H X X OP code L L L L

Idle H X X OP code L L L L

Any H X X X X X L H H H

(4)

Active

HXXXXXLHHL

Any H XXXX X HXXX

Idle H H X X X X L L L H

Idle H L X X X X L L L H

Idle L HXXX X HXXX

(SelfRefresh)

LH HH

ActiveH LXXX X XXXX

(5)

Any

H LXXX X HXXX

LH H H

ActiveL HXXX X XXXX

Any L HXXX X HXXX

(PowerDown)

LH H H

ActiveHXLXXXXXXX

ActiveHXHXXXXXXX

Etron Confidential 5 Rev. 1.1 Jan. 2002

Etr onT ech

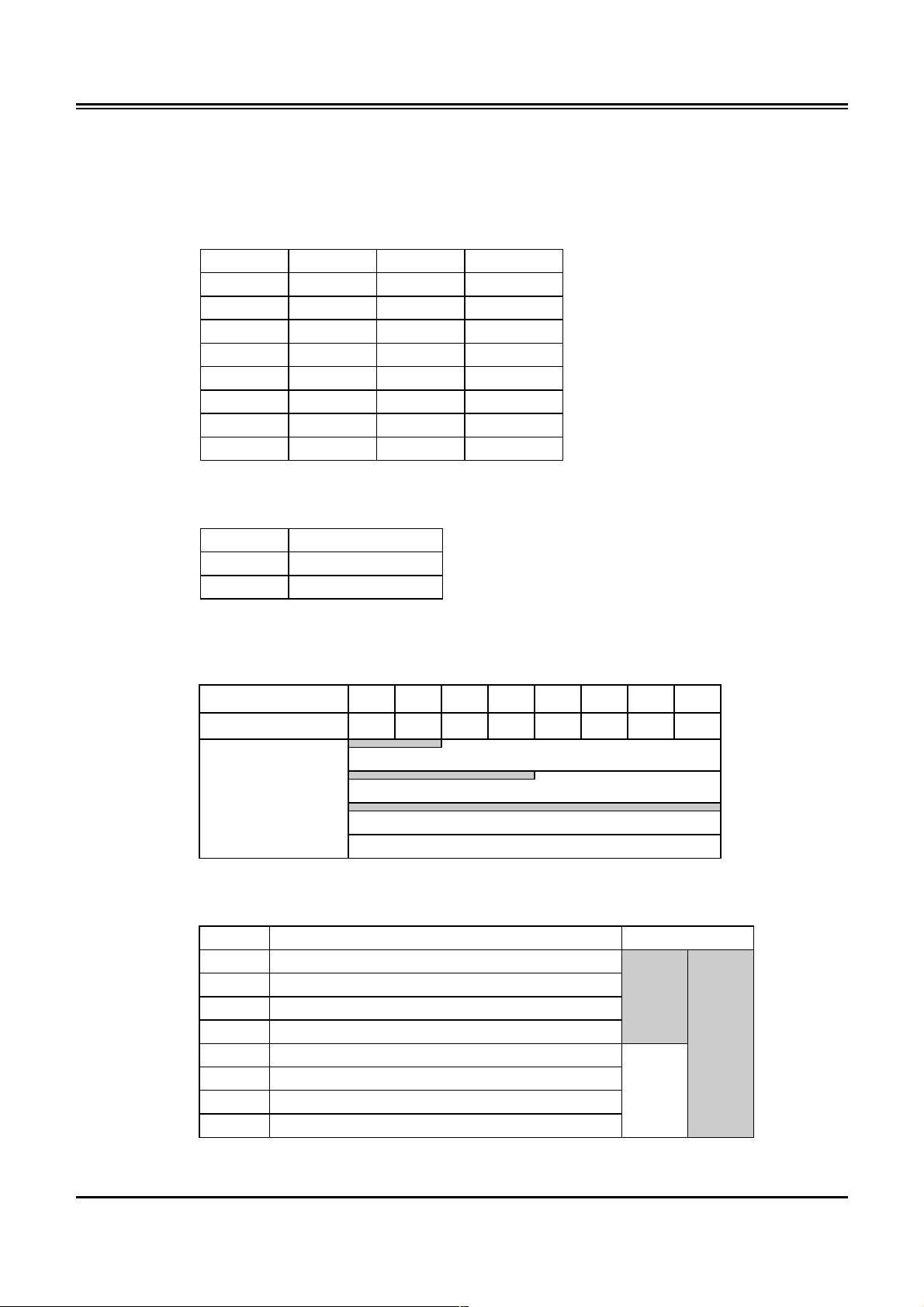

Mode Register Set (MRS)

The mode register is divided into various fields depending on functionality.

•

Burst Length Field (A2~A0)

This field specif ies the data length of column access using the A2~A0 pins and selects the

Burst Length to be 2, 4, 8.

A2 A1 A0 Burst Length

0 0 0 Reserved

001 2

010 4

011 8

1 0 0 Reserved

1 0 1 Reserved

1 1 0 Reserved

1 1 1 Reserved

•

Addressing Mode Select Field (A3)

The Addressing Mode can be one of two modes, both Interleave Mode or Sequential Mode.

Both Sequential Mode and Interleave Mode support burst length of 2,4 and 8.

4Mx16 DDR SDRAM

EM658160

A3 Addressing Mode

0 Sequential

1 Interleave

--- Addressing Sequence of Sequential Mode

An internal column address is performed by increasing the address from the column

address which is input to the device. The internal column address is var ied by the Burst

Length as shown in the following table.

Data n 01234567

Column Address

Burst Length 4 words

--- Addressing Sequence of Interleave Mode

A column access is started in the input c olumn address and is performed by inverting the

address bits in the sequence shown in the following table.

Data n Column Address Burst Length

Data 0 A7 A6 A5 A4 A3 A2 A1 A0

Data 1 A7 A6 A5 A4 A3 A2 A1 A0# 4 words

Data 2 A7 A6 A5 A4 A3 A2 A1# A0

Data 3 A7 A6 A5 A4 A3 A2 A1# A0# 8 words

Data 4 A7 A6 A5 A4 A3 A2# A1 A0

Data 5 A7 A6 A5 A4 A3 A2# A1 A0#

Data 6 A7 A6 A5 A4 A3 A2# A1# A0

Data 7 A7 A6 A5 A4 A3 A2# A1# A0#

n n+1 n+2 n+3 n+4 n+5 n+6 n+7

2 words

8 words

Full Page (Even starting address)

Etron Confidential 6 Rev. 1.1 Jan. 2002

Etr onT ech

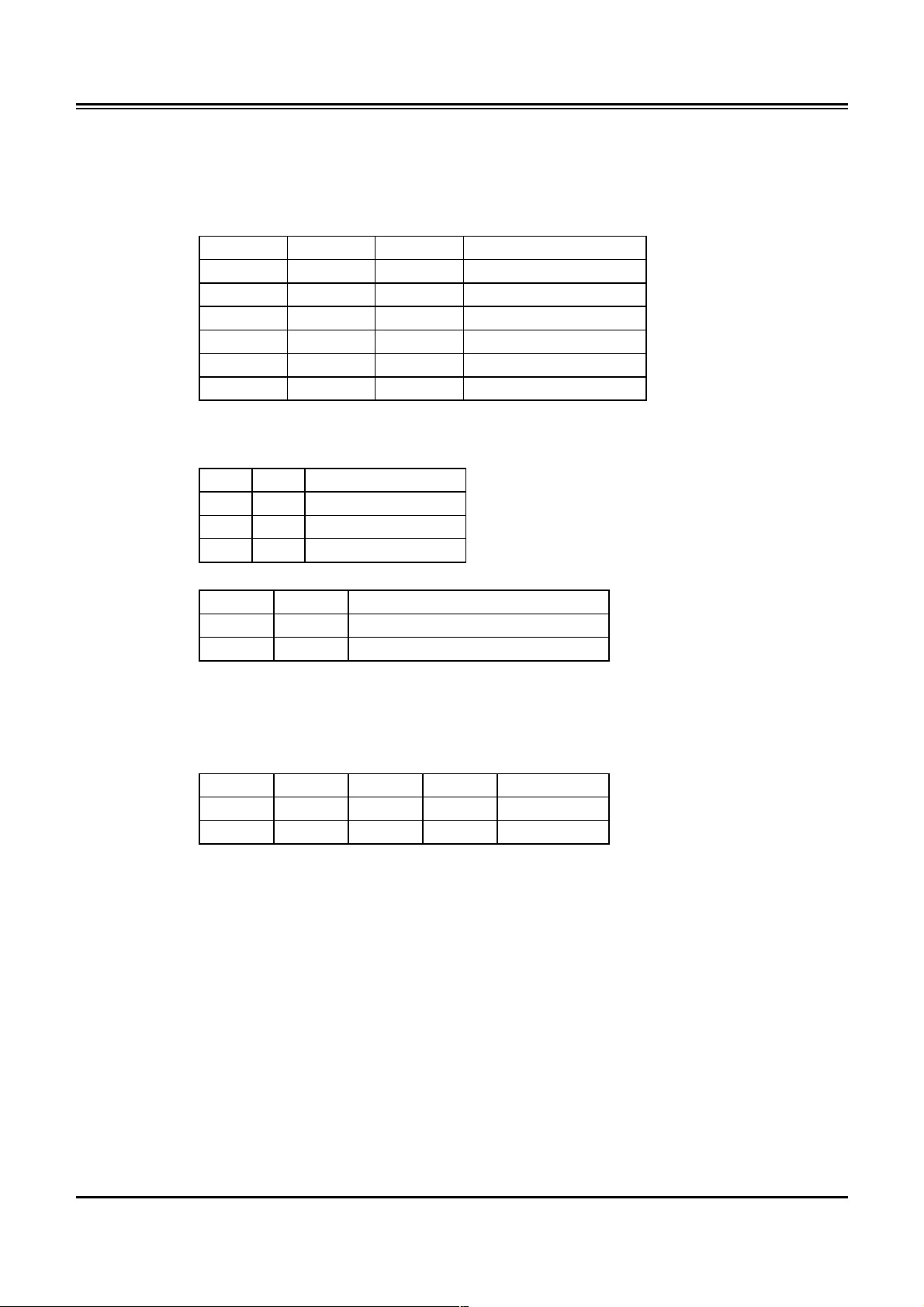

•

CAS Latency Field (A6~A4)

This field specifies the num ber of clock cycles from the asser tion of the Read com m and to the

first read data. The m inimum whole value of CAS Latency depends on the frequency of CK.

The minimum whole value satisfying the following formula must be programmed into this field.

(min) ≤ CAS Latency X t

t

CAC

A6 A5 A4 CAS Latency

0 0 0 Reserved

010 2 clocks

011 3 clocks

1 0 1 Reserved

1 1 0 2.5 clocks

1 1 1 Reserved (3.5 clocks)

•

Test Mode field (A8~A7)

These two bits are used to enter the test mode and m ust be programmed to "00" in norm al

operation.

A8 A7 Test Mode

0 0 Normal mode

1 0 DLL Reset

X 1 Test mode

•

( BS0, BS1)

4Mx16 DDR SDRAM

CK

EM658160

BS1 BS0 An ~ A0

RFU 0 MRS Cycle

RFU 1 Extended Functions (EMRS)

Extended Mode Register Set (EMRS)

BS1 BS0 A11~ A1 A0

RFU 1 RFU 0 DLL Enable

RFU 1 RFU 1 DLL Disable

Etron Confidential 7 Rev. 1.1 Jan. 2002

Etr onT ech

4Mx16 DDR SDRAM

EM658160

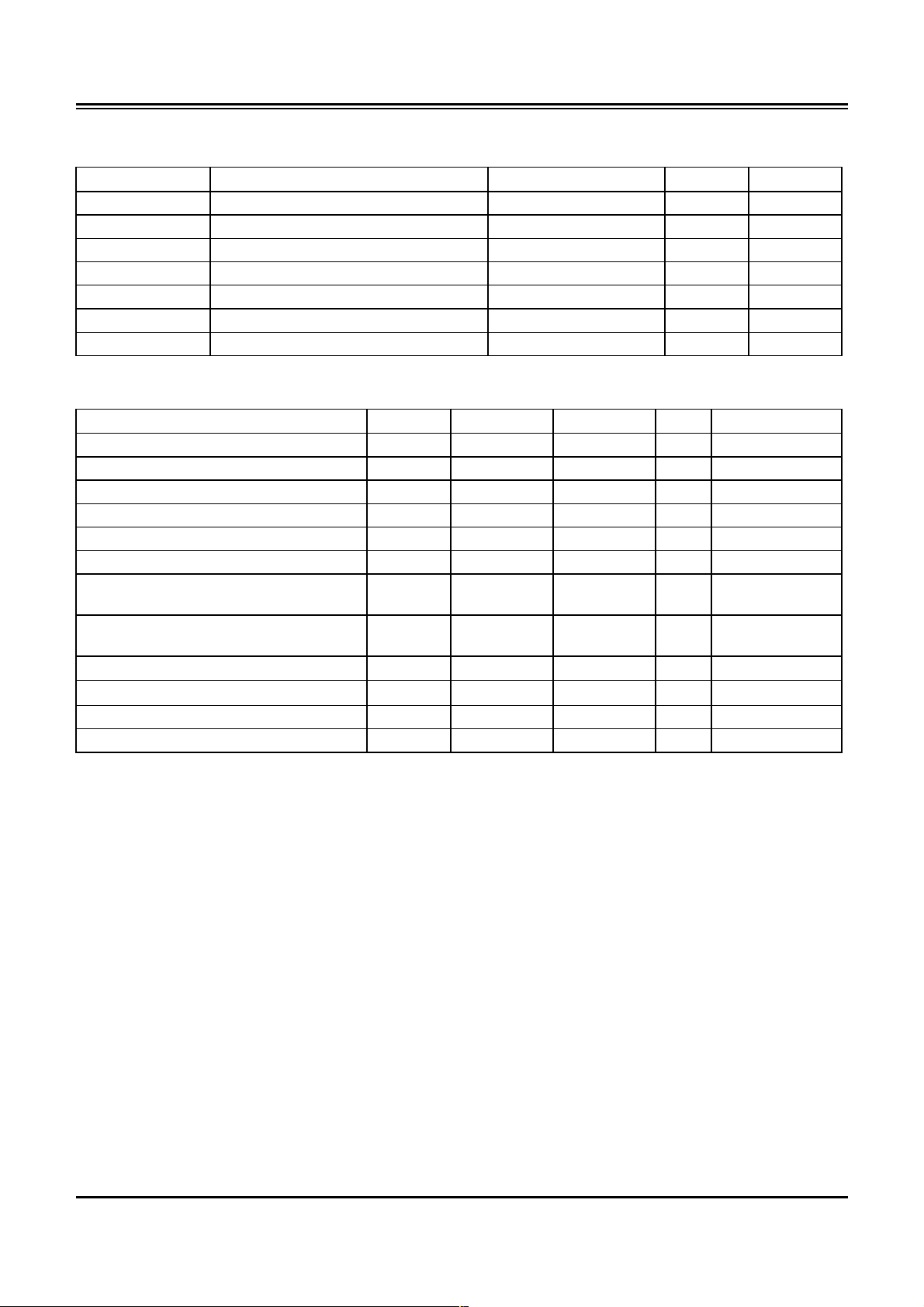

Absolute Maximum Rating

Symbol Item Rating Unit Note

VIN, V

VDD, V

T

OPR

T

STG

T

SOLDER

P

I

OUT

OUT

DDQ

D

Input, Output Voltage - 0.3~ VDD + 0.3 V 1

Power Supply Voltage - 0.3~3.6 V 1

Operating Temperature 0~70 °C 1

Storage Temperature - 55~150 °C 1

Soldering Temperature (10s) 260 °C 1

Power Dissipation 1 W 1

Short Circuit Output Current 50 mA 1

Recommended D.C. Operating Conditions (Ta = 0 ~ 70

Parameter Symbol Min. Max. Unit Note

Power Supply Voltage V

Power Supply Voltage (for I/O Buffer) V

Input Reference Voltage V

Termination Voltage V

Input High Voltage (DC) V

Input Low Voltage (DC) V

Input Voltage Level, CLK and CLK#

IH

IL

V

IN

inputs

Input Different Voltage, CLK and CLK#

V

ID

inputs

Input leakage current I

Output leakage current I

Output High Voltage V

Output Low Voltage V

DD

DDQ

REF

TT

(DC) V

(DC) -0.3 V

(DC) -0.3 V

(DC) -0.36 V

I

OZ

OH

OL

3.0 3.6 V

2.3 2.7 V

1.15 1.35 V

V

- 0.04 V

REF

+ 0.18 V

REF

REF

DDQ

REF

DDQ

DDQ +

-5 5

-5 5

VTT + 0.76 - V I

VTT – 0.76 V I

°C)

+ 0.04 V

+ 0.3 V

– 0.18 V

+ 0.3 V

0.6 V

µ

µ

A

A

= -15.2 mA

OH

= +15.2 mA

OL

Etron Confidential 8 Rev. 1.1 Jan. 2002

Loading...

Loading...