ESS ES4428, ES4427 Datasheet

ES4428/ES4427

Web/DVD Set-Top Box Solution

Product Brief

DESCRIPTION

The ES4428/ES4427 Web/DVD Internet set-top box chipset

seamlessly combines both Web browser technology and DVD

technology into a h igh ly i ntegrated, low-cost solution for th e nex t

generation of Internet set-top boxes for home use.

The ES4428, which is based on ESS’s Programmable

Multimedia Processor (PMP) device architecture, includes a

programmable internal RISC processor core that makes it

adaptable for use in embedded systems applications such as

set-top boxes. The ES4427 companion chip supplies proper

video sync capabilities and performs NTSC- and PAL-based

video encoding an d decoding as ne cessary to provide bro adcast

quality video to the television screen.

The ES4428 DVD processor integrates MPEG-based audio and

video data stream decoding for DVD/VCD/SuperVCD playback,

DVD system navigation and Dolby AC-3 decoding into a single

device. The ES4428 demuxes the incoming DVD audio and

video data streams from the DVD loader using its glueless 8/16bit parallel interface, whic h is hardware-compati ble with many

DVD loaders. The ES4428 also supports both 8- and 16-bit

Flash/Read-Only Me mory (ROM) an d 8- and 16-bit Synchronous

DRAM (SDRAM) memory I/O operations.

The ES4428 controls data I/O transactions to and from the

ES4427 companion chip through its 8-bit Device Serial Connect

(DSC) parallel bus interface. The ES4428 also provides a 16-bit

wide hardware interface with V.90-compatible modem

subsystems incorporated into the set-top box design.

The ES4427 incorporates a multi-standard TV encoder that

supports both the NTSC and PAL formats and CCIR-601 nonsquare operations. Two microphone ADCs and PLL clock

synthesizers are incorporated in the ES4427 device architecture.

The ES4427 includes an I/O-mapped auxiliary expansion port

that interfaces with the ES4428. Four pins of the port can be

configured as edge-triggered interrupts, supporting critical

functions, such as handling remote control and modem interrupt

requests, DVD/V CD loa der res et s and mode m boa rd rese ts.

Command and register ac cesses are issued throu gh the

DSC interface from the ES4428 DVD processor to the

ES4427 through the devi ce serial communication (DSC)

interface for accessing the internal registers of the

ES4427. The DSC interface port is comprised of three

interface signals, the strobe (DSC_S), data (DSC_D), and

clock (DSC_C).

The DSC port is selected when the DSC strobe goes high

and latches the data at th e risi ng edge of the cloc k. E ach

16-bit DSC transfer is co mprised of an address fo llowed

by data.

The ES4428 is available in an industry-standard 208-pin Plastic

Quad Flat Pack (PQFP ) package, while the ES4427 is available

in an industry-standard 100-pin PQFP package.

ES4428 FEATURES

• On-chip hardware interface with V.90 data/fax/voice modem

subsystem implemented

• 640 x 480 NTSC and 640 x 576 PAL television video formats

supported

• Configurable for browser/DVD applications

• Hardware support for infrared remote control and/or wireless

keyboard

• On-chip MPEG audio/video decoder and system parser

• On-chip on-screen display (OSD) controller supports 4-bit

blending.

• On-chip subpicture unit (SPU) decoder supports karaoke lyric,

subtitle and closed captioning functions.

• VideoCD 1.1 and 2.0, Interactive 3.0, Super VCD and Audio CD

compatibility available with Video CD / Super VCD player

configuration

• VideoCD 1.1 and 2.0, Interactive 3.0, Super VCD, Audio CD

and MP3 compatibility available with Super VCD / DVD player

configuration

• DTS audio decoding supported

• Programmable multimedia processor architecture

• ISO/IEC 13818-2 MPEG-2 compliant

• ISO/IEC 11172 MPEG-1 compliant

ES4427 FEATURES

• 8-bit DSC parallel bus interface generates edge-triggered

interupts for data read/write interfacing with ES4428

• Dual microphone and vocal assist hardware support provided

• PLL clock synthesizer based on 27 MHz crystal input generates

required clocks for video encoder, video DACs and video

processor

SOFTWARE SUPPORT

• Software stack support for the POP3, SMTP and SNMP Internet

e-mail protocols defined by RFC 821, RFC 1157and RFC 2449

• Software stack support provided for the HTTP Web browsing

protocol defined by RFC 1945, RFC 2068 and RFC 2616

• Software stack support provided for the TCP/IP Internet

protocols defined by RFC 791 and RFC 793

• Software stack support provided for RTP payload format for

MPEG-1/2 and H.261 video streaming protocols defined by

RFC 2032, RFC 2038 and RFC 2250

• Software support for HTML 1.0, 2.0 and 3.2, *.aiff, *.au and

*.wav audio file formats and *.gif, *.jpg and *.xbm graphic file

formats, JavaScript 1.1, SSL 2.0 and SSL 3.0

• Character generation and software support for English,

Big 5/GB Chinese and Japanese fonts

• Software support for infrared remote control and wireless

keyboard

ESS Technology, Inc. SAM0358-052201 1

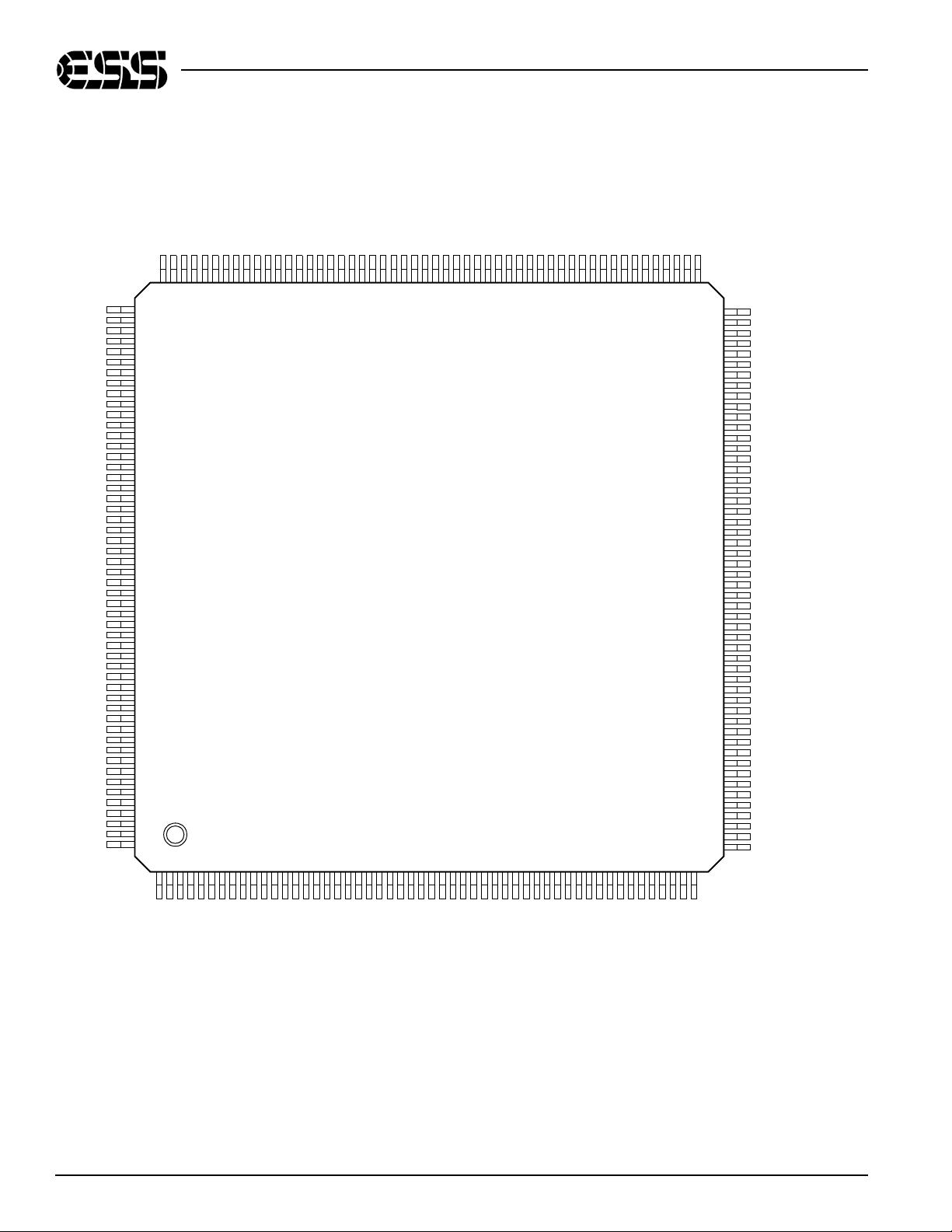

ES4428 PINOUT

Figure 1 shows the ES4428 device pinout.

NC

NC

VSS

VCC

NC

VPP

AUX0

AUX1

AUX2

VSS

VCC

AUX3

AUX4

AUX5

AUX6

AUX7

LOE#

VSS

VCC

LCS0#

LCS1#

LCS2#

LCS3#

VSS

LD0

LD1

LD2

LD3

LD4

VCC

VSS

LD5

LD6

LD7

LD8

LD9

LD10

LD11

VSS

VCC

LD12

LD13

LD14

LD15

LWRLL#

LWRHL#

VSS

VCC

NC

NC

LA0

LA1

LA2

LA3

VSS

NCNCNC

NC

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

1 2 3 4 5 6 7 8 9101112131415161718192021222324252627282930313233343536373839404142434445464748495051

NC

152

151

150

149

VCC

148

VSS

147

NC

146

NCNCNCNCHD15

144

145

143

HD4

HD5

HD6

HD2

VSS

129

128

127

126

HD3

125

124

HD1

123

HD0

122

VCC

121

142

141

HD14

140

VCC

139

VSS

138

HD13

137

HD12

136

HD11

135

HD10

134

HD9

133

HD8

132

HD7

131

VCC

130

ES4428

208-Pin PQFP Package

VSS

120

HSYNC#

119

VSYNC#

118

PCLKQSCN

117

PCLK2XSCN

116

YUV7

115

ES4428/ES4427 PRODUCT BRIEF

YUV6

YUV5

VSS

VCC

YUV4

YUV3

YUV2

YUV1

YUV0

DCLK

105

106

107

108

109

110

111

112

113

114

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

52

53

VCC

VSS

DSCK

DQM

DCS0#

VCC

VSS

DCS1#

DB15

DB14

DB13

DB12

VCC

VSS

DB11

DB10

DB9

DB8

DB7

DB6

VSS

VCC

DB5

DB4

DB3

DB2

DB1

DB0

VSS

VCC

DRAS2#/DBANKSEL0

DRAS1#/DBANKSEL1

DRAS0#

DWE#

DOE#/DSCK_EN

DCAS#

VCC

VSS

DMA11

DMA10

DMA9

DMA8

DMA7

DMA6

VSS

VCC

DMA5

DMA4

DMA3

DMA2

DMA1

DMA0

NC

NC

NC

LA6

LA7

LA8

LA4

VCC

LA9

LA5

VSS

VCC

LA11

LA10

LA12

VSS

LA13

VCC

LA14

LA15

LA16

LA17

LA18

LA19

VSS

VCC

LA21

LA20

TDMDR

RESET#

TDMCLK

TDMDX/RSEL

VSS

TDMFS

VCC

TDMTSC#

TWS/SEL_PLL1

SEL_PLL2

TSD/SEL_PLL0

MCLK

NC

VSS

VCC

TBCK

XIN

RSD

RWS

RBCK

VSS

VCC

XOUT

APLLCAP

Figure 1 ES4428 Device Pinout

2 SAM0358-052201 ESS Technology, Inc.

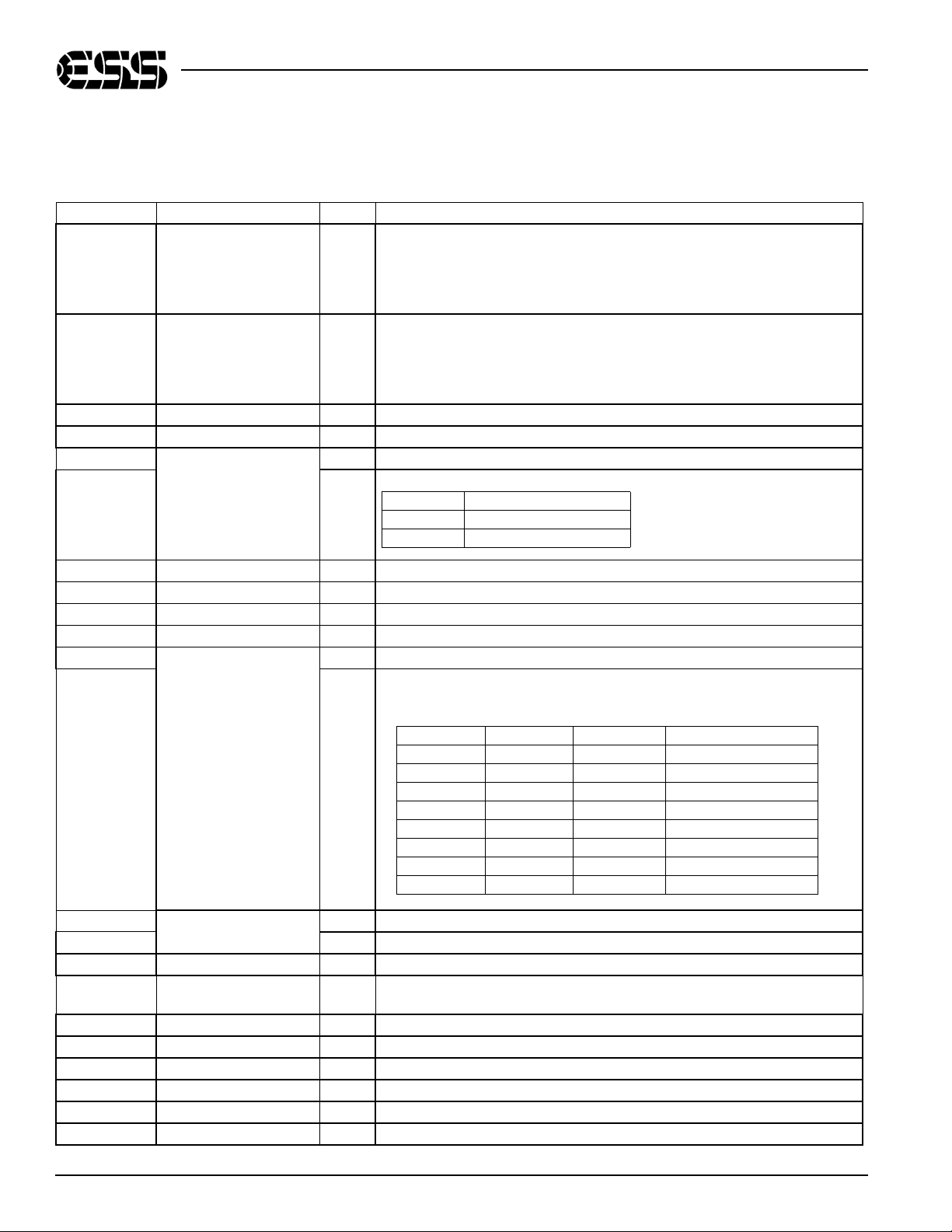

ES4428 PIN DESCRIPTION

Table 1 lists the pin descriptions for the ES4428.

Table 1 ES4428 Pin Descriptions

Name Number I/O Definition

1, 9, 18, 27, 35, 44, 51,

59, 68, 75, 83, 92, 99,

VCC

VSS

LA[21:0] 23:19,16:10,7:2,207:204 O Device address output.

RESET# 24 I Reset.

TDMDX

RSEL

104, 1 11, 121, 130, 139,

148, 157, 164, 172, 183,

193, 201

8, 17, 26, 34, 43, 52, 6 0,

67, 76, 84, 91, 98, 103,

1 12, 1 20, 12 9, 138, 14 7,

156, 163, 171, 177, 184,

192, 200, 208

25

I

3.3V power supply.

I

Ground.

O TDM transmit data output.

I ROM Select.

RSEL Selection

0 16-bit ROM

1 8-bit ROM

ES4428/ES4427 PRODUCT BRIEF

TDMDR 28 I TDM rec eive data inpu t.

TDMCLK 29 I TDM clock input.

TDMFS 30 I TDM fram e sync.

TDMTSC# 31 O TDM output enable.

TWS

SEL_PLL1

TSD 33 O Audio transmit serial data output.

SEL_PLL0 I Refer to the description and matrix for SEL_PLL1 pin 32.

SEL_PLL2 36 I Refer to the description and matrix for SEL_PLL1 pin 32.

NC

MCLK 39 I/O Audio master clock for audio DAC.

TBCK 40 I/O Audio transmit bit clock output.

RSD 45 I Audio receive serial data input.

RWS 46 I Audio receive frame sync input.

RBCK 47 I Audio receive bit clock input.

APLLCAP 48 I Analog PLL capacitor input.

37, 38, 41, 42, 146:142,

155:149, 158, 203:202

32

O Audio transmit frame sync output.

System and DSCK output clock frequency selection at reset time. The matrix

below lists the available clock frequencies and their respective PLL bit

settings..

SEL_PLL2 SEL_PLL1 SEL_PLL0 Clock Output

0 0 0 VCO doesn’t work.

00127 MHz

0 1 0 Bypass mode

01154 MHz

1 0 0 121.5 MHz

10181 MHz

1 1 0 94.5 MHz

1 1 1 108 MHz

—

No connect. Leave open.

3 SAM0358-052201 ESS Technology, Inc.

Loading...

Loading...