Page 1

ESP32 Technical Reference Manual

Espressif Systems

August 31, 2016

Page 2

About This Manual

ESP32 Technical Reference Manual targets application developers. The manual provides detailed and

complete information on how to use the ESP32 memory and peripherals.

Release Notes

Date Version Release notes

2016.08 V1.0 Initial release.

Disclaimer and Copyright Notice

Information in this document, including URL references, is subject to change without notice. THIS DOCUMENT

IS PROVIDED AS IS WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF

MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY

OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

All liability, including liability for infringement of any proprietary rights, relating to use of information in this

document is disclaimed. No licenses express or implied, by estoppel or otherwise, to any intellectual property

rights are granted herein. The Wi-Fi Alliance Member logo is a trademark of the Wi-Fi Alliance. The Bluetooth

logo is a registered trademark of Bluetooth SIG.

All trade names, trademarks and registered trademarks mentioned in this document are property of their

respective owners, and are hereby acknowledged.

Copyright © 2016 Espressif Inc. All rights reserved.

Page 3

Contents

1 System and Memory 8

1.1 Introduction 8

1.2 Features 8

1.3 Functional Description 10

1.3.1 Address Mapping 10

1.3.2 Embedded Memory 10

1.3.2.1 Internal ROM 0 11

1.3.2.2 Internal ROM 1 11

1.3.2.3 Internal SRAM 0 12

1.3.2.4 Internal SRAM 1 12

1.3.2.5 Internal SRAM 2 13

1.3.2.6 DMA 13

1.3.2.7 RTC FAST Memory 13

1.3.2.8 RTC SLOW Memory 13

1.3.3 External Memory 13

1.3.4 Peripherals 14

1.3.4.1 Asymmetric PID Controller Peripheral 15

1.3.4.2 Non-Contiguous Peripheral Memory Ranges 15

1.3.4.3 Memory Speed 16

2 Interrupt Matrix 17

2.1 Introduction 17

2.2 Features 17

2.3 Functional Description 17

2.3.1 Peripheral Interrupt Source 17

2.3.2 CPU Interrupt 20

2.3.3 Allocate Peripheral Interrupt Sources to Peripheral Interrupt on CPU 20

2.3.4 CPU NMI Interrupt Mask 21

2.3.5 Query Current Interrupt Status of Peripheral Interrupt Source 21

3 Reset and Clock 22

3.1 System Reset 22

3.1.1 Introduction 22

3.1.2 Reset Source 22

3.2 System Clock 23

3.2.1 Introduction 23

3.2.2 Clock Source 24

3.2.3 CPU Clock 24

3.2.4 Peripheral Clock 25

3.2.4.1 APB_CLK Source 25

3.2.4.2 REF_TICK Source 26

3.2.4.3 LEDC_SCLK Source 26

3.2.4.4 APLL_SCLK Source 26

3.2.4.5 PLL_D2_CLK Source 26

Page 4

3.2.4.6 Clock Source Considerations 27

3.2.5 Wi-Fi BT Clock 27

3.2.6 RTC Clock 27

4 IO_MUX and GPIO Matrix 28

4.1 Introduction 28

4.2 Peripheral Input via GPIO Matrix 29

4.2.1 Summary 29

4.2.2 Functional Description 29

4.2.3 Simple GPIO Input 30

4.3 Peripheral Output via GPIO Matrix 30

4.3.1 Summary 30

4.3.2 Functional Description 30

4.3.3 Simple GPIO Output 31

4.4 Direct I/O via IO_MUX 31

4.4.1 Summary 31

4.4.2 Functional Description 32

4.5 RTC IO_MUX for Low Power and Analog I/O 32

4.5.1 Summary 32

4.5.2 Functional Description 32

4.6 Light-sleep Mode Pin Functions 32

4.7 Pad Hold Feature 33

4.8 I/O Pad Power Supply 33

4.8.1 VDD_SDIO Power Domain 33

4.9 Peripheral Signal List 34

4.10 IO_MUX Pad List 38

4.11 RTC_MUX Pin List 39

4.12 Register Summary 40

4.13 Registers 45

5 LED_PWM 66

5.1 Introduction 66

5.2 Functional Description 66

5.2.1 Architecture 66

5.2.2 Timers 67

5.2.3 Channels 67

5.2.4 Interrupts 68

5.3 Register Summary 68

5.4 Registers 71

6 Remote Controller Peripheral 81

6.1 Introduction 81

6.2 Functional Description 81

6.2.1 RMT Architecture 81

6.2.2 RMT RAM 82

6.2.3 Clock 82

6.2.4 Transmitter 82

Page 5

6.2.5 Receiver 83

6.2.6 Interrupts 83

6.3 Register Summary 84

6.4 Registers 85

7 PULSE_CNT 90

7.1 Introduction 90

7.2 Functional Description 90

7.2.1 Architecture 90

7.2.2 Counter Channel Inputs 90

7.2.3 Watchpoints 91

7.2.4 Examples 92

7.2.5 Interrupts 92

7.3 Register Summary 92

7.4 Registers 94

8 64-bit Timers 98

8.1 Introduction 98

8.2 Functional Description 98

8.2.1 16-bit Prescaler 98

8.2.2 64-bit Time-base Counter 98

8.2.3 Alarm Generation 99

8.2.4 MWDT 99

8.2.5 Interrupts 99

8.3 Register summary 99

8.4 Registers 101

9 Watchdog Timers 108

9.1 Introduction 108

9.2 Features 108

9.3 Functional Description 108

9.3.1 Clock 108

9.3.1.1 Operating Procedure 109

9.3.1.2 Write Protection 109

9.3.1.3 Flash Boot Protection 109

9.3.1.4 Registers 110

10 AES Accelerator 111

10.1 Introduction 111

10.2 Features 111

10.3 Functional Description 111

10.3.1 AES Algorithm Operations 111

10.3.2 Key, Plaintext and Ciphertext 111

10.3.3 Endianness 112

10.3.4 Encryption and Decryption Operations 114

10.3.5 Speed 114

10.4 Register summary 114

Page 6

10.5 Registers 116

11 SHA Accelerator 118

11.1 Introduction 118

11.2 Features 118

11.3 Functional Description 118

11.3.1 Padding and Parsing the Message 118

11.3.2 Message Digest 118

11.3.3 Hash Operation 119

11.3.4 Speed 119

11.4 Register Summary 119

11.5 Registers 121

Page 7

List of Tables

1 Address Mapping 10

2 Embedded Memory Address Mapping 11

3 Module with DMA 13

4 External Memory Address Mapping 14

5 Peripheral Address Mapping 14

6 PRO_CPU, APP_CPU interrupt configuration 18

7 CPU Interrupts 20

8 PRO_CPU and APP_CPU reset reason values 22

9 CPU_CLK Source 24

10 CPU_CLK Derivation 25

11 Peripheral Clock Usage 25

12 APB_CLK Derivation 26

13 REF_TICK Derivation 26

14 LEDC_SCLK Derivation 26

15 IO_MUX Light-sleep Pin Function Registers 32

16 GPIO Matrix Peripheral Signals 34

17 IO_MUX Pad Summary 38

18 RTC_MUX Pin Summary 39

26 Operation Mode 111

27 AES Text Endianness 112

28 AES-128 Key Endianness 113

29 AES-192 Key Endianness 113

30 AES-256 Key Endianness 113

Page 8

List of Figures

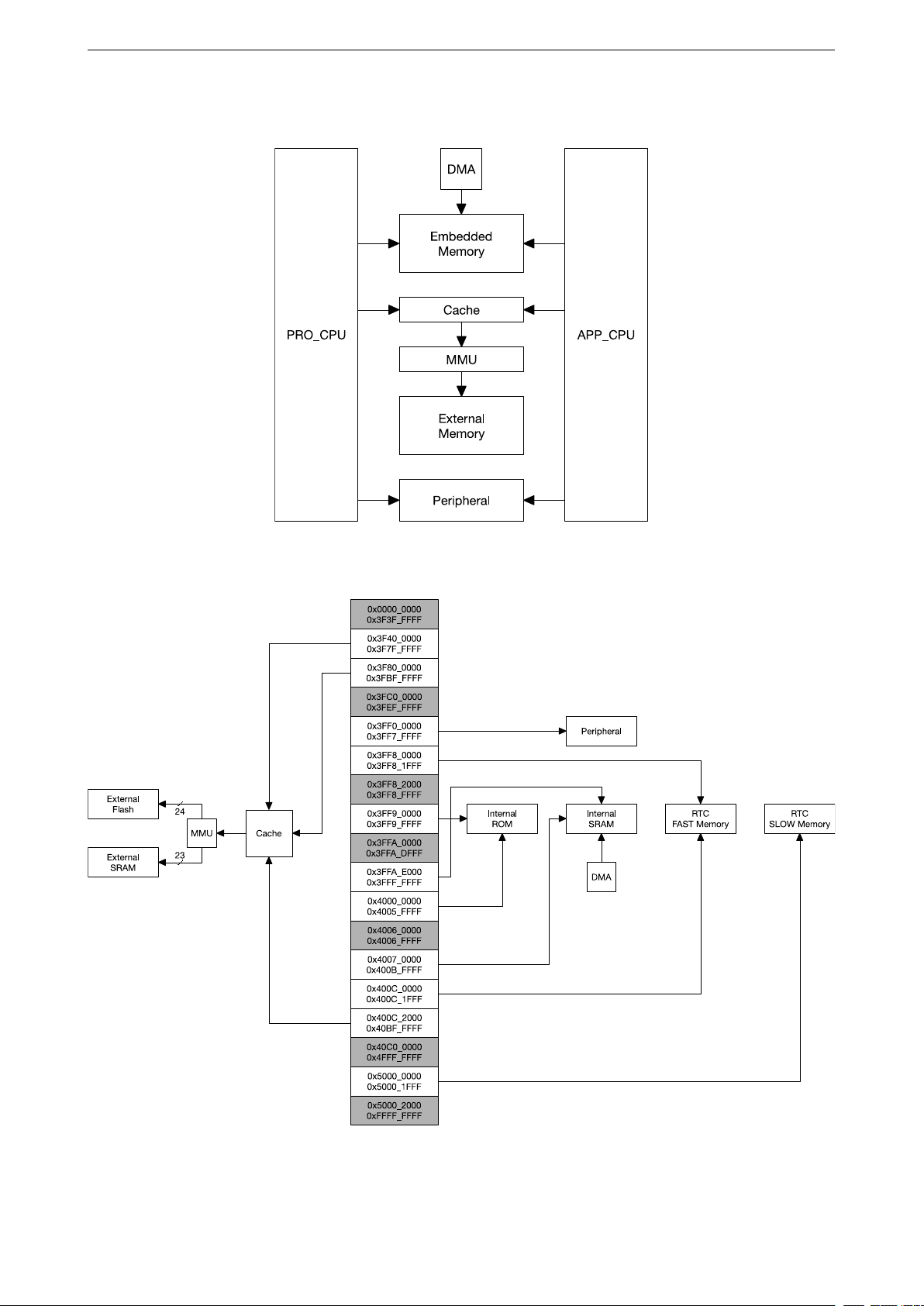

1 System Structure 9

2 System Address Mapping 9

3 Interrupt Matrix Structure 17

4 System Reset 22

5 System Clock 23

6 IO_MUX, RTC IO_MUX and GPIO Matrix Overview 28

7 Peripheral Input via IO_MUX, GPIO Matrix 29

8 Output via GPIO Matrix 31

9 ESP32 I/O Pad Power Sources 33

10 LED_PWM Architecture 66

11 LED_PWM High-speed Channel Diagram 66

12 LED PWM Output Signal Diagram 67

13 Output Signal Diagram of Gradient Duty Cycle 68

14 RMT Architecture 81

15 Data Structure 82

16 PULSE_CNT Architecture 90

17 PULSE_CNT Upcounting Diagram 92

18 PULSE_CNT Downcounting Diagram 92

Page 9

1 SYSTEM AND MEMORY

1. System and Memory

1.1 Introduction

The ESP32 is a dual-core system with two Harvard Architecture Xtensa LX6 CPUs. All embedded memory,

external memory and peripherals are located on the data bus and/or the instruction bus of these CPUs.

With some minor exceptions (see below), the address mapping of two CPUs is symmetric, meaning they use the

same addresses to access the same memory. Multiple peripherals in the system can access embedded memory

via DMA.

The two CPUs are named “PRO_CPU” and “APP_CPU” (for “protocol” and “application”), however for most

purposes the two CPUs are interchangeable.

1.2 Features

• Address Space

– Symmetric address mapping

– 4 GB (32-bit) address space for both data bus and instruction bus

– 1296 KB embedded memory address space

– 19704 KB external memory address space

– 512 KB peripheral address space

– Some embedded and external memory regions can be accessed by either data bus or instruction bus

– 328 KB DMA address space

• Embedded Memory

– 448 KB Internal ROM

– 520 KB Internal SRAM

– 8 KB RTC FAST Memory

– 8 KB RTC SLOW Memory

• External Memory

Off-chip SPI memory can be mapped into the available address space as external memory. Parts of the

embedded memory can be used as transparent cache for this external memory.

– Supports up to 16 MB off-Chip SPI Flash.

– Supports up to 8 MB off-Chip SPI SRAM.

• Peripherals

– 41 peripherals

• DMA

– 13 modules are capable of DMA operation

Espressif Systems 8 ESP32 Technical Reference Manual V1.0

Page 10

1.2 Features 1 SYSTEM AND MEMORY

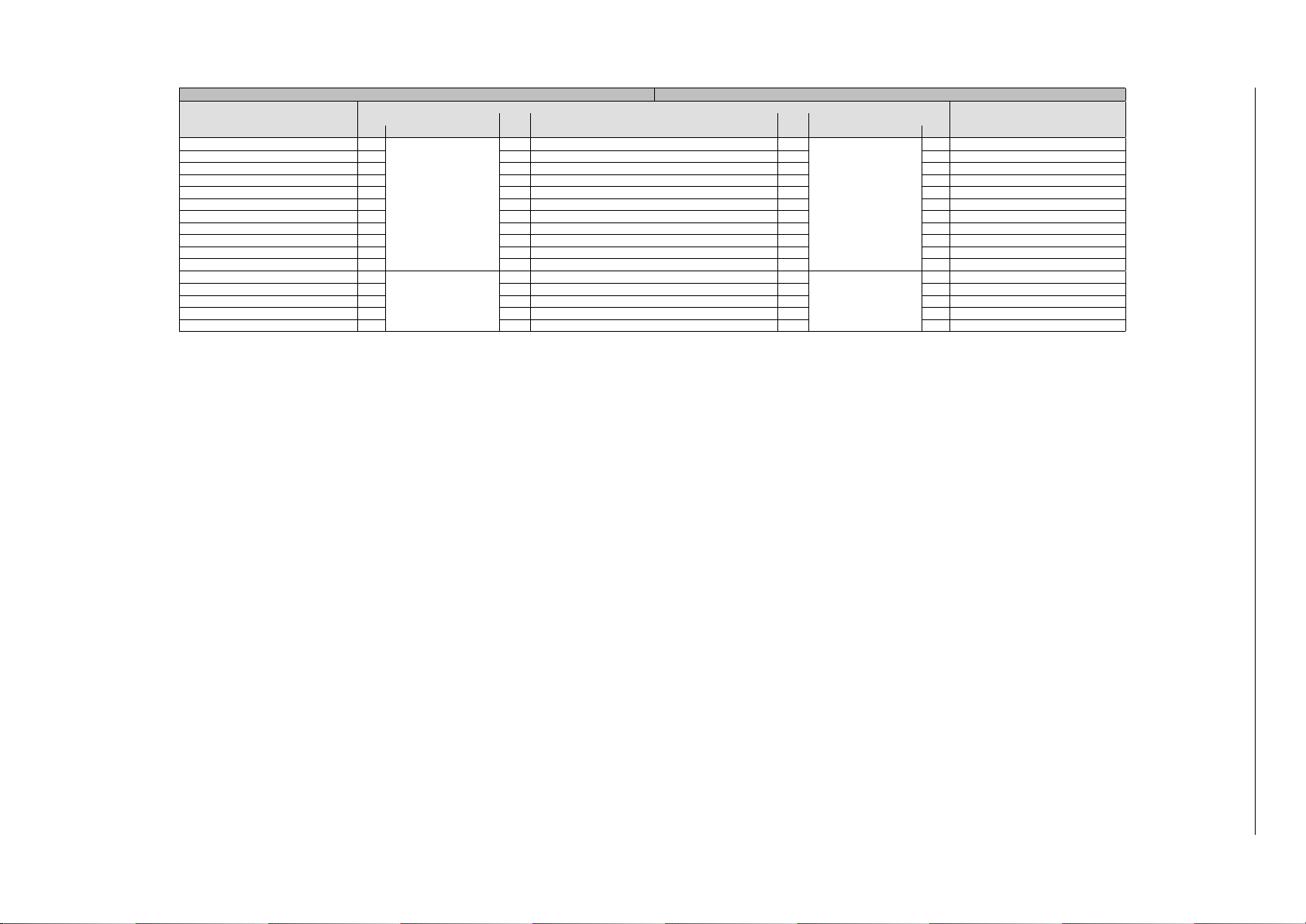

Figure 1 block diagram illustrates the system structure, the block diagram in Figure 2 illustrates the address map

structure.

Figure 1: System Structure

Figure 2: System Address Mapping

Espressif Systems 9 ESP32 Technical Reference Manual V1.0

Page 11

1.3 Functional Description 1 SYSTEM AND MEMORY

1.3 Functional Description

1.3.1 Address Mapping

Each of the two Harvard Architecture Xtensa LX6 CPUs has 4 GB (32-bit) address space. Address spaces are

symmetric between the two CPUs.

Addresses below 0x4000_0000 are serviced using the data bus. Addresses in the range 0x4000_0000 ~

0x4FFF_FFFF are serviced using the instruction bus. Finally, addresses over and including 0x5000_0000 are

shared by the data and instruction bus.

The data bus and instruction bus are both little-endian: for example, byte addresses 0x0, 0x1, 0x2, 0x3 access

the least significant, second least significant, second most significant, and most significant bytes of the 32-bit

word stored at address 0x0, respectively. The CPU can access data bus addresses via aligned or non-aligned

byte, half-word and word read and write operations. The CPU can read and write data through the instruction

bus, but only in a word aligned manner; non-word-aligned access will cause a CPU exception.

Each CPU can directly access embedded memory through both the data bus and the instruction bus, external

memory which is mapped into the address space (via transparent caching & MMU) and peripherals. Table 1

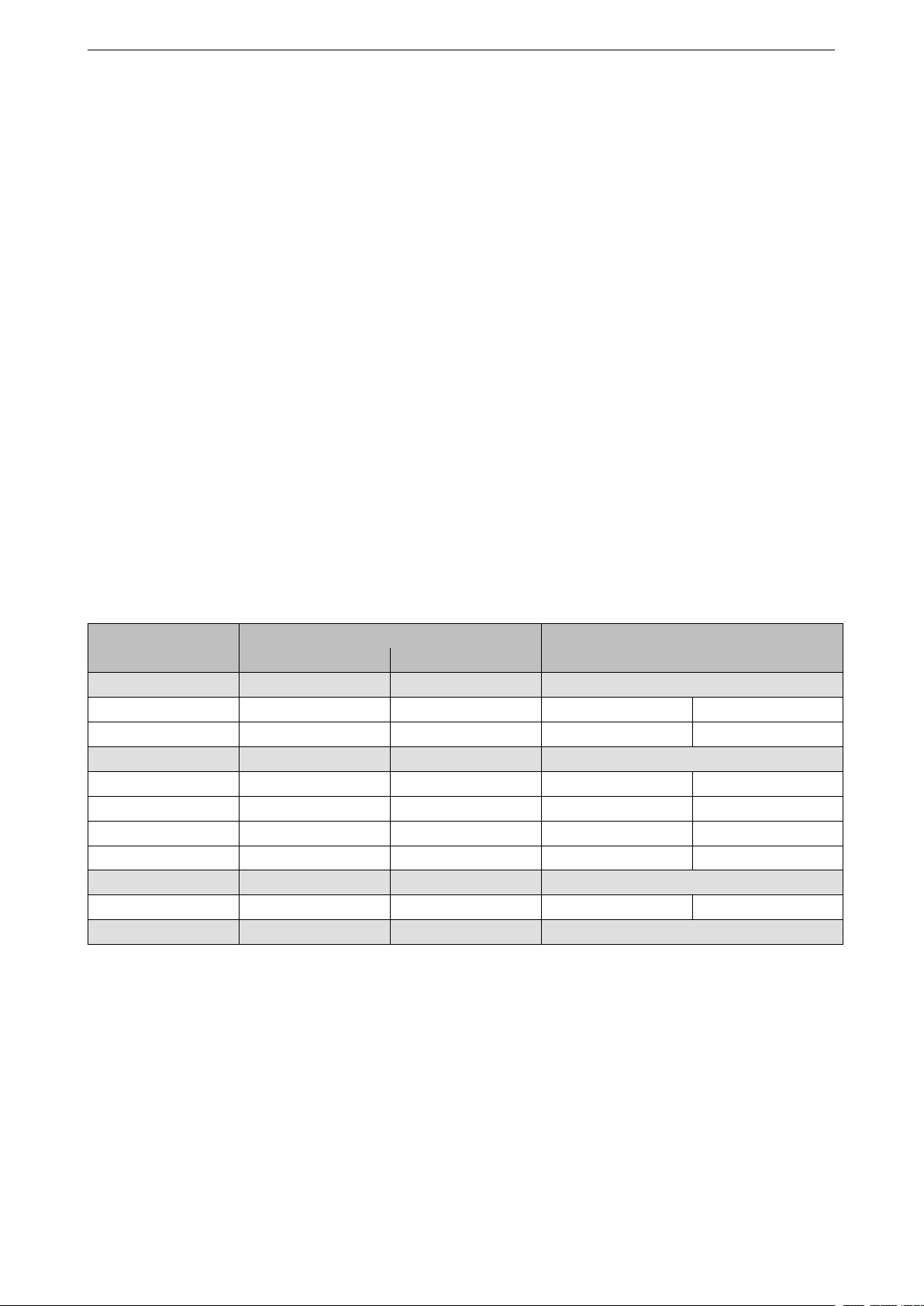

illustrates address ranges that can be accessed by each CPU’s data bus and instruction bus.

Some embedded memories and some external memories can be accessed via the data bus or the instruction

bus. In these cases, the same memory is available to either of the CPUs at two address ranges.

Table 1: Address Mapping

Bus Type

Data 0x3F40_0000 0x3F7F_FFFF 4 MB External Memory

Data 0x3F80_0000 0x3FBF_FFFF 4 MB External Memory

Data 0x3FF0_0000 0x3FF7_FFFF 512 KB Peripheral

Data 0x3FF8_0000 0x3FFF_FFFF 512 KB Embedded Memory

Instruction 0x4000_0000 0x400C_1FFF 776 KB Embedded Memory

Instruction 0x400C_2000 0x40BF_FFFF 11512 KB External Memory

Data Instruction 0x5000_0000 0x5000_1FFF 8 KB Embedded Memory

Low Address High Address

0x0000_0000 0x3F3F_FFFF Reserved

0x3FC0_0000 0x3FEF_FFFF 3 MB Reserved

0x40C0_0000 0x4FFF_FFFF 244 MB Reserved

0x5000_2000 0xFFFF_FFFF Reserved

Boundary Address

Size Target

1.3.2 Embedded Memory

The Embedded Memory consists of four segments: internal ROM (448 KB), internal SRAM (520 KB), RTC FAST

memory (8 KB) and RTC SLOW memory (8 KB).

The 448 KB internal ROM is divided into two parts: Internal ROM 0 (384 KB) and Internal ROM 1 (64 KB).

The 520 KB internal SRAM is divided into three parts: Internal SRAM 0 (192 KB), Internal SRAM 1 (128 KB), and

Internal SRAM 2 (200 KB).

RTC FAST Memory and RTC SLOW Memory are both implemented as SRAM.

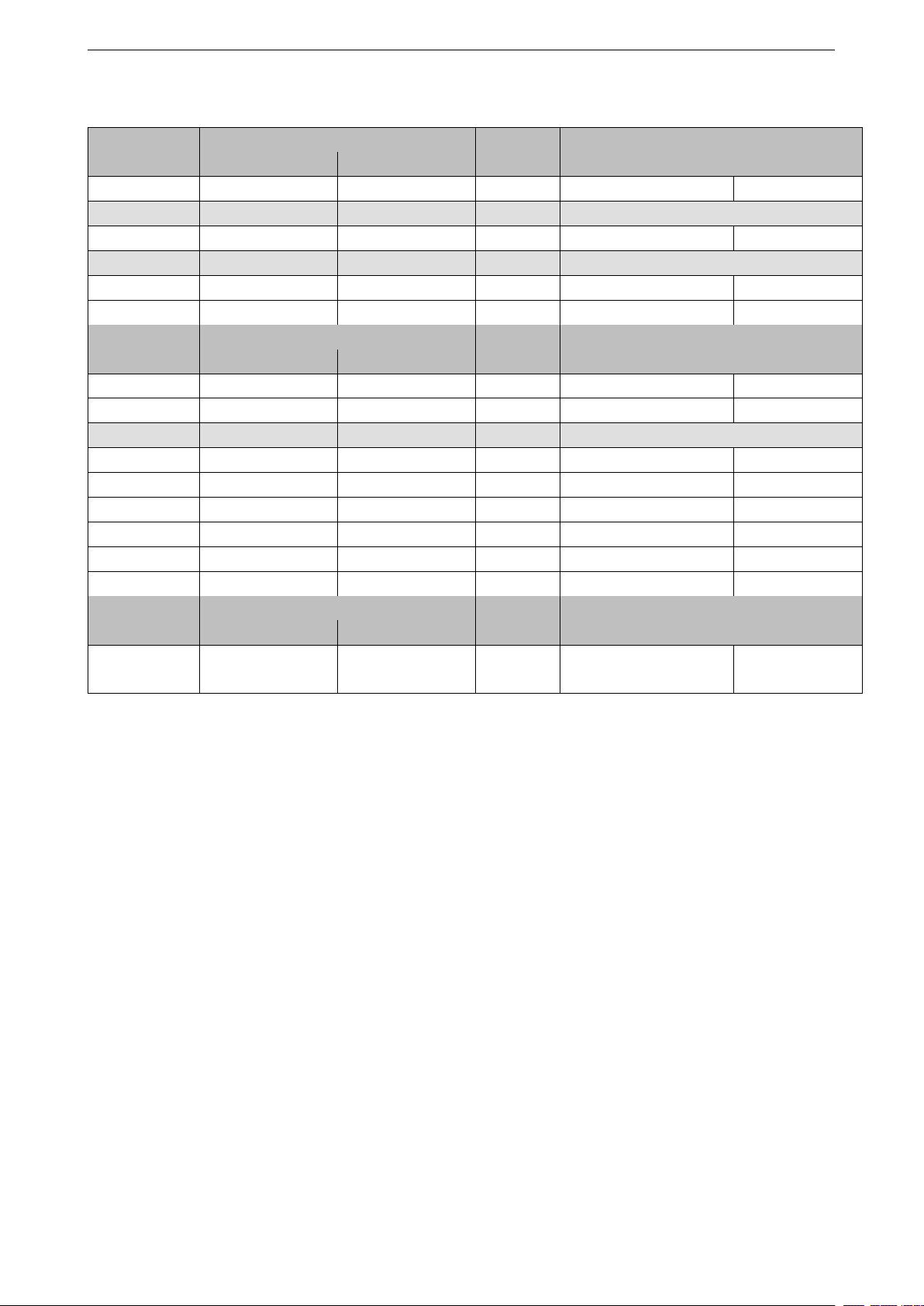

Table 2 lists all embedded memories and their address ranges on the data and instruction buses.

Espressif Systems 10 ESP32 Technical Reference Manual V1.0

Page 12

1.3 Functional Description 1 SYSTEM AND MEMORY

Table 2: Embedded Memory Address Mapping

Bus Type

Data 0x3FF8_0000 0x3FF8_1FFF 8 KB RTC FAST Memory PRO_CPU Only

Data 0x3FF9_0000 0x3FF9_FFFF 64 KB Internal ROM 1 -

Data 0x3FFA_E000 0x3FFD_FFFF 200 KB Internal SRAM 2 DMA

Data 0x3FFE_0000 0x3FFF_FFFF 128 KB Internal SRAM 1 DMA

Bus Type

Instruction 0x4000_0000 0x4000_7FFF 32 KB Internal ROM 0 Remap

Instruction 0x4000_8000 0x4005_FFFF 352 KB Internal ROM 0 -

Instruction 0x4007_0000 0x4007_FFFF 64 KB Internal SRAM 0 Cache

Instruction 0x4008_0000 0x4009_FFFF 128 KB Internal SRAM 0 -

Instruction 0x400A_0000 0x400A_FFFF 64 KB Internal SRAM 1 -

Instruction 0x400B_0000 0x400B_7FFF 32 KB Internal SRAM 1 Remap

Instruction 0x400B_8000 0x400B_FFFF 32 KB Internal SRAM 1 -

Instruction 0x400C_0000 0x400C_1FFF 8 KB RTC FAST Memory PRO_CPU Only

Bus Type

Data Instruc-

tion

Low Address High Address

0x3FF8_2000 0x3FF8_FFFF 56 KB Reserved -

0x3FFA_0000 0x3FFA_DFFF 56 KB Reserved -

Low Address High Address

0x4006_0000 0x4006_FFFF 64 KB Reserved -

Low Address High Address

0x5000_0000 0x5000_1FFF 8 KB RTC SLOW Memory -

Boundary Address

Boundary Address

Boundary Address

Size Target Comment

Size Target Comment

Size Target Comment

1.3.2.1 Internal ROM 0

The capacity of Internal ROM 0 is 384 KB, It is accessible by both CPUs through the address range

0x4000_0000 ~ 0x4005_FFFF, which is on the instruction bus.

The address range of the first 32 KB of the ROM 0 (0x4000_0000 ~ 0x4000_7FFF) can be re-mapped to access

a part of Internal SRAM 1 that normally resides in the memory range 0x400B_0000 ~ 0x400B_7FFF instead.

While remapping, such 32 KB SRAM can not be accessed by address range 0x400B_0000 ~ 0x400B_7FFF any

more, but it can still be accessible through the data bus (0x3FFE_8000 ~ 0x3FFE_FFFF). This can be done on a

per-CPU basis: setting bit 0 of register DPORT_PRO_BOOT_REMAP_CTRL_REG or

DPORT_APP_BOOT_REMAP_CTRL_REG will remap SRAM for the PRO_CPU and APP_CPU,

respectively.

1.3.2.2 Internal ROM 1

The capacity of Internal ROM 1 is 64 KB. It can be read by either CPU at address range 0x3FF9_0000 ~

0x3FF9_FFFF of the data bus.

Espressif Systems 11 ESP32 Technical Reference Manual V1.0

Page 13

1.3 Functional Description 1 SYSTEM AND MEMORY

1.3.2.3 Internal SRAM 0

The capacity of Internal SRAM 0 is 192 KB. Hardware can be configured to use the first 64KB to cache external

memory access. When not used as cache, the first 64KB can be read and written by either CPU at addresses

0x4007_0000 ~ 0x4007_7FFF of the instruction bus. The remaining 128 KB can always be read and written by

either CPU at addresses 0x4007_8000 ~ 0x4007_FFFF of instruction bus.

1.3.2.4 Internal SRAM 1

The capacity of Internal SRAM 1 is 128 KB. Either CPU can read and write this memory at addresses

0x3FFE_0000 ~ 0x3FFF_FFFF of the data bus, and also at addresses 0x400A_0000 ~ 0x400B_FFFF of the

instruction bus.

The address range accessed via the instruction bus is in reverse order (word-wise) compared to access via the

data bus. That is to say, address

0x3FFE_0000 and 0x400B_FFFC access the same word

0x3FFE_0004 and 0x400B_FFF8 access the same word

0x3FFE_0008 and 0x400B_FFF4 access the same word

……

0x3FFF_FFF4 and 0x400A_0008 access the same word

0x3FFF_FFF8 and 0x400A_0004 access the same word

0x3FFF_FFFC and 0x400A_0000 access the same word

The data bus and instruction bus of the CPU are still both little endian, so the byte order of individual words is not

reversed between address spaces. For example, address

0x3FFE_0000 accesses the least significant byte in the word accessed by 0x400B_FFFC.

0x3FFE_0001 accesses the second least significant byte in the word accessed by 0x400B_FFFC.

0x3FFE_0002 accesses the second most significant byte in the word accessed by 0x400B_FFFC.

0x3FFE_0003 accesses the most significant byte in the word accessed by 0x400B_FFFC.

0x3FFE_0004 accesses the least significant byte in the word accessed by 0x400B_FFF8.

0x3FFE_0005 accesses the second least significant byte in the word accessed by 0x400B_FFF8.

0x3FFE_0006 accesses the second most significant byte in the word accessed by 0x400B_FFF8.

0x3FFE_0007 accesses the most significant byte in the word accessed by 0x400B_FFF8.

……

0x3FFF_FFF8 accesses the least significant byte in the word accessed by 0x400A_0004.

0x3FFF_FFF9 accesses the second least significant byte in the word accessed by 0x400A_0004.

0x3FFF_FFFA accesses the second most significant byte in the word accessed by 0x400A_0004.

0x3FFF_FFFB accesses the most significant byte in the word accessed by 0x400A_0004.

0x3FFF_FFFC accesses the least significant byte in the word accessed by 0x400A_0000.

0x3FFF_FFFD accesses the second most significant byte in the word accessed by 0x400A_0000.

0x3FFF_FFFE accesses the second most significant byte in the word accessed by 0x400A_0000.

0x3FFF_FFFF accesses the most significant byte in the word accessed by 0x400A_0000.

Part of this memory can be remapped to the ROM 0 address space. See Internal Rom 0 for more

information.

Espressif Systems 12 ESP32 Technical Reference Manual V1.0

Page 14

1.3 Functional Description 1 SYSTEM AND MEMORY

1.3.2.5 Internal SRAM 2

The capacity of Internal SRAM 2 is 200 KB. It can be read and written by either CPU at addresses 0x3FFA_E000

~ 0x3FFD_FFFF on the data bus.

1.3.2.6 DMA

DMA uses the same addressing as the CPU data bus to read and write Internal SRAM 1 and Internal SRAM 2.

This means DMA uses address range 0x3FFE_0000 ~ 0x3FFF_FFFF to read and write Internal SRAM 1 and

address range 0x3FFA_E000 ~ 0x3FFD_FFFF to read and write Internal SRAM 2.

In the ESP32, 13 peripherals are equipped with DMA. Table 3 lists these peripherals.

Table 3: Module with DMA

UART0 UART1 UART2

SPI1 SPI2 SPI3

I2S0 I2S1

SDIO Slave SDMMC

EMAC

BT WIFI

1.3.2.7 RTC FAST Memory

RTC FAST Memory is 8 KB of SRAM. It can be read and written by PRO_CPU only at address range

0x3FF8_0000 ~ 0x3FF8_1FFF on the data bus or address range 0x400C_0000 ~ 0x400C_1FFF on the

instruction bus. Unlike most other memory regions, RTC FAST memory cannot be accessed by the

APP_CPU.

The two address ranges of PRO_CPU access RTC FAST Memory in the same order, so for example, address

0x3FF8_0000 and 0x400C_0000 access the same word. On the APP_CPU, these address ranges do not

provide access to RTC FAST Memory or any other memory location.

1.3.2.8 RTC SLOW Memory

RTC SLOW Memory is 8 KB of SRAM which can be read from and written by either CPU at address range

0x5000_0000 ~ 0x5000_1FFF. This address range is shared by both the data bus and the instruction bus.

1.3.3 External Memory

The ESP32 can access external SPI flash and SPI SRAM as external memory. Table 4 provides a list of external

memories that can be accessed by either CPU at a range of addresses on the data and instruction buses. When

a CPU accesses external memory through the Cache and MMU, the cache will map the CPU’s address to an

external physical memory address (in the external memory’s address space), according to the MMU settings. Due

to this address mapping, the ESP32 can address up to 16 MB External Flash and 8 MB External SRAM.

Espressif Systems 13 ESP32 Technical Reference Manual V1.0

Page 15

1.3 Functional Description 1 SYSTEM AND MEMORY

Table 4: External Memory Address Mapping

Bus Type

Data 0x3F40_0000 0x3F7F_FFFF 4 MB External Flash Read

Data 0x3F80_0000 0x3FBF_FFFF 4 MB External SRAM Read and Write

Bus Type

Instruction 0x400C_2000 0x40BF_FFFF 11512 KB External Flash Read

Low Address High Address

Low Address High Address

Boundary Address

Boundary Address

Size Target Comment

Size Target Comment

1.3.4 Peripherals

The ESP32 has 41 peripherals. Table 5 specifically describes the peripherals their respective address ranges.

Almost all peripheral modules can be accessed by either CPU at the same address, the only exception being the

PID Controller.

Table 5: Peripheral Address Mapping

Bus Type

Data 0x3FF0_0000 0x3FF0_0FFF 4 KB DPort Register

Data 0x3FF0_1000 0x3FF0_1FFF 4 KB AES Accelerator

Data 0x3FF0_2000 0x3FF0_2FFF 4 KB RSA Accelerator

Data 0x3FF0_3000 0x3FF0_3FFF 4 KB SHA Accelerator

Data 0x3FF0_4000 0x3FF0_4FFF 4 KB Secure Boot

Data 0x3FF1_0000 0x3FF1_3FFF 16 KB Cache MMU Table

Data 0x3FF1_F000 0x3FF1_FFFF 4 KB PID Controller Per-CPU peripheral

Data 0x3FF4_0000 0x3FF4_0FFF 4 KB UART0

Data 0x3FF4_2000 0x3FF4_2FFF 4 KB SPI1

Data 0x3FF4_3000 0x3FF4_3FFF 4 KB SPI0

Data 0x3FF4_4000 0x3FF4_4FFF 4 KB GPIO

Data 0x3FF4_8000 0x3FF4_8FFF 4 KB RTC

Data 0x3FF4_9000 0x3FF4_9FFF 4 KB IO MUX

Data 0x3FF4_B000 0x3FF4_BFFF 4 KB SDIO Slave One of three parts

Data 0x3FF4_C000 0x3FF4_CFFF 4 KB UDMA1

Data 0x3FF4_F000 0x3FF4_FFFF 4 KB I2S0

Data 0x3FF5_0000 0x3FF5_0FFF 4 KB UART1

Data 0x3FF5_3000 0x3FF5_3FFF 4 KB I2C0

Data 0x3FF5_4000 0x3FF5_4FFF 4 KB UDMA0

Low Address High Address

0x3FF0_5000 0x3FF0_FFFF 44 KB Reserved

0x3FF1_4000 0x3FF1_EFFF 44 KB Reserved

0x3FF2_0000 0x3FF3_FFFF 128 KB Reserved

0x3FF4_1000 0x3FF4_1FFF 4 KB Reserved

0x3FF4_5000 0x3FF4_7FFF 12 KB Reserved

0x3FF4_A000 0x3FF4_AFFF 4 KB Reserved

0x3FF4_D000 0x3FF4_EFFF 8 KB Reserved

0x3FF5_1000 0x3FF5_2FFF 8 KB Reserved

Boundary Address

Size Target Comment

Espressif Systems 14 ESP32 Technical Reference Manual V1.0

Page 16

1.3 Functional Description 1 SYSTEM AND MEMORY

Bus Type

Data 0x3FF5_5000 0x3FF5_5FFF 4 KB SDIO Slave One of three parts

Data 0x3FF5_6000 0x3FF5_6FFF 4 KB RMT

Data 0x3FF5_7000 0x3FF5_7FFF 4 KB PCNT

Data 0x3FF5_8000 0x3FF5_8FFF 4 KB SDIO Slave One of three parts

Data 0x3FF5_9000 0x3FF5_9FFF 4 KB LED PWM

Data 0x3FF5_A000 0x3FF5_AFFF 4 KB Efuse Controller

Data 0x3FF5_B000 0x3FF5_BFFF 4 KB Flash Encryption

Data 0x3FF5_E000 0x3FF5_EFFF 4 KB PWM0

Data 0x3FF5_F000 0x3FF5_FFFF 4 KB TIMG0

Data 0x3FF6_0000 0x3FF6_0FFF 4 KB TIMG1

Data 0x3FF6_4000 0x3FF6_4FFF 4 KB SPI2

Data 0x3FF6_5000 0x3FF6_5FFF 4 KB SPI3

Data 0x3FF6_6000 0x3FF6_6FFF 4 KB SYSCON

Data 0x3FF6_7000 0x3FF6_7FFF 4 KB I2C1

Data 0x3FF6_8000 0x3FF6_8FFF 4 KB SDMMC

Data 0x3FF6_9000 0x3FF6_AFFF 8 KB EMAC

Data 0x3FF6_C000 0x3FF6_CFFF 4 KB PWM1

Data 0x3FF6_D000 0x3FF6_DFFF 4 KB I2S1

Data 0x3FF6_E000 0x3FF6_EFFF 4 KB UART2

Data 0x3FF6_F000 0x3FF6_FFFF 4 KB PWM2

Data 0x3FF7_0000 0x3FF7_0FFF 4 KB PWM3

Data 0x3FF7_5000 0x3FF7_5FFF 4 KB RNG

Low Address High Address

0x3FF5_C000 0x3FF5_DFFF 8 KB Reserved

0x3FF6_1000 0x3FF6_3FFF 12 KB Reserved

0x3FF6_B000 0x3FF6_BFFF 4 KB Reserved

0x3FF7_1000 0x3FF7_4FFF 16 KB Reserved

0x3FF7_6000 0x3FF7_FFFF 40 KB Reserved

Boundary Address

Size Target Comment

1.3.4.1 Asymmetric PID Controller Peripheral

There are two PID Controllers in the system. They serve the PRO_CPU and the APP_CPU, respectively. The

PRO_CPU and the APP_CPU can only access their own PID Controller and not their counterpart’s PID

Controller. Each CPU uses the same memory range 0x3FF1_F000 ~ 3FF1_FFFF to access its own PID

Controller.

1.3.4.2 Non-Contiguous Peripheral Memory Ranges

The SDIO Slave peripheral consists of three parts and the two CPUs use non-contiguous addresses to access

these. The three parts are accessed at the address ranges 0x3FF4_B000 ~ 3FF4_BFFF, 0x3FF5_5000 ~

3FF5_5FFF and 0x3FF5_8000 ~ 3FF5_8FFF of each CPU’s data bus. Similar to other peripherals, access to this

peripheral is identical for both CPUs.

Espressif Systems 15 ESP32 Technical Reference Manual V1.0

Page 17

1.3 Functional Description 1 SYSTEM AND MEMORY

1.3.4.3 Memory Speed

The ROM as well as the SRAM are both clocked from CPU_CLK and can be accessed by the CPU in a single

cycle. The RTC FAST memory is clocked from the APB_CLOCK and the RTC SLOW memory from the

FAST_CLOCK, so access to these memories may be slower. DMA uses the APB_CLK to access memory.

Internally, the SRAM is organized in 32K-sized banks. Each CPU and DMA channel can access the SRAM at full

speed and simultaneously, provided they access address different memory banks.

Espressif Systems 16 ESP32 Technical Reference Manual V1.0

Page 18

2 INTERRUPT MATRIX

2. Interrupt Matrix

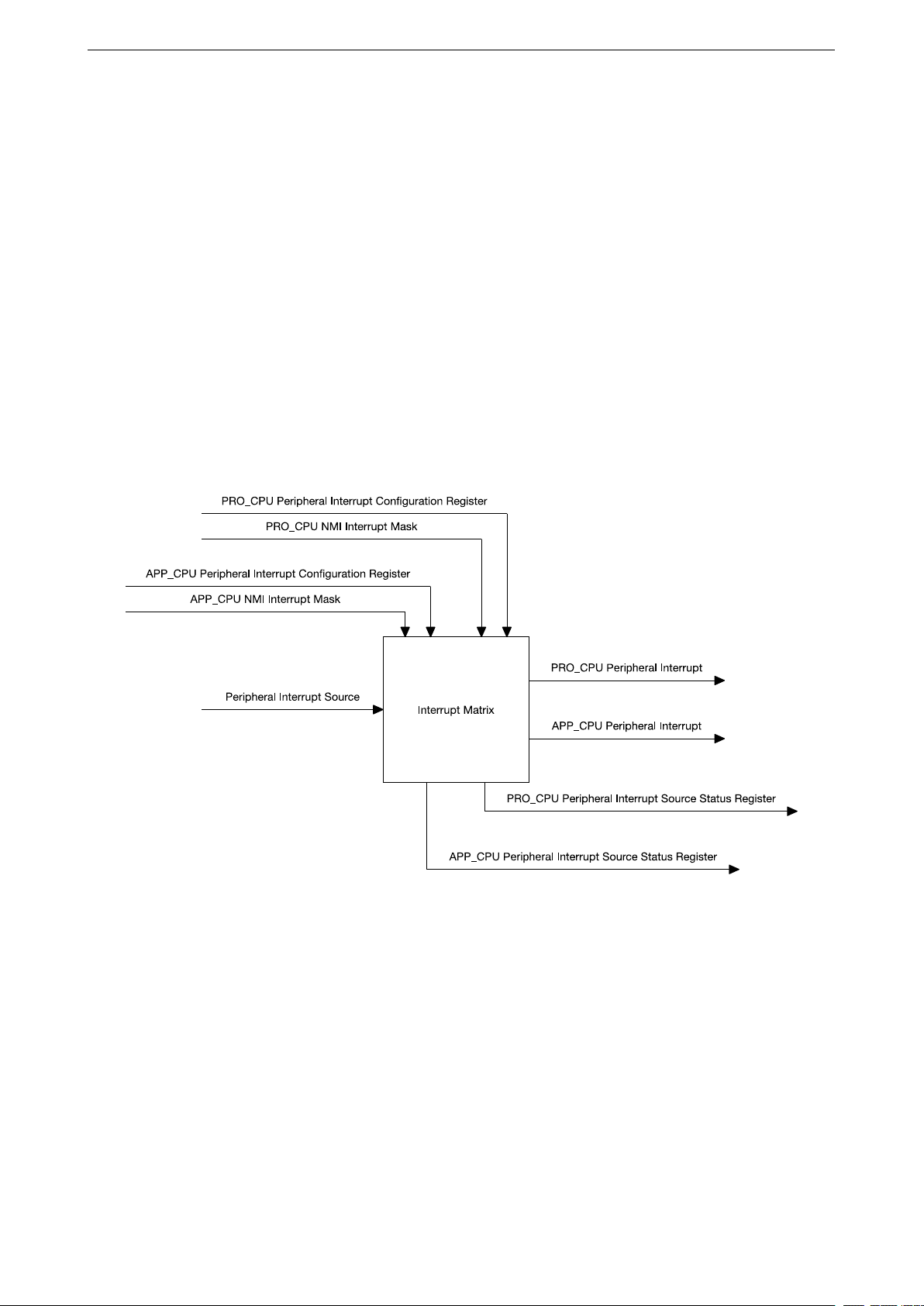

2.1 Introduction

The Interrupt Matrix embedded in the ESP32 independently allocates peripheral interrupt sources to the two

CPUs’ peripheral interrupts. This configuration is highly flexible in order to meet many different needs.

2.2 Features

• Accepts 71 peripheral interrupt sources as input.

• Generates 26 peripheral interrupt sources per CPU as output (52 total).

• CPU NMI Interrupt Mask.

• Queries current interrupt status of peripheral interrupt sources.

The structure of the Interrupt Matrix is shown in Figure 3.

Figure 3: Interrupt Matrix Structure

2.3 Functional Description

2.3.1 Peripheral Interrupt Source

ESP32 has 71 peripheral interrupt sources in total. All peripheral interrupt sources are listed in table 6. 67 of 71

ESP32 peripheral interrupt sources can be allocated to either CPU.

The four remaining peripheral interrupt sources are CPU-specific, two per CPU. GPIO_INTERRUPT_PRO and

GPIO_INTERRUPT_PRO_NMI can only be allocated to PRO_CPU. GPIO_INTERRUPT_APP and

GPIO_INTERRUPT_APP_NMI can only be allocated to APP_CPU. As a result, PRO_CPU and APP_CPU each

have 69 peripheral interrupt sources.

Espressif Systems 17 ESP32 Technical Reference Manual V1.0

Page 19

Espressif Systems 18 ESP32 Technical Reference Manual V1.0

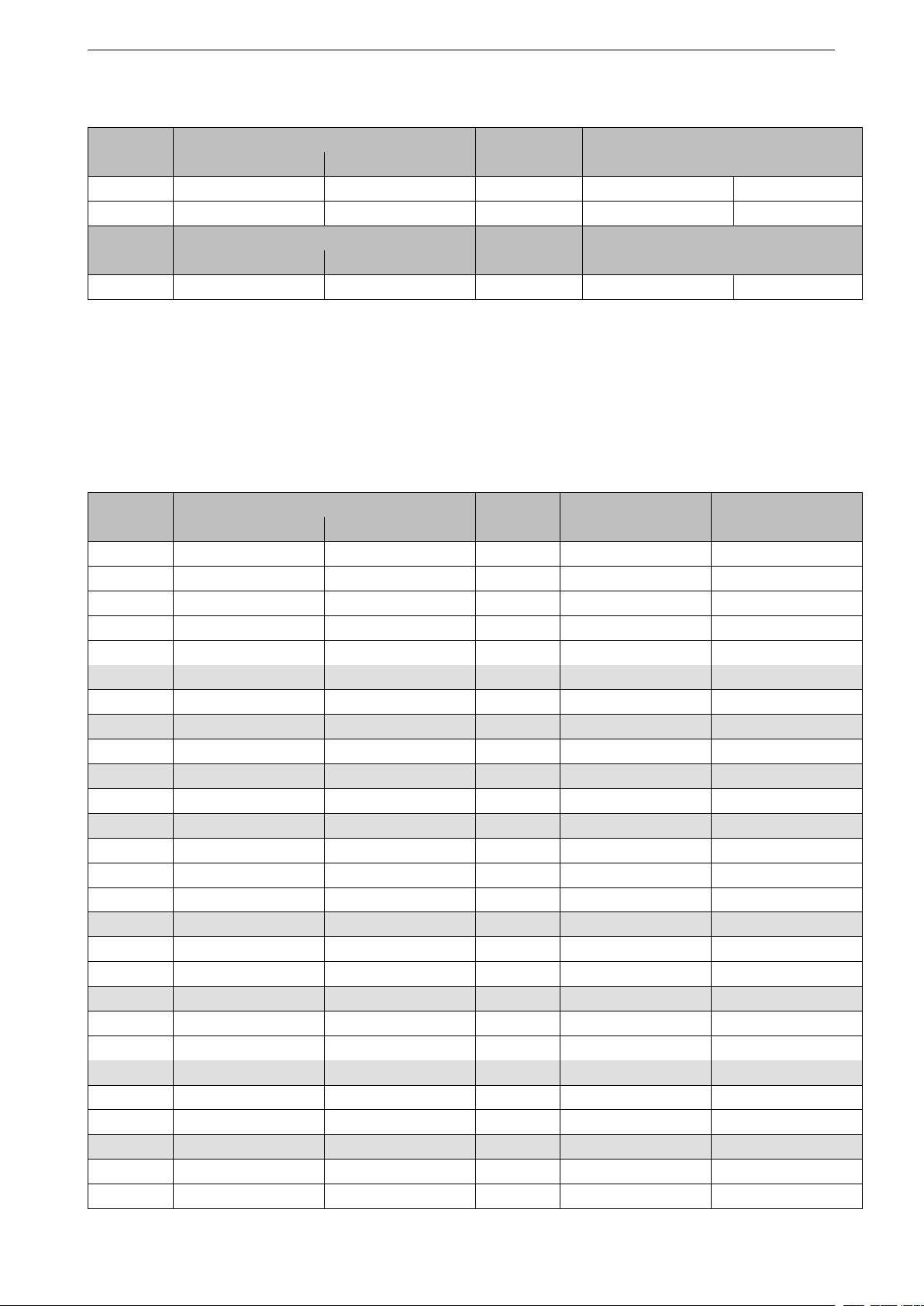

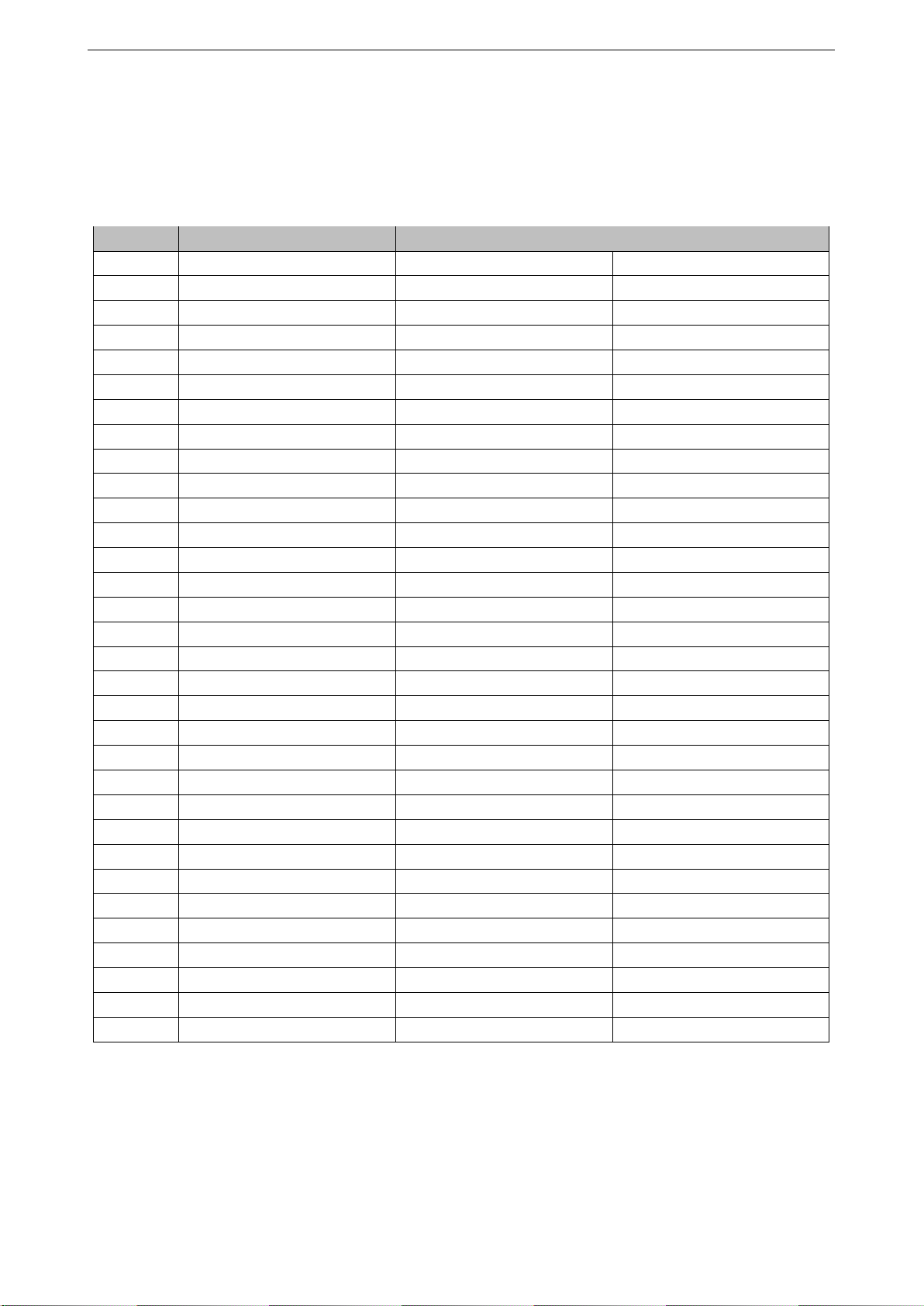

Table 6: PRO_CPU, APP_CPU interrupt configuration

2.3 Functional Description 2 INTERRUPT MATRIX

PRO_CPU APP_CPU

Peripheral Interrupt

Configuration Register

PRO_MAC_INTR_MAP_REG 0

PRO_MAC_NMI_MAP_REG 1 1 MAC_NMI 1 1 APP_MAC_NMI_MAP_REG

PRO_BB_INT_MAP_REG 2 2 BB_INT 2 2 APP_BB_INT_MAP_REG

PRO_BT_MAC_INT_MAP_REG 3 3 BT_MAC_INT 3 3 APP_BT_MAC_INT_MAP_REG

PRO_BT_BB_INT_MAP_REG 4 4 BT_BB_INT 4 4 APP_BT_BB_INT_MAP_REG

PRO_BT_BB_NMI_MAP_REG 5 5 BT_BB_NMI 5 5 APP_BT_BB_NMI_MAP_REG

PRO_RWBT_IRQ_MAP_REG 6 6 RWBT_IRQ 6 6 APP_RWBT_IRQ_MAP_REG

PRO_BT_BB_NMI_MAP_REG 5 5 BT_BB_NMI 5 5 APP_BT_BB_NMI_MAP_REG

PRO_RWBT_IRQ_MAP_REG 6 6 RWBT_IRQ 6 6 APP_RWBT_IRQ_MAP_REG

PRO_RWBLE_IRQ_MAP_REG 7 7 RWBLE_IRQ 7 7 APP_RWBLE_IRQ_MAP_REG

PRO_RWBT_NMI_MAP_REG 8 8 RWBT_NMI 8 8 APP_RWBT_NMI_MAP_REG

PRO_RWBLE_NMI_MAP_REG 9 9 RWBLE_NMI 9 9 APP_RWBLE_NMI_MAP_REG

PRO_SLC0_INTR_MAP_REG 10 10 SLC0_INTR 10 10 APP_SLC0_INTR_MAP_REG

PRO_SLC1_INTR_MAP_REG 11 11 SLC1_INTR 11 11 APP_SLC1_INTR_MAP_REG

PRO_UHCI0_INTR_MAP_REG 12 12 UHCI0_INTR 12 12 APP_UHCI0_INTR_MAP_REG

PRO_UHCI1_INTR_MAP_REG 13 13 UHCI1_INTR 13 13 APP_UHCI1_INTR_MAP_REG

PRO_TG_T0_LEVEL_INT_MAP_REG 14 14 TG_T0_LEVEL_INT 14 14 APP_TG_T0_LEVEL_INT_MAP_REG

PRO_TG_T1_LEVEL_INT_MAP_REG 15 15 TG_T1_LEVEL_INT 15 15 APP_TG_T1_LEVEL_INT_MAP_REG

PRO_TG_WDT_LEVEL_INT_MAP_REG 16 16 TG_WDT_LEVEL_INT 16 16 APP_TG_WDT_LEVEL_INT_MAP_REG

PRO_TG_LACT_LEVEL_INT_MAP_REG 17 17 TG_LACT_LEVEL_INT 17 17 APP_TG_LACT_LEVEL_INT_MAP_REG

PRO_TG1_T0_LEVEL_INT_MAP_REG 18 18 TG1_T0_LEVEL_INT 18 18 APP_TG1_T0_LEVEL_INT_MAP_REG

PRO_TG1_T1_LEVEL_INT_MAP_REG 19 19 TG1_T1_LEVEL_INT 19 19 APP_TG1_T1_LEVEL_INT_MAP_REG

PRO_TG1_WDT_LEVEL_INT_MAP_REG 20 20 TG1_WDT_LEVEL_INT 20 20 APP_TG1_WDT_LEVEL_INT_MAP_REG

PRO_TG1_LACT_LEVEL_INT_MAP_REG 21 21 TG1_LACT_LEVEL_INT 21 21 APP_TG1_LACT_LEVEL_INT_MAP_REG

PRO_GPIO_INTERRUPT_PRO_MAP_REG

PRO_GPIO_INTERRUPT_PRO_NMI_MAP_REG

PRO_CPU_INTR_FROM_CPU_0_MAP_REG 24 24 CPU_INTR_FROM_CPU_0 24 24 APP_CPU_INTR_FROM_CPU_0_MAP_REG

PRO_CPU_INTR_FROM_CPU_1_MAP_REG 25 25 CPU_INTR_FROM_CPU_1 25 25 APP_CPU_INTR_FROM_CPU_1_MAP_REG

PRO_CPU_INTR_FROM_CPU_2_MAP_REG 26 26 CPU_INTR_FROM_CPU_2 26 26 APP_CPU_INTR_FROM_CPU_2_MAP_REG

PRO_CPU_INTR_FROM_CPU_3_MAP_REG 27 27 CPU_INTR_FROM_CPU_3 27 27 APP_CPU_INTR_FROM_CPU_3_MAP_REG

PRO_SPI_INTR_0_MAP_REG 28 28 SPI_INTR_0 28 28 APP_SPI_INTR_0_MAP_REG

PRO_SPI_INTR_1_MAP_REG 29 29 SPI_INTR_1 29 29 APP_SPI_INTR_1_MAP_REG

PRO_SPI_INTR_2_MAP_REG 30 30 SPI_INTR_2 30 30 APP_SPI_INTR_2_MAP_REG

PRO_SPI_INTR_3_MAP_REG 31 31 SPI_INTR_3 31 31 APP_SPI_INTR_3_MAP_REG

PRO_I2S0_INT_MAP_REG 0

PRO_I2S1_INT_MAP_REG 1 33 I2S1_INT 33 1 APP_I2S1_INT_MAP_REG

PRO_UART_INTR_MAP_REG 2 34 UART_INTR 34 2 APP_UAR T_INTR_MAP_REG

PRO_UART1_INTR_MAP_REG 3 35 UART1_INTR 35 3 APP_UART1_INTR_MAP_REG

PRO_UART2_INTR_MAP_REG 4 36 UART2_INTR 36 4 APP_UART2_INTR_MAP_REG

PRO_SDIO_HOST_INTERRUPT_MAP_REG 5 37 SDIO_HOST_INTERRUPT 37 5 APP_SDIO_HOST_INTERRUPT_MAP_REG

PRO_EMAC_INT_MAP_REG 6 38 EMAC_INT 38 6 APP_EMAC_INT_MAP_REG

PRO_PWM0_INTR_MAP_REG 7 39 PWM0_INTR 39 7 APP_PWM0_INTR_MAP_REG

PRO_PWM1_INTR_MAP_REG 8 40 PWM1_INTR 40 8 APP_PWM1_INTR_MAP_REG

PRO_PWM2_INTR_MAP_REG 9 41 PWM2_INTR 41 9 APP_PWM2_INTR_MAP_REG

PRO_PWM3_INTR_MAP_REG 10 42 PWM3_INTR 42 10 APP_PWM3_INTR_MAP_REG

PRO_LEDC_INT_MAP_REG 11 43 LEDC_INT 43 11 APP_LEDC_INT_MAP_REG

PRO_EFUSE_INT_MAP_REG 12 44 EFUSE_INT 44 12 APP_EFUSE_INT_MAP_REG

PRO_CAN_INT_MAP_REG 13 45 CAN_INT 45 13 APP_CAN_INT_MAP_REG

PRO_RTC_CORE_INTR_MAP_REG 14 46 RTC_CORE_INTR 46 14 APP_R TC_CORE_INTR_MAP_REG

PRO_RMT_INTR_MAP_REG 15 47 RMT_INTR 47 15 APP_RMT_INTR_MAP_REG

PRO_PCNT_INTR_MAP_REG 16 48 PCNT_INTR 48 16 APP_PCNT_INTR_MAP_REG

PRO_I2C_EXT0_INTR_MAP_REG 17 49 I2C_EXT0_INTR 49 17 APP_I2C_EXT0_INTR_MAP_REG

PRO_I2C_EXT1_INTR_MAP_REG 18 50 I2C_EXT1_INTR 50 18 APP_I2C_EXT1_INTR_MAP_REG

PRO_RSA_INTR_MAP_REG 19 51 RSA_INTR 51 19 APP_RSA_INTR_MAP_REG

PRO_SPI1_DMA_INT_MAP_REG 20 52 SPI1_DMA_INT 52 20 APP_SPI1_DMA_INT_MAP_REG

Status Register Status Register

Bit Name

PRO_INTR_STATUS_REG_0

22 22

23 23

PRO_INTR_STATUS_REG_1

No. Name No.

0 MAC_INTR 0

GPIO_INTERRUPT_PRO GPIO_INTERRUPT_APP

GPIO_INTERRUPT_PRO_NMI GPIO_INTERRUPT_APP_NMI

32 I2S0_INT 32

Peripheral Interrupt Source

Name Bit

APP_INTR_STATUS_REG_0

22 22

23 23

APP_INTR_STATUS_REG_1

Peripheral Interrupt

Configuration Register

0 APP_MAC_INTR_MAP_REG

APP_GPIO_INTERRUPT_APP_MAP_REG

APP_GPIO_INTERRUPT_APP_NMI_MAP_REG

0 APP_I2S0_INT_MAP_REG

Page 20

Espressif Systems 19 ESP32 Technical Reference Manual V1.0

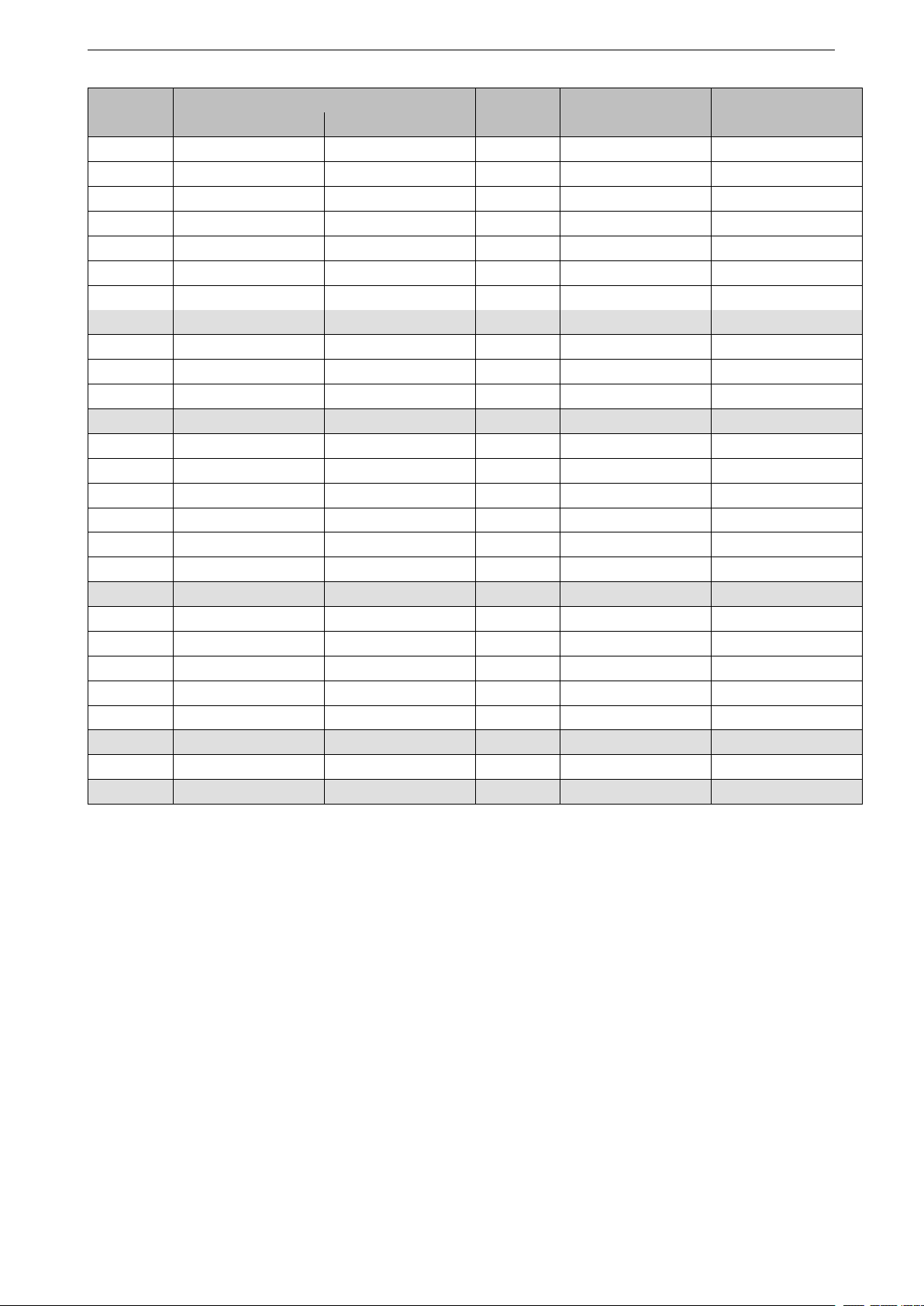

PRO_CPU APP_CPU

Peripheral Interrupt

Configuration Register

PRO_SPI2_DMA_INT_MAP_REG 21

PRO_SPI3_DMA_INT_MAP_REG 22 54 SPI3_DMA_INT 54 22 APP_SPI3_DMA_INT_MAP_REG

PRO_WDG_INT_MAP_REG 23 55 WDG_INT 55 23 APP_WDG_INT_MAP_REG

PRO_TIMER_INT1_MAP_REG 24 56 TIMER_INT1 56 24 APP_TIMER_INT1_MAP_REG

PRO_TIMER_INT2_MAP_REG 25 57 TIMER_INT2 57 25 APP_TIMER_INT2_MAP_REG

PRO_TG_T0_EDGE_INT_MAP_REG 26 58 TG_T0_EDGE_INT 58 26 APP_TG_T0_EDGE_INT_MAP_REG

PRO_TG_T1_EDGE_INT_MAP_REG 27 59 TG_T1_EDGE_INT 59 27 APP_TG_T1_EDGE_INT_MAP_REG

PRO_TG_WDT_EDGE_INT_MAP_REG 28 60 TG_WDT_EDGE_INT 60 28 APP_TG_WDT_EDGE_INT_MAP_REG

PRO_TG_LACT_EDGE_INT_MAP_REG 29 61 TG_LACT_EDGE_INT 61 29 APP_TG_LACT_EDGE_INT_MAP_REG

PRO_TG1_T0_EDGE_INT_MAP_REG 30 62 TG1_T0_EDGE_INT 62 30 APP_TG1_T0_EDGE_INT_MAP_REG

PRO_TG1_T1_EDGE_INT_MAP_REG 31 63 TG1_T1_EDGE_INT 63 31 APP_TG1_T1_EDGE_INT_MAP_REG

PRO_TG1_WDT_EDGE_INT_MAP_REG 0

PRO_TG1_LACT_EDGE_INT_MAP_REG 1 65 TG1_LACT_EDGE_INT 65 1 APP_TG1_LACT_EDGE_INT_MAP_REG

PRO_MMU_IA_INT_MAP_REG 2 66 MMU_IA_INT 66 2 APP_MMU_IA_INT_MAP_REG

PRO_MPU_IA_INT_MAP_REG 3 67 MPU_IA_INT 67 3 APP_MPU_IA_INT_MAP_REG

PRO_CACHE_IA_INT_MAP_REG 4 68 CACHE_IA_INT 68 4 APP_CACHE_IA_INT_MAP_REG

Status Register Status Register

Bit Name

PRO_INTR_STATUS_REG_1

PRO_INTR_STATUS_REG_2

No. Name No.

53 SPI2_DMA_INT 53

64 TG1_WDT_EDGE_INT 64

Peripheral Interrupt Source

Name Bit

APP_INTR_STATUS_REG_1

APP_INTR_STATUS_REG_2

Peripheral Interrupt

Configuration Register

21 APP_SPI2_DMA_INT_MAP_REG

0 APP_TG1_WDT_EDGE_INT_MAP_REG

2.3 Functional Description 2 INTERRUPT MATRIX

Page 21

2.3 Functional Description 2 INTERRUPT MATRIX

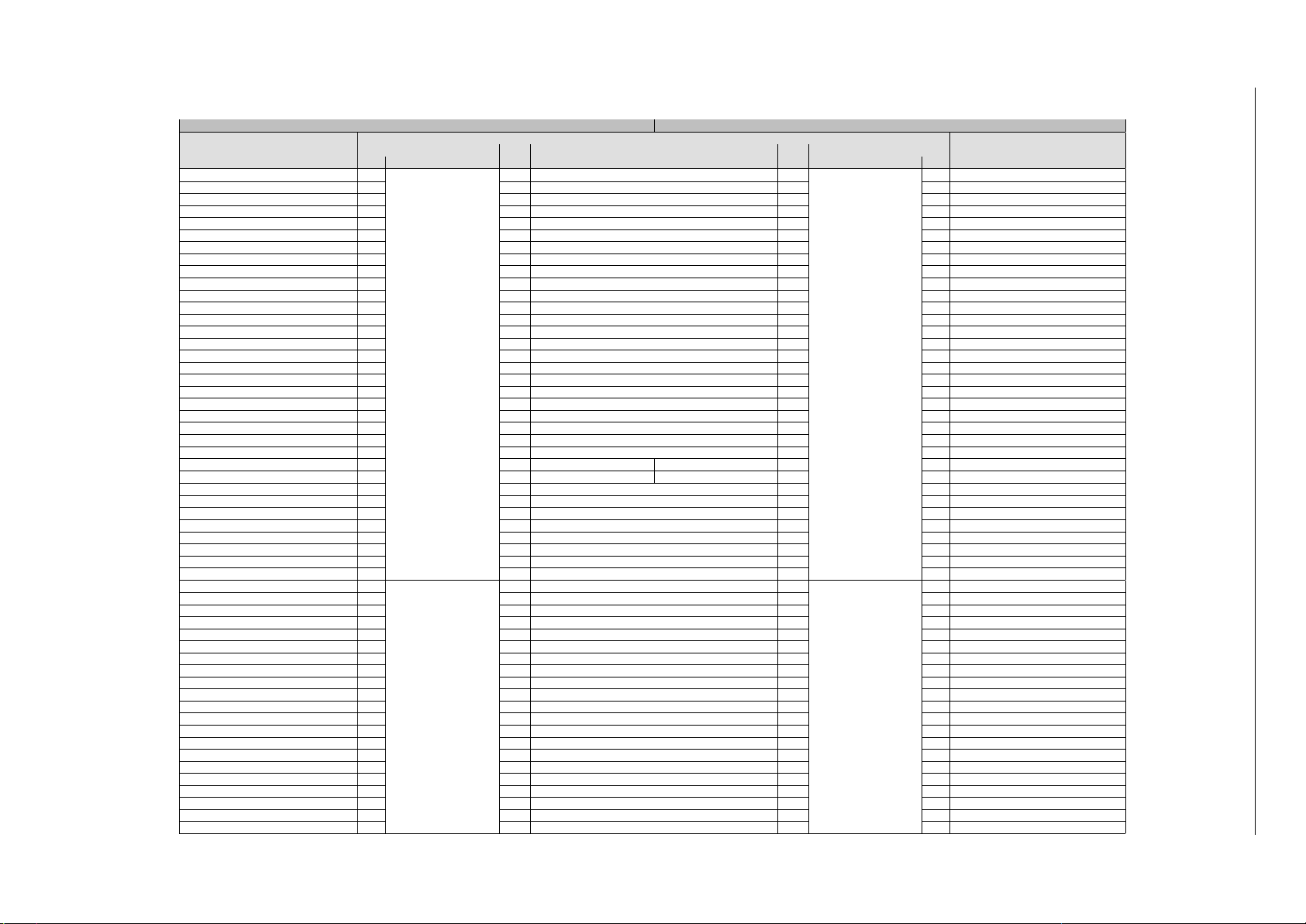

2.3.2 CPU Interrupt

Both of the two CPUs (PRO and APP) have 32 interrupts each, of which 26 are peripheral interrupts. All

interrupts in a CPU are listed in Table 7.

Table 7: CPU Interrupts

No. Category Type Priority Level

0 Peripheral Level-Triggered 1

1 Peripheral Level-Triggered 1

2 Peripheral Level-Triggered 1

3 Peripheral Level-Triggered 1

4 Peripheral Level-Triggered 1

5 Peripheral Level-Triggered 1

6 Internal Timer.0 1

7 Internal Software 1

8 Peripheral Level-Triggered 1

9 Peripheral Level-Triggered 1

10 Peripheral Edge-Triggered 1

11 Internal Profiling 3

12 Peripheral Level-Triggered 1

13 Peripheral Level-Triggered 1

14 Peripheral NMI NMI

15 Internal Timer.1 3

16 Internal Timer.2 5

17 Peripheral Level-Triggered 1

18 Peripheral Level-Triggered 1

19 Peripheral Level-Triggered 2

20 Peripheral Level-Triggered 2

21 Peripheral Level-Triggered 2

22 Peripheral Edge-Triggered 3

23 Peripheral Level-Triggered 3

24 Peripheral Level-Triggered 4

25 Peripheral Level-Triggered 4

26 Peripheral Level-Triggered 5

27 Peripheral Level-Triggered 3

28 Peripheral Edge-Triggered 4

29 Internal Software 3

30 Peripheral Edge-Triggered 4

31 Peripheral Level-Triggered 5

2.3.3 Allocate Peripheral Interrupt Sources to Peripheral Interrupt on CPU

In this section:

• Source_X stands for any particular peripheral interrupt source.

• PRO_X_MAP_REG (or APP_X_MAP_REG) stands for any particular peripheral interrupt configuration

Espressif Systems 20 ESP32 Technical Reference Manual V1.0

Page 22

2.3 Functional Description 2 INTERRUPT MATRIX

register of the PRO_CPU (or APP_CPU). The peripheral interrupt configuration register corresponds to the

peripheral interrupt source Source_X. Referring to Table 6, the registers listed under “PRO_CPU

(APP_CPU) - Peripheral Interrupt Configuration Register” correspond to the peripheral interrupt sources

listed in “Peripheral Interrupt Source - Name”.

• Interrupt_P stands for CPU peripheral interrupt, numbered as Num_P. Num_P can take the ranges 0 ~ 5, 8

~ 10, 12 ~ 14, 17 ~ 28, 30 ~ 31.

• Interrupt_I stands for CPU internal interrupt numbered as Num_I. Num_I can take values 6, 7, 11, 15, 16,

29.

Using this terminology, the possible operations of the Interrupt Matrix controller can be described as

follows:

• Allocate peripheral interrupt source Source_X to CPU (PRO_CPU or APP_CPU)

Set PRO_X_MAP_REG�or APP_X_MAP_REG�to Num_P. Num_P can be any CPU peripheral interrupt

number. CPU interrupts can be shared between multiple peripherals (see below).

• Disable peripheral interrupt source Source_X for CPU (PRO_CPU or APP_CPU)

Set PRO_X_MAP_REG�or APP_X _MAP_REG�for peripheral interrupt source to any Num_I. The specific

choice of internal interrupt number does not change behaviour, as none of the interrupt numbered as

Num_I are connected to either CPU.

• Allocate multiple peripheral sources Source_Xn ORed to PRO_CPU (APP_CPU) peripheral interrupt

Set multiple PRO_Xn_MAP_REG (APP_Xn_MAP_REG) to the same Num_P. Any of these peripheral

interrupts will trigger CPU Interrupt_P.

2.3.4 CPU NMI Interrupt Mask

The Interrupt Matrix temporarily masks all peripheral interrupt sources allocated to PRO_CPU’s ( or APP_CPU’s )

NMI interrupt if it receives the signal PRO_CPU NMI Interrupt Mask ( or APP_CPU NMI Interrupt Mask ) from the

peripheral PID Controller respectively.

2.3.5 Query Current Interrupt Status of Peripheral Interrupt Source

The current interrupt status of a peripheral interrupt source can be read via the bit value in

PRO_INTR_STATUS_REG_n (APP_INTR_STATUS_REG_n) as shown in the mapping in Table 6.

Espressif Systems 21 ESP32 Technical Reference Manual V1.0

Page 23

3 RESET AND CLOCK

3. Reset and Clock

3.1 System Reset

3.1.1 Introduction

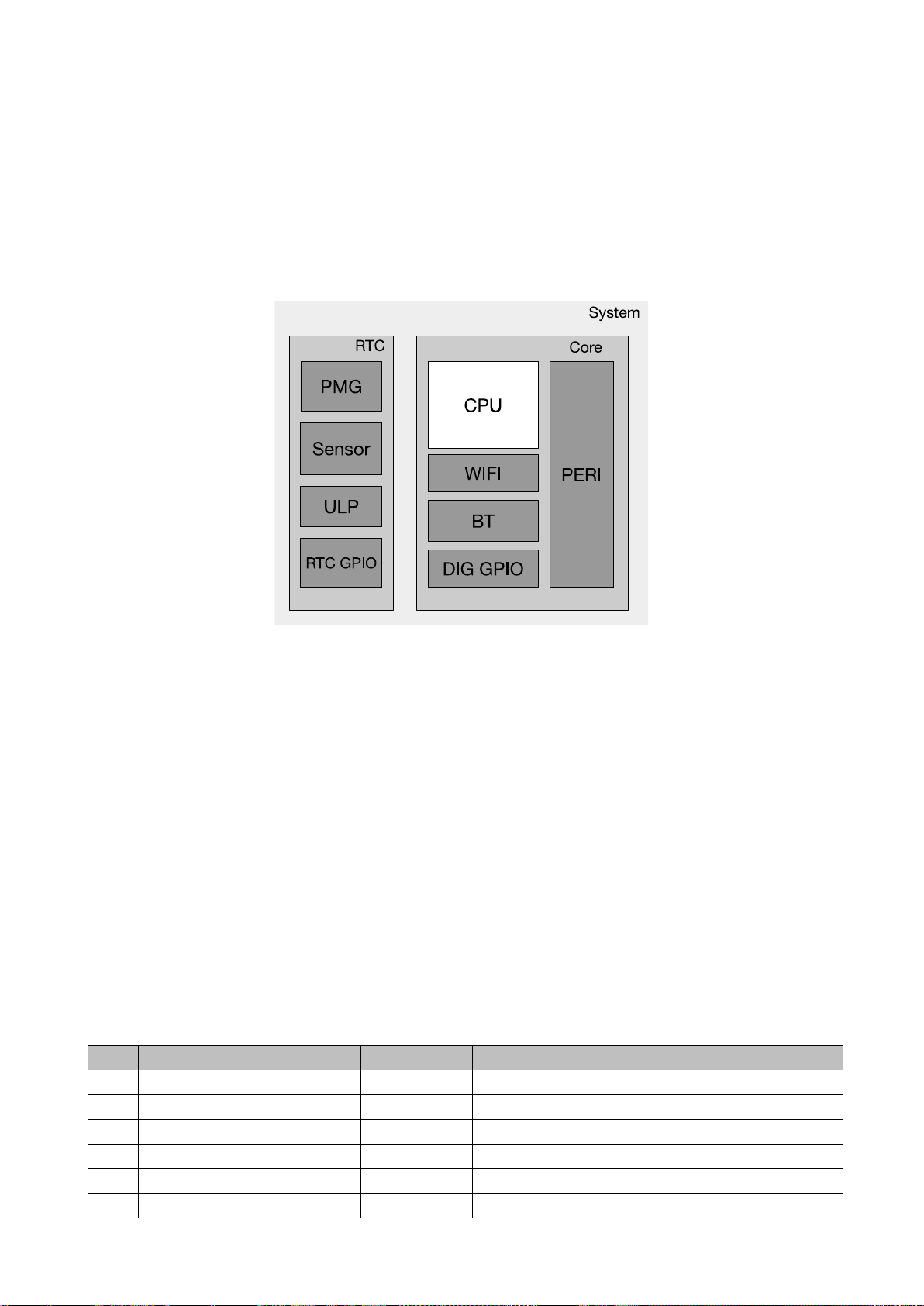

The ESP32 has three reset levels: CPU reset, Core reset, and System reset. None of these reset levels clear the

RAM. Figure 4 shows the subsystems included in each reset level.

Figure 4: System Reset

• CPU reset: Only resets the registers of one or both the CPU cores.

• Core reset: Resets all the digital registers, including CPU cores, external GPIO and digital GPIO. The RTC is

not reset.

• System reset: Resets all the registers on the chip, including those of the RTC.

3.1.2 Reset Source

While most of the time the APP_CPU and PRO_CPU will be reset simultaneously, some reset sources are able to

reset only one of the two cores. The reset reason for each core can be looked up individually: the PRO_CPU

reset reason will be stored in RTC_CNTL_RESET_CAUSE_PROCPU, the reset reason for the APP_CPU in

APP_CNTL_RESET_CAUSE_PROCPU. Table 8 shows the possible reset reason values that can be read from

these registers.

Table 8: PRO_CPU and APP_CPU reset reason values

PRO APP Source Reset Type Note

0x01 0x01 Chip Power On Reset System Reset -

0x10 0x10 RWDT System Reset System Reset Refer to WDT Chapter.

0x0F 0x0F Brown Out Reset System Reset Refer to Power Management Chapter.

0x03 0x03 Software System Reset Core Reset Configure RTC_CNTL_SW_SYS_RST register.

0x05 0x05 Deep Sleep Rest Core Reset Refer to Power Management Chapter.

0x07 0x07 MWDT0 Global Reset Core Reset Refer to WDT Chapter.

Espressif Systems 22 ESP32 Technical Reference Manual V1.0

Page 24

3.2 System Clock 3 RESET AND CLOCK

PRO APP APP Source Reset Type Note

0x08 0x08 MWDT1 Global Reset Core Reset Refer to WDT Chapter.

0x09 0x09 RWDT Core Reset Core Reset Refer to WDT Chapter.

0x0B - MWDT0 CPU Reset CPU Reset Refer to WDT Chapter.

0x0C - Software CPU Reset CPU Reset Configure RTC_CNTL_SW_APPCPU_RST register.

- 0x0B MWDT1 CPU Reset CPU Reset Refer to WDT Chapter.

- 0x0C Software CPU Reset CPU Reset Configure RTC_CNTL_SW_APPCPU_RST register.

0x0D 0x0D RWDT CPU Reset CPU Reset Refer to WDT Chapter.

Indicates that the PRO CPU has indepen-

- 0xE PRO CPU Reset CPU Reset

dently reset the APP CPU by configuring the

DPORT_APPCPU_RESETTING register.

3.2 System Clock

3.2.1 Introduction

The ESP32 integrates multiple clock sources for the CPU cores, the peripherals and the RTC. These clocks can

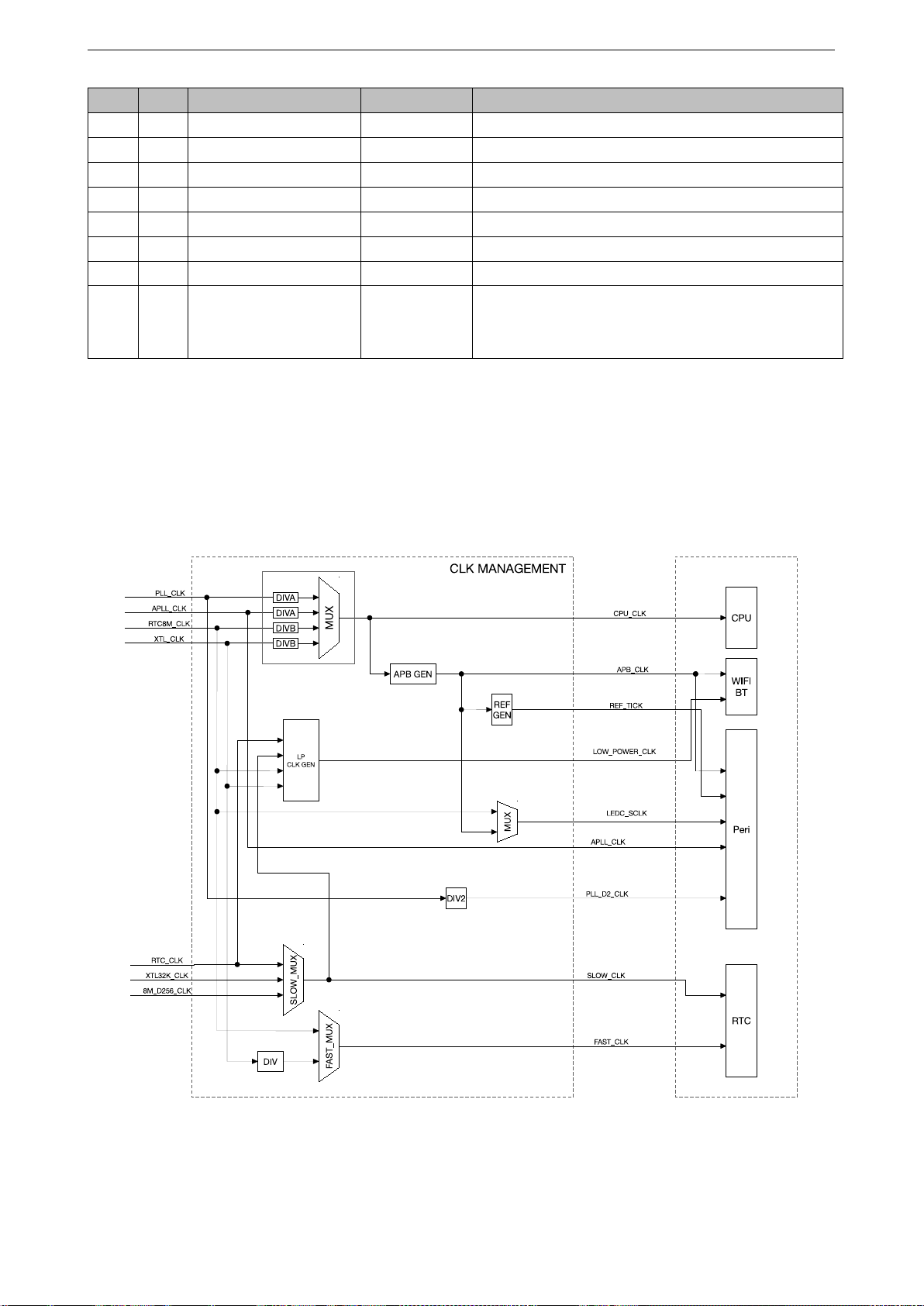

be configured to meet different requirements. Figure 5 shows the system clock structure.

Figure 5: System Clock

Espressif Systems 23 ESP32 Technical Reference Manual V1.0

Page 25

3.2 System Clock 3 RESET AND CLOCK

3.2.2 Clock Source

The ESP32 can use an external crystal oscillator, an internal PLL or an oscillating circuit as a clock source.

Specifically, the clock sources available are:

• High Speed Clocks

– PLL_CLK is an internal PLL clock with a frequency of 320 MHz.

– XTL_CLK is a clock signal generated using an external crystal with a frequency range of 2 ~ 40 MHz.

• Low Power Clocks

– XTL32K_CLK is a clock generated using an external crystal with a frequency of 32 KHz.

– RTC8M_CLK is an internal clock with a default frequency of 8 MHz. This frequency is adjustable.

– RTC8M_D256_CLK is divided from RTC8M_CLK 256. Its frequency is (RTC8M_CLK / 256). With the

default RTC8M_CLK frequency of 8 MHz, this clock runs at 31.250 KHz.

– RTC_CLK is an internal low power clock with a default frequency of 150 KHz. This frequency is

adjustable.

• Audio Clock

– APLL_CLK is an internal Audio PLL clock with a frequency range of 16 ~ 128 MHz.

3.2.3 CPU Clock

As Figure 5 shows, CPU_CLK is the master clock for both CPU cores. CPU_CLK clock can be as high as 160

MHz when the CPU is in high performance mode. Alternatively, the CPU can run at lower frequencies to reduce

power consumption.

The CPU_CLK clock source is determined by the RTC_CNTL_SOC_CLK_SEL register. PLL_CLK, APLL_CLK,

RTC8M_CLK and XTL_CLK can be set as the CPU_CLK source; see Table 9 and 10.

Table 9: CPU_CLK Source

RTC_CNTL_SOC_CLK_SEL Value Clock Source

0 XTL_CLK

1 PLL_CLK

2 RTC8M_CLK

3 APLL_CLK

Espressif Systems 24 ESP32 Technical Reference Manual V1.0

Page 26

3.2 System Clock 3 RESET AND CLOCK

Table 10: CPU_CLK Derivation

Clock Source SEL* CPU Clock

0 / XTL_CLK -

1 / PLL_CLK 0

1 / PLL_CLK 1

2 / RTC8M_CLK -

3 / APLL_CLK 0 CPU_CLK = APLL_CLK / 4

3 / APLL_CLK 1 CPU_CLK = APLL_CLK / 2

*SEL: DPORT_CPUPERIOD _SEL value

CPU_CLK = XTL_CLK / (APB_CTRL_PRE_DIV_CNT+1)

APB_CTRL_PRE_DIV_CNT range is 0 ~ 1023. Default is 0.

CPU_CLK = PLL_CLK / 4

CPU_CLK frequency is 80 MHz

CPU_CLK = PLL_CLK / 2

CPU_CLK frequency is 160 MHz

CPU_CLK = RTC8M_CLK / (APB_CTRL_PRE_DIV_CNT+1)

APB_CTRL_PRE_DIV_CNT range is 0 ~ 1023. Default is 0.

3.2.4 Peripheral Clock

Peripheral clocks include APB_CLK, REF_TICK, LEDC_SCLK, APLL_CLK and PLL_D2_CLK.

Table 11 shows which clocks can be used by which peripherals.

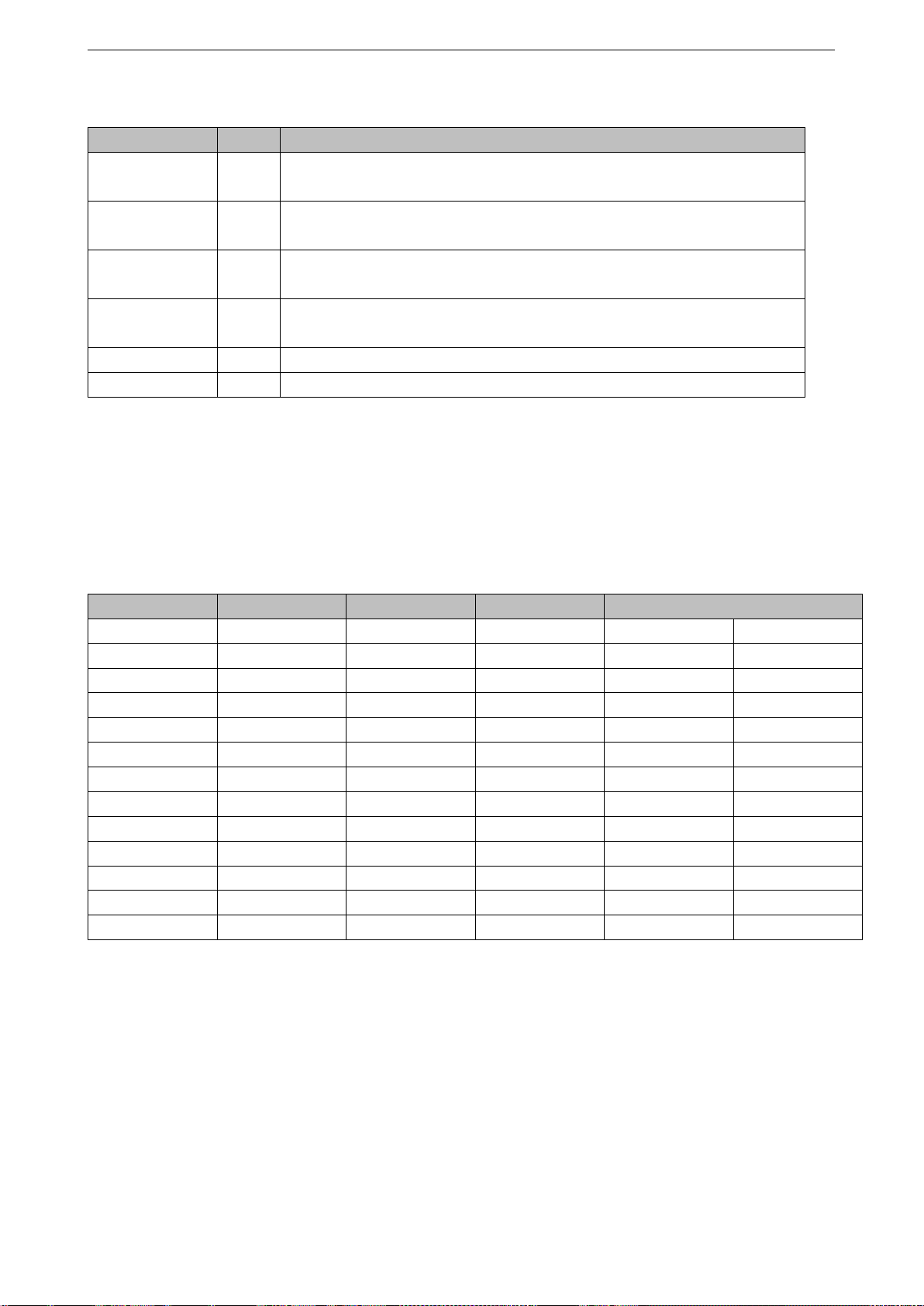

Table 11: Peripheral Clock Usage

Peripherals APB_CLK REF_TICK LEDC_SCLK APLL_CLK PLL_D2_CLK

EMAC Y N N Y N

TIMG Y N N N N

I2S Y N N Y Y

UART Y Y N N N

RMT Y Y N N N

LED PWM Y Y Y N N

PWM Y N N N N

I2C Y N N N N

SPI Y N N N N

PCNT Y N N N N

Efuse Controller Y N N N N

SDIO Slave Y N N N N

SDMMC Y N N N N

3.2.4.1 APB_CLK Source

The APB_CLK is derived from CPU_CLK as detailed in Table 12. The division factor depends on the CPU_CLK

source.

Espressif Systems 25 ESP32 Technical Reference Manual V1.0

Page 27

3.2 System Clock 3 RESET AND CLOCK

Table 12: APB_CLK Derivation

CPU_CLK Source APB_CLK

PLL_CLK PLL_CLK / 4

APLL_CLK CPU_CLK / 2

XTAL_CLK CPU_CLK

RTC8M_CLK CPU_CLK

3.2.4.2 REF_TICK Source

REF_TICK is derived from APB_CLK via a divider. The divider value used depends on the APB_CLK source,

which in turn depends on the CPU_CLK source.

By configuring correct divider values for each APB_CLK source, the user can ensure that the REF_TICK

frequency does not change when CPU_CLK changes source causing the APB_CLK frequency to change.

Clock divider registers are shown in Table 13.

Table 13: REF_TICK Derivation

CPU_CLK & APB_CLK Source Clock Divider Register

PLL_CLK APB_CTRL_PLL_TICK_NUM

XTAL_CLK APB_CTRL_XTAL_TICK_NUM

APLL_CLK APB_CTRL_APLL_TICK_NUM

RTC8M_CLK APB_CTRL_CK8M_TICK_NUM

3.2.4.3 LEDC_SCLK Source

The LEDC_SCLK clock source is selected by the LEDC_APB_CLK_SEL register, as shown in Table 14.

Table 14: LEDC_SCLK Derivation

LEDC_APB_CLK_SEL Value LEDC_SCLK Source

1 RTC8M_CLK

0 APB_CLK

3.2.4.4 APLL_SCLK Source

The APLL_CLK is sourced from PLL_CLK, with its output frequency configured using the APLL configuration

registers.

3.2.4.5 PLL_D2_CLK Source

PLL_D2_CLK is half the PLL_CLK frequency.

Espressif Systems 26 ESP32 Technical Reference Manual V1.0

Page 28

3.2 System Clock 3 RESET AND CLOCK

3.2.4.6 Clock Source Considerations

Most peripherals will operate using the APB_CLK frequency as a reference. When this frequency changes, the

peripherals will need to update their clock configuration to operate at the same frequency after the change.

Peripherals accessing REF_TICK can continue operating normally when switching clock sources, without

changing clock source. Please refer to Table 11 for details.

The LED PWM module can use RTC8M_CLK as a clock source, meaning that it can be used when APB_CLK is

disabled. In other words, when the system is in low power consumption mode (refer to power manager module),

normal peripherals will be halted (APB_CLK is turned off), but the LED PWM can work normally via

RTC8M_CLK.

3.2.5 Wi-Fi BT Clock

Wi-Fi and BT can only operate if APB_CLK has PLL_CLK as its clock source. Suspending PLL_CLK requires

Wi-Fi and BT to both have entered low power consumption mode first.

For LOW_POWER_CLK, one of RTC_CLK, SLOW_CLK, RTC8M_CLK or XTL_CLK can be selected as the low

power consumption mode clock source for Wi-Fi and BT.

3.2.6 RTC Clock

The clock sources of SLOW_CLK and FAST_CLK are low frequency clocks. The RTC module can operate when

most other clocks are stopped.

SLOW_CLK is used to clock the Power Management module. It can be sourced from RTC_CLK, XTL32K_CLK

or RTC8M_D256_CLK

FAST_CLK is used to clock the On-chip Sensor module. It can be sourced from a divided XTL_CLK or from

RTC8M_CLK.

Espressif Systems 27 ESP32 Technical Reference Manual V1.0

Page 29

4 IO_MUX AND GPIO MATRIX

4. IO_MUX and GPIO Matrix

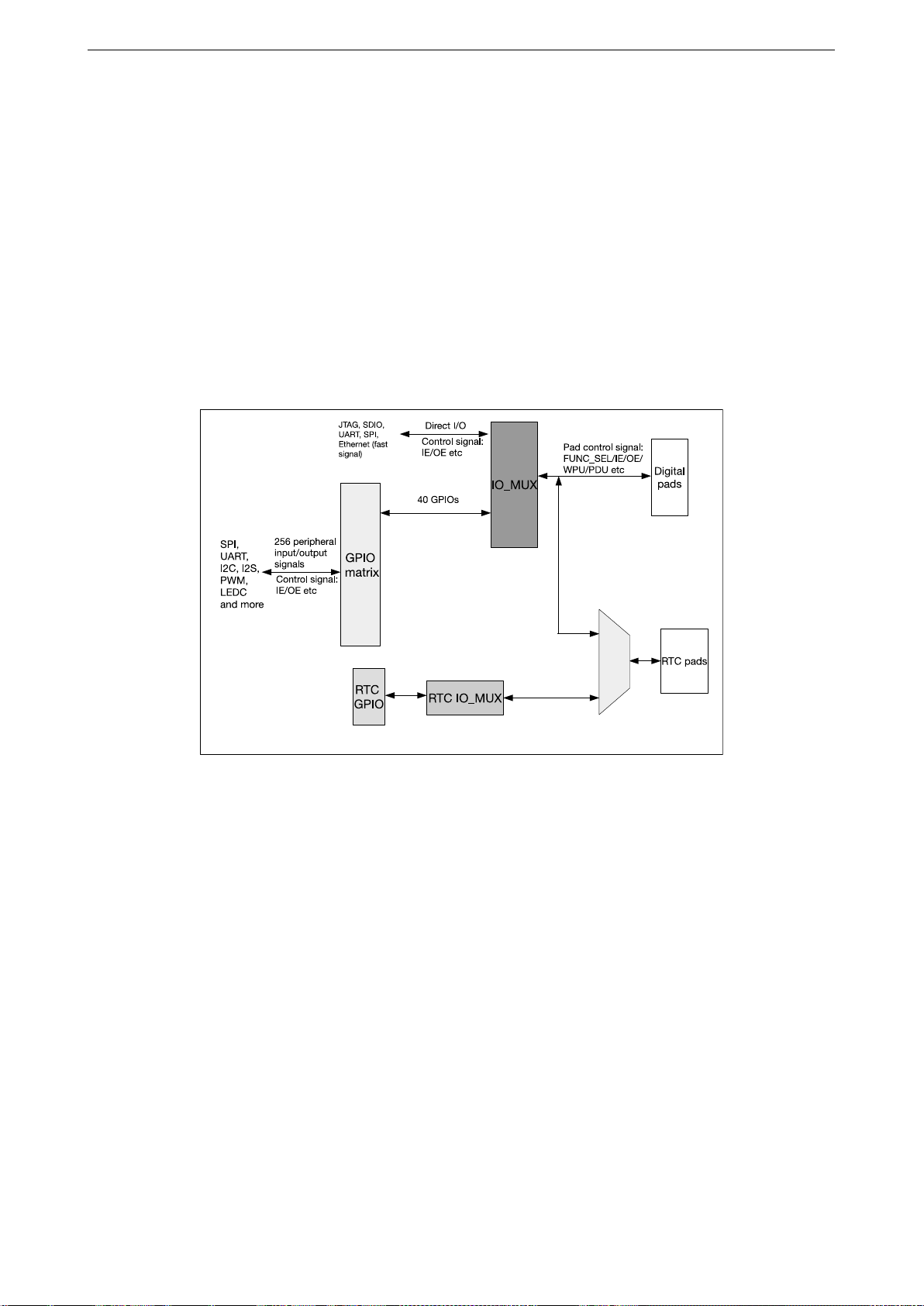

4.1 Introduction

The ESP32 chip features 40 physical GPIO pads. Some GPIO pads cannot be used or do not have the

corresponding pin on the chip package. Each pad can be used as a general purpose I/O or can be connected to

an internal peripheral signal. The IO_MUX, RTC IO_MUX and the GPIO matrix are responsible for routing signals

from the peripherals to GPIO pads. Together these systems provide highly configurable I/O.

This chapter describes the signal selection and connection between the digital pads (FUNC_SEL, IE, OE, WPU,

WDU, etc), 256 peripheral input/output signals (control signals: SIG_IN_SEL, SIG_OUT_SEL, IE, OE, etc), fast

peripheral input/output signals (control signals: SIG_IN_SEL, SIG_OUT_SEL, IE, OE, etc), and RTC

IO_MUX.

Figure 6: IO_MUX, RTC IO_MUX and GPIO Matrix Overview

1. The IO_MUX contains one register per GPIO pad. Each pad can be configured for ”GPIO” function

(connected to the GPIO Matrix) or configured for a direct function (bypassing the GPIO Matrix. Some high

speed digital functions (Ethernet, SDIO, SPI, JTAG, UART) can bypass the GPIO Matrix for better high

frequency digital performance. In this case, the IO_MUX is used to connect these pads directly to the

peripheral.)

Refer to Section 4.10 for a list of IO_MUX functions for each I/O pad.

2. The GPIO Matrix is a full switching matrix between the peripheral input/output signals and the pads.

• For input to the chip: Each of the 256 internal peripheral inputs can select any GPIO pad as the input

source.

• For output from the chip: The output signal of each of the 40 GPIO pads can be from one of the 256

peripheral output signals.

Refer to Section 4.9 for a list of GPIO Matrix peripheral signals.

3. RTC IO_MUX is used to connect GPIO pads to their low power and analog functions. Only a subset of

GPIO pads have these optional ”RTC” functions.

Espressif Systems 28 ESP32 Technical Reference Manual V1.0

Page 30

4.2 Peripheral Input via GPIO Matrix 4 IO_MUX AND GPIO MATRIX

GPIO_FUNCy_IN_SEL

GPIO0_in

GPIO1_in

GPIO2_in

GPIO3_in

GPIO39_in

0 (FUNC)

1 (FUNC)

2 (GPIO)

3

39

Peripheral Signal Y

I/O Pad X

In GPIO matrix

In IO MUX

GPIO X in

GPIOx_MCU_SEL

2

1

3

X

GPIOX_in

0

Constant 0 input

Constant 1 input

(0x30) 48

(0x38) 56

0

1 (GPIO)

GPIO_SIGxx_IN_SEL

GPIOx_FUN_IE = 1

Refer to Section 4.11 for a list of RTC IO_MUX functions.

4.2 Peripheral Input via GPIO Matrix

4.2.1 Summary

To receive a peripheral input signal via the GPIO Matrix, the GPIO Matrix is configured to source the peripheral

signal’s input index (0-255) from one of the 40 GPIOs (0-39).

The input signal is read from the GPIO pad through the IO_MUX. The IO_MUX must be configured to set the

chosen pad to ”GPIO” function. This causes the GPIO pad input signal to be routed into the GPIO Matrix which

in turn routes it to the selected peripheral input.

4.2.2 Functional Description

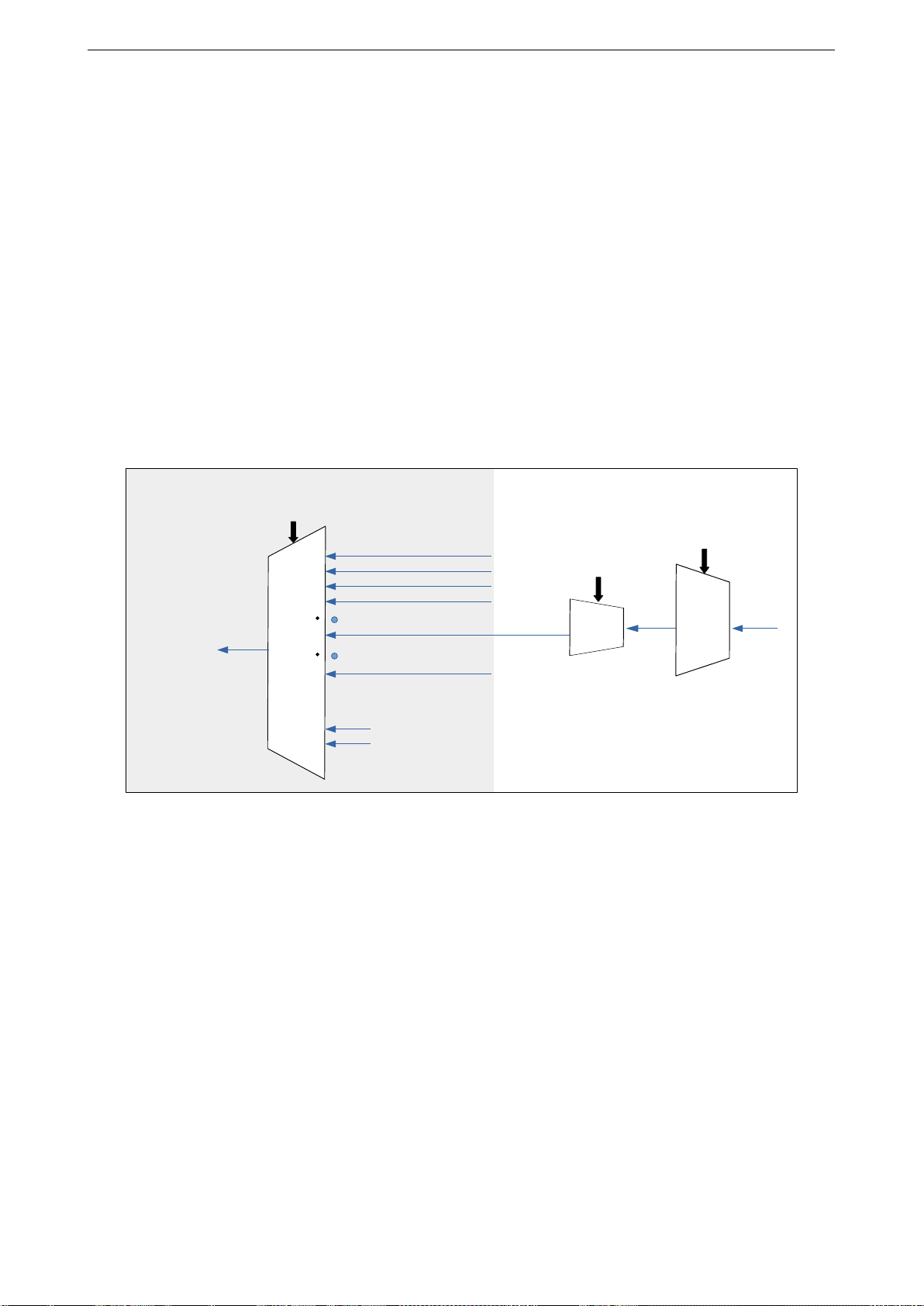

Figure 7 shows the logic for input selection via GPIO Matrix.

To read GPIO pad X into peripheral signal Y, follow these steps:

Espressif Systems 29 ESP32 Technical Reference Manual V1.0

Figure 7: Peripheral Input via IO_MUX, GPIO Matrix

1. Configure the GPIO_FUNCy_IN_SEL_CFG register for peripheral signal Y in the GPIO Matrix:

• Set the GPIO_FUNCx_IN_SEL field to the number of the GPIO pad X to read from.

2. Configure the GPIO_FUNCx_OUT_SEL_CFG and GPIO_ENABLE_DATA[x] for GPIO pad X in the GPIO

Matrix:

• For input ony signals, the pad output can be disabled by setting the GPIO_FUNCx_OEN_SEL bits to

one and GPIO_ENABLE_DATA[x] to zero. Otherwise, there is no need to disable output.

3. Configure the IO_MUX register for GPIO pad X:

• Set the function field to GPIO.

• Enable the input by setting the xx_FUN_IE bit.

• Set xx_FUN_WPU and xx_FUN_WPD fields as desired to enable internal pull-up/pull-down resistors.

Page 31

4.3 Peripheral Output via GPIO Matrix 4 IO_MUX AND GPIO MATRIX

Notes:

• One input pad can be connected to multiple input_signals.

• The input signal can be inverted with GPIO_FUNCx_IN_INV_SEL.

• It is possible to have a peripheral read a constant low or constant high input value without connecting this

input to a pad. This can be done by selecting a special GPIO_FUNCy_IN_SEL input instead of a GPIO

number:

– When GPIO_FUNCx_IN_SEL is 0x30, input_signal_x is always 0

– When GPIO_FUNCx_IN_SEL is 0x38, input_signal_x is always 1.

4.2.3 Simple GPIO Input

The GPIO_IN_DATA register holds the input values of each GPIO pad.

The input value of any GPIO pin can be read at any time without configuring the GPIO Matrix for a particular

peripheral signal. However, it is necessary to configure the xx_FUN_IE register for pad X, as shown in Section

4.2.2.

4.3 Peripheral Output via GPIO Matrix

4.3.1 Summary

To output a signal from a peripheral via the GPIO Matrix, the GPIO Matrix is configured to route the peripheral

output signal (0-255) to one of the first 34 GPIOs (0-33). (Note that GPIO pads 34-39 cannot be used as

outputs.)

The output signal is routed from the peripheral into the GPIO Matrix. It is then routed into the IO_MUX, which is

configured to set the chosen pad to ”GPIO” function. This causes the output GPIO signal to be connected to the

pad.

4.3.2 Functional Description

One of 256 input signals can be selected to go through the GPIO matrix into the IO_MUX and then to a pad.

Figure 8 illustrates the configuration.

To output peripheral signal Y to particular GPIO pad X, follow these steps:

1. Configure the GPIO_FUNCx_OUT_SEL_CFG register and GPIO_ENABLE_DATA[x] of GPIO X in the GPIO

Matrix:

• Set GPIO_FUNCx_OUT_SEL to the index of desired peripheral output signal Y.

• Set the GPIO_FUNCx_OEN_SEL bits and GPIO_ENABLE_DATA[x] to enable output mode by force,

OR, clear GPIO_FUNCx_OEN_SEL to zero so that the output enable signal will be decided by the

internal logic function.

2. Optionally, to enable open drain mode set the GPIO_PINx_PAD_DRIVER bit in the GPIO_PINx register.

3. Configure the I/O mux register for GPIO pad X:

• Set the function field to GPIO.

Espressif Systems 30 ESP32 Technical Reference Manual V1.0

Page 32

4.4 Direct I/O via IO_MUX 4 IO_MUX AND GPIO MATRIX

GPIO_FUNCx_OUT_SEL

signal0_out

signal1_out

signal2_out

signal3_out

signal255_out

GPIO_OUT_DATA bit x

0

1

2

3

255

256

(0x100)

GPIOx_out

In GPIO matrix

In IO MUX

0 (FUNC)

1 (FUNC)

2 (GPIO)

I/O Pad X

GPIO X out

GPIOx_MCU_SEL

GPIOx_FUN_OE = 1

• Set the xx_FUN_DRV field to the desired value for output strength. The higher the value is, the higher

the output strength is. Pull up/down the pad by configuring xx_FUNC_WPU and xx_FUNC_WPD

registers in open drain mode.

Notes:

• The output signal from a single peripheral can be sent to multiple pads simultaneously.

• Only the first 34 GPIOs (0-33) can be used as outputs.

• The output signal can be inverted by setting the GPIO_FUNCx_OUT_INV_SEL bit.

Figure 8: Output via GPIO Matrix

4.3.3 Simple GPIO Output

The GPIO Matrix can also be used for simple GPIO output - setting a bit in the GPIO_OUT_DATA register will

write to the corresponding GPIO pad.

To configure a pad as simple GPIO output, the GPIO Matrix GPIO_FUNCx_OUT_SEL register is configured with a

special peripheral index value (0x100).

4.4 Direct I/O via IO_MUX

4.4.1 Summary

Some high speed digital functions (Ethernet, SDIO, SPI, JTAG, UART) can bypass the GPIO Matrix for better high

frequency digital performance. In this case, the IO_MUX is used to connect these pads directly to the

peripheral.

Selecting this option is less flexible than using the GPIO Matrix, as the IO_MUX register for each GPIO pad can

only select from a limited number of functions. However, better high frequency digital performance will be

maintained.

Espressif Systems 31 ESP32 Technical Reference Manual V1.0

Page 33

4.6 Light-sleep Mode Pin Functions 4 IO_MUX AND GPIO MATRIX

4.4.2 Functional Description

Two registers must be configured in order to bypass the GPIO Matrix for peripheral I/O:

1. IO_MUX for the GPIO pad must be set to the desired pad function (Section 4.10 has a list of pad functions).

2. For inputs, the SIG_IN_SEL register must be set to route the input directly to the peripheral.

4.5 RTC IO_MUX for Low Power and Analog I/O

4.5.1 Summary

18 pins have low power (RTC domain) capabilities and analog functions which are handled by the RTC

subsystem of ESP32. The IO_MUX and GPIO Matrix are not used for these functions, instead the RTC_MUX is

used to redirect the I/O to the RTC subsystem.

When configured as RTC GPIOs, the output pads can still retain the output level value when the chip is in

Deep-sleep mode, and the input pads can wake up the chip from Deep-sleep.

Section 4.11 has a list of RTC_MUX pins and their functions.

4.5.2 Functional Description

Each pad with analog and RTC functions is controlled by the RTC_IO_TOUCH_PADx_TO_GPIO bit in the

RTC_GPIO_PINx register. By default this bit is set to 1, routing all I/O via the IO_MUX subsystem as described in

earlier subsections.

If the RTC_IO_TOUCH_PADx_TO_GPIO bit is cleared, then I/O to and from that pad is routed to the RTC

subsystem instead. In this mode, the RTC_GPIO_PINx register is used for digital I/O and the analog features of

the pad are also available. See Section 4.11 for a list of RTC pin functions.

See 4.11 for a table mapping GPIO pads to their RTC equivalent pins and analog functions. Note that the

RTC_IO_PINx registers use the RTC GPIO pin numbering, not the GPIO pad numbering.

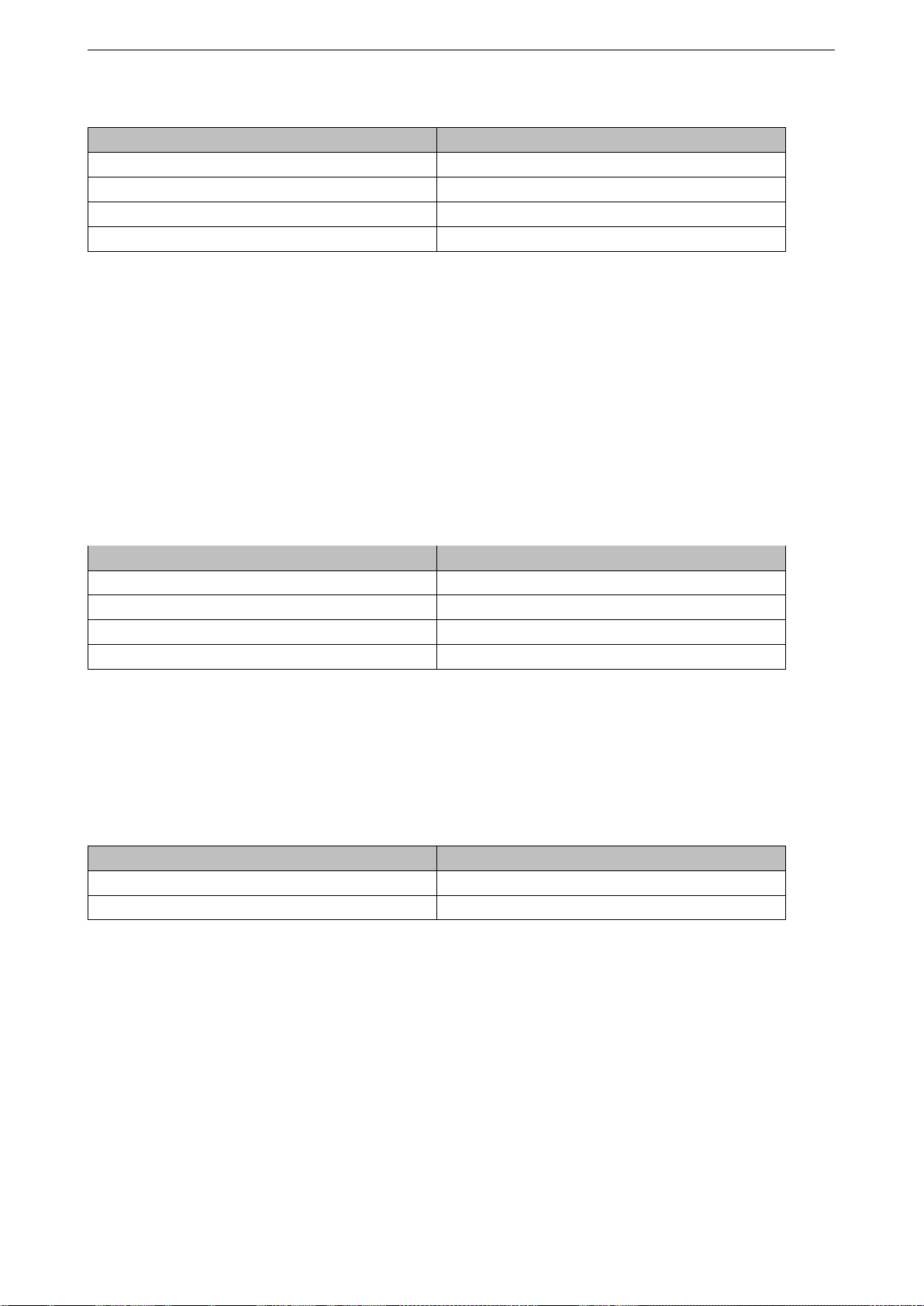

4.6 Light-sleep Mode Pin Functions

Pins can have different functions when the ESP32 is in Light-sleep mode. If the GPIOxx_SLP_SEL bit in the

IO_MUX register for a GPIO pad is set to 1, a different set of registers is used to control the pad when the ESP32

is in Light-sleep mode:

Table 15: IO_MUX Light-sleep Pin Function Registers

IO_MUX Function

Output Drive Strength GPIOxx_FUNC_DRV GPIOxx_MCU_DRV

Pullup Resistor GPIOxx_FUNC_WPU GPIOxx_MCU_WPU

Pulldown Resistor GPIOxx_FUNC_WPD GPIOxx_MCU_WPD

Output Enable (From GPIO Matrix _OEN field) GPIOxx_MCU_OE

If GPIOxx_SLP_SEL is set to 0, the pin functions remain the same in both normal execution and Light-sleep

modes.

Espressif Systems 32 ESP32 Technical Reference Manual V1.0

Normal Execution Light-sleep Mode

OR GPIOxx_SLP_SEL = 0 AND GPIOxx_SLP_SEL = 1

Page 34

4.7 Pad Hold Feature 4 IO_MUX AND GPIO MATRIX

4.7 Pad Hold Feature

Each IO pad (including the RTC pads) has an individual hold function controlled by a RTC register. When the pad

is set to hold, the state is latched at that moment and will not change no matter how the internal signals change

or how the IO_MUX configuration or GPIO configuration is modified. Users can use the hold function for the pads

to retain the pad state through a core reset and system reset triggered by watchdog time-out or Deep-sleep

events.

4.8 I/O Pad Power Supply

IO pad power supply is shown in Figure 9.

Figure 9: ESP32 I/O Pad Power Sources

• Pads marked blue are RTC pads that have their individual analog function and can also act as normal

digital IO pads. For details, please refer to Section 4.11.

• Pads marked pink and green only have digital functions.

• Pads marked green can be powered externally or internally via VDD_SDIO (see below).

4.8.1 VDD_SDIO Power Domain

VDD_SDIO can source or sink current, allowing this power domain to be powered externally or internally. To

power VDD_SDIO externally, apply the same power supply of VDD3P3_RTC to the VDD_SDIO pad.

Without an external power supply, the internal regulator will supply VDD_SDIO. The VDD_SDIO voltage can be

configured to be either 1.8V or 3.3V (the same as that at VRTC), depending on the state of the MTDI pad at reset

- a high level configures 1.8V and a low level configures 3.3V. Setting the efuse bit decides the default voltage of

the VDD_SDIO. In addition, software can change the voltage of the VDD_SDIO by configuring register bits.

Espressif Systems 33 ESP32 Technical Reference Manual V1.0

Page 35

4.9 Peripheral Signal List 4 IO_MUX AND GPIO MATRIX

4.9 Peripheral Signal List

Table 16 contains a list of Peripheral Input/Output signals used by the GPIO Matrix:

Table 16: GPIO Matrix Peripheral Signals

Signal Input Signal Output Signal Direct I/O in IO_MUX

0 SPICLK_in SPICLK_out YES

1 SPIQ_in SPIQ_out YES

2 SPID_in SPID_out YES

3 SPIHD_in SPIHD_out YES

4 SPIWP_in SPIWP_out YES

5 SPICS0_in SPICS0_out YES

6 SPICS1_in SPICS1_out

7 SPICS2_in SPICS2_out

8 HSPICLK_in HSPICLK_out YES

9 HSPIQ_in HSPIQ_out YES

10 HSPID_in HSPID_out YES

11 HSPICS0_in HSPICS0_out YES

12 HSPIHD_in HSPIHD_out YES

13 HSPIWP_in HSPIWP_out YES

14 U0RXD_in U0TXD_out YES

15 U0CTS_in U0RTS_out YES

16 U0DSR_in U0DTR_out

17 U1RXD_in U1TXD_out YES

18 U1CTS_in U1RTS_out YES

23 I2S0O_BCK_in I2S0O_BCK_out

24 I2S1O_BCK_in I2S1O_BCK_out

25 I2S0O_WS_in I2S0O_WS_out

26 I2S1O_WS_in I2S1O_WS_out

27 I2S0I_BCK_in I2S0I_BCK_out

28 I2S0I_WS_in I2S0I_WS_out

29 I2CEXT0_SCL_in I2CEXT0_SCL_out

30 I2CEXT0_SDA_in I2CEXT0_SDA_out

31 pwm0_sync0_in sdio_tohost_int_out

32 pwm0_sync1_in pwm0_out0a

33 pwm0_sync2_in pwm0_out0b

34 pwm0_f0_in pwm0_out1a

35 pwm0_f1_in pwm0_out1b

36 pwm0_f2_in pwm0_out2a

37 pwm0_out2b

39 pcnt_sig_ch0_in0

40 pcnt_sig_ch1_in0

41 pcnt_ctrl_ch0_in0

42 pcnt_ctrl_ch1_in0

43 pcnt_sig_ch0_in1

44 pcnt_sig_ch1_in1

Espressif Systems 34 ESP32 Technical Reference Manual V1.0

Page 36

4.9 Peripheral Signal List 4 IO_MUX AND GPIO MATRIX

Signal Input Signal Output Signal Direct I/O in IO_MUX

45 pcnt_ctrl_ch0_in1

46 pcnt_ctrl_ch1_in1

47 pcnt_sig_ch0_in2

48 pcnt_sig_ch1_in2

49 pcnt_ctrl_ch0_in2

50 pcnt_ctrl_ch1_in2

51 pcnt_sig_ch0_in3

52 pcnt_sig_ch1_in3

53 pcnt_ctrl_ch0_in3

54 pcnt_ctrl_ch1_in3

55 pcnt_sig_ch0_in4

56 pcnt_sig_ch1_in4

57 pcnt_ctrl_ch0_in4

58 pcnt_ctrl_ch1_in4

61 HSPICS1_in HSPICS1_out

62 HSPICS2_in HSPICS2_out

63 VSPICLK_in VSPICLK_out_mux YES

64 VSPIQ_in VSPIQ_out YES

65 VSPID_in VSPID_out YES

66 VSPIHD_in VSPIHD_out YES

67 VSPIWP_in VSPIWP_out YES

68 VSPICS0_in VSPICS0_out YES

69 VSPICS1_in VSPICS1_out

70 VSPICS2_in VSPICS2_out

71 pcnt_sig_ch0_in5 ledc_hs_sig_out0

72 pcnt_sig_ch1_in5 ledc_hs_sig_out1

73 pcnt_ctrl_ch0_in5 ledc_hs_sig_out2

74 pcnt_ctrl_ch1_in5 ledc_hs_sig_out3

75 pcnt_sig_ch0_in6 ledc_hs_sig_out4

76 pcnt_sig_ch1_in6 ledc_hs_sig_out5

77 pcnt_ctrl_ch0_in6 ledc_hs_sig_out6

78 pcnt_ctrl_ch1_in6 ledc_hs_sig_out7

79 pcnt_sig_ch0_in7 ledc_ls_sig_out0

80 pcnt_sig_ch1_in7 ledc_ls_sig_out1

81 pcnt_ctrl_ch0_in7 ledc_ls_sig_out2

82 pcnt_ctrl_ch1_in7 ledc_ls_sig_out3

83 rmt_sig_in0 ledc_ls_sig_out4

84 rmt_sig_in1 ledc_ls_sig_out5

85 rmt_sig_in2 ledc_ls_sig_out6

86 rmt_sig_in3 ledc_ls_sig_out7

87 rmt_sig_in4 rmt_sig_out0

88 rmt_sig_in5 rmt_sig_out1

89 rmt_sig_in6 rmt_sig_out2

90 rmt_sig_in7 rmt_sig_out3

Espressif Systems 35 ESP32 Technical Reference Manual V1.0

Page 37

4.9 Peripheral Signal List 4 IO_MUX AND GPIO MATRIX

Signal Input Signal Output Signal Direct I/O in IO_MUX

91 rmt_sig_out4

92 rmt_sig_out5

93 rmt_sig_out6

94 rmt_sig_out7

95 I2CEXT1_SCL_in I2CEXT1_SCL_out

96 I2CEXT1_SDA_in I2CEXT1_SDA_out

97 host_card_detect_n_1 host_ccmd_od_pullup_en_n

98 host_card_detect_n_2 host_rst_n_1

99 host_card_write_prt_1 host_rst_n_2

100 host_card_write_prt_2 gpio_sd0_out

101 host_card_int_n_1 gpio_sd1_out

102 host_card_int_n_2 gpio_sd2_out

103 pwm1_sync0_in gpio_sd3_out

104 pwm1_sync1_in gpio_sd4_out

105 pwm1_sync2_in gpio_sd5_out

106 pwm1_f0_in gpio_sd6_out

107 pwm1_f1_in gpio_sd7_out

108 pwm1_f2_in pwm1_out0a

109 pwm0_cap0_in pwm1_out0b

110 pwm0_cap1_in pwm1_out1a

111 pwm0_cap2_in pwm1_out1b

112 pwm1_cap0_in pwm1_out2a

113 pwm1_cap1_in pwm1_out2b

114 pwm1_cap2_in pwm2_out1h

115 pwm2_flta pwm2_out1l

116 pwm2_fltb pwm2_out2h

117 pwm2_cap1_in pwm2_out2l

118 pwm2_cap2_in pwm2_out3h

119 pwm2_cap3_in pwm2_out3l

120 pwm3_flta pwm2_out4h

121 pwm3_fltb pwm2_out4l

122 pwm3_cap1_in

123 pwm3_cap2_in

124 pwm3_cap3_in

140 I2S0I_DATA_in0 I2S0O_DATA_out0

141 I2S0I_DATA_in1 I2S0O_DATA_out1

142 I2S0I_DATA_in2 I2S0O_DATA_out2

143 I2S0I_DATA_in3 I2S0O_DATA_out3

144 I2S0I_DATA_in4 I2S0O_DATA_out4

145 I2S0I_DATA_in5 I2S0O_DATA_out5

146 I2S0I_DATA_in6 I2S0O_DATA_out6

147 I2S0I_DATA_in7 I2S0O_DATA_out7

148 I2S0I_DATA_in8 I2S0O_DATA_out8

149 I2S0I_DATA_in9 I2S0O_DATA_out9

Espressif Systems 36 ESP32 Technical Reference Manual V1.0

Page 38

4.9 Peripheral Signal List 4 IO_MUX AND GPIO MATRIX

Signal Input Signal Output Signal Direct I/O in IO_MUX

150 I2S0I_DATA_in10 I2S0O_DATA_out10

151 I2S0I_DATA_in11 I2S0O_DATA_out11

152 I2S0I_DATA_in12 I2S0O_DATA_out12

153 I2S0I_DATA_in13 I2S0O_DATA_out13

154 I2S0I_DATA_in14 I2S0O_DATA_out14

155 I2S0I_DATA_in15 I2S0O_DATA_out15

156 I2S0O_DATA_out16

157 I2S0O_DATA_out17

158 I2S0O_DATA_out18

159 I2S0O_DATA_out19

160 I2S0O_DATA_out20

161 I2S0O_DATA_out21

162 I2S0O_DATA_out22

163 I2S0O_DATA_out23

164 I2S1I_BCK_in I2S1I_BCK_out

165 I2S1I_WS_in I2S1I_WS_out

166 I2S1I_DATA_in0 I2S1O_DATA_out0

167 I2S1I_DATA_in1 I2S1O_DATA_out1

168 I2S1I_DATA_in2 I2S1O_DATA_out2

169 I2S1I_DATA_in3 I2S1O_DATA_out3

170 I2S1I_DATA_in4 I2S1O_DATA_out4

171 I2S1I_DATA_in5 I2S1O_DATA_out5

172 I2S1I_DATA_in6 I2S1O_DATA_out6

173 I2S1I_DATA_in7 I2S1O_DATA_out7

174 I2S1I_DATA_in8 I2S1O_DATA_out8

175 I2S1I_DATA_in9 I2S1O_DATA_out9

176 I2S1I_DATA_in10 I2S1O_DATA_out10

177 I2S1I_DATA_in11 I2S1O_DATA_out11

178 I2S1I_DATA_in12 I2S1O_DATA_out12

179 I2S1I_DATA_in13 I2S1O_DATA_out13

180 I2S1I_DATA_in14 I2S1O_DATA_out14

181 I2S1I_DATA_in15 I2S1O_DATA_out15

182 I2S1O_DATA_out16

183 I2S1O_DATA_out17

184 I2S1O_DATA_out18

185 I2S1O_DATA_out19

186 I2S1O_DATA_out20

187 I2S1O_DATA_out21

188 I2S1O_DATA_out22

189 I2S1O_DATA_out23

190 I2S0I_H_SYNC pwm3_out1h

191 I2S0I_V_SYNC pwm3_out1l

192 I2S0I_H_ENABLE pwm3_out2h

193 I2S1I_H_SYNC pwm3_out2l

Espressif Systems 37 ESP32 Technical Reference Manual V1.0

Page 39

4.10 IO_MUX Pad List 4 IO_MUX AND GPIO MATRIX

Signal Input Signal Output Signal Direct I/O in IO_MUX

194 I2S1I_V_SYNC pwm3_out3h

195 I2S1I_H_ENABLE pwm3_out3l

196 pwm3_out4h

197 pwm3_out4l

198 U2RXD_in U2TXD_out YES

199 U2CTS_in U2RTS_out YES

200 emac_mdc_i emac_mdc_o

201 emac_mdi_i emac_mdo_o

202 emac_crs_i emac_crs_o

203 emac_col_i emac_col_o

204 pcmfsync_in bt_audio0_irq

205 pcmclk_in bt_audio1_irq

206 pcmdin bt_audio2_irq

207 ble_audio0_irq

208 ble_audio1_irq

209 ble_audio2_irq

210 pcmfsync_out

211 pcmclk_out

212 pcmdout

213 ble_audio_sync0_p

214 ble_audio_sync1_p

215 ble_audio_sync2_p

224 sig_in_func224

225 sig_in_func225

226 sig_in_func226

227 sig_in_func227

228 sig_in_func228

Direct I/O in IO_MUX ”YES” means this signal is also available directly via IO_MUX. To apply GPIO Matrix for

these signals, their corresponding SIG_IN_SEL register must be cleared.

4.10 IO_MUX Pad List

Table 17 shows the IO_MUX functions for each I/O pad:

Table 17: IO_MUX Pad Summary

GPIO Pad Name Function 1 Function 2 Function 3 Function 4 Function 5 Function 6 Reset Notes

0 GPIO0 GPIO0 CLK_OUT1 GPIO0 - - EMAC_TX_CLK 3 R

1 U0TXD U0TXD CLK_OUT3 GPIO1 - - EMAC_RXD2 3 -

2 GPIO2 GPIO2 HSPIWP GPIO2 HS2_DATA0 SD_DATA0 - 2 R

3 U0RXD U0RXD CLK_OUT2 GPIO3 - - - 3 -

4 GPIO4 GPIO4 HSPIHD GPIO4 HS2_DATA1 SD_DATA1 EMAC_TX_ER 2 R

5 GPIO5 GPIO5 VSPICS0 GPIO5 HS1_DATA6 - EMAC_RX_CLK 3 -

6 SD_CLK SD_CLK SPICLK GPIO6 HS1_CLK U1CTS - 3 -

7 SD_DATA_0 SD_DATA0 SPIQ GPIO7 HS1_DATA0 U2RTS - 3 -

8 SD_DATA_1 SD_DATA1 SPID GPIO8 HS1_DATA1 U2CTS - 3 -

Espressif Systems 38 ESP32 Technical Reference Manual V1.0

Page 40

4.11 RTC_MUX Pin List 4 IO_MUX AND GPIO MATRIX

GPIO Pad Name Function 1 Function 2 Function 3 Function 4 Function 5 Function 6 Reset Notes

9 SD_DATA_2 SD_DATA2 SPIHD GPIO9 HS1_DATA2 U1RXD - 3 -

10 SD_DATA_3 SD_DATA3 SPIWP GPIO10 HS1_DATA3 U1TXD - 3 -

11 SD_CMD SD_CMD SPICS0 GPIO11 HS1_CMD U1RTS - 3 -

12 MTDI MTDI HSPIQ GPIO12 HS2_DATA2 SD_DATA2 EMAC_TXD3 2 R

13 MTCK MTCK HSPID GPIO13 HS2_DATA3 SD_DATA3 EMAC_RX_ER 1 R

14 MTMS MTMS HSPICLK GPIO14 HS2_CLK SD_CLK EMAC_TXD2 1 R

15 MTDO MTDO HSPICS0 GPIO15 HS2_CMD SD_CMD EMAC_RXD3 3 R

16 GPIO16 GPIO16 - GPIO16 HS1_DATA4 U2RXD EMAC_CLK_OUT 1 -

17 GPIO17 GPIO17 - GPIO17 HS1_DATA5 U2TXD EMAC_CLK_180 1 -

18 GPIO18 GPIO18 VSPICLK GPIO18 HS1_DATA7 - - 1 -

19 GPIO19 GPIO19 VSPIQ GPIO19 U0CTS - EMAC_TXD0 1 -

20 GPIO20 GPIO20 - GPIO20 - - - 1 -

21 GPIO21 GPIO21 VSPIHD GPIO21 - - EMAC_TX_EN 1 -

22 GPIO22 GPIO22 VSPIWP GPIO22 U0RTS - EMAC_TXD1 1 -

23 GPIO23 GPIO23 VSPID GPIO23 HS1_STROBE - - 1 -

25 GPIO25 GPIO25 - GPIO25 - - EMAC_RXD0 0 R

26 GPIO26 GPIO26 - GPIO26 - - EMAC_RXD1 0 R

27 GPIO27 GPIO27 - GPIO27 - - EMAC_RX_DV 1 R

32 32K_XP GPIO32 - GPIO32 - - - 0 R

33 32K_XN GPIO33 - GPIO33 - - - 0 R

34 VDET_1 GPIO34 - GPIO34 - - - 0 R, I

35 VDET_2 GPIO35 - GPIO35 - - - 0 R, I

36 SENSOR_VP GPIO36 - GPIO36 - - - 0 R, I

37 SENSOR_CAPP GPIO37 - GPIO37 - - - 0 R, I

38 SENSOR_CAPN GPIO38 - GPIO38 - - - 0 R, I

39 SENSOR_VN GPIO39 - GPIO39 - - - 0 R, I

Reset Configurations

”Reset” column shows each pad’s default configurations after reset:

• 0 - IE=0 (input disabled).

• 1 - IE=1 (input enabled).

• 2 - IE=1, WPD=1 (input enabled, pulldown resistor).

• 3 - IE=1, WPU=1 (input enabled, pullup resistor).

Notes

• R - Pad has RTC/analog functions via RTC_MUX.

• I - Pad can only be configured as input GPIO.

Refer to ESP32 Pin List datasheet for more details and a complete table of pin functions.

4.11 RTC_MUX Pin List

Table 18 shows the RTC pins and how they correspond to GPIO pads:

Table 18: RTC_MUX Pin Summary

RTC GPIO Num GPIO Num Pad Name

1 2 3

Analog Function

0 36 SENSOR_VP ADC_H ADC1_CH0 -

1 37 SENSOR_CAPP ADC_H ADC1_CH1 -

Espressif Systems 39 ESP32 Technical Reference Manual V1.0

Page 41

4.12 Register Summary 4 IO_MUX AND GPIO MATRIX

RTC GPIO Num GPIO Num Pad Name

2 38 SENSOR_CAPN ADC_H ADC1_CH2 -

3 39 SENSOR_VN ADC_H ADC1_CH3 -

4 34 VDET_1 - ADC1_CH6 -

5 35 VDET_2 - ADC1_CH7 -

6 25 GPIO25 DAC_1 ADC2_CH8 -

7 26 GPIO26 DAC_2 ADC2_CH9 -

8 33 32K_XN XTAL_32K_N ADC1_CH5 TOUCH8

9 32 32K_XP XTAL_32K_P ADC1_CH4 TOUCH9

10 4 GPIO4 - ADC2_CH0 TOUCH0

11 0 GPIO0 - ADC2_CH1 TOUCH1

12 2 GPIO2 - ADC2_CH2 TOUCH2

13 15 MTDO - ADC2_CH3 TOUCH3

14 13 MTCK - ADC2_CH4 TOUCH4

15 12 MTDI - ADC2_CH5 TOUCH5

16 14 MTMS - ADC2_CH6 TOUCH6

17 27 GPIO27 - ADC2_CH7 TOUCH7

1 2 3

Analog Function

4.12 Register Summary

Name Description Address Access

GPIO_OUT_REG GPIO 0-31 output register_REG 0x3FF44004 R/W

GPIO_OUT_W1TS_REG GPIO 0-31 output register_W1TS_REG 0x3FF44008 RO

GPIO_OUT_W1TC_REG GPIO 0-31 output register_W1TC_REG 0x3FF4400C RO

GPIO_OUT1_REG GPIO 0-31 output register1_REG 0x3FF44010 R/W

GPIO_OUT1_W1TS_REG GPIO 0-31 output register1_W1TS_REG 0x3FF44014 RO

GPIO_OUT1_W1TC_REG GPIO 0-31 output register1_W1TC_REG 0x3FF44018 RO

GPIO_OUT_W1TS_REG GPIO 0-31 output bit set register_REG 0x3FF44008 RO

GPIO_OUT_W1TC_REG GPIO 0-31 output bit clear register_REG 0x3FF4400C RO

GPIO_OUT1_REG GPIO 32-39 output register_REG 0x3FF44010 R/W

GPIO_OUT1_W1TS_REG GPIO 32-39 output register_W1TS_REG 0x3FF44014 RO

GPIO_OUT1_W1TC_REG GPIO 32-39 output register_W1TC_REG 0x3FF44018 RO

GPIO_OUT1_W1TS_REG GPIO 32-39 output bit set register_REG 0x3FF44014 RO

GPIO_OUT1_W1TC_REG GPIO 32-39 output bit clear register_REG 0x3FF44018 RO

GPIO_ENABLE_REG GPIO 0-31 output enable register_REG 0x3FF44020 R/W

GPIO_ENABLE_W1TS_REG GPIO 0-31 output enable register_W1TS_REG 0x3FF44024 RO

GPIO_ENABLE_W1TC_REG GPIO 0-31 output enable register_W1TC_REG 0x3FF44028 RO

GPIO_ENABLE1_REG GPIO 0-31 output enable register1_REG 0x3FF4402C R/W

GPIO_ENABLE1_W1TS_REG GPIO 0-31 output enable register1_W1TS_REG 0x3FF44030 RO

GPIO_ENABLE1_W1TC_REG GPIO 0-31 output enable register1_W1TC_REG 0x3FF44034 RO

GPIO_ENABLE_W1TS_REG GPIO 0-31 output enable bit set register_REG 0x3FF44024 RO

GPIO_ENABLE_W1TC_REG GPIO 0-31 output enable bit clear register_REG 0x3FF44028 RO

GPIO_ENABLE1_REG GPIO 32-39 output enable register_REG 0x3FF4402C R/W

Espressif Systems 40 ESP32 Technical Reference Manual V1.0

Page 42

4.12 Register Summary 4 IO_MUX AND GPIO MATRIX

Name Description Address Access

GPIO_ENABLE1_W1TS_REG GPIO 32-39 output enable register_W1TS_REG 0x3FF44030 RO

GPIO_ENABLE1_W1TC_REG GPIO 32-39 output enable register_W1TC_REG 0x3FF44034 RO

GPIO_ENABLE1_W1TS_REG GPIO 32-39 output enable bit set register_REG 0x3FF44030 RO

GPIO_ENABLE1_W1TC_REG GPIO 32-39 output enable bit clear register_REG 0x3FF44034 RO

GPIO_STRAP_REG Bootstrap pin value register_REG 0x3FF44038 RO

GPIO_IN_REG GPIO 0-31 input register_REG 0x3FF4403C RO

GPIO_IN1_REG GPIO 0-31 input register1_REG 0x3FF44040 RO

GPIO_IN1_REG GPIO 32-39 input register_REG 0x3FF44040 RO

GPIO_STATUS_REG GPIO 0-31 interrupt status register_REG 0x3FF44044 R/W

GPIO_STATUS_W1TS_REG GPIO 0-31 interrupt status register_W1TS_REG 0x3FF44048 RO

GPIO_STATUS_W1TC_REG GPIO 0-31 interrupt status register_W1TC_REG 0x3FF4404C RO

GPIO_STATUS1_REG GPIO 0-31 interrupt status register1_REG 0x3FF44050 R/W

GPIO_STATUS1_W1TS_REG GPIO 0-31 interrupt status register1_W1TS_REG 0x3FF44054 RO

GPIO_STATUS1_W1TC_REG GPIO 0-31 interrupt status register1_W1TC_REG 0x3FF44058 RO

GPIO_STATUS_W1TS_REG GPIO 0-31 interrupt status bit set register_REG 0x3FF44048 RO

GPIO_STATUS_W1TC_REG GPIO 0-31 interrupt status bit clear register_REG 0x3FF4404C RO

GPIO_STATUS1_REG GPIO 32-39 interrupt status register_REG 0x3FF44050 R/W

GPIO_STATUS1_W1TS_REG GPIO 32-39 interrupt status register_W1TS_REG 0x3FF44054 RO

GPIO_STATUS1_W1TC_REG GPIO 32-39 interrupt status register_W1TC_REG 0x3FF44058 RO

GPIO_STATUS1_W1TS_REG GPIO 32-39 interrupt status bit set register_REG 0x3FF44054 RO

GPIO_STATUS1_W1TC_REG GPIO 32-39 interrupt status bit clear register_REG 0x3FF44058 RO

GPIO_ACPU_INT_REG GPIO 0-31 APP_CPU interrupt status_REG 0x3FF44060 RO

GPIO_ACPU_INT1_REG GPIO 0-31 APP_CPU interrupt status1_REG 0x3FF44074 RO

GPIO_ACPU_NMI_INT_REG

GPIO_ACPU_NMI_INT1_REG

GPIO 0-31 APP_CPU non-maskable interrupt sta-

tus_REG

GPIO 0-31 APP_CPU non-maskable interrupt sta-

tus1_REG

0x3FF44064 RO

0x3FF44078 RO

GPIO_PCPU_INT_REG GPIO 0-31 PRO_CPU interrupt status_REG 0x3FF44068 RO

GPIO_PCPU_INT1_REG GPIO 0-31 PRO_CPU interrupt status1_REG 0x3FF4407C RO

GPIO_PCPU_NMI_INT_REG

GPIO_PCPU_NMI_INT1_REG

GPIO 0-31 PRO_CPU non-maskable interrupt sta-

tus_REG

GPIO 0-31 PRO_CPU non-maskable interrupt sta-

tus1_REG

0x3FF4406C RO

0x3FF44080 RO

GPIO_ACPU_INT1_REG GPIO 32-39 APP_CPU interrupt status_REG 0x3FF44074 RO

GPIO_ACPU_NMI_INT1_REG

GPIO 32-39 APP_CPU non-maskable interrupt

status_REG

0x3FF44078 RO

GPIO_PCPU_INT1_REG GPIO 32-39 PRO_CPU interrupt status_REG 0x3FF4407C RO

GPIO_PCPU_NMI_INT1_REG

GPIO 32-39 PRO_CPU non-maskable interrupt

status_REG

0x3FF44080 RO

GPIO_PIN0_REG Configuration for GPIO pin 0_REG 0x3FF44088 R/W

GPIO_PIN1_REG Configuration for GPIO pin 1_REG 0x3FF4408C R/W

GPIO_PIN2_REG Configuration for GPIO pin 2_REG 0x3FF44090 R/W

... ...

GPIO_PIN38_REG Configuration for GPIO pin 38_REG 0x3FF44120 R/W

Espressif Systems 41 ESP32 Technical Reference Manual V1.0

Page 43

4.12 Register Summary 4 IO_MUX AND GPIO MATRIX

Name Description Address Access

GPIO_PIN39_REG Configuration for GPIO pin 39_REG 0x3FF44124 R/W

GPIO_FUNC0_IN_SEL_CFG_REG Peripheral function 0 input selection register_REG 0x3FF44130 R/W

GPIO_FUNC1_IN_SEL_CFG_REG Peripheral function 1 input selection register_REG 0x3FF44134 R/W

... ...

GPIO_FUNC254_IN_SEL_CFG_REG

GPIO_FUNC255_IN_SEL_CFG_REG

Peripheral function 254 input selection regis-

ter_REG

Peripheral function 255 input selection regis-

ter_REG

0x3FF44528 R/W

0x3FF4452C R/W

GPIO_FUNC0_OUT_SEL_CFG_REG Peripheral output selection for GPIO 0_REG 0x3FF44530 R/W

GPIO_FUNC1_OUT_SEL_CFG_REG Peripheral output selection for GPIO 1_REG 0x3FF44534 R/W

... ...

GPIO_FUNC38_OUT_SEL_CFG_REG Peripheral output selection for GPIO 38_REG 0x3FF445C8 R/W

GPIO_FUNC39_OUT_SEL_CFG_REG Peripheral output selection for GPIO 39_REG 0x3FF445CC R/W

Name Description Address Access

IO_MUX_GPIO36_REG Configuration register for pad GPIO36 0x3FF53004 R/W

IO_MUX_GPIO37_REG Configuration register for pad GPIO37 0x3FF53008 R/W

IO_MUX_GPIO38_REG Configuration register for pad GPIO38 0x3FF5300C R/W

IO_MUX_GPIO39_REG Configuration register for pad GPIO39 0x3FF53010 R/W

IO_MUX_GPIO34_REG Configuration register for pad GPIO34 0x3FF53014 R/W

IO_MUX_GPIO35_REG Configuration register for pad GPIO35 0x3FF53018 R/W

IO_MUX_GPIO32_REG Configuration register for pad GPIO32 0x3FF5301C R/W

IO_MUX_GPIO33_REG Configuration register for pad GPIO33 0x3FF53020 R/W

IO_MUX_GPIO25_REG Configuration register for pad GPIO25 0x3FF53024 R/W

IO_MUX_GPIO26_REG Configuration register for pad GPIO26 0x3FF53028 R/W

IO_MUX_GPIO27_REG Configuration register for pad GPIO27 0x3FF5302C R/W