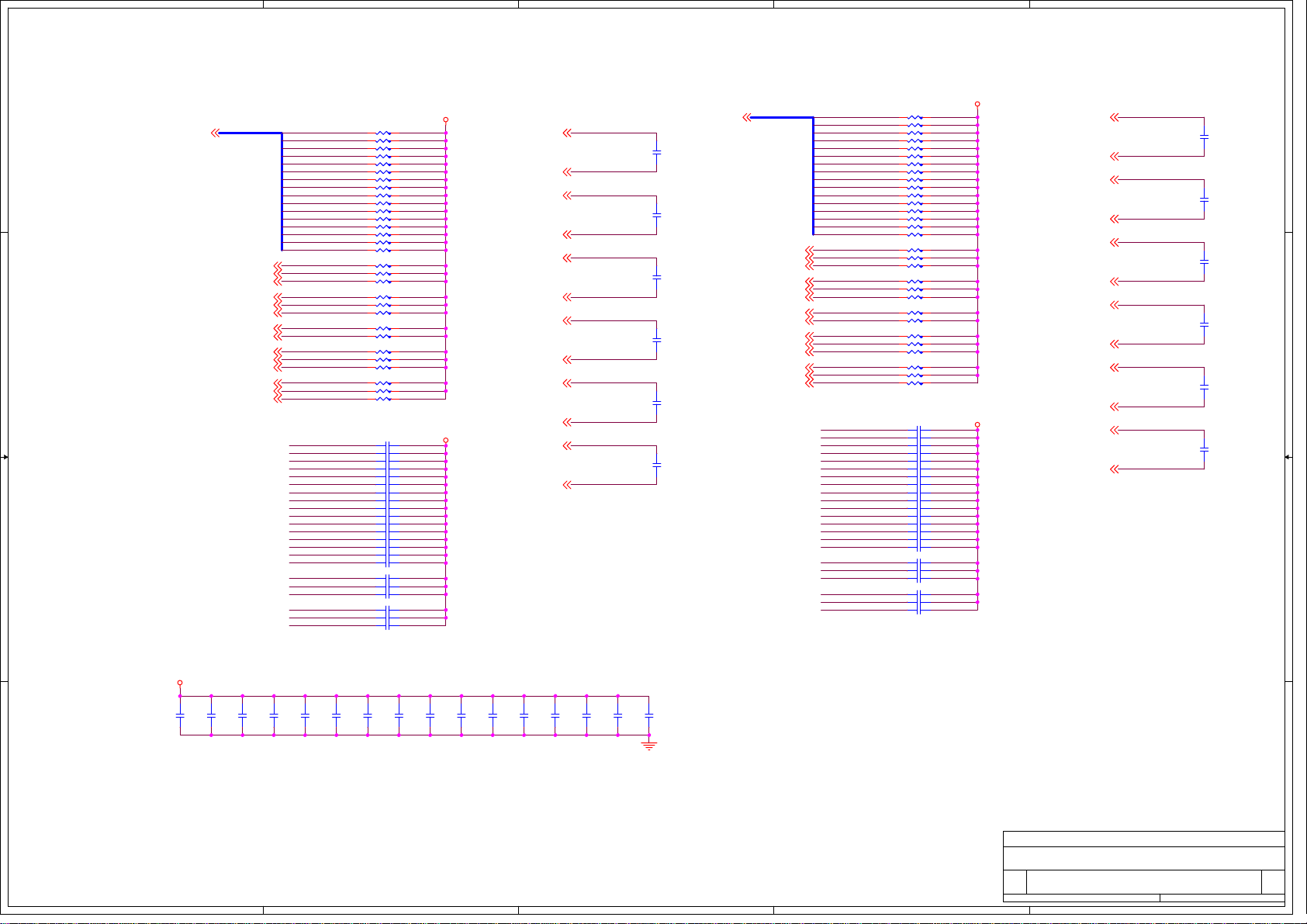

Page 1

A

B

C

D

E

EP-AF570+Ultra

4 4

3 3

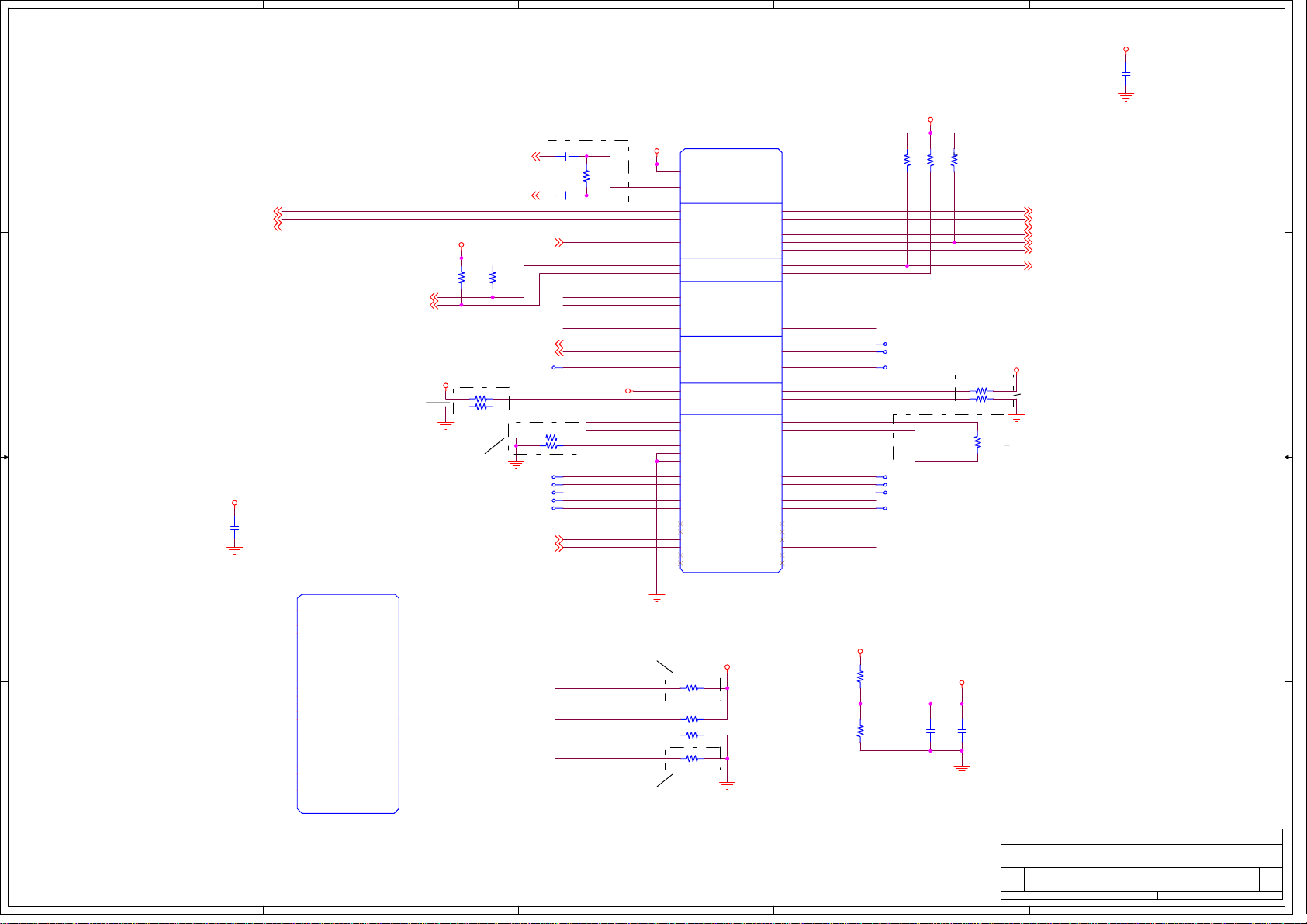

AMD-M2 + NF570 Ultra Schmeatics

TITLE

COVER SHEET

BLOCK DIAGRAM

PROCESSER(SOCKET M2)

DDR DIMM 1,2,3,4

DDR TERMINATIONS

MCP55P

PCI EXPRESS SLOT+SLI SLOT

PCI SLOTS

IDE CONNECTORS

1.5VSB 3VSB 1.5V

LPC I/O

COM1 LPT1 P80P

BIOS

Revision 1.0

SHEET

1

2

3~6

7~8

9

10~17

18

19

20

21

22

23

H/W MONITOR & FAN

2 2

FRONT PANEL & BIOS & KB/MS CONNECTOR

AUDIO C ODEC(ALC660/883)

LAN PCI-E RTL8111B/RTL8101E

LAN PCI-E RTL8111B/RTL8101E

CPU POEWR(VRM 11)

DC TO DC

DC TO DC

1 1

USB CONNECTORS

ATX POWER & POWER SEQUENCING

A

B

C

24

25

26

27

28

29

30

31

32

33

EPOX

Title

Cover Page

Size Document Number Rev

A3

AF570+Ultra

D

Date: Sheet

E

of

133Monday, August 28, 2006

1.0

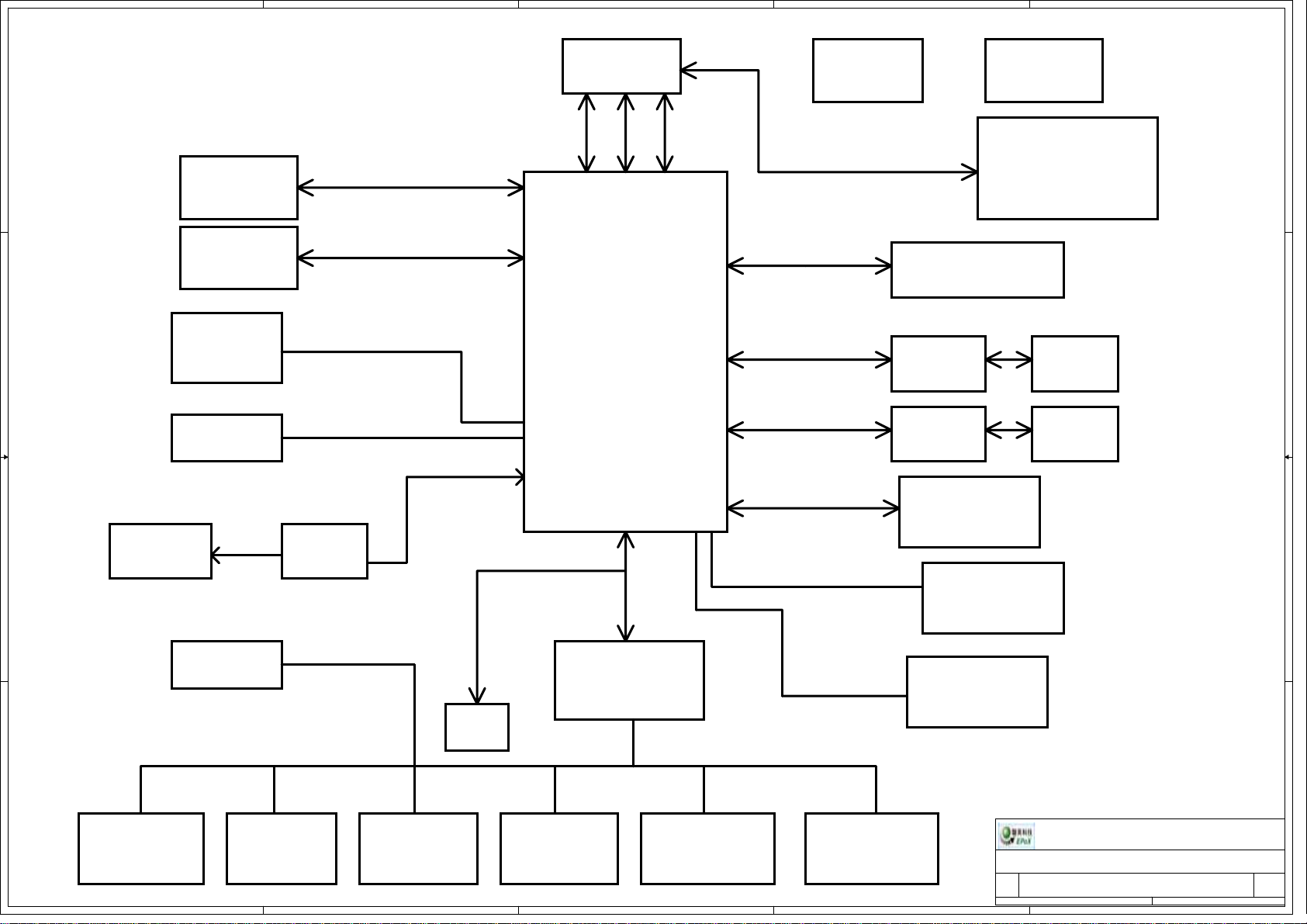

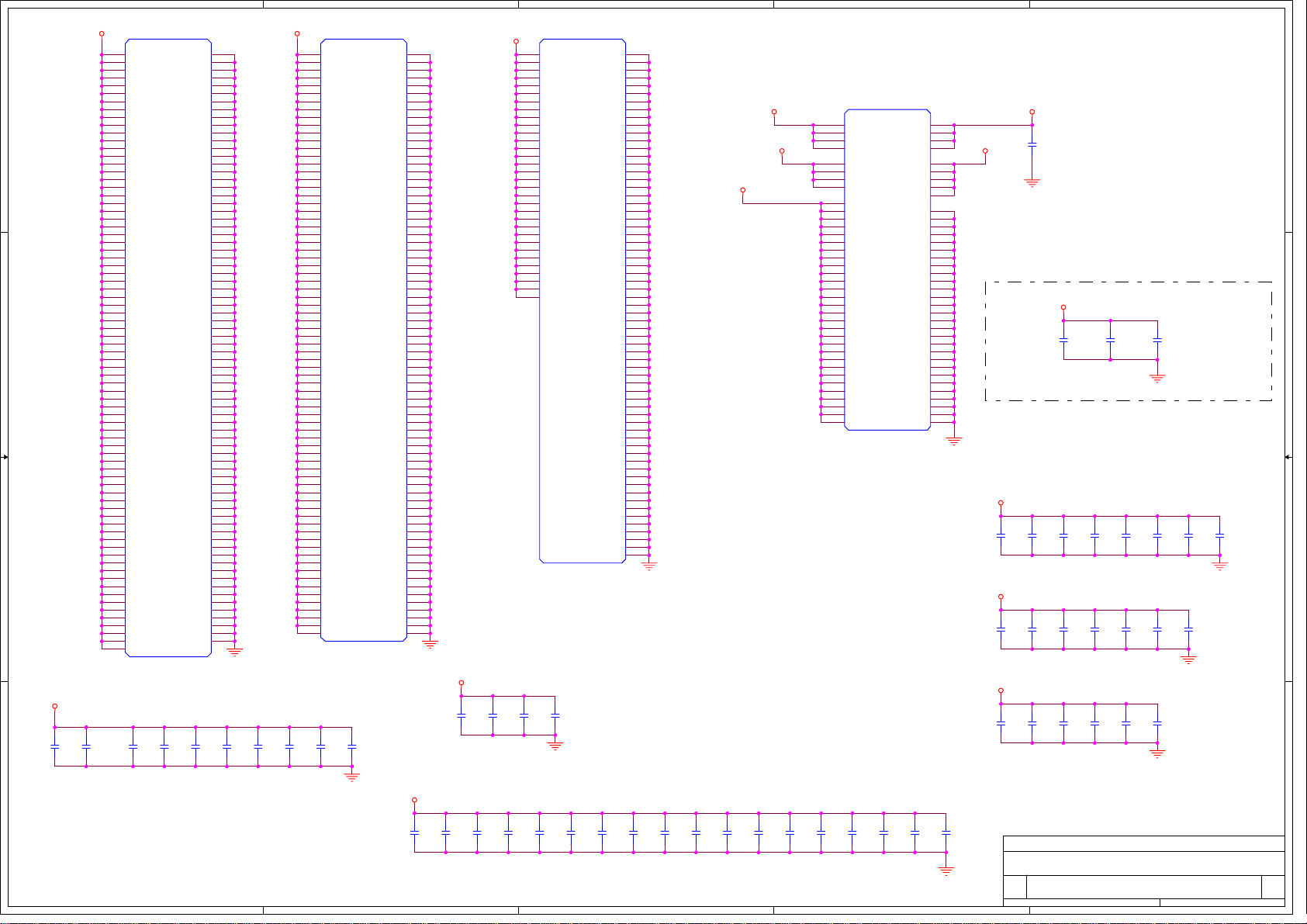

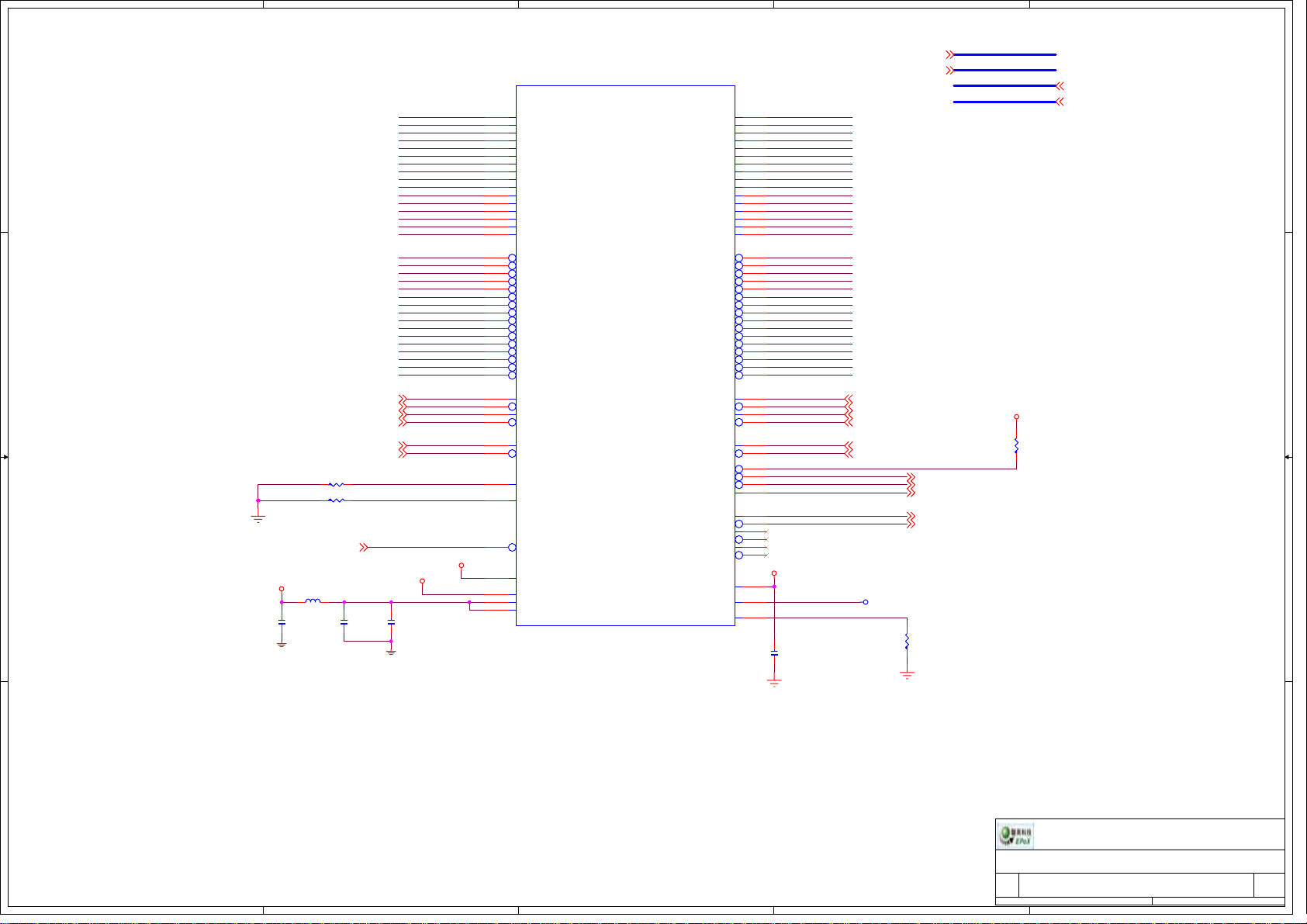

Page 2

A

B

C

D

E

AMD K8

SOCKET M2-940

4 4

CONTROL

ADDRESS

PCI-E x16 Solt

PCI-E x16 Solt

3 3

IDE 1

10 PORT

PCI-E x16

PCI-E x8

ATA-133

USB BUS

MCP55P

DATA

DDR MEMORY BUS

Dual DDR2 400/533/667MHZ

PCI-E x1

RGMII BUS

RGMII BUS

USB

DC-DC

CONVERTER

CLOCK

GENERATOR

DDR2 DIMM X 4

PCI-E x1 Solt X1

RJ-45

M88E1116

CONNECTOR

RJ-45

M88E1116

CONNECTOR

HDA LINK

PCI BUS

PCI Solt X2

AUDIO

2 2

CONNECTOR

HDA

CODEC

SATA 1,2,3,4,5,6

LPC

BUS

PS/2 K/B

MOUSE

LPC SUPER I/O

ATX POWER

F71883F

FRONT PANEL

BIOS

1 1

C

SEARIAL

PORT

GAME PORT

D

EPOX

Title

BLOCK DIAGRAM

Size Document Number Rev

A3

AF570+Ultra

Date: Sheet

E

of

233Monday, August 28, 2006

1.0

IR

HARDWARE

PARALLEL

FLOPPY

MONITOR

A

B

PORT

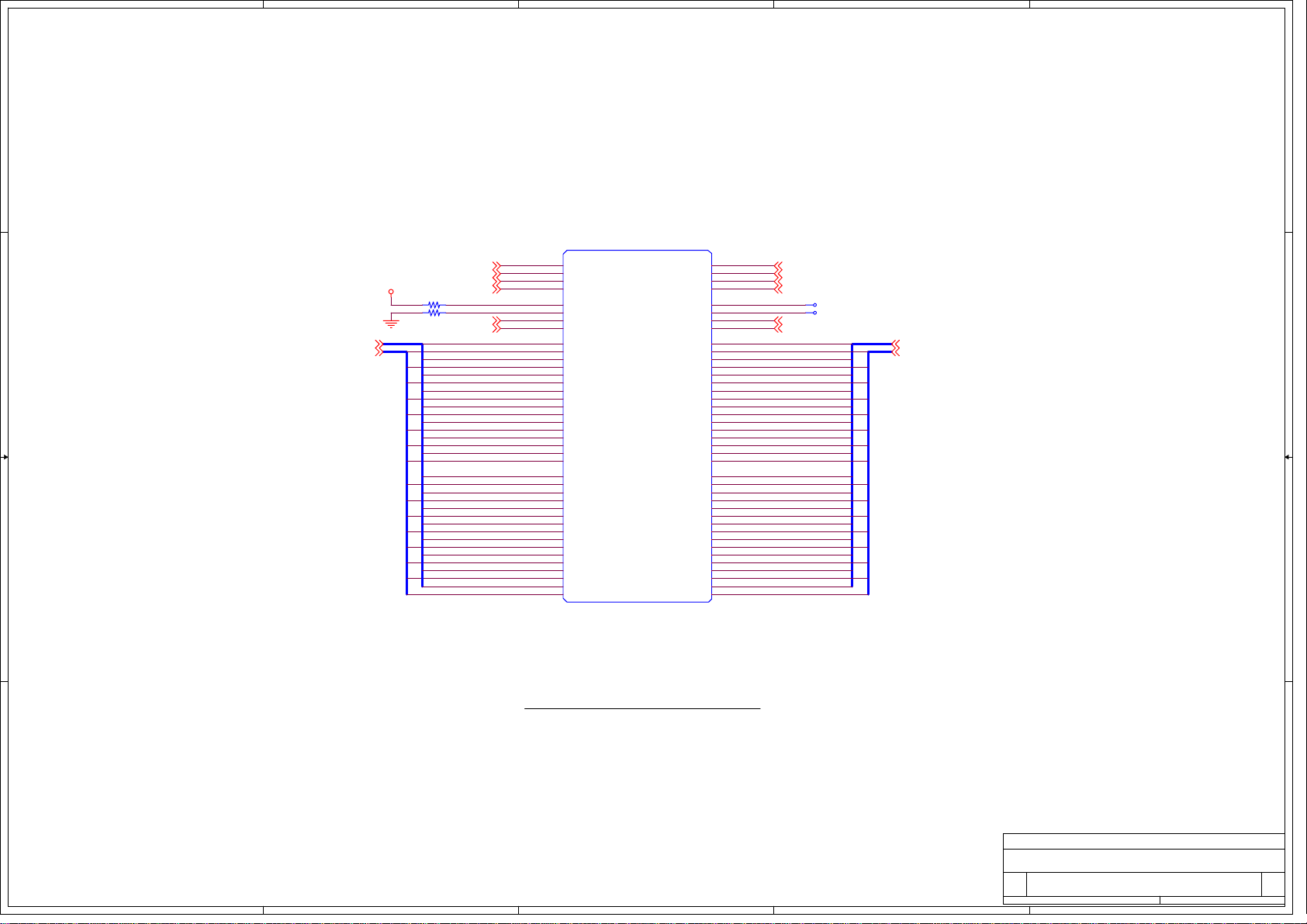

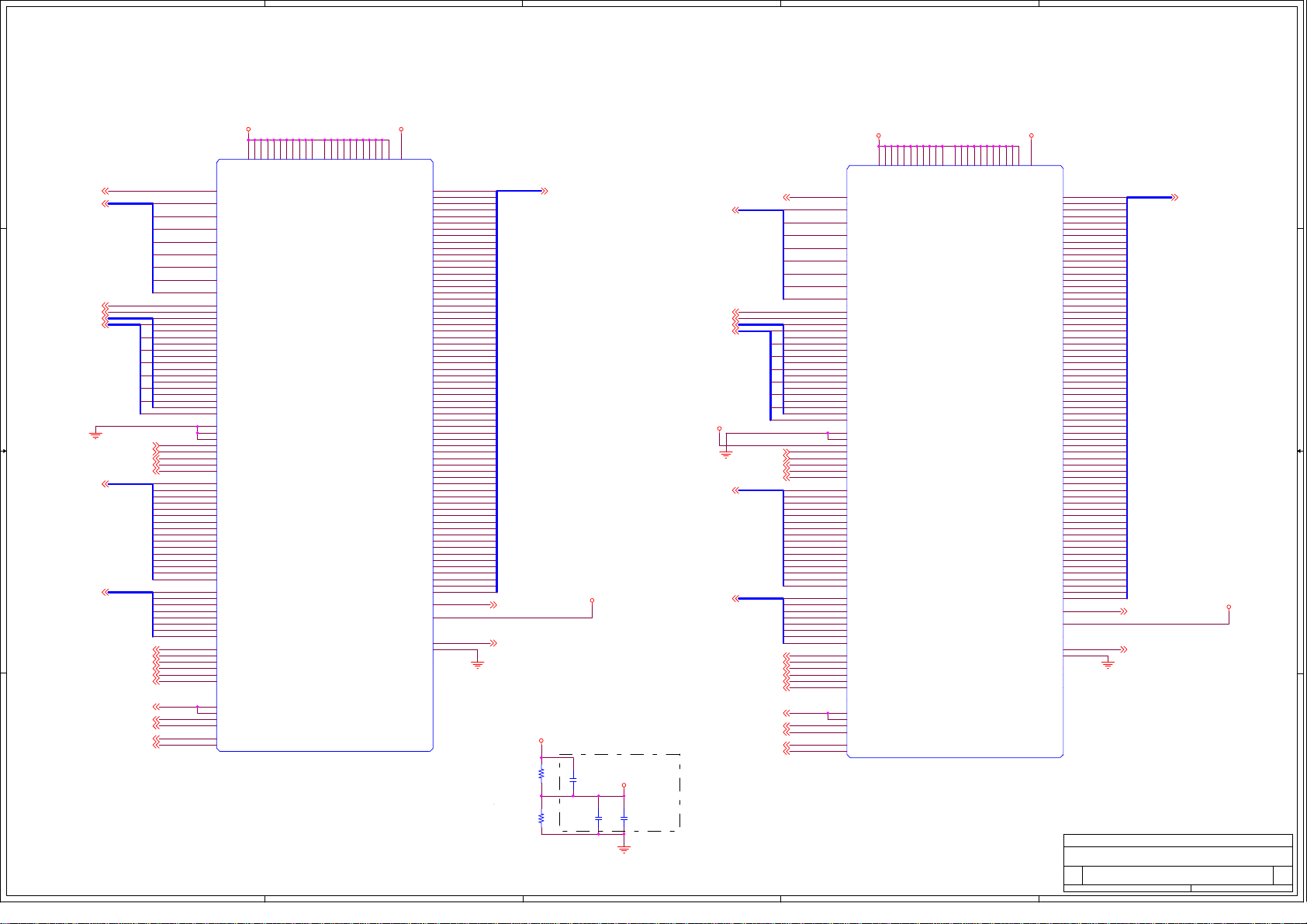

Page 3

5

D D

4

3

2

1

CPU HyperTransport Interface

U13A

HT_UPCLK110

HT_UPCLK1-10

VTT_CPU

C C

B B

HT_UP[15..0]10

HT_UP-[15..0]10

HT_UPCLK010

HT_UPCLK0-10

49.9R150

49.9R154

HT_UPCNTL10

HT_UPCNTL-10

HT_UP15

HT_UP-15

HT_UP14

HT_UP-14

HT_UP13

HT_UP-13

HT_UP12

HT_UP-12

HT_UP11

HT_UP-11

HT_UP10

HT_UP-10

HT_UP9

HT_UP-9

HT_UP8

HT_UP-8

HT_UP7

HT_UP-7

HT_UP6

HT_UP-6

HT_UP5

HT_UP-5

HT_UP4

HT_UP-4

HT_UP3

HT_UP-3

HT_UP2

HT_UP-2

HT_UP1

HT_UP-1

HT_UP-0

HT_CPU_CTLIN_H1

HT_CPU_CTLIN_L1

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

HYPERTRANSPORT

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

AD5

AD4

AD1

AC1

HT_CPU_CTLOUT_H1

Y6

HT_CPU_CTLOUT_L1

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_DWNCLK1 10

HT_DWNCLK1- 10

HT_DWNCLK0 10

HT_DWNCLK0- 10

TPB21

TPB20

HT_DWNCNTL 10

HT_DWNCNTL- 10

HT_DWN15

HT_DWN-15

HT_DWN14

HT_DWN-14

HT_DWN13

HT_DWN-13

HT_DWN12

HT_DWN-12

HT_DWN11

HT_DWN-11

HT_DWN10

HT_DWN-10

HT_DWN9

HT_DWN-9

HT_DWN8

HT_DWN-8

HT_DWN7

HT_DWN-7

HT_DWN6

HT_DWN-6

HT_DWN5

HT_DWN-5

HT_DWN4

HT_DWN-4

HT_DWN3

HT_DWN-3

HT_DWN2

HT_DWN-2

HT_DWN1

HT_DWN-1

HT_DWN0HT_UP0

HT_DWN-0

HT_DWN[15..0] 10

HT_DWN-[15..0] 10

Layout: Add stitching caps if crossing plane split

HyperTransport Net Naming Convention

HT_"link driver"_"link receiver"_"function" _"polarity " _"number"

A A

Title

EPoX

Size Document Number Rev

Date: Sheet of

5

4

3

2

Monday, August 28, 2006

M2-CPU

AF570+Ultra

333

1

1.0

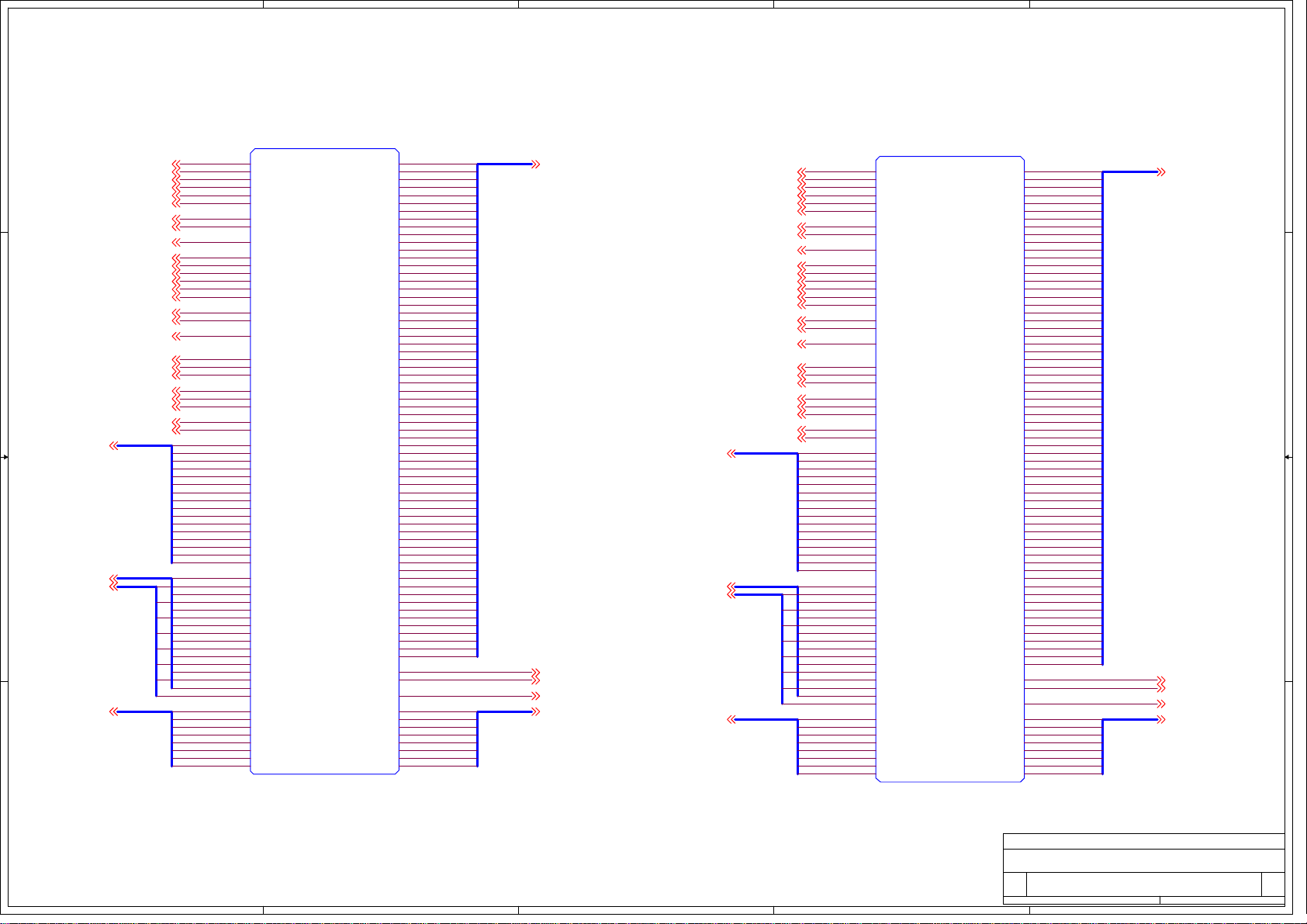

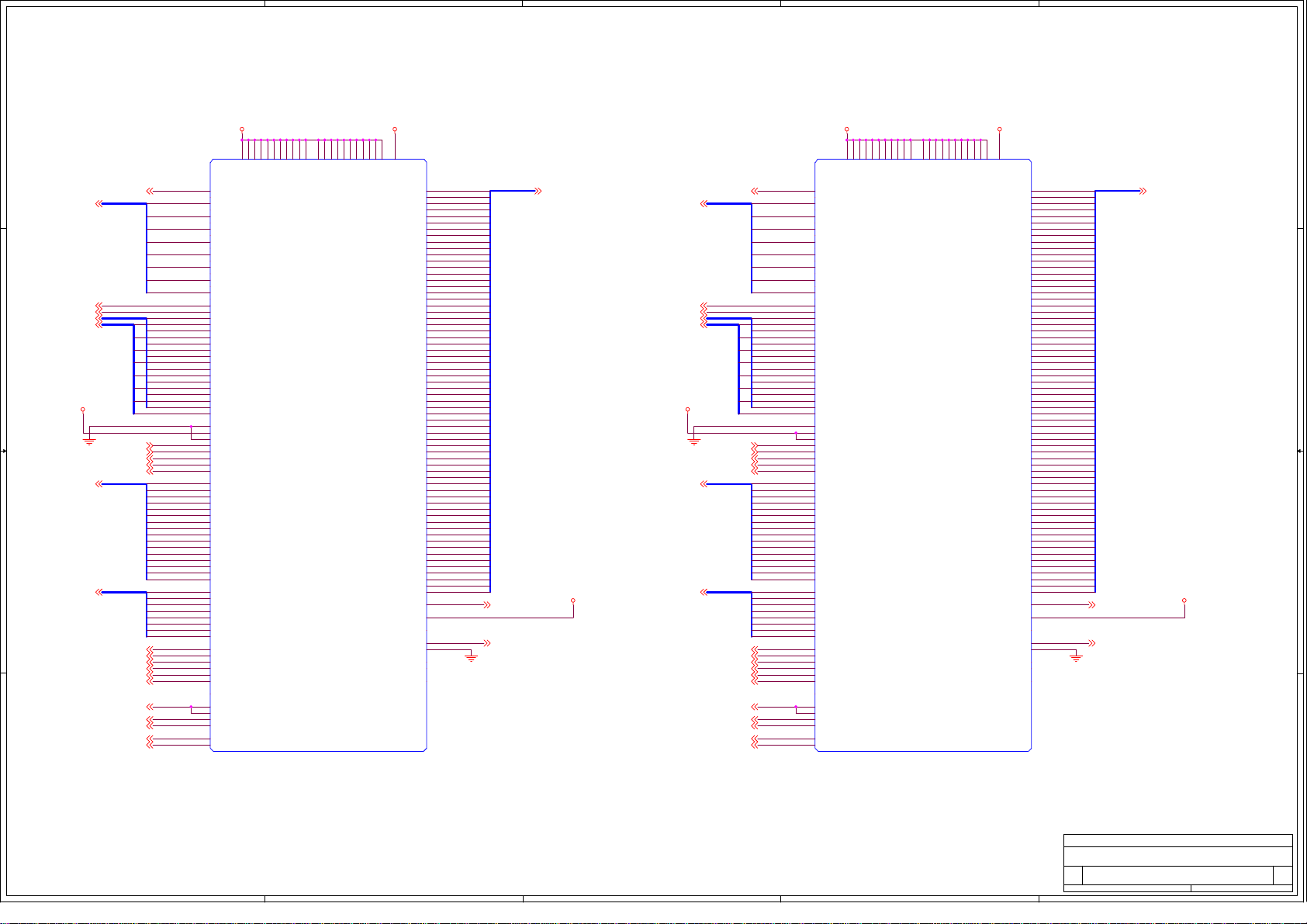

Page 4

5

4

3

2

1

CPU DDR2 Memory Interface

D D

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

G19

H19

U27

U26

AC25

AA24

AC28

AE20

AE19

G20

G21

V27

W27

AD27

AA25

AC27

AB25

AB27

AA26

N25

Y27

AA27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

L27

T25

T27

F19

F15

MEM_MA0_CLK_H27,9

MEM_MA0_CLK_L27,9 MEM_MB0_CLK_H27,9

MEM_MA0_CLK_H17,9

MEM_MA0_CLK_L17,9

MEM_MA0_CLK_H07,9

MEM_MA0_CLK_L07,9

MEM_MA0_CS_L17,9

MEM_MA0_CS_L07,9

MEM_MA0_ODT07,9

MEM_MA1_CLK_H28,9

MEM_MA1_CLK_L28,9

MEM_MA1_CLK_H18,9

MEM_MA1_CLK_L18,9

MEM_MA1_CLK_H08,9

MEM_MA1_CLK_L08,9

MEM_MA1_CS_L18,9

MEM_MA1_CS_L08,9

C C

MEM_MA1_ODT08,9

MEM_MA_CAS_L7,8,9

MEM_MA_WE_L7,8,9

MEM_MA_RAS_L7,8,9

MEM_MA_BANK27,8,9

MEM_MA_BANK17,8,9

MEM_MA_BANK07,8,9

MEM_MA_CKE18,9

MEM_MA_CKE07,9

MEM_MA_ADD[15..0]7,8,9

B B

MEM_MA_DQS_H[7..0]7,8

MEM_MA_DQS_L[7..0]7,8

MEM_MA_DM[7..0]7,8

A A

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

U13B

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_DATA[63..0] 7,8

MEM_MA_DQS_H8 7,8

MEM_MA_DQS_L8 7,8

MEM_MA_DM8 7,8

MEM_MA_CHECK[7..0 ] 7,8

U13C

AJ19

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AK19

A18

A19

U31

U30

AE30

AC31

AD29

AL19

AL18

C19

D19

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

N31

AA31

AA28

M31

M29

N28

N29

AE31

N30

P29

AA29

P31

R29

R28

R31

R30

T31

T29

U29

U28

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AH17

AJ23

AK29

C30

A23

B17

B13

MEM_MB0_CLK_L27,9

MEM_MB0_CLK_H17,9

MEM_MB0_CLK_L17,9

MEM_MB0_CLK_H07,9

MEM_MB0_CLK_L07,9

MEM_MB0_CS_L17,9

MEM_MB0_CS_L07,9

MEM_MB0_ODT07,9

MEM_MB1_CLK_H28,9

MEM_MB1_CLK_L28,9

MEM_MB1_CLK_H18,9

MEM_MB1_CLK_L18,9

MEM_MB1_CLK_H08,9

MEM_MB1_CLK_L08,9

MEM_MB1_CS_L18,9

MEM_MB1_CS_L08,9

MEM_MB1_ODT08,9

MEM_MB_CAS_L7,8,9

MEM_MB_WE_L7,8,9

MEM_MB_RAS_L7,8,9

MEM_MB_BANK27,8,9

MEM_MB_BANK17,8,9

MEM_MB_BANK07,8,9

MEM_MB_CKE18,9

MEM_MB_CKE07,9

MEM_MB_ADD[15..0]7,8,9

MEM_MB_DQS_H[7..0]7,8

MEM_MB_DQS_L[7..0]7,8

MEM_MB_DM[7..0]7,8

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DATA[63..0] 7,8

MEM_MB_DQS_H8 7,8

MEM_MB_DQS_L8 7,8

MEM_MB_DM8 7,8

MEM_MB_CHECK[7..0 ] 7,8

Title

Size Document Number Rev

Date: Sheet of

5

4

3

2

Monday, August 28, 2006

M2-CPU

AF570+Ultra

433

1

1.0

Page 5

5

4

3

2

1

These signals must be

driven low during S3

CPU Control & Debug Interfaces

and S5 states, including

state transitions, to meet

HT I/O Link Specification

Keep trace to resistor

less than 600mils from CPU pin and

D D

BUF-CPU_PWRGD33

BUF-HT_STOP-33

BUF-CPU_RST-33

CPU_SIC15

CPU_SID15

C C

Keep trace to resistors less

than 1.5" from CPU pin

Erratum 133 , R e v i sion Guide for

AMD NPT 0Fh Processors

3VSB

C361

0.1uF

B B

A A

GND

U13E

INTERNAL MISC

L25

L26

L31

L30

W26

W25

AE27

U24

V24

AE28

Y31

Y30

AG31

V31

W31

AF31

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

E20

B19

AL4

AK4

AK3

F2

F3

G4

G3

G5

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

trace to AC caps less than 1250mils

VCC_DDR

VCC_DDR

CPU_CLK10

CPU_CLK-10

R157

R163

300

300

CPU_CORE_FB29

CPU_CORE_FB-29

39.2R183

39.2R184

GND

SKTOCC-22

TPB9

CPU_M_VREF_SUS

M_ZN

M_ZP

R159 300

R170 300

TPB19

TPB18

TPB12

TPB22

TPB14

D-22,24

D1+22

C179

3900pF

C176

3900pF

Erratum 133 , R e v i sion Guide for

AMD NPT 0Fh Processors

Erratum 133 , R e v i sion Guide for

AMD NPT 0Fh Processors

+2.5VDDA

C10

R151

169

CPU_CLKIN_SC_H

CPU_CLKIN_SC_L

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

CPU_TEST25_H

CPU_TES T 25_L CPU_TEST29_L

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST12

D10

AL3

AL6

AK6

AL10

AJ10

AH10

AL9

E12

F12

AH11

AJ11

A10

B10

F10

AJ7

AH9

AJ5

AG9

AG8

AH7

AJ6

GND

VDDA1

VDDA2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

E9

TEST18

TEST13

F6

TEST9

D6

TEST17

E7

TEST16

F8

TEST15

C5

TEST14

TEST12

E5

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

M2

MISC

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

TDO

PSI_L

TEST8

U13D

VCC_DDR

CPU_TEST26

CPU_TEST25_H

CPU_TES T 25_L

CPU_TEST21

300R165

510R182

510R181

300R164

GND

Required for compatibility

with future processors

VCC_DDR

Level tran slation output circuits

Assuming system devices

Require 3.3V signaling

VID5 22,29

VID4 22,29

VID3 22,29

VID2 22,29

VID1 22,29

VID0 22,29

THERMTRIP- 10

VTT_CPU

Keep trace to resistors

less than 1.5" from CPU pin

GND

Route as 80-Ohm differential impedance

D2

D1

C1

E3

E2

E1

AK7

AL7

AK10

B6

AK11

AL11

CPU_PSI_LCPU_VTT_SUS_SENSE

F1

CPU_HTREF1

V8

CPU_HTREF0

V7

C11

D11

CPU_DBRDY

VID5

VID4

VID3

VID2

VID1

VID0

CPU_PROCHOT_L_1.8

CPU_TDO

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_TEST29_H

TPB11

TPB10

TPB23

R174

300

R166

300

44.2 R149

44.2 R153

R172

80.6

R161

300

Keep trace to resistor less than 1" from CPU pin

CPU_TEST24CPU_TEST17

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

CPU_TEST23

CPU_TEST22

CPU_TEST21

CPU_TEST20

CPU_TEST26

TPB17

TPB13

TPB15

TPB16

CPU_M_VREF_SUS

VCC_DDR

R171

16.9

R173

16.9

CPU_M_VREF_SUS

C191

C192

0.1uF

1000pF

GND

VCC_DDR

C251

0.1uF

M2

5

4

3

2

Title

M2-CPU

Size Document Number Rev

A3

Date: Sheet

AF570+Ultra

of

533Monday, August 28, 2006

1

1.0

Page 6

5

VCC_CPU VCC_CPU

A4

A6

AA8

AA10

AA12

AA14

AA16

AA18

AB7

D D

C C

B B

AB9

AB11

AC4

AC5

AC8

AC10

AD2

AD3

AD7

AD9

AE10

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

F11

G10

G12

H11

H23

J12

J14

J16

J18

J20

J22

J24

K11

K13

K15

K17

K19

K21

K23

L10

L12

Y17

Y19

B3

B5

B7

C2

C4

C6

C8

D3

D5

D7

D9

E4

E6

E8

F5

F7

F9

G6

G8

H7

J8

K7

K9

L4

L5

L8

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD150

VDD151

VDD1

U13F

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

P11

P13

P15

P17

P19

R10

R12

R14

R16

R18

R20

T11

T13

T15

T17

T19

T21

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

V21

W10

W12

W14

W16

W18

W20

Y11

Y13

Y15

Y21

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

N8

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

P7

VDD19

P9

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

U8

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

V9

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

VDD72

VDD73

VDD74

VDD75

VDD2

U13G

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

4

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

VCC_CPU

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

L20

L22

M21

M23

N20

N22

P21

P23

R22

T23

U22

V23

W22

Y23

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

U13H

VDD3

VCC_CPU

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

3

2

1

Processor Power & Ground

VLDT_RUN_B is connected to the VLDT_RUN power

supply through the package or on the die. It is only connected

on the board to decoupling near the CPU package.

VTT_CPU

AJ4

AJ3

D12

C12

B12

A12

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

P24

P26

P28

P30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

AJ2

AJ1

T24

T26

T28

T30

VTT_DDR VTT_DDR

VCC_DDR

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO29

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

U13I

VDDIO

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

VLDT_RUN_B

C163

10uF/10V 1206

Place near processor on VLDT pour.

VTT_CPU

C190

10uF/10V 1206

10uF/10V 1206(B)

C250

1uF

C169

0.01uF

CB66

CB69

10uF/10V 1206(B)

C266

1uF

0.01uF

C365

0.1uF(B)

C265

1uF

0.1uF

CB31

1uF(B)

CB65

0.1uF(B)

C281

1uF

VCC_DDR

CB71

VCC_DDR

VCC_DDR

C174

CB68

CB70

10uF/10V 1206(B)

10uF/10V 1206(B)

C200

C204

1uF

1uF

CB64

0.01uF(B)

VTT_DDR

CB28

1uF(B)

CB27

1uF(B)

CB26

1uF(B)

CB25

1uF(B)

C286

1uF

CB30

C283

0.1uF

C232

0.1uF

0.1uF

0.01uF

C297

C170

1uF(B)

C211

C213

C342

4.7uF 0805

0.1uF

5

4.7uF 0805

C206

C205

A A

C347

C353

0.1uF

0.1uF

0.1uF

C337

C335

0.1uF

C349

0.1uF

0.1uF

1000pF

VCC_CPU

C311

C161

10uF/10V 1206

C162

10uF/10V 1206

10uF/10V 1206

2

Title

M2-CPU

Size Document Number Rev

A3

Date: Sheet of

AF570+Ultra

1

633Monday, August 28, 2006

1.0

CB80

4

CB76

CB72

10uF/10V 1206(B)

CB67

10uF/10V 1206(B)

10uF/10V 1206(B)

CB73

CB78

10uF/10V 1206(B)

CB75

CB85

10uF/10V 1206(B)

10uF/10V 1206(B)

10uF/10V 1206(B)

CB82

CB84

10uF/10V 1206(B)

10uF/10V 1206(B)

3

CB77

CB74

10uF/10V 1206(B)

10uF/10V 1206(B)

CB83

CB81

10uF/10V 1206(B)

CB79

10uF/10V 1206(B)

10uF/10V 1206(B)

10uF/10V 1206(B)

Page 7

5

4

3

2

1

First Logical DDR2 DIMM

DIMMA0

D D

MEM_MA_DM84,8

MEM_MA_DM[7..0]4,8

MEM_MA_DQS_H84,8

MEM_MA_DQS_L84,8

MEM_MA_DQS_H[7..0]4,8

MEM_MA_DQS_L[7..0]4,8

C C

GND

MEM_MA_BANK24,8,9

MEM_MA_BANK14,8,9

MEM_MA_BANK04,8,9

MEM_MA_ADD[15..0]4,8,9

B B

MEM_MA_CHECK[7..0]4,8

MEM_MA0_CLK_H04,9

MEM_MA0_CLK_L04,9

MEM_MA0_CLK_H14,9

MEM_MA0_CLK_L14,9

MEM_MA0_CLK_H24,9

MEM_MA0_CLK_L24,9

MEM_MA_CKE04,9

MEM_MA_RAS_L4,8,9

MEM_MA_CAS_L4,8,9

MEM_MA0_CS_L04,9

MEM_MA0_CS_L14,9

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MSMBCK8,15

MSMBDT8,15

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_CKE0

VCC_DDR

172

178

184

187

189

197

64

170

175

181

191

69

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

VDD1067VDD11

VDDQ1

VDDQ2

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDDQ3

+3_3V

72

78

VDDQ1075VDDQ11

238

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

ERR_OUT_L

PAR_IN

DIMM1

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

MEM_MA_DATA0MEM_MA_CHECK7

3

DQ0

73

1

MEM_MA_WE_L 4,8,9

MEM_MA_DATA[63..0] 4,8

MEM_M_VREF_SUS

102

195

77

55

68

19

NC1

MEM_MA0_ODT0 4,9

GND

MEM_M_VREF_SUS

Layout: Place near DIMM sockets

VCC_DDR

MEM_MB_DM[7..0]4,8

MEM_MB_DQS_H84,8

MEM_MB_DQS_L84,8

MEM_MB_DQS_H[7..0]4,8

MEM_MB_DQS_L[7..0]4,8

+3_3V

GND

MEM_MB_BANK24,8,9

MEM_MB_BANK14,8,9

MEM_MB_BANK04,8,9

MEM_MB_ADD[15..0]4,8,9

MEM_MB_CHECK[7..0]4,8

MEM_MB0_CLK_H04,9

MEM_MB0_CLK_L04,9

MEM_MB0_CLK_H14,9

MEM_MB0_CLK_L14,9

MEM_MB0_CLK_H24,9

MEM_MB0_CLK_L24,9

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MSMBCK8,15

MSMBDT8,15

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_CKE04,9

MEM_MB_RAS_L4,8,9

MEM_MB_CAS_L4,8,9

MEM_MB0_CS_L04,9

MEM_MB0_CS_L14,9

194

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

VCC_DDR

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

DIMMB0

172

178

184

187

189

197

64

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

69

VDD1067VDD11

+3_3V

170

175

181

191

194

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

72

78

VDDQ1075VDDQ11

ERR_OUT_L

238

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

NC1

DIMM2

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

73

1

102

195

77

55

68

19

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0MEM_MB_CHECK7

GND

MEM_MB_WE_L 4,8,9

MEM_MB0_ODT0 4,9

MEM_MB_DATA[63..0] 4,8MEM_MB_DM84,8

MEM_M_VREF_SUS

60.4 1%

60.4 1%

MEM_M_VREF_SUS

0.1uF

C329

C330

0.1uF

C301

0.01uF

Custom

GND

3

2

Title

DDR2

Size Document Number Rev

Date: Sheet

AF570+Ultra

1

733Monday, August 28, 2006

of

1.0

A A

5

4

R287

R288

Page 8

5

4

3

2

1

Second Logical DDR2 DIMM

DIMMA1

D D

172

178

184

187

189

197

64

170

175

181

191

69

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

VDD1067VDD11

VDDQ1

VDDQ2

MEM_MA_DM[7..0]4,7

MEM_MA_DM84,7

MEM_MA_DQS_H84,7

MEM_MA_DQS_L84,7

MEM_MA_DQS_H[7..0]4,7

MEM_MA_DQS_L[7..0]4,7

C C

MSMBCK7,15

GND

MSMBDT7,15

MEM_MA_BANK24,7,9

MEM_MA_BANK14,7,9

MEM_MA_BANK04,7,9

MEM_MA_ADD[15..0]4,7,9

B B

MEM_MA_CHECK[7..0]4,7

MEM_MA1_CLK_H04,9

MEM_MA1_CLK_L04,9

MEM_MA1_CLK_H14,9

MEM_MA1_CLK_L14,9

MEM_MA1_CLK_H24,9

MEM_MA1_CLK_L24,9

MEM_MA_CKE14,9

MEM_MA_RAS_L4,7,9

MEM_MA_CAS_L4,7,9

MEM_MA1_CS_L04,9

MEM_MA1_CS_L14,9

164

DQS17_H

165

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK7 MEM_MA_DATA0

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDDQ3

+3_3V +3_3V

72

78

VDDQ1075VDDQ11

DIMM3

238

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

ERR_OUT_L

PAR_IN

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

3

DQ0

73

1

MEM_MA_WE_L 4,7,9

102

195

77

55

68

19

NC1

MEM_MA1_ODT0 4,9

GND

MEM_MA_DATA[63..0] 4,7

MEM_MB_DM[7..0]4,7

MEM_MB_DQS_H84,7

MEM_MB_DQS_L84,7

MEM_MB_DQS_H[7..0]4,7

MEM_MB_DQS_L[7..0]4,7

MEM_MB_ADD[15..0]4,7,9

MEM_M_VREF_SUS MEM_M_VREF_SUS

MEM_MB_CHECK[7..0]4,7

MEM_MB_DM84,7

+3_3V+3_3V

GND

MEM_MB_BANK24,7,9

MEM_MB_BANK14,7,9

MEM_MB_BANK04,7,9

MEM_MB1_CLK_H04,9

MEM_MB1_CLK_L04,9

MEM_MB1_CLK_H14,9

MEM_MB1_CLK_L14,9

MEM_MB1_CLK_H24,9

MEM_MB1_CLK_L24,9

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MSMBCK7,15

MSMBDT7,15

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

194

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

MEM_MB_CKE14,9

MEM_MB_RAS_L4,7,9

MEM_MB_CAS_L4,7,9

MEM_MB1_CS_L04,9

MEM_MB1_CS_L14,9

VCC_DDRVCC_DDR

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

DIMMB1

172

178

184

187

189

197

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

64

170

175

181

191

194

69

VDD1067VDD11

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

72

78

VDDQ1075VDDQ11

DIMM4

238

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

ERR_OUT_L

PAR_IN

MEM_MB_DATA63

236

MEM_MB_DATA62

235

MEM_MB_DATA61

230

MEM_MB_DATA60

229

MEM_MB_DATA59

117

MEM_MB_DATA58

116

MEM_MB_DATA57

111

MEM_MB_DATA56

110

MEM_MB_DATA55

227

MEM_MB_DATA54

226

MEM_MB_DATA53

218

MEM_MB_DATA52

217

MEM_MB_DATA51

108

MEM_MB_DATA50

107

MEM_MB_DATA49

99

MEM_MB_DATA48

98

MEM_MB_DATA47

215

MEM_MB_DATA46

214

MEM_MB_DATA45

209

MEM_MB_DATA44

208

MEM_MB_DATA43

96

MEM_MB_DATA42

95

MEM_MB_DATA41

90

MEM_MB_DATA40

89

MEM_MB_DATA39

206

MEM_MB_DATA38

205

MEM_MB_DATA37

200

MEM_MB_DATA36

199

MEM_MB_DATA35

87

MEM_MB_DATA34

86

MEM_MB_DATA33

81

MEM_MB_DATA32

80

MEM_MB_DATA31

159

MEM_MB_DATA30

158

MEM_MB_DATA29

153

MEM_MB_DATA28

152

MEM_MB_DATA27

40

MEM_MB_DATA26

39

MEM_MB_DATA25

34

MEM_MB_DATA24

33

MEM_MB_DATA23

150

MEM_MB_DATA22

149

MEM_MB_DATA21

144

MEM_MB_DATA20

143

MEM_MB_DATA19

31

MEM_MB_DATA18

30

MEM_MB_DATA17

25

MEM_MB_DATA16

24

MEM_MB_DATA15

141

MEM_MB_DATA14

140

MEM_MB_DATA13

132

MEM_MB_DATA12

131

MEM_MB_DATA11

22

MEM_MB_DATA10

21

MEM_MB_DATA9

13

DQ9

MEM_MB_DATA8

12

DQ8

MEM_MB_DATA7

129

DQ7

MEM_MB_DATA6

128

DQ6

MEM_MB_DATA5

123

DQ5

MEM_MB_DATA4

122

DQ4

MEM_MB_DATA3

10

DQ3

MEM_MB_DATA2

9

DQ2

MEM_MB_DATA1

4

DQ1

MEM_MB_DATA0

3

DQ0

73

1

MEM_MB_WE_L 4,7,9

MEM_MB_DATA[63..0] 4,7

102

195

77

55

68

19

NC1

MEM_MB1_ODT0 4,9

GND

A A

Custom

Title

DDR2

Size Document Number Rev

5

4

3

2

Date: Sheet

AF570+Ultra

1

833Monday, August 28, 2006

1.0

of

Page 9

5

4

3

2

1

DDR2 Termination

VTT_DDR

D D

C C

B B

MEM_MA_ADD[15..0]4,7,8

MEM_MA_CAS_L4,7,8

MEM_MA_WE_L4,7,8

MEM_MA_RAS_L4,7,8

MEM_MA_BANK24,7,8

MEM_MA_BANK14,7,8

MEM_MA_BANK04,7,8

MEM_MA_CKE14,8

MEM_MA_CKE04,7

MEM_MA0_CS_L14,7

MEM_MA0_CS_L04,7

MEM_MA0_ODT04,7

MEM_MA1_CS_L14,8

MEM_MA1_CS_L04,8

MEM_MA1_ODT04,8

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

R295 47 0402

R292 47 0402

R345 47 0402

R303 47 0402

R300 47 0402

R322 47 0402

R298 47 0402

R304 47 0402

R302 47 0402

R306 47 0402

R308 47 0402

R312 47 0402

R314 47 0402

R321 47 0402

R318 47 0402

R324 47 0402

R338 47 0402

R335 47 0402

R329 47 0402

R294 47 0402

R325 47 0402

R327 47 0402

R291 47 0402

R293 47 0402

R348 47 0402

R333 47 0402

R341 47 0402

R347 47 0402

R331 47 0402

R343 47 0402

VTT_DDR

MEM_MA0_CLK_H24,7

MEM_MA0_CLK_L24,7

MEM_MA0_CLK_H14,7

MEM_MA0_CLK_L14,7

MEM_MA0_CLK_H04,7

MEM_MA0_CLK_L04,7

MEM_MB0_CLK_H24,7

MEM_MB0_CLK_L24,7

MEM_MB0_CLK_H14,7

VCC_DDR

22pF 0402C255

22pF 0402C237

22pF 0402C254

22pF 0402C256

22pF 0402C239

22pF 0402C244

22pF 0402C257

22pF 0402C258

22pF 0402C240

22pF 0402C259

22pF 0402C241

22pF 0402C236

22pF 0402C260

22pF 0402C242

22pF 0402C261

22pF 0402C253

22pF 0402C246

22pF 0402C264

22pF 0402C245

22pF 0402C238

22pF 0402C262

22pF 0402C263

MEM_MB0_CLK_L14,7

MEM_MB0_CLK_H04,7

MEM_MB0_CLK_L04,7

MEM_MB_ADD[15..0]4,7,8 MEM_MA1_CLK_H24,8

C225

1.5pF 0402

C224

1.5pF 0402

MEM_MB_CAS_L4,7,8

MEM_MB_WE_L4,7,8

C243

1.5pF 0402

C228

1.5pF 0402

C229

1.5pF 0402

C249

1.5pF 0402

MEM_MB_RAS_L4,7,8

MEM_MB_BANK24,7,8

MEM_MB_BANK14,7,8

MEM_MB_BANK04,7,8

MEM_MB_CKE14,8

MEM_MB_CKE04,7

MEM_MB0_CS_L14,7

MEM_MB0_CS_L04,7

MEM_MB0_ODT04,7

MEM_MB1_CS_L14,8

MEM_MB1_CS_L04,8

MEM_MB1_ODT04,8

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

R297 47 0402

R299 47 0402

R344 47 0402

R305 47 0402

R309 47 0402

R328 47 0402

R307 47 0402

R313 47 0402

R311 47 0402

R315 47 0402

R310 47 0402

R317 47 0402

R319 47 0402

R320 47 0402

R316 47 0402

R323 47 0402

R339 47 0402

R337 47 0402

R332 47 0402

R301 47 0402

R326 47 0402

R330 47 0402

R296 47 0402

R290 47 0402

R349 47 0402

R336 47 0402

R340 47 0402

R346 47 0402

R334 47 0402

R342 47 0402

22pF 0402C287

22pF 0402C268

22pF 0402C279

22pF 0402C284

22pF 0402C270

22pF 0402C275

22pF 0402C288

22pF 0402C289

22pF 0402C271

22pF 0402C290

22pF 0402C272

22pF 0402C273

22pF 0402C285

22pF 0402C274

22pF 0402C291

22pF 0402C278

22pF 0402C277

22pF 0402C294

22pF 0402C293

22pF 0402C269

22pF 0402C292

22pF 0402C276

VCC_DDR

C222

1.5pF 0402

MEM_MA1_CLK_L24,8

MEM_MA1_CLK_H14,8

C227

1.5pF 0402

MEM_MA1_CLK_L14,8

MEM_MA1_CLK_H04,8

C247

1.5pF 0402

MEM_MA1_CLK_L04,8

MEM_MB1_CLK_H24,8

C226

1.5pF 0402

MEM_MB1_CLK_L24,8

MEM_MB1_CLK_H14,8

C230

1.5pF 0402

MEM_MB1_CLK_L14,8

MEM_MB1_CLK_H04,8

C248

1.5pF 0402

MEM_MB1_CLK_L04,8

VTT_DDR

Layout: Spread out on VTT pour

C202

0.1uF

C203

0.1uF

0.1uF

C334

0.1uF

C346

C350

0.1uF

0.1uF

A A

5

C336

C352

0.1uF

C344

0.1uF

4

C341

0.1uF

C340

0.1uF

C338

0.1uF

C351

0.1uF

C345

0.1uF

C348

0.1uF

C343

0.1uF

C339

0.1uF

Title

EPoX

Size Document Number Rev

Date: Sheet of

3

2

Monday, August 28, 2006

DDR VTT

AF570+Ultra

1

1.0

933

Page 10

A

B

C

D

E

HT_DWN-[15..0]3

U16A

BGA776-MCP55

HT_DWN0

4 4

3 3

HT_DWNCLK03

HT_DWNCLK0-3

HT_DWNCLK13

HT_DWNCLK1-3

HT_DWNCNTL3

HT_DWNCNTL-3

R266 150 1%

R267 49.9 1%

THERMTRIP-5

2 2

+3_3V

LB2 BEAD 60(B)

C321

0.1uF

3.3V_PLL_CPU

CB37

4.7uF 0805(B)0.01uF(B)

HT_DWN1

HT_DWN2

HT_DWN3

HT_DWN4

HT_DWN5

HT_DWN6

HT_DWN7

HT_DWN8

HT_DWN9

HT_DWN10

HT_DWN11

HT_DWN12

HT_DWN13

HT_DWN14

HT_DWN15

HT_DWN-0

HT_DWN-1

HT_DWN-2

HT_DWN-3

HT_DWN-4

HT_DWN-5

HT_DWN-6

HT_DWN-7

HT_DWN-8

HT_DWN-9

HT_DWN-10

HT_DWN-11

HT_DWN-12

HT_DWN-13

HT_DWN-14

HT_DWN-15

HT_DWNCLK0

HT_DWNCLK0HT_DWNCLK1

HT_DWNCLK1-

HT_DWNCNTL

HT_DWNCNTL-

HT_MCP_COMP_GND1

HT_MCP_COMP_GND2

THERMTRIP-

+3_3V

CB35

VCC1_5

AK32

AJ32

AH32

AH30

AF31

AE32

AD32

AD30

AG27

AF27

AD26

AE29

AB23

AB26

AB28

AA28

AK31

AJ31

AH31

AH29

AF30

AE31

AD31

AD29

AG28

AF28

AD25

AE28

AB24

AB25

AB27

AA29

AG30

AG29

AD27

AD28

AC30

AC29

AG26

AG25

AJ29

P23

AC21

AC22

AC23

HT_MCP_RXD0_P

HT_MCP_RXD1_P

HT_MCP_RXD2_P

HT_MCP_RXD3_P

HT_MCP_RXD4_P

HT_MCP_RXD5_P

HT_MCP_RXD6_P

HT_MCP_RXD7_P

HT_MCP_RXD8_P

HT_MCP_RXD9_P

HT_MCP_RXD10_P

HT_MCP_RXD11_P

HT_MCP_RXD12_P

HT_MCP_RXD13_P

HT_MCP_RXD14_P

HT_MCP_RXD15_P

HT_MCP_RXD0_N

HT_MCP_RXD1_N

HT_MCP_RXD2_N

HT_MCP_RXD3_N

HT_MCP_RXD4_N

HT_MCP_RXD5_N

HT_MCP_RXD6_N

HT_MCP_RXD7_N

HT_MCP_RXD8_N

HT_MCP_RXD9_N

HT_MCP_RXD10_N

HT_MCP_RXD11_N

HT_MCP_RXD12_N

HT_MCP_RXD13_N

HT_MCP_RXD14_N

HT_MCP_RXD15_N

HT_MCP_RX_CLK0_P

HT_MCP_RX_CLK0_N

HT_MCP_RX_CLK1_P

HT_MCP_RX_CLK1_N

HT_MCP_RXCTL_P

HT_MCP_RXCTL_N

HT_MCP_COMP_GND1

HT_MCP_COMP_GND2

THERMTRIP/GPIO*

+1.5V_PLL_CPU_HT

+3.3V_HT

+3.3V_PLL_CPU

+3.3V_PLL_HT

?

MCP55

SEC 1 OF 9

HT_MCP_TXD0_P

HT_MCP_TXD1_P

HT_MCP_TXD2_P

HT_MCP_TXD3_P

HT_MCP_TXD4_P

HT_MCP_TXD5_P

HT_MCP_TXD6_P

HT_MCP_TXD7_P

HT_MCP_TXD8_P

HT_MCP_TXD9_P

HT_MCP_TXD10_P

HT_MCP_TXD11_P

HT_MCP_TXD12_P

HT_MCP_TXD13_P

HT_MCP_TXD14_P

HT_MCP_TXD15_P

HT_MCP_TXD0_N

HT_MCP_TXD1_N

HT_MCP_TXD2_N

HT_MCP_TXD3_N

HT_MCP_TXD4_N

HT_MCP_TXD5_N

HT_MCP_TXD6_N

HT_MCP_TXD7_N

HT_MCP_TXD8_N

HT_MCP_TXD9_N

HT_MCP_TXD10_N

HT_MCP_TXD11_N

HT_MCP_TXD12_N

HT_MCP_TXD13_N

HT_MCP_TXD14_N

HT_MCP_TXD15_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_TX_CLK1_P

HT_MCP_TX_CLK1_N

HT_MCP_TXCTL_P

HT_MCP_TXCTL_N

HT_MCP_REQ*

HT_MCP_STOP*

HT_MCP_RST*

HT_MCP_PWRGD

CLKOUT0_CLKIN_200MHZ_P

CLKOUT0_CLKIN_200MHZ_N

CLKOUT1_200MHZ_P

CLKOUT1_200MHZ_N

CLKOUT2_200MHZ_P

CLKOUT2_200MHZ_N

HT_VREF

CLKOUT_25MHZ

CLK200_TERM_GND

R29

T29

T31

U31

W29

Y29

Y31