Page 1

TRADEMARK

All products and company names are trademarks or registered

trademarks of their respective holders.

These specifications are subject to change without notice.

Manual Revision 1.0

December 20, 1999

EP-3VBM+EP-3VBM+

EP-3VBM+EP-3VBM+

EP-3VBM+

A SocA Soc

A SocA Soc

A Soc

kk

kk

k

et 370 Pret 370 Pr

et 370 Pret 370 Pr

et 370 Pr

ocessor basedocessor based

ocessor basedocessor based

ocessor based

AA

AA

A

GP MainboarGP Mainboar

GP MainboarGP Mainboar

GP Mainboar

d (133/100/66MHz)d (133/100/66MHz)

d (133/100/66MHz)d (133/100/66MHz)

d (133/100/66MHz)

Page 2

EP-3VBM+

User Notice

No part of this product, including the product and software may be reproduced,

transmitted, transcribed, stored in a retrieval system, or translated into any language in

any form without the express written permission of EPoX Computer Company

(hereinafter referred to as EPoX) except for documentation kept by the purchaser for

backup purposes.

We provide this manual “as is” without warranty of any kind, either expressed or

implied, including but not limited to the implied warranties or conditions of merchantability or fitness for a particular purpose. In no event shall EPoX be liable for any loss

of profits, loss of business, loss of use or data, interruption of business or for indirect,

special incidental, or consequential damages of any kind, even if EPoX has been advised

of the possibility of such damages arising from any defect or error in the manual or

product. EPoX may revise this manual from time to time without notice. For updated

BIOS, drivers, or product release information you may visit our websites at http://www.

epox.com or http://www.epox.com.tw.

Products mentioned in this manual are mentioned for identification purposes only.

Product names appearing in this manual may or may not be registered trademarks or

copyrights of their respective companies. The product name and revision number

are both printed on the mainboard itself.

Handling Procedures

Static electricity can severely damage your equipment. Handle the EP-3VBM+ and any

other device in your system with extreme care and avoid unnecessary contact with

system components on the mainboard. Always work on an antistatic surface to avoid

possible damage to the mainboard from static discharge. Always have the power supply

unplugged and powered off when inserting and removing devices within the computer

chassis. EPoX assumes no responsibility for any damage to the EP-3VBM+ mainboard

that results from failure to follow instruction or failure to observe safety precautions.

CAUTION

The EP-3VBM+ mainboard is subject to

damage by static electricity. Always

observe the handling procedures.

Page 3

EP-3VBM+

Technical Support Services

If you need additional information, help during installation or normal use of this

product, please contact your retailer. Your retailer will have the most current information about your configuration. If your retailer cannot help, you may visit our online

technical support website and/or contact our support technicians at the locations listed

below.

Record your serial number before installing your EP-3VBM+ mainboard. (The serial

number is located near the ISA slots at the edge of the board.)

EP-3VBM+ serial number: _________________________________

Contacting Technical Support

EPoX technical support is working hard to answer all of your questions online. From

our website you can find answers to many common questions, drivers, BIOS updates,

tech notes, and important technical bulletins. If you are still unable to locate the

solution you are seeking, you always have the option to contact our support technicians

directly.

North American website (English language)

http://www.epox.com

sales@epox.com

support@epox.com

European website (Multi-language)

http://www.epox.nl

sales@epox.nl

support@epox.nl

Taiwan website (Chinese language)

http://www.epox.com.tw

sales@epox.com.tw

support@epox.com.tw

Thank you for using EPoX mainboards!

Copyright 1999 EPoX Computer Company. All rights reserved.

Page 4

EP-3VBM+

T able of Contents

Section 1 Introduction

Components Checklist ....................................... 1-1

Overview

EP-3VBM+ Form-factor.................................... 1-2

I/O Shield Connector......................................... 1-3

Power-On/Off (Remote).................................... 1-3

System Block Diagram ...................................... 1-4

Section 2 Features

EP-3VBM+ Features ......................................... 2-1

Section 3 Installation

EP-3VBM+ Detailed Layout ............................. 3-1

Easy Installation Procedure

CPU Insertion .................................................... 3-3

Jumper Settings.................................................. 3-5

System Memory Configuration .......................... 3-6

Device Connectors ............................................ 3-9

External Modem Ring-in Power On and

Keyboard Power On Function (KBPO) ............. 3-1 1

Section 4 Award BIOS Setup

BIOS Instructions .............................................. 4-1

Standard CMOS Setup....................................... 4-2

BIOS Features Setup ......................................... 4-3

Chipset Features Setup ...................................... 4-8

Power Management Setup ................................. 4-11

PNP/PCI Configuration ..................................... 4-15

Load Setup Defaults .......................................... 4-17

Integrated Peripherals........................................ 4-17

Page 5

EP-3VBM+

Sensor and CPU Speed Setup ............................ 4-22

Change Supervisor or User Password ............... 4-24

IDE HDD Auto Detection.................................. 4-25

Save & Exit Setup ............................................. 4-27

Exit Without Saving........................................... 4-27

Section 5 Appendix

Appendix A

Memory Map ..................................................... A-1

I/O Map ............................................................. A-1

Timer & DMA Channels Map ........................... A-2

Interrupt Map..................................................... A-2

R TC & CMOS RAM Map................................. A-3

Appendix B

POST Codes...................................................... A-4

Unexpected Errors............................................. A-7

Appendix C

Load Setup Defaults .......................................... A-9

Appendix D

GHOST 5.1 Quick User’s Guide ....................... A-11

Page 6

EP-3VBM+

Page Left Blank

Page 7

Introduction

EP-3VBM+

Page 1-1

Section 1

INTRODUCTION

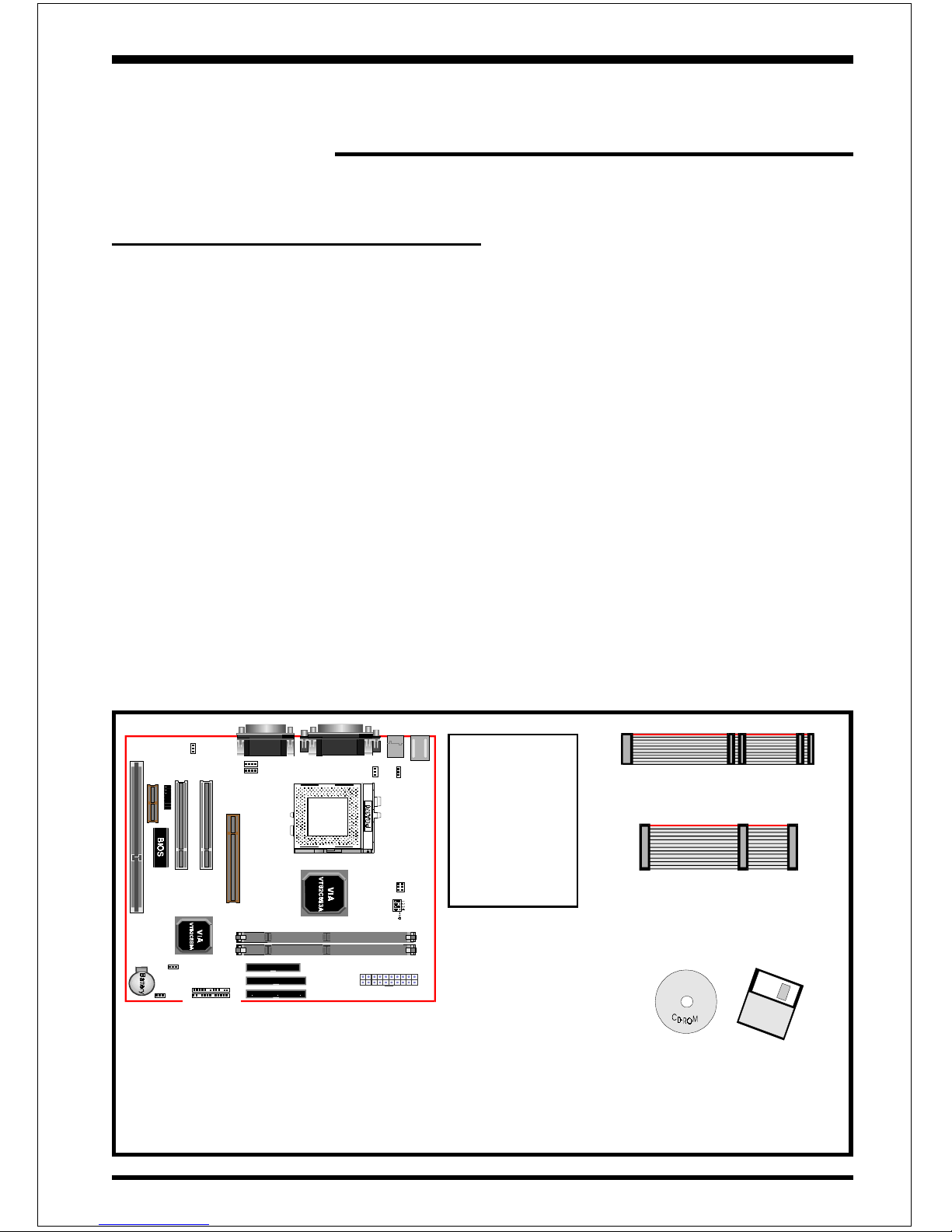

Components Checklist

üü

üü

ü A. (1) EP-3VBM+ mainboard

üü

üü

ü B. (1) EP-3VBM+ user’s manual

üü

üü

ü C. (1) Floppy drive ribbon cable

üü

üü

ü D. (1) Hard drive ribbon cable

üü

üü

ü E. (1) Driver and utility

USER’S

MANUAL

EP-3VBM+

B

A

C

D

E

Page 8

Introduction

EP-3VBM+

Page 1-2

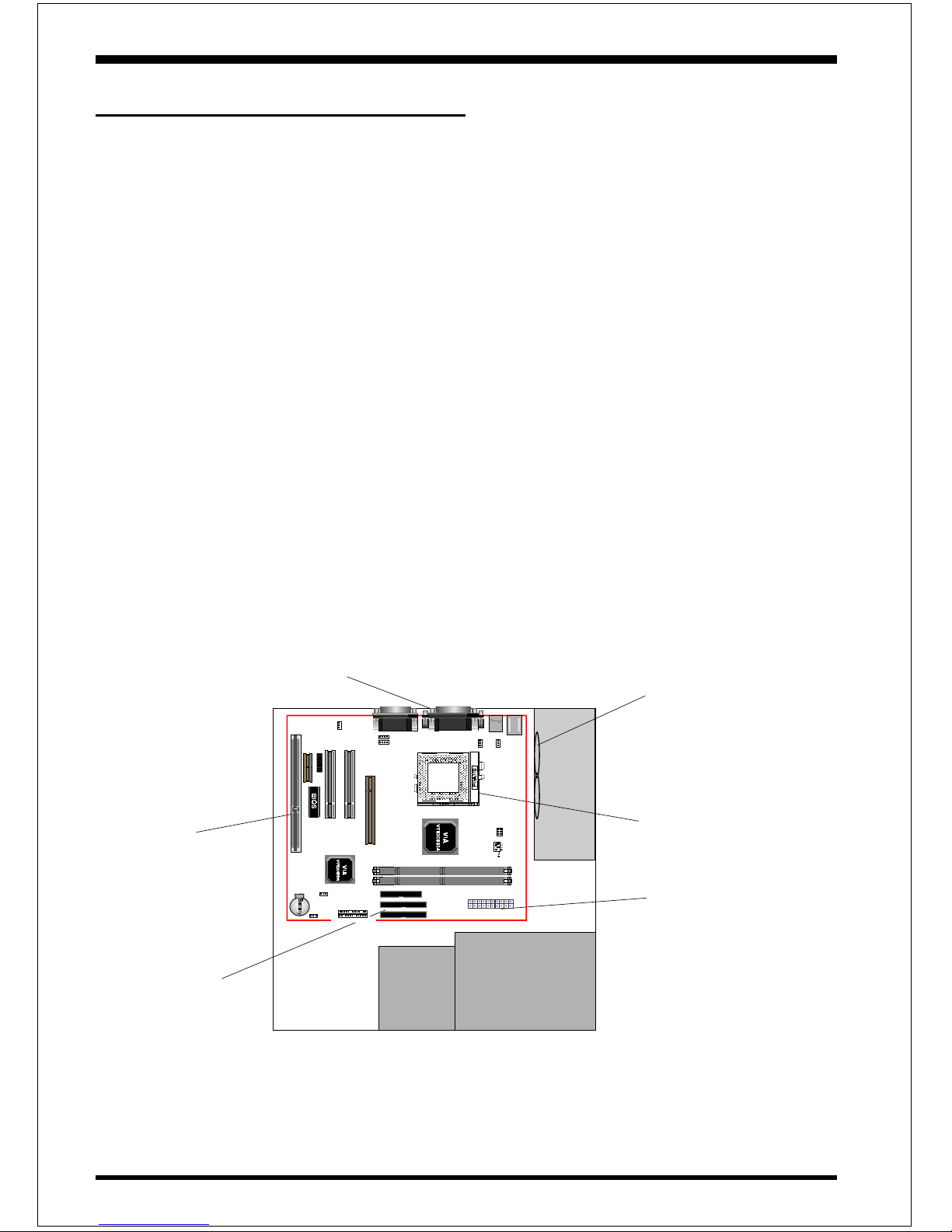

EP-3VBM+ Form-Factor

The EP-3VBM+ is designed with Micro-ATX form factor - the new industry

standard of chassis. The Micro-ATX form factor is essentially a Baby-AT

baseboard rotated 90 degrees within the chassis enclosure and a new mounting

configuration for the power supply . With these changes the processor is relocated

away from the expansion slots, allowing them all to hold full length add-in cards.

Micro-ATX defines a double height aperture to the rear of the chassis which can

be used to host a wide range of onboard I/O. Only the size and position of this

aperture is defined, allowing PC manufacturers to add new I/O features (e.g.; TV

input, TV output, modem, LAN, etc.) to systems. This will help systems integrators differentiate their products in the marketplace, and better meet your needs.

• Smaller size promotes a smaller system size.

• I/O shield does not need to be retooled in an ATX 2.01 or later.

The

mainboard should be used in an ATX 2.01 (or later) compliant case.

• A smaller power supply cam be used. High integration on mainboard reduces

the system costs.

Full length

slots

Expandable I/O

5 1/4"

Bay

3 1/2"

Bay

Figure 1: Summary of MicroATX chassis features

CPU located near

Power Supply

Single chassis

fan for

system

MicroATX

Power

Supply

ATX power

connector

Floppy / IDE

connectors

close to

peripheral

bays

Page 9

Introduction

EP-3VBM+

Page 1-3

ATX

POWER SUPPLY

Power-On/Off (Remote)

The EP-3VBM+ has a single 20-pin connector for ATX power supplies. For ATX

power supplies that support the Remote On/Off feature, this should be connected

to the systems front panel for system Power On/Off button. The systems power

On/Off button should be a momentary button that is normally open.

The EP-3VBM+ has been designed with “Soft Off" functions. You can turn Off

the system from one of two sources: The first is the front panel Power On/Off

button, and the other is the "Soft Off" function (coming from the EP-3VBM+’s

onboard circuit controller) that can be controlled by the operating system. Windows 95/98 will control this when the user clicks that they are ready to Shutdown

the system.

Figure 3: Simple ATX Power ON/OFF Controller

Case (chassis) Power

ON/OFF button (J 3)

J 3

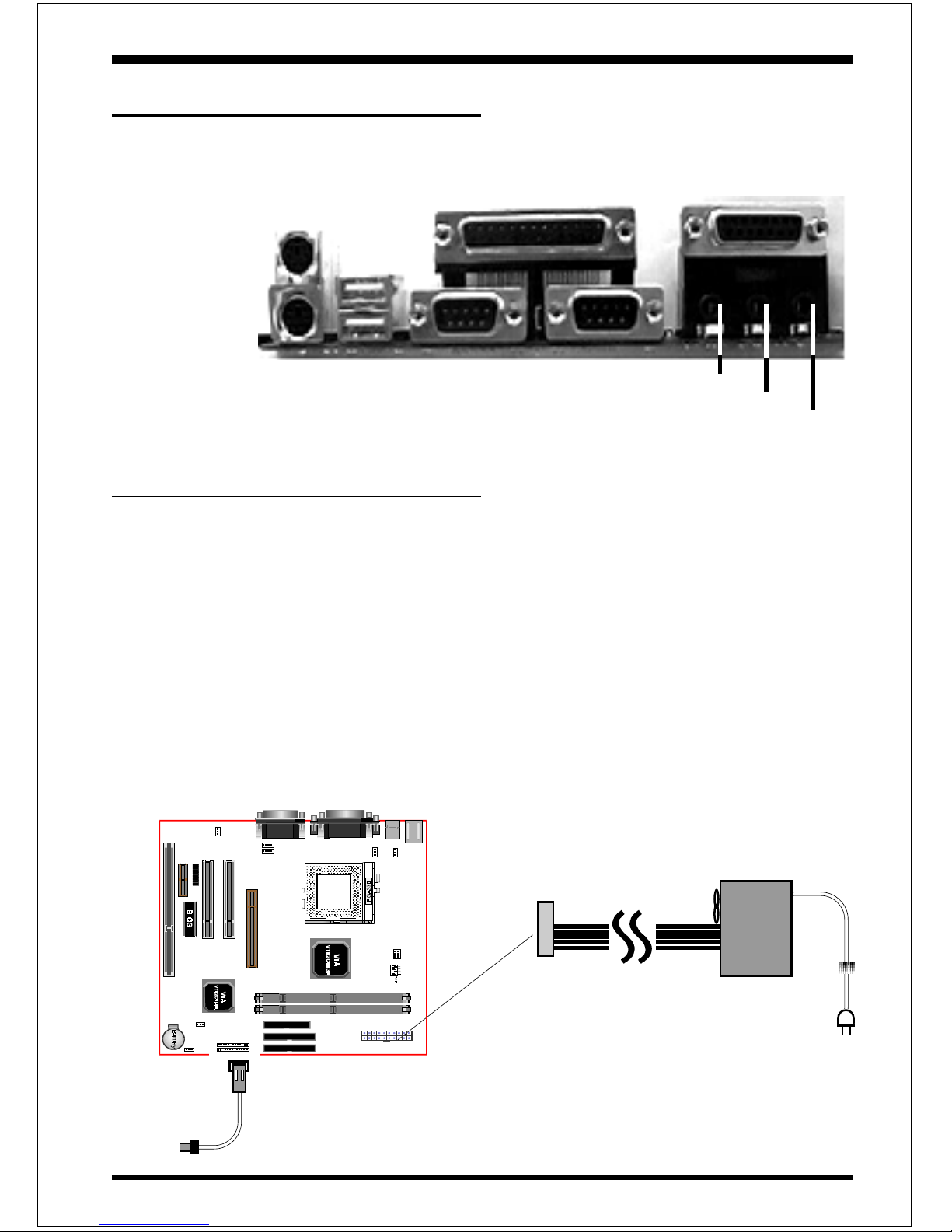

I/O Shield Connector

The EP-3VBM+ is equipped with an I/O back panel. Please use the appropriate

I/O shield (figure 2).

PS/2 Mouse

PS/2

KEYBOARD

USB port

COM1 COM2

parallel port

Speaker

Line_in

MIC

Figure 2: I/O back panel layout

Joystick/Midi port

Page 10

Introduction

EP-3VBM+

Page 1-4

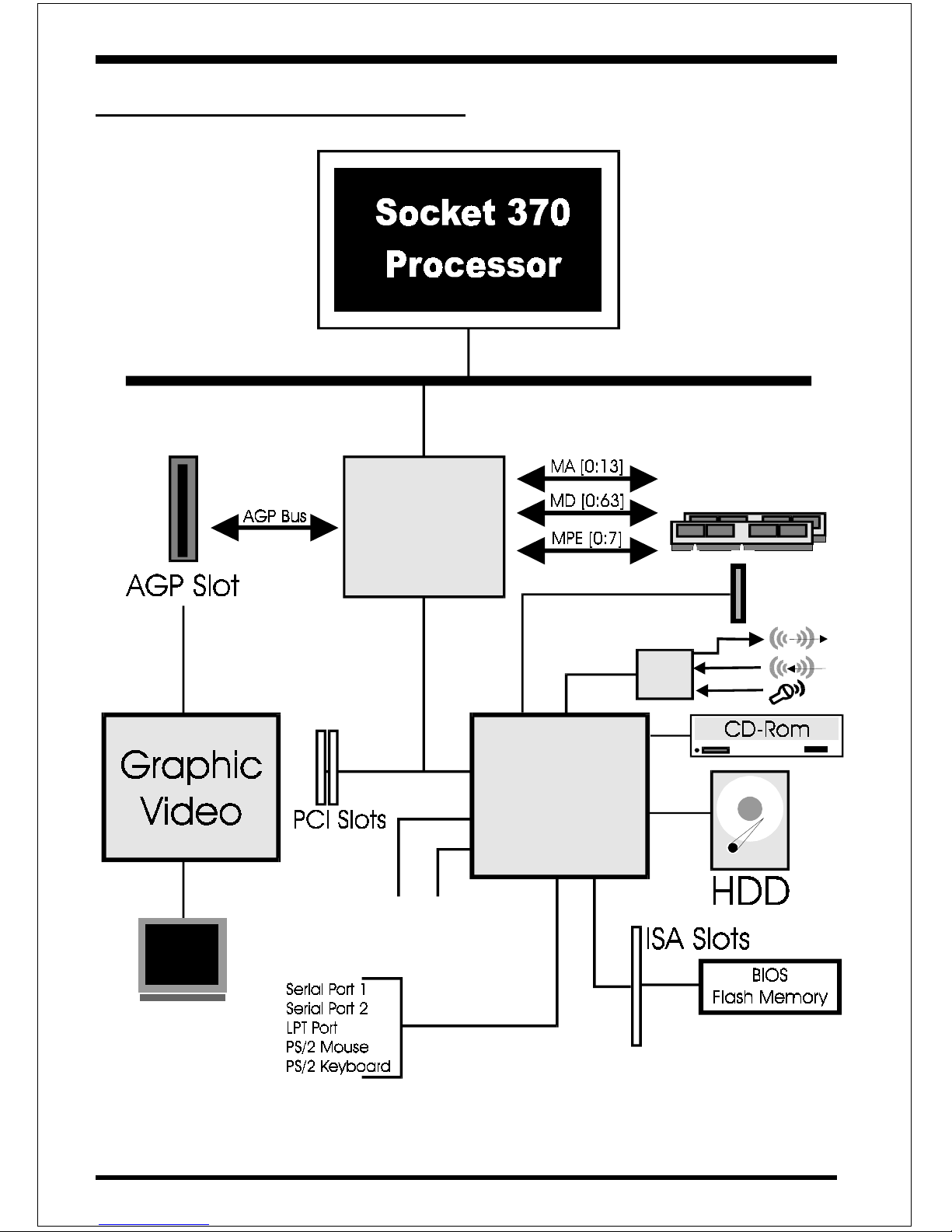

Figure 4: System Block Diagram

System Block Diagram

PAC

PCI Bridge

and mem ory

controller

VT82C693A

VT82C6 86 A

I/O Bridge

100/66MHz

133/100/66MHz

66MHz

AC

97

USB 0,1 USB 2,3

AMR Slot

Page 11

FeaturesEP-3VBM+

Page 2-1

Section 2

FEA TURES

EP-3VBM+ Fea tures:

• EP-3VBM+ is based on the Socket 370 Processors including PCGA & FC-

PGA operating at 500 ~700MHz. The board is configured by an ESSJ

(Easy-Setting-Single-Jumper) to match your CPU clock speed.

• Designed with VIA Apollo Pro PCIset.

• Supports up to 512MB of DRAM (minimum of 8 MB) on board (please

see Section 3-2).

• EP-3VBM+ will support Error Checking and Correcting (ECC) when using

parity SDRAM memory modules. This will detect multiple bit errors and

correct 1-bit memory errors.

• Supports (1) 16 bit ISA slots, (2) 32 bit PCI slots, (1) AGP slot, (1) AMR

slot and provides (2) independent high performance PCI IDE interfaces

capable of supporting PIO Mode 3/4 and Ultra DMA 33/66 devices.

The EP-3VBM+ supports (2) PCI Bus Master slots and a jumperless PCI

INT# control scheme which reduces configuration confusion when plugging

in PCI card(s).

• Supports AT API (e.g. CD-ROM) devices on both Primary and Secondary

IDE interfaces.

• Designed with on chip Multi I/O: (1) floppy port, (1) parallel port (EPP,

ECP), and (2) serial ports (16550 Fast UART).

Note: Japanese “Floppy 3 mode” is also supported

• Features Award Plug & Play BIOS. W ith Flash Memory you can always

upgrade to the current BIOS as they are released. (http://www.epox.com/

please visit our T echnical Support section for the latest updates).

• EP-3VBM+ utilizes a Lithium battery which provides environmental protec

tion and longer battery life.

Page 12

Features

EP-3VBM+

Page 2-2

• Supports the (4) Universal Serial Bus (USB) Ports. The onboard

VT82C686A chip provides the means for connecting PC peripherals such

as; keyboards, joysticks, telephones, and modems.

• Built-in ATX 20-pin power supply connector.

• Software power-down when using Windows

®

95/98.

• Supports ring-in feature (remote power-on through external modem,

allows system to be turned on remotely).

• Resume by Alarm - Allows your system to turn on at a preselected time.

• Power Loss Recovery - In the event of a power outtage your system will

automatically turn itself back on without user intervention.

• Supports CPU Hardware sleep and SMM (System Management Mode).

• Supports Keyboard power ON function (KBPO).

• Built-in WOL (W ake-up On Lan) Connector.

• Built-in AC97 PCI Audio.

Page 13

Installation

EP-3VBM+

Page 3-1

Section 3

INSTALLATION

Page 14

Installation

EP-3VBM+

Page 3-2

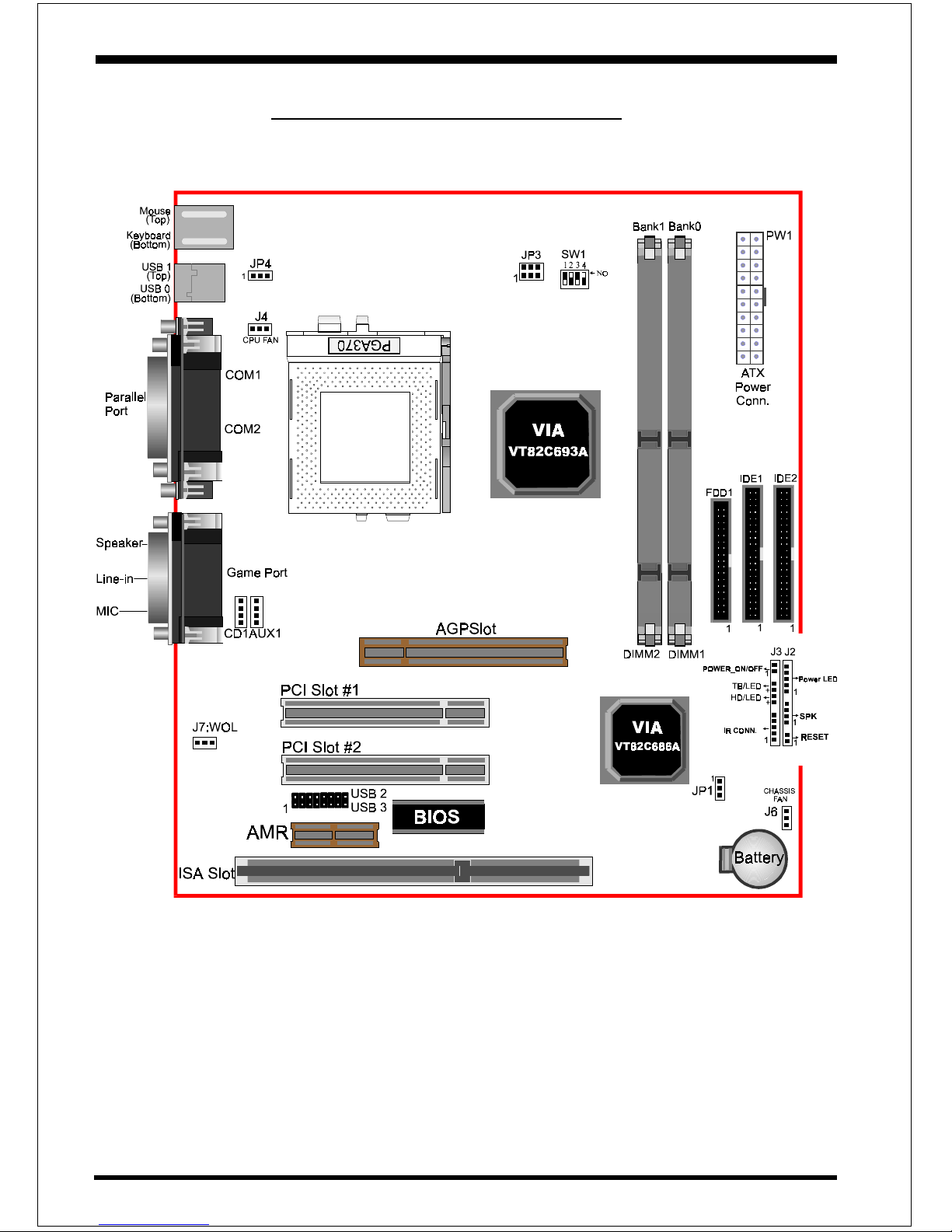

EP-3VBM+ Detailed Layout

Figure 1

Page 15

Installation

EP-3VBM+

Page 3-3

Easy Installation Procedure

The EP-3VBM+ is designed for all Socket 370 processors, such as Intel FC-PGA 370

CuMine (Coppermine) 128K/256K processors which are based on 0.18 micro process

technology and utilizing the AGTL+ bus architecture at 100 and 133MHz.

The EP-3VBM+ has the very few jumpers on board, making your installation faster and

easier. In despite of user friendly design, the EP-3VBM+ offers the flexible FSB

selection, being capable of running speedy FSB at 133MHz for Intel PIII CuMine CPU

& upcoming new Cyrix Socket 370 processors.

Before you get started, please read the following quick installation guide with careful.

Easy Installation Procedure

The following must be completed before powering on your new system:

3-1. CPU Insertion

3-2. Jumper Settings

3-3. System memory Configuration

3-4. Device Connectors

3-5 External Modem Ring-in Power ON and Keyboard Power ON

Functions (KBPO)

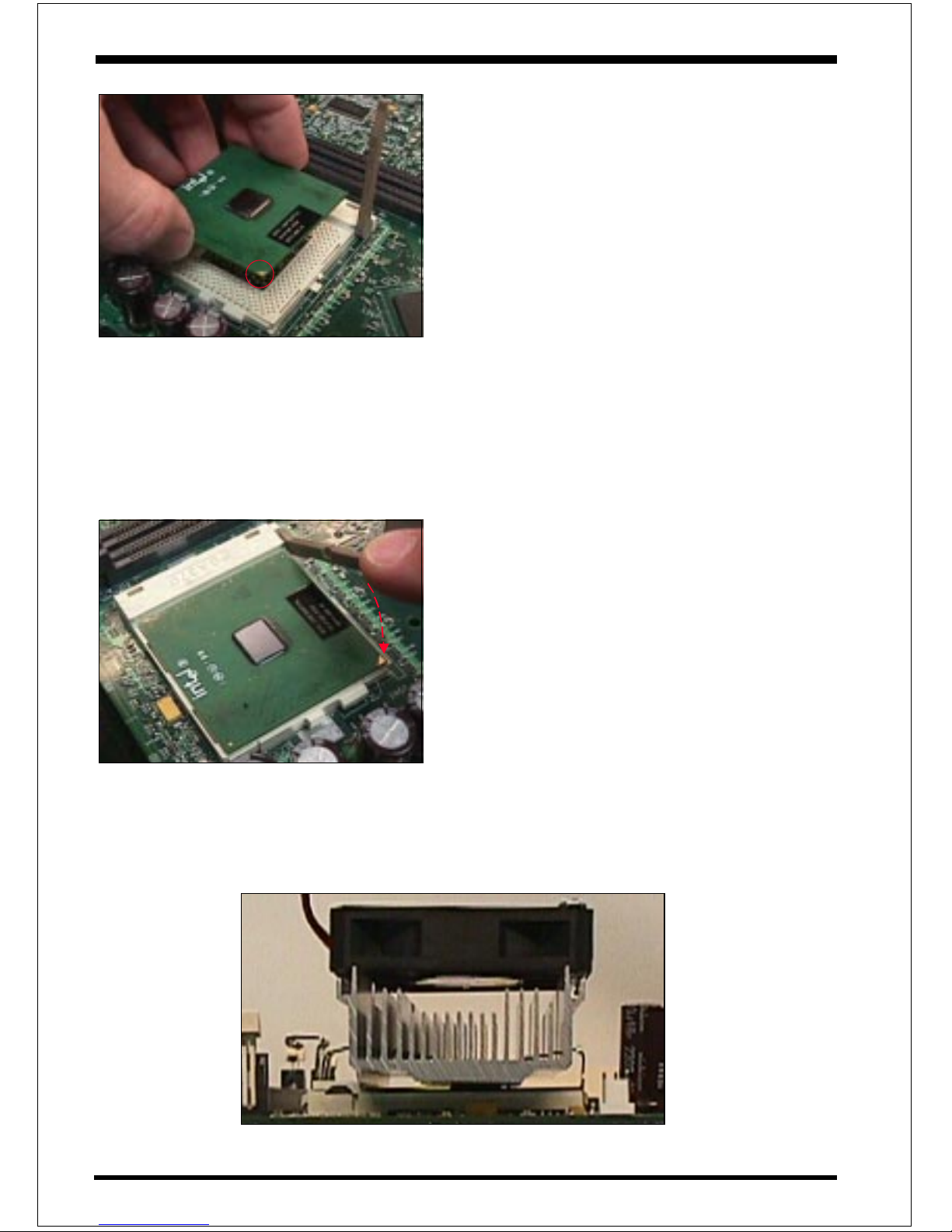

Section 3-1

CPU Insertion

CPU Insertion: (use CuMineTM for reference)

Step 1

Open the socket by raising the actuation

lever.

Figure 2

Page 16

Installation

EP-3VBM+

Page 3-4

Step 2

Insert the processor.

Ensure proper pin 1 orientation by aligning

the FC-PGA corner marking with the socket

corner closest to the actuation arm tip. The

pin field is keyed to prevent mis-oriented

insertion.

Don’t force processor into socket. If it does not

go in easily, check for mis-orientation and

debris.

Make sure the processor is fully inserted into

the socket on all sides.

Step 3

Close the socket by lowering and locking the

actuation lever.

Note: Intel’s reference design thermal solution is an active heatsink; an extruded alumi-

num heatsink based and a fan attached to the top on the fin array. (See Figure 5)

Figure 3

Figure 4

Figure 5

Page 17

Installation

EP-3VBM+

Page 3-5

*reserved

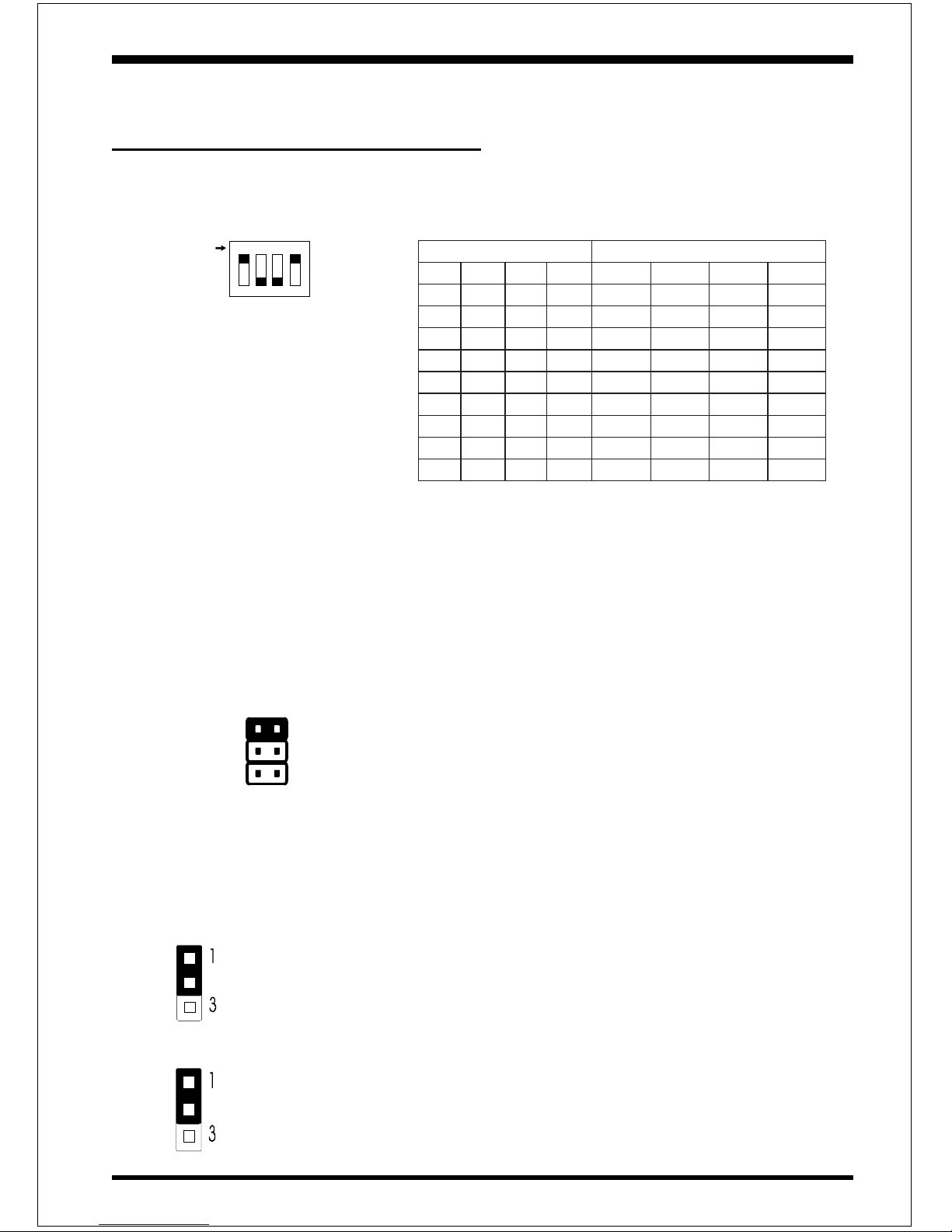

SW1: CPU Mutiple Frequency Selection

Section 3-2

Jumper Settings

JP3: CPU FSB Selection

The FSB can be 66, 100 and 133MHz

100MHz

66MHz (Default)

133MHz

1

4

3

6

The CPU frequency with “*” is reserved for future

CPU use and hasn’t been approved and tested yet at

this moment.

Ps: 66MHz for Celeron

TM

Processor

100/133MHz for CuMineTM (FC-PGA370)/128K/256K Processor

Joshua processor *

1234

ON

1WS)zHM(UPC

1234 oitaRzHM66zHM001zHM331

NONONOX4662004335

NONOX5.4003054006

NONOX5333005766*

NOX5.5663055337*

NONONOX6004006008*

NONOX5.6334056768*

NONOX7664007

NOX5.7005*057*

NONOX8335*008*

JP1 C lear CO MS

1-2 : Run M ode(default)

2-3 : Clear C MO S

JP4 K eyboard Pow er-ON F unction Selection

1-2 : D isabled

2-3 : Enabled

Page 18

Installation

EP-3VBM+

Page 3-6

Section 3-3

System Memory Configuration

Memory Layout

The EP-3VBM+ supports (2) 168-pin DIMMs (Dual In-line Memory Module).

The DIMMs can be either EDO (Enhanced Data Out) or SDRAM

(Synchronized DRAM).

• DIMM SDRAM may be 83MHz (12ns), 100MHz (10ns) or

125MHz (8ns) bus speed.

• If you use both 50ns and 60ns memory you must configure

your BIOS to read 60ns.

• When using Synchronous DRAM we recommend using the

4 clock variety over the 2 clock.

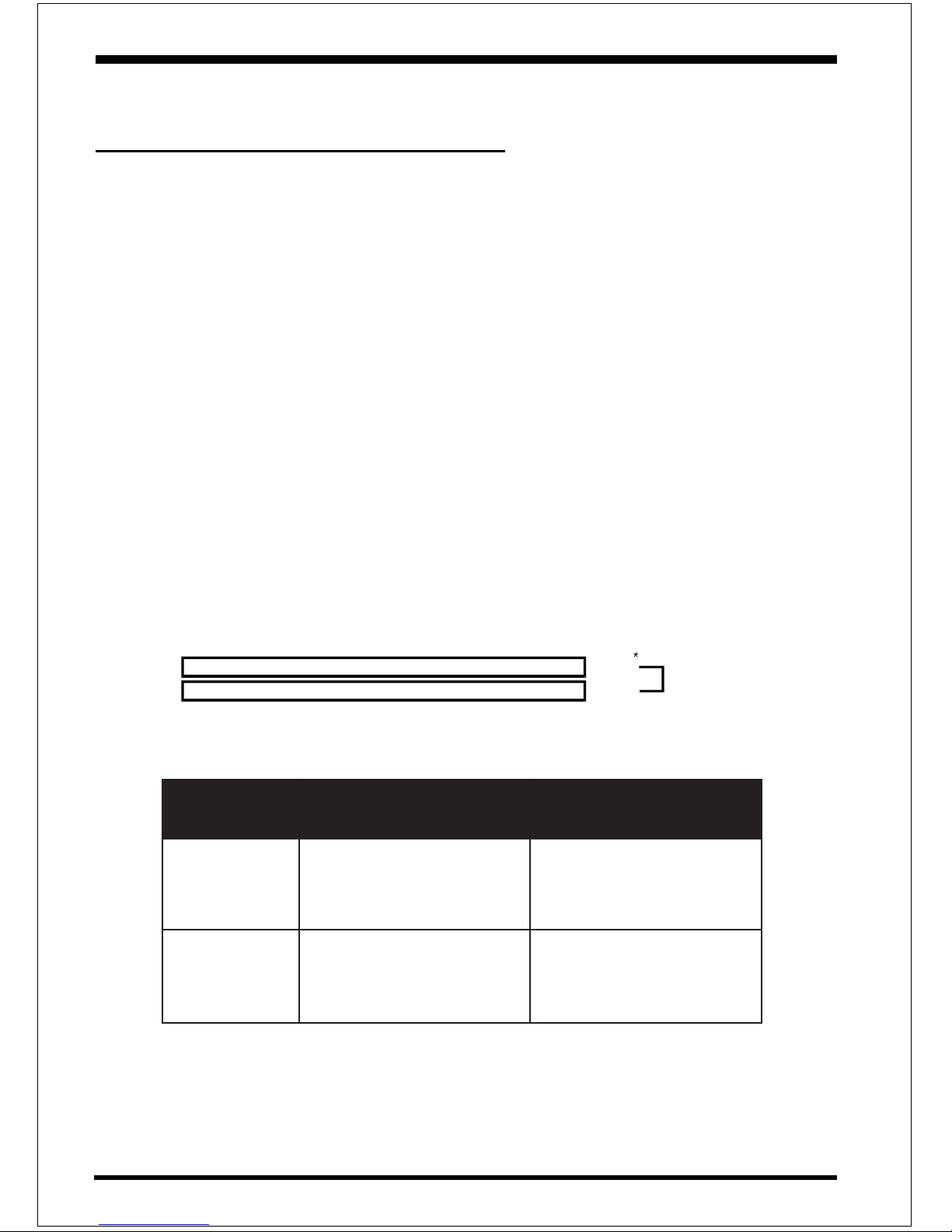

Figure 6 and Table 1 show several possible memory configurations using both

SIMM and DIMM.

* SDRAM only supports 8, 16, 32, 64, 128, 256MB DIMM modules.

Table 1

Figure 6

DIMM 1

DIMM 2

Bank 0

Bank 1

-Synchronous

-E DO

yromeMlatoT

1MMID

)0knaB(

2MMID

)1knaB(

BM652=

mumixaM

*MARDS/ODE

,BM46,BM23,BM61,BM8

1XBM652,BM821

enoN

BM215=

mumixaM

*MARDS/ODE

,BM46,BM23,BM61,BM8

1XBM652,BM821

*MARDS/ODE

,BM46,BM23,BM61,BM8

1XBM652,BM821

Page 19

Installation

EP-3VBM+

Page 3-7

DIMM Module Installation

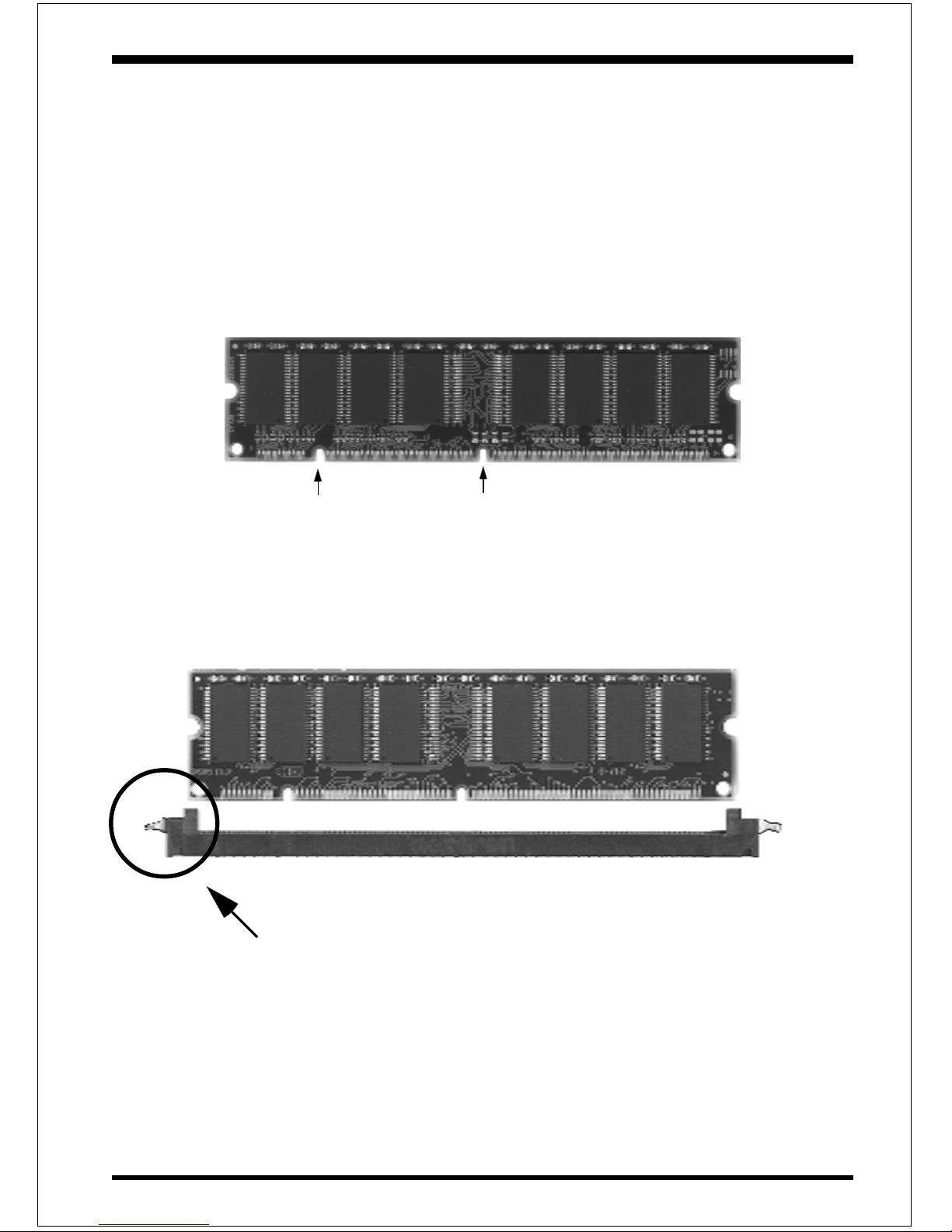

Figure 7 displays the notch marks and what they should look like on your

DIMM memory module.

DIMMs have 168-pins and two notches that will match with the onboard DIMM

socket. DIMM modules are installed by placing the chip firmly into the socket

at a 90 degree angle and pressing straight down (figure 8) until it fits tightly into

the DIMM socket (figure 9).

Figure 7

Figure 8

DIMM Module clip before installation

LEFT KEY ZONE

(UNBUFFERED)

CENTER KEY ZONE

(3.3 V DRAM)

Page 20

Installation

EP-3VBM+

Page 3-8

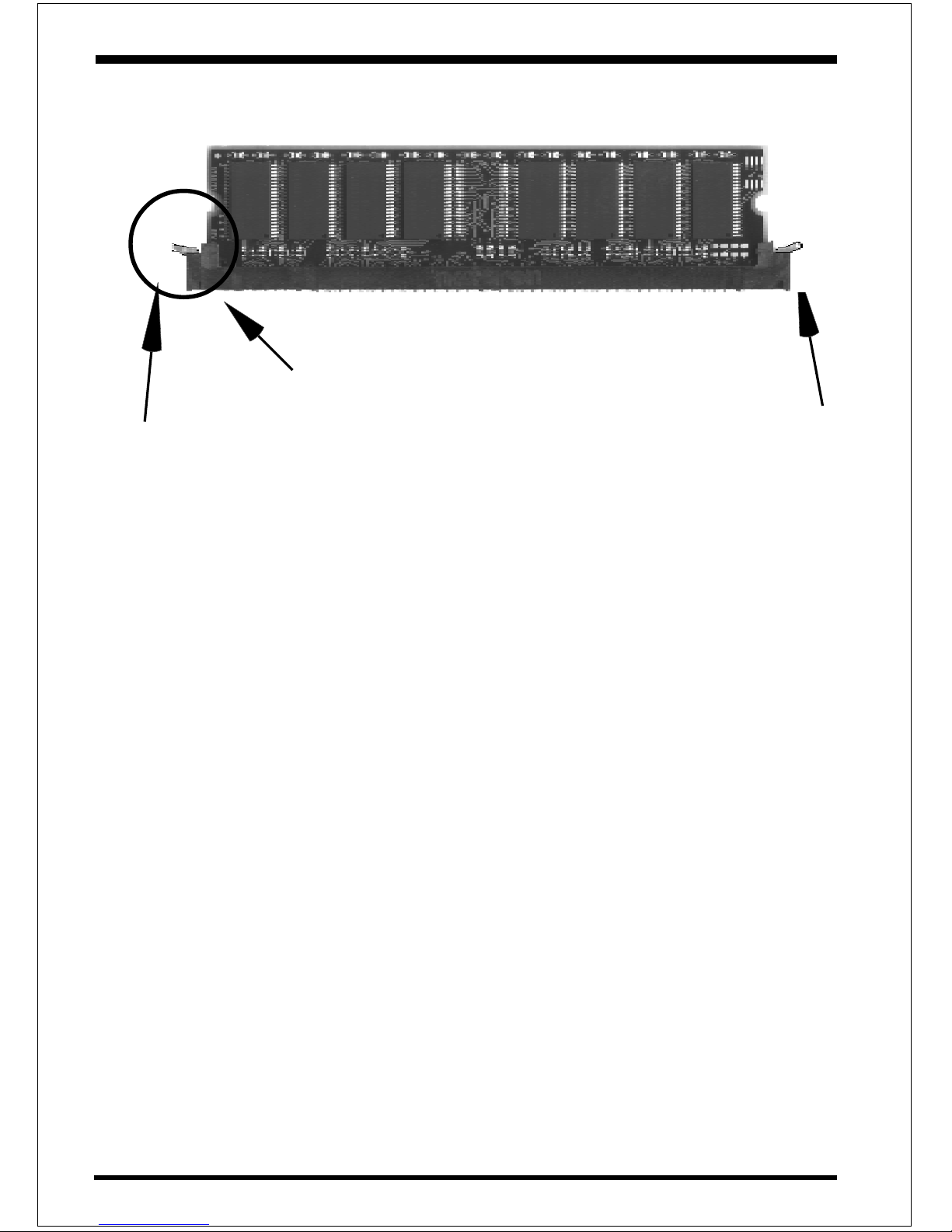

Figure 9

DIMM Module clip after installation

To remove the DIMM module simply press down both of the white clips on either

side and the module will be released from the socket.

Page 21

Installation

EP-3VBM+

Page 3-9

Section 3-4

Device Connectors

Please install the motherboard into the chassis.

Now that your motherboard is installed you are ready to connect all your

connections (figure 10).

J2: Chassis Panel Connector

• Power LED, Speaker, Reset

J3: Turbo LED, HDD LED, IR Conn., Sleep/Power_ON

J4: CPU Fan Power

• A plug-in for the CPU Fan Power

J6: Chassis Fan Power

• A plug-in for the chassis Fan Power

J7: WOL Connector

IDE1: Primary IDE

IDE2: Secondary IDE

FDD1:Floppy Controller Connector

PW1: ATX Power Connector

• 20-pin power connector

CD1: CD Audio Connector

AUX1:AUX Audio Connector

USB Conn.: The third and fourth USB port (Cable optional)

Figure 10

PS/2 Mouse

PS/2

KEYBOARD

USB port

COM1 COM2

parallel port

Speaker

Line_in

MIC

Joystic/Midi port

Page 22

Installation

EP-3VBM+

Page 3-10

Device Connectors (continued)

J2

Speaker - Connect to the system's speaker for beeping

1. Speaker 3. GND

2. N/C 4. GND

Reset - Closed to restart system.

Power LED - Power LED connector

1. Power LED(+) 4. NC

2. N/C 5. GND

3. GND

1

1

1

(This is connected to the power button on the case. Using the

Soft-Off by Pwr-BTTN feature, you can choose either Instant

Off (turns system off immediatly), or 4 sec delay (you need to

hold the button down for 4 seconds before the system turns off).

When the system is in 4 sec delay mode, there is a special

feature to make the system to go into suspend mode when the

button is pressed momentarily.)

Turbo LED indicator - LED ON when higher speed is selected

IDE LED indicator - LED ON when Onboard PCI IDE Hard

disks is activate

J3

1

+

+

IR Connector

1. VCC 4. GND

2. NC 5. IRTX

3. IRRX

1

Power On/Off

Page 23

Installation

EP-3VBM+

Page 3-11

Section 3-5

External Modem Ring-in Power

ON and Keyboard Power ON

Functions (KBPO)

On the basis of bounded functions in I/O chipset, the two serial ports are able to

support the External Modem Ring-in Power ON function. Once users connect

the external modem to COM1 or COM2, the EP-3VBM+ mainboard allows

users to turn on their system through the remote and host's dial-up control.

Exclusive Keyboard Power ON Function

To innovate a unique feature to benefit users, we devoted the easiest and most

convenient way to turn on your system based on the the ATX power supply.

How to work with it

Step 1: Please check JP4 at the position 2-3 after you finished the system

installation.

Step 2: You can enjoy the Keyboard Power ON function (KBPO) by pressing

any 2 key and BUTTON only to turn on your system. Your system will

be turned on automatically, after releasing the keys. To power off you

system, you can use the Soft-OFF function under Windows 95.

Notes: Intel ATX version 2.0 specification has recommended you use the

power supply with 0.72A(720mA) in 5.0VSB. With our EP-3VBM+

mainboard, the 5.0VSB standby power only has to be > = 0.2A (200mA)

then you can enjoy this unique benefit. However, the ATX power

supply which is < 0.2 (200mA) is still applicable to your system by

placed JP4 at the position 1-2 to disable this feature.

JP4 K eyboard Pow er-ON F unction Selection

1-2 : D isabled

2-3 : Enabled

(Default)

Page 24

Installation

EP-3VBM+

Page 3-12

Page Left Blank

Page 25

BIOS

EP-3VBM+

Page 4-1

Section 4

AWARD BIOS SETUP

BIOS Instructions

Award’s ROM BIOS provides a built-in Setup program which allows user to

modify the basic system configuration and hardware parameters. The modified

data will be stored in a battery-backed CMOS, so that data will be retained even

when the power is turned off. In general, the information saved in the CMOS

RAM will stay unchanged unless there is a configuration change in the system,

such as hard drive replacement or a device is added.

It is possible for the CMOS battery to fail, this will cause data loss in the CMOS

only. If this does happen you will need to reconfigure your BIOS settings.

To enter the Setup Program :

Power on the computer and press the <Del> key immediately, this will bring you

into the BIOS CMOS SETUP UTILITY.

Figure 1: CMOS Setup Utility

STANDARD CMOS SETUP SENSOR AND CPU SPEED SETUP

BIOS FEATURES SETUP SUPERVISOR PASSWORD

CHIPSET FEATURES SETUP USER PASSWORD

POWER MANAGEMENT SETUP IDE HDD AUTO DETECTION

PNP/PCI CONFIGURATION SAVE & EXIT SETUP

INTEGRATED PERIPHERALS EXIT WITHOUT SAVING

LOAD SETUP DEFAULTS

ROM PCI / ISA BIOS (2A6LGPAA)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC.

ESC : QUIT : SELECT ITEM

F10 : Save & Exit Setup (Shift)F2 : Change Color

Time, Date, Hard Disk Type...

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Page 26

BIOS

EP-3VBM+

Page 4-2

The menu displays all the major selection items. Select the item you need to

reconfigure. The selection is made by moving the cursor (press any direction key )

to the item and pressing the ‘Enter’ key. An on-line help message is displayed at

the bottom of the screen as the cursor is moved to various items which provides a

better understanding of each function. When a selection is made, the menu of the

selected item will appear so that the user can modify associated configuration

parameters.

4-1 Standard CMOS Setup

Choose “Standard CMOS Setup” in the CMOS SETUP UTILITY Menu (Figure

2). The Standard CMOS Setup allows the user to configure system settings such

as the current date and time, type of hard disk drive installed, floppy drive type,

and display type. Memory size is auto-detected by the BIOS and displayed for

your reference. When a field is highlighted (use direction keys to move the cursor

and the <Enter> key to select), the entries in the field can be changed by pressing

the <PgDn> or the <PgUp> key.

Figure 2: Standard CMOS Setup

Note: If the hard disk Primary Master/Slave and Secondary Master/

Slave are set to Auto, then the hard disk size and model will be

auto-detected.

ROM PCI/ISA BIOS(2A6LGPAA)

STANDARD CMOS SETUP

AWARD SOFTWARE, INC.

Date (mm:dd:yy) : Wed, Apr 17 1996

Time (hh:mm:ss) : 14 : 30 : 50

HARD DISKS TYPE SIZE CYLS HEAD PRECOMP LANDZONE SECTORS MODE

Primary Master : Auto 00 0 0 0 0 Auto

Primary Slave : Auto 00 0 0 0 0 Auto

Secondary Master : Auto 00 0 0 0 0 Auto

Secondary Slave : Auto 00 0 0 0 0 Auto

Drive A : 1.44M, 3.5 in.

Drive B : None

Video : EGA/VGA

Halt On : All, But Keyboard

ESC : Quit : Select Item PU/PD/+/- : Modify

F1 : Help (Shift) F2 : Change Color

Base Memory : 640K

Extended Memory : 392192K

Other Memory : 384K

Total Memory : 393216K

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Page 27

BIOS

EP-3VBM+

Page 4-3

Virus Warning : Disabled

CPU Internal Cache : Enabled

External Cache : Enabled

CPU L2 Cache ECC Checking : Disabled

Quick Power On Self Test : Enabled

Boot Sequence : A, C, SCSI

Swap Floppy Drive : Disabled

Boot Up Floppy Seek : Enabled

Boot Up NumLock Status : On

IDE HDD Block Mode : Enabled

Gate A20 option : Fast

Memory Parity/ECC Check : Disabled

Typematic Rate Setting : Disabled

Typematic Rate (Chars/Sec) : 6

Type matic Delay (Msec) : 250

Security Option : Setup

PCI/VGA Palette Snoop : Disabled

OS Select For DRAM > 64MB : Non-OS2

Note: The “Halt On:” field is used to determine when to halt the system

by the BIOS if an error occurs.

Note: Floppy 3 Mode support is a mode used to support a special 3.5”

drive used in Japan. This is a 3.5” disk that stores only 1.2 MB,

the default setting for this is disabled.

4-2 BIOS Features Setup

Selecting the “BIOS FEATURES SETUP” option in the CMOS SETUP UTILITY menu allows users to change system related parameters in the displayed

menu. This menu shows all of the manufacturer’s default values for the EP3VBM+.

Pressing the [F1] key will display a help message for the selected item.

Figure 3: BIOS Features Setup

Virus W arning:

During and after the system boots up, any attempt to write to the boot sector

or partition table of the hard disk drive will halt the system and an error

message will appear.

You should then run an anti-virus program to locate the virus. Keep in mind

that this feature protects only the boot sector, not the entire hard drive.

The default value is Disabled.

ROM PCI/ISA BIOS(2A6LGPAA)

BIOS FEATURES SETUP

AWARD SOFTWARE, INC.

Esc : Quit : Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift) F2 : Color

F7 : Load Setup Defaults

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Video BIOS Shadow : Enabled

C8000-CBFFF Shadow : Disabled

CC000-CFFFF Shadow : Disabled

D0000-D3FFF Shadow : Disabled

D4000-D7FFF Shadow : Disabled

D8000-DBFFF Shadow : Disabled

DC000-DFFFF Shadow : Disabled

Page 28

BIOS

EP-3VBM+

Page 4-4

Enabled: Activates automatically when the system boots up causing a

warning message to appear when anything attempts to access the

boot sector.

Disabled: No warning message will appear when anything attempts to

access the boot sector.

Note: Many disk diagnostic programs that access the boot sector table

can trigger the virus warning message. If you plan to run such a

program, we recommend that you first disable the virus warning.

CPU Internal Cache:

This controls the status of the processor’s internal cache area. The default is

Enabled.

Enabled: This activates the processor’s internal cache thereby increasing

performance.

Disabled: This deactivates the processor’s internal cache thereby lowering

performance.

External (L2) Cache:

This controls the status of the external (L2) cache area.

The default is Enanbled.

Enabled: This activates the motherboard’s L2 cache thereby increasing

performance.

Disabled: This deactivates the motherboard’s L2 cache ther eby lowering

performance.

CPU L2 Cache ECC Checking:

This controls the CPU’ s L2 cache to supports Error Checking and Correcting

(ECC). The default is Disabled

Enabled: Enabled the CPU’s L2 cache to Support ECC function. When

enabled this item the performance should be impact 2% ~4%.

Disabled: Disabled the CPU’s L2 cache to support ECC function.

Quick Power On Self Test:

This category speeds up the Power On Self Test (POST).

The default is Enabled.

Enabled: This setting will shorten or skip of the items checked during POST.

Disabled: Normal POST.

Page 29

BIOS

EP-3VBM+

Page 4-5

Boot Sequence:

This category determines which drive is searched first by the O/S (Operating

System).

The default is A,C,SCSI.

The following is your list of options:

[A, C, SCSI] - [C, A, SCSI] - [C, CD-ROM, A] - [CD-ROM, C, A]

[D, A,CD-ROM],[E, A, CD-ROM] - [F, A, CD-ROM] - [SCSI, A, C]

[SCSI C, A] - [C Only]

Swap Floppy Drive:

This will swap your physical drive letters A & B if you are using two floppy

disks.

The default is Disabled.

Enabled: Floppy A & B will be swapped under the O/S.

Disabled: Floppy A & B will be not swapped.

Boot Up Floppy Seek:

During Power-On-Self-T est (POST), BIOS will determine if the floppy disk

drive installed is 40 or 80 tracks. Only 360K type is 40 tracks while 760K, 1.

2MB and 1.44MB are all 80 tracks.

The default is Enabled.

Enabled: The BIOS will search the floppy disk drive to determine if it is 40

or 80 tracks.

Disabled: The BIOS will not search for the type of floppy disk drive by track

number.

Note: BIOS can not tell the difference between 720K, 1.2MB and 1.

44MB drive types as they are all 80 tracks.

Boot Up NumLock Status:

This controls the state of the NumLock key when the system boots.

The default is On.

On: The keypad acts as a 10-key pad.

Off: The keypad acts like the cursor keys.

Page 30

BIOS

EP-3VBM+

Page 4-6

IDE HDD Block Mode:

IDE Block Mode allows the controller to access blocks of sectors rather than a

single sector at a time.

The default is Enabled.

Enabled: Enabled IDE HDD Block Mode. Provides higher HDD

transfer rates.

Disabled: Disable IDE HDD Block Mode.

Gate A20 Option:

This refers to the way the system addresses memory above 1MB (extended

memory).

The default is Fast.

Normal: The A20 signal is controlled by the keyboard controller or chipset

hardware.

Fast: The A20 signal is controlled by Port 92 or chipset specific method.

Memory Parity/ECC Check:

If the DRAM chip in your system support parity/ECC check, select Enabled.

T ypematic Rate Setting:

This determines the keystrokes repeat rate.

The default is Disabled.

Enabled: Allows typematic rate and typematic delay programming.

Disabled: The typematic rate and typematic delay will be controlled by the

keyboard controller in your system.

T ypematic Rate (Chars/Sec):

This is the number of characters that will be repeated by a keyboard press.

The default is 6.

6: 6 characters per second. 8: 8 characters per second.

10: 10 characters per second. 12: 12 characters per second.

15: 15 characters per second. 20: 20 characters per second.

24: 24 characters per second. 30: 30 characters per second.

T ypematic Delay (msec):

This setting controls the time between the first and the second character

displayed by typematic auto-repeat.

Page 31

BIOS

EP-3VBM+

Page 4-7

The default is 250.

250: 250 msec.

500: 500 msec.

750: 750 msec.

1000: 1000 msec.

Security Option:

This category allows you to limit access to the System and Setup, or just to

Setup.

The default is Setup.

System: The system will not boot and the access to Setup will be denied if

the correct password is not entered at the prompt.

Setup: The system will boot; but the access to Setup will be denied if the

incorrect password is not entered at the prompt.

PCI/VGA Palette Snoop:

This field controls the ability of a primary PCI VGA controller to share a

common palette (When a snoop write cycles) with an ISA video card.

The default is Disabled.

Enabled: If an ISA card is connected to a PCI VGA card via the VESA

connector, and that ISA card connects to a VGA monitor, then that

ISA card uses the RAMDAC of the PCI card.

Disabled: Disables the VGA card Palette Snoop function.

OS Select For DRAM > 64MB:

Some operating systems require special handling. Use this option only if your

system has greater than 64MB of memory.

The default is Non-OS2.

OS2: Select this if you are running the OS/2 operating system with

greater than 64MB of RAM.

Non-OS2: Select this for all other operating systems and configurations.

Video BIOS Shadow:

This option allows video BIOS to be copied into RAM. V ideo Shadowing will

increase the video performance of your system.

The default is Enabled.

Enabled: Video shadow is enabled.

Disabled: Video shadow is disabled.

Page 32

BIOS

EP-3VBM+

Page 4-8

C8000 - CBFFF Shadow:

CC000 - CFFFF Shadow:

D0000 - D3FFF Shadow:

D4000 - D7FFF Shadow:

D8000 - DBFFF Shadow:

DC000 - DFFFF Shadow:

These categories determine whether ROMs from option cards will be copied

into RAM. This will be in 16K byte or 32K byte units, and the size will

depend on chipset of the option card.

Enabled: Optional shadow is enabled.

Disabled: Optional shadow is disabled.

4-3 Chipset Fea tures Setup

Choose the “CHIPSET FEATURES SETUP” in the CMOS SETUP UTILITY

menu to display following menu.

Figure 4: Chipset Features Setup

ROM PCI/ISA BIOS(2A6LGPAA)

CHIPSET FEATURES SETUP

AWARD SOFTWARE, INC.

Bank 0/1 DRAM Timing : SDRAM Fast OnChip USB : Enabled

Bank 2/3 DRAM Timing : SDRAM Fast USB Keyboard Support : Disabled

Bank 4/5 DRAM Timing : SDRAM Fast OnChip Sound : Enabled

SDRAM Cycle length : Auto OnChip Modem : Disabled

SDRAM Bank Interleave : Disabled

DRAM Page-Mode : Enabled

DRAM Fast Decoding : Auto

DRAM Read Option : Fast

Memory Hole : Disabled

Read Around write : Disabled

Concurrent PCI/Host : Enabled

System BIOS Cacheabe : Disabled

Video BIOS Cacheable : Enabled

Video RAM Cacheable : Disabled

AGP Aperture Size : 64M

AGP - 2X Mode : Enabled

Esc : Quit : Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift) F2 : Color

F7 : Load Setup Defaults

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Page 33

BIOS

EP-3VBM+

Page 4-9

Bank 0/1, 2/3, 4/5 DRAM Timing:

This value in this field is set by the system board manufacturer, depending on

whether the board has paged DRAMs or EDO (extended data output)

DRAMs.

The Choice: Bank 0/1, 2/3, 4/5.

SDRAM Cycle length:

This setting defines the CAS timing parameter of the SDRAM in terms of

clocks.

The default is 3.

2: Provides faster memory performance.

3: Provides better memory compatibility.

SDRAM Bank Interleave:

The item allows you to set how many banks of SDRAM support in your

mainboard.

The Choice: 2 Bank, 4 Bank, Disabled.

DRAM Page-Mode:

The item will active or inactive chipset page registers.

Enabled: Page-Mode Enabled.

Disabled: No page registers update and non Page-Mode operation.

DRAM Fast Decoding:

The item will effective DRAM operation sequential.

DRAM Read Option:

The item will effective DRAM reading CMD sequential.

Memory Hole:

You can reserve this memory area for the use of ISA adaptor ROMs.

The default is Disabled.

Enabled: This field enables the main memory (15~16MB) to remap to ISA

BUS.

Disabled: Normal Setting.

Note: If this feature is enabled you will not be able to cache this

memory segment.

Page 34

BIOS

EP-3VBM+

Page 4-10

Read Around write:

DRAM optimization feature: If a memory read is addressed to a location

whose latest write is being held in a buffer contents, and the read is not sent to

the DRAM.

The Choice: Enabled, Disabled

Concurrent PCI/Host:

When disabled, CPU bus will be occupied during the entire PCI operation

period.

The Choice: Enabled, Disabled

System BIOS Cacheable:

As with caching the V ideo BIOS above, enabling this selection allows accesses

to the system BIOS ROM addressed at F0000H-FFFFFH to be cached,

provided that the cache controller is enabled.

The Choice: Enabled, Disabled.

Video BIOS Cacheable:

When enabled. The Video BIOS cache will cause access to video BIOS

addressed at C0000H to C7FFFH to be cached, if the cache controller is also

enabled

The Choice: Enabled, Disabled.

Video RAM Cacheable:

Select enabled allows caching of the video RAM, resulting in better system

performance. However, if any program writes to this memory area, a system

error may result.

The Choice: Enabled, Disabled.

AGP Aperture Size:

The amount of system memory that the AGP card is allowed to share.

The default is 64.

4: 4MB of systems memory accessable by the AGP card.

8: 8MB of systems memory accessable by the AGP card.

16: 16MB of systems memory accessable by the AGP card.

32: 32MB of systems memory accessable by the AGP card.

64: 64MB of systems memory accessable by the AGP card.

128: 128MB of systems memory accessable by the AGP card.

256: 256MB of systems memory accessable by the AGP card.

Page 35

BIOS

EP-3VBM+

Page 4-11

OnChip USB:

Select Enabled if your system contains a Universal Serial Bus(USB) controller

and you have a USB peripheral.

USB Keyboard Support:

This controls the activation status of an optional USB keyboard that may be

attached.

The default is disabled.

Enabled: Enable USB keyboard support.

Disabled: Disable USB keyboard support.

OnChip Sound:

Turn on/of f onchip sound device.

OnChip Modem:

Turn on/of f onchip software modem device.

4-4 Po wer Management Setup

Choose the “POWER MANAGEMENT SETUP” in the CMOS SETUP UTILITY to display the following screen. This menu allows the user to modify the

power management parameters and IRQ signals. In general, these parameters

should not be changed unless it’ s absolutely necessary.

Figure 5: Power Management Setup

ROM PCI/ISA BIOS (2A6LGPAA)

POWER MANAGEMENT SETUP

AWARD SOFTWARE, INC.

ACPI function : Enabled

Power Management : User Define

PM Control by APM : Yes

Video off After : Suspend

Video off Method : V/H SYNC+Blank

MODEM Use IRQ : 3

Soft-off by PWRBTN : Delay 4 Sec

PWRON After PW-Fail : Former-Status

HDD Power Down : Disable

Doze Mode : Disable

Suspend Mode : Disable

** PM Events **

VGA : OFF

LPT & COM : LPT/COM

HDD & FDD : NO

DMA/master : OFF

Modem Ring Resume : Disabled

RTC Alarm Resume : Disabled

Esc : Quit : Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift) F2 : Color

F7 : Load Setup Defaults

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Primary INTR : ON

IRQ3 (COM 2) : Primary

IRQ4 (COM 1) : Primary

IRQ5 (LPT 2) : Primary

IRQ6 (Floppy Disk) : Primary

IRQ7 (LPT 1) : Primary

IRQ8 (RTC Alarm) : Disabled

IRQ9 (IRQ2 Redir) : Secondary

IRQ10 (Reserved) : Secondary

IRQ11 (Reserved) : Secondary

IRQ12 (PS/2 Mouse) : Primary

IRQ13 (Coprocessor) : Primary

IRQ14 (Hard Disk) : Primary

IRQ15 (Reserved) : Disabled

Page 36

BIOS

EP-3VBM+

Page 4-12

You can only change the content of Doze Mode, Standby Mode, and Suspend

Mode when the Power Management is set to ‘User Define’.

Power Management:

Use this to select your Power Management selection.

The default is User define.

Disabled: The system operates in NORMAL conditions (Non-GREEN),

and the Power Management function is disabled.

Max. saving: Maximum power savings. Inactivity period is 1 minute in

each mode.

Min. saving: Minimum power savings. Inactivity period is 1 hour in

each mode.

User define: Allows user to define PM Timers parameters to control

power saving mode.

PM controlled APM:

This option shows weather or not you want the Power Management to be

controlled the Advanced Power Management (APM).

The default is Yes.

Yes: APM controls your PM

No: APM does not control your PM

Video Off Method:

This option allows you to select how the video will be disabled by the power

management.

The default is V/H Sync + Blank

V/H Sync + Blank: System turns off vertical and horizontal synchronization

ports and writes blanks to the video buffer.

DPMS: Select this option if your monitor supports the Display

Power Management Signaling (DPMS) standard of the

Video Electronics Standards Association (VESA). Use

the software supplied for your video subsystem to select

video power management values.

Blank Screen: System only writes blanks to the video buffer.

Page 37

BIOS

EP-3VBM+

Page 4-13

MODEM Use IRQ:

Name the interrupt request (IRQ) line assigned to the modem (if any) on your

system. Activity of the selected IRQ always awakens the system.

Default is IRQ 3.

N/A: No IRQ is used. 3: IRQ 3

4: IRQ 4 5: IRQ 5

7: IRQ 7 9: IRQ 9

10: IRQ 10 11: IRQ 11

The EP-3VBM+ supports HDD Power Down, Doze and Standby power

saving functions when using the Intel Pentium II Processor.

The default is Disabled

Soft-Off by PWR-BTTN:

Use this to select your soft-off function.

The default is Delay 4 sec.

Instant Off: Turns off instantly.

Delay 4 Second : Turns off after a 4 second delay . If momentary press of

button, the system will go into Suspend Mode. Press again

to take system out of Suspend Mode.

PWRON After PW-Fail:

The system will stay of or power on after a power interrupte.

The default is Fomer-Status.

Fomer-Status: Stay off or power on depend on system safe shut-down or

power fail.

ON: System always power on after a power interrupte.

OFF: System always stay off after a power interrupte.

HDD Power Down:

HDD Standby timer can be set from 1 to 15 minute(s).

Doze Mode:

The “Doze” mode timer starts to count when no “PM events” have occurred.

Suspend Mode:

This function works only when the Pentium II Processor is installed. The

timer starts to count when “System Standby” mode timer is timed out and no

“PM Events” are occurring. Valid range is from 1 minute up to 1 hour.

Page 38

BIOS

EP-3VBM+

Page 4-14

VGA:

When set to On (default), any event occurring at a VGA port will awaken a

system which has been powered down.

LPT & COM:

When set to On (default), any event occurring at a COM(serial)/LPT (printer)

port will awaken a system which has been powered down.

HDD & FDD:

When set to On (default), any event occurring at a hard or floppy drive port

will awaken a system which has been powered down.

DMA/master:

When set to On (default), any event occurring to the DMA controller will

awaken a system which has been powered down.

RTA Alarm Resume:

When set to Enable rta alarm resume, you could set the date (of month) and

timer (hh:mm:ss), any event occurring at will awaken a system which has been

powered down.

Modem Ring Resume:

When set to Enabled, any event occurring to the Modem Ring will awaken a

system which has been powered down.

Primary INTR:

When set to On (default), any event occurring at will awaken a system which

has been powered down.

Page 39

BIOS

EP-3VBM+

Page 4-15

4-5 PNP/PCI Configuration

The PNP/PCI configuration program is for the user to modify the PCI/ISA IRQ

signals when various PCI/ISA cards are inserted in the PCI or ISA slots.

WARNING: Conflicting IRQ’s may cause the system to not find certain

devices.

Figure 6: PCI Configuration Setup

PNP OS Installed:

Do you have a PNP OS installed on your system. The default is No.

Yes: Select if you are using a PNP OS

No: Select if your OS does not support PNP.

Resources Controlled By:

Who controlled the system PNP/PCI resources.

The default is Manual.

Manual: PNP Card’s resources will be controlled manually. You can set

which IRQ-X and DMA-X are assigned to PCI/ISA PNP or Legacy

ISA Car ds.

Auto: If your ISA card and PCI card are all PNP cards, BIOS will assign

the interrupt resource automatically.

ROM PCI/ISA BIOS(2A6LGPAA)

PNP/PCI CONFIGURATION

AWARD SOFTWARE, INC.

CPU to PCI Write Buffer : Enabled

PCI Dynamic Bursting : Enabled

PCI Master 0 WS Write : Enabled

PCI Delay Transaction : Disabled

PCI#2 Access #1 Retry : Disabled

AGP Master 1 WS Write : Enabled

AGP Master 1 WS Read : Disabled

Solt 1 Use IRQ No. : Auto

Solt 2 Use IRQ No. : Auto

Solt 3 Use IRQ No. : Auto

Solt 4 Use IRQ No. : Auto

Solt 5 Use IRQ No. : Auto

PNP OS Installed : No

Resources Controlled By : Manual

Reset Configuration Data : Disabled

IRQ-3 Assigned to : PCI/ISA PnP

IRQ-4 Assigned to : PCI/ISA PnP

IRQ-5 Assigned to : PCI/ISA PnP

IRQ-7 Assigned to : PCI/ISA PnP

IRQ-9 Assigned to : PCI/ISA PnP

IRQ-10 Assigned to : PCI/ISA PnP

IRQ-11 Assigned to : PCI/ISA PnP

IRQ-12 Assigned to : PCI/ISA PnP

IRQ-14 Assigned to : PCI/ISA PnP

IRQ-15 Assigned to : PCI/ISA PnP

DMA-0 Assigned to : PCI/ISA PnP

DMA-1 Assigned to : PCI/ISA PnP

DMA-3 Assigned to : PCI/ISA PnP

DMA-5 Assigned to : PCI/ISA PnP

DMA-6 Assigned to : PCI/ISA PnP

DMA-7 Assigned to : PCI/ISA PnP

Esc : Quit : Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift) F2 : Color

F7 : Load Setup Defaults

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Page 40

BIOS

EP-3VBM+

Page 4-16

Reset Configuration Data:

This setting allows you to clear ESCD data..

The default is Disabled.

Disabled: Normal Setting.

Enabled: If you have plugged in some Legacy cards to the system and they

were recorded into ESCD (Extended System Configuration Data),

you can set this field to Enabled in order to clear ESCD.

CPU to PCI Write Buffer:

When enabled, up to four D words of data can be written to the PCI bus

without interruting the CPU. When disabled, a write buffer is not used and the

CPU read cycle will not be completed until the PCI bus signals that it is ready

to receive the data.

The Choice: Enabled, Disabled.

PCI Dynamic Bursting:

When Enabled, data transfers on the PCI bus, where possible, make use of the

high-performance PCI bust protocol, in which graeater amounts of data are

transferred at a single command.

The Choice: Enabled, Disabled.

PCI Master 0 WS Write:

When Enabled, writes to the PCI bus are command with zero wait states.

The Choice: Enabled, Disabled.

PCI Delay T ransaction:

The chipset has an embedded 32-bit posted write buffer to support delay

transactions cycles. Select Enabled to support compliance with PCI specification version 2.1.

The Choice: Enabled, Disabled.

PCI #2 Access #1 Retry:

This item allows you enabled/disable the PCI #2 Access #1 Retry.

The Choice: Enabled, Disabled.

Page 41

BIOS

EP-3VBM+

Page 4-17

4-6 Load Setup Defaults

The “LOAD SETUP DEFAULTS” function loads the system default data directly

from ROM and initializes the associated hardware properly. This function will be

necessary only when the system CMOS data is corrupted.

4-7 Integrated Peripherals

Figure 8: Integrated Peripherals

Note: If you do not use the Onboard IDE connector, then you will need to

set Onboard Primary PCI IDE: Disabled and Onboard Secondary

PCI IDE: Disabled

Note: The Onboard PCI IDE cable should be equal to or less than 18

inches (45 cm.).

IDE Prefetch Mode:

Enable prefetching for IDE drive interfaces that support its faster drive

accesses. If uou are getting disk drive errors, change the setting to omit the

drive interface where the errors occur. Depending on the configuration of your

IDE subsystem, this field may not appear, and it does not appear when the

Internal PCI/IDE field, above, is Disabled.

The Choice: Enabled, Disabled.

ROM PCI/ISA BIOS(2A6LGPAA)

INTEGRATED PERIPHERALS

AWARD SOFTWARE, INC.

OnChip IDE Channel0 : Enabled

OnChip IDE Channel1 : Enabled

IDE Prefetch Mode : Enabled

Primary Master PIO : Auto

Primary Slave PIO : Auto

Secondary Master PIO : Auto

Secondary Slave PIO : Auto

Primary Master UDMA : Auto

Primary Slave UDMA : Auto

Secondary MasterUDMA : Auto

Secondary Slave UDMA : Auto

Init Display First : PCI Slot

Onboard FDD Controller : Enabled

Onboard Serial Port 1 : Auto

Onboard Serial Port 2 : Auto

UART 2 Mode : HPSIR

IR Function Duplex : Half

TX, RX inverting enable : No, Yes

Esc : Quit : Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift) F2 : Color

F7 : Load Setup Defaults

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Onboard Parallel Port : 378/IRQ7

Onboard Parallel Mode : ECP/EPP

ECP Mode Use DMA : 3

Parallel Port EPP Type : EPP1.9

Onboard Legacy Audio : Enabled

Sound Blaster : Disabled

SB I/O Base Address : 220H

SB IRQ Select : IRQ 5

SB DMA Select : DMA 1

MPU-401 : Disabled

MPU-401 I/O Address : 330-333H

FM Port (388-38BH) : Disabled

Game Port (200-207H) : Enabled

Page 42

BIOS

EP-3VBM+

Page 4-18

Onchip IDE Channel:

The default value is Enabled.

Enabled: Enables Onboard IDE primary port.

Disabled: Disables Onboard IDE primary port.

Onchip IDE Channel:

The default is Enabled.

Enabled: Enables Onboard IDE secondary port.

Disabled: Disables Onboard IDE secondary port.

Primary Master PIO:

The default is Auto.

Auto: BIOS will automatically detect the Onboar d Primary Master PCI IDE

HDD Accessing mode.

Mode 0~4:Manually set the IDE Programmed interrupt mode.

Primary Slave PIO:

The default is Auto.

Auto: BIOS will automatically detect the Onboard Primary Slave PCI

IDE HDD Accessing mode.

Mode 0~4: Manually set the IDE Programmed interrupt mode.

Secondary Master PIO:

The default is Auto.

Auto: BIOS will automatically detect the Onboard Secondary Master

PCI IDE HDD Accessing mode.

Mode 0~4: Manually set the IDE Programmed interrupt mode.

Secondary Slave PIO:

The default is Auto.

Auto: BIOS will automatically detect the Onboard Secondary Slave PCI IDE

HDD Accessing mode.

Mode 0~4: Manually set the IDE Programmed interrupt mode.

Primary Master UDMA:

This allows you to select the mode of operation for the hard drive.

The default is Auto.

Auto: The computer will select the optimal setting.

Disabled: The hard drive will run in normal mode.

Page 43

BIOS

EP-3VBM+

Page 4-19

Primary Slave UDMA:

This allows you to select the mode of operation for the hard drive.

The default is Auto.

Auto: The computer will select the optimal setting.

Disabled: The hard drive will run in normal mode.

Secondary Master UDMA:

This allows you to select the mode of operation for the hard drive.

The default is Auto.

Auto: The computer will select the optimal setting.

Disabled: The hard drive will run in normal mode.

Secondary Slave UDMA:

This allows you to select the mode of operation for the hard drive.

The default is Auto.

Auto: The computer will select the optimal setting.

Disabled: The hard drive will run in normal mode.

Init Display First:

If two video cards are used (1 AGP and 1 PCI) this specifies which one will be

the primary display adapter.

The default is PCI Slot.

PCI Slots: PCI video card will be primary adapter.

AGP: AGP video card will be primary adapter.

Onboard FDD Controller:

This controls the state of the onboard floppy controller. The default value is

Enabled.

Enabled: Enable the Onboard floppy drive interface controller.

Disabled: Disable the Onboard floppy drive interface controller.

Onboard Serial Port 1:

This field allows the user to configure the 1st serial port.

The default is Auto.

AUTO: Enable Onboard Serial port 1 and address is Auto adjusted

COM1: Enable Onboard Serial port 1 and address is 3F8H/IRQ4.

COM2: Enable Onboard Serial port 1 and address is 2F8H/IRQ3.

COM3: Enable Onboard Serial port 1 and address is 3E8H/IRQ4.

Page 44

BIOS

EP-3VBM+

Page 4-20

COM4: Enable Onboard Serial port 1 and address is 2E8H/IRQ3.

Disabled: Disable Onboard Serial port 1.

Onboard Serial Port 2:

This field allows the user to configure the 2nd serial port.

The default is Auto.

AUTO: Enable Onboard Serial port 2 and address is Auto adjusted

COM1: Enable Onboard Serial port 2 and address is 3F8H/IRQ4.

COM2: Enable Onboard Serial port 2 and address is 2F8H/IRQ3.

COM3: Enable Onboard Serial port 2 and address is 3E8H/IRQ4.

COM4: Enable Onboard Serial port 2 and address is 2E8H/IRQ3.

Disabled: Disable Onboard Serial port 2.

UART 2 Mode:

This item allows you to determine which Infra Red (IR) function of onboard

I/O chip.

The Choice: Standard, ASKIR, HPSIR.

IR Function Duplex:

This item allows you to select the IR function when you select the UAR T2

Mode is ASKIR.

The Choice: Half, Full.

TX, RX inverting enable:

This item invert serial port 2 TX and RX output signal level.

No, No

TX, RX have no signal inverting.

No, Yes RX have signal inverting.

Yes, No

TX have signal inverting.

Yes, Yes

TX, RX have signal inverting.

Onboard Parallel port:

This field allows the user to configure the LPT port.

The default is 378H / IRQ7.

378H: Enable Onboard LPT port and address is 378H and IRQ7.

278H: Enable Onboard LPT port and address is 278H and IRQ5.

3BCH: Enable Onboard LPT port and address is 3BCH and IRQ7.

Disabled: Disable Onboard LPT port.

Page 45

BIOS

EP-3VBM+

Page 4-21

Onboard Parallel Mode:

This field allows the user to select the parallel port mode.

The default is ECP+EPP.

Normal: Standar d mode. IBM PC/AT Compatible bidirectional parallel

port.

EPP: Enhanced Parallel Port mode.

ECP: Extended Capabilities Port mode.

EPP+ECP: ECP Mode & EPP Mode.

ECP Mode USE DMA:

This field allows the user to select DMA1 or DMA3 for the ECP mode.

The default is DMA3.

DMA1: This field selects the routing of DMA1 for the ECP mode.

DMA3: This field selects the routing of DMA3 for the ECP mode.

Parallel Port EPP T ype:

This item allows you to determine the IR transfer mode of onboard I/O chip.

The Choice: EPP1.9, EPP1.7.

Onboard Legacy Audio:

Legacy Audio enabled/disabled.

Sound Blaster:

Sound Blaster compatible device enabled/disabled.

SB I/O Base Address:

Sound Blaster I/O resource selection.

SB IRQ Select:

Legacy audio device IRQ selection.

SB DMA Select:

Sound Blaster DMA channel selection.

MPU-401:

MPU-401 function enabled/disabled.

MPU-401 I/O Address:

Built-in MPU-401 compatible MIDI I/O port selection:

300-303H 310-313H

320-323H 330-333H (default)

Page 46

BIOS

EP-3VBM+

Page 4-22

FM Port (388-38BH):

Frequency modulation port at I/O port 388-38BH enabled/disabled.

Game Port (200-207H):

Built-in joystick port support disabled/enabled(default).

4-8 SENSOR AND CPU SPEED SETUP

Figure 9: Sensor And CPU Speed Setup

Auto Detect DIMM/PCI Clk:

When enabled the motherboard will automatically disable the clock source for a

DIMM socket which does not have a module in it. Same applies for PCI slots.

The default is Enabled.

Enabled: Enables this option.

Disabled: Disables this option.

Spread Spectrum :

The default is Disabled.

Enabled: Enables this option.

Disabled: Disables this option.

ROM PCI/ISA BIOS(2A6LGPAA)

SENSOR AND CPU SPEED SETUP

AWARD SOFTWARE, INC.

Auto Detect DIMM/PCI Clk : Enabled Current CPU Temp. : 31oC/87oF

Spread Spectrum : Disabled Current System Temp. : 24oC/75oF

CPU Host Clock (CPU/PCI) : Default Current CPU Fan Speed : 0 R PM

DRAM Clock Is : Host Clock Current Chassis Fan Speed : 0 RPM

CPU Fan In Suspend : Off Vcore : 1.87V Vtt : 1.52V

3.3V : 3.28V 5V : 5.02V

12V : 11.88V

Esc : Quit : Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift) F2 : Color

F7 : Load Setup Defaults

éé

éé

é

êê

êê

ê

èè

èè

è

çç

çç

ç

Page 47

BIOS

EP-3VBM+

Page 4-23

CPU Host Clock (CPU/PCI):

Allows the external clock to be modified depending upon what FSB has been

selected. Should not be used to clock processor faster than it was designed for.

(See page A-11).

The default is Default.

66MHz FSB options: Default, 66.8, 68.5, 75, and 83MHz.

100MHz FSB options: Default, 100, 103, 112, and 133MHz.

DRAM Clock Is:

The item will synchronize/asynchronize DRAM operation clock.

Host Clock: DRAM has same working clock with CPU host bus.

2/3 Host: DRAM running with lower operation clock.

CPUF AN Off In Suspend:

This option is used to set if the CPU fans will turn off during suspend mode.

The default is Enabled.

Enabled: The system will turn off the CPU fans during suspend mode.

Disabled: The system will not turn off the CPU fan during suspend mode.

Current System Temp:

This is the Current temperature of the system.

Current CPU T emperatur e:

This is the current temperature of the CPU.

Current CPU FAN Speed:

The current CPU fan speed in RPMs.

Current Chassis FAN Speed:

The current chassis fan speed in RPMs.

CPU(V):

The voltage level of the CPU(V io/Vcore).

Vtt, +3.3V, +5V, +12V: The voltage level of the switch power supply.

Page 48

BIOS

EP-3VBM+

Page 4-24

4-9 Change Supervisor or

User Password

To change the password, choose the “SUPERVISOR PASSWORD or USER

PASSWORD” option from the CMOS SETUP UTILITY menu and press

[Enter].

NOTE: Either “Setup” or “System” must be selected in the “Security Option”

of the BIOS FEA TURES SETUP menu.

1. If CMOS is corrupted or the option was not used, a default password

stored in the ROM will be used. The screen will display the following

message:

Enter Password:

Press the [Enter] key to continue after the proper password is given.

2. If the CMOS is corrupted or the option was used earlier and the user

wishes to change the default password, the SETUP UTILITY will display

a message and ask for a confirmation.

Confirm Password:

3. After pressing the [Enter] key (ROM password if the option was not

used) or current password (user-defined password), the user can change

the password and store new one in CMOS RAM. A maximum of 8

characters can be entered.

Page 49

BIOS

EP-3VBM+

Page 4-25

4-10 IDE HDD Auto Detection

The “IDE HDD auto detection” utility is a very useful tool, especially when you

do not know which kind of hard disk type you are using. You can use this utility

to detect the correct disk type installed in the system automatically. But now you

can set HARD DISK TYPE to Auto in the STANDARD CMOS SETUP. You

don’t need the “IDE HDD AUTO DETECTION” utility. The BIOS will Autodetect the hard disk size and model on display during POST.

Figure 10: IDE HDD Auto Detection

NOTE: HDD Modes

The Award BIOS supports 3 HDD modes : NORMAL, LBA & LARGE NORMAL mode

Generic access mode in which neither the BIOS nor the IDE controller will make

any transformations during accessing.

The maximum number of cylinders, head & sectors for NORMAL mode are.

1024, 16 & 63

no. Cylinder (1024)

x no. Head ( 16)

x no. Sector ( 63)

x no. per sector ( 512)

528 Megabytes

HARD DISKS TYPE SIZE CYLS HEADS PRECOMP LANDZONE SECTORS MODE

Primary Master :

Select Secondary Slave Option (N=Skip) : N

OPTIONSSIZE CYLS HEAD PRECOMP LANDZ SECTORMODE

2 (Y) 4310 524 255 0 14847 63 LBA

1 4310 14848 9 65535 14847 63 NORMAL

3 4310 928 144 65535 14847 63 LARGE

Note: Some OSes (like SCO-UNIX) must use NORMAL for installation

ESC : Skip

ROM PCI/ISA BIOS(2A6LGPAA)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC.

Page 50

BIOS

EP-3VBM+

Page 4-26

If user set his HDD to NORMAL mode, the maximum accessible HDD size will

be 528 Megabytes even though its physical size may be greater than that!

LBA (Logical Block Addressing) mode: A new HDD accessing method to

overcome the 528 Megabyte bottleneck. The number of cylinders, heads &

sectors shown in setup may not be the number physically contained in the HDD.

During HDD accessing, the IDE controller will transform the logical address

described by sector, head & cylinder into its own physical address inside the

HDD. The maximum HDD size supported by LBA mode is 8.4 GigaBytes which

is obtained by the following formula:

no. Cylinder (1024)

x no. Head ( 255)

x no. Sector ( 63)

x bytes per sector ( 512)

8.4 GigaBytes

LARGE mode: Extended HDD access mode supported by Award Software.

Some IDE HDDs contain more than 1024 cylinder without LBA support (in some

cases, user do not want LBA). The Award BIOS provides another alternative to

support these kinds of LARGE mode.

CYLS HEADS SECTOR MODE

1120 16 59 NORMAL

560 32 59 LARGE

BIOS tricks DOS (or other OS) that the number of cylinders is less than 1024 by

dividing it by 2. At the same time, the number of heads is multiplied by 2. A

reverse transformation process will be made inside

INT 12h in order to access the right HDD address!

Maximum HDD size:

no. Cylinder (1024)

x no. Head ( 32)

x no. Sector ( 63)

x bytes per sector ( 512)

1 GigaByte

Note: To support LBA or LARGE mode of HDDs, there must be some

software involved. All the software is located in the Award HDD

Page 51

BIOS

EP-3VBM+

Page 4-27

Service Routine (INT 13h). It may fail to access a HDD with LBA

(LARGE) mode selected if you are running under an Operating

System which replaces the whole INT 13h.

UNIX operating systems do not support either LBA or LARGE and must utilize

the Standard mode. UNIX can support drives larger than 528MB.

4-11 Save & Exit Setup

The “SAVE & EXIT SETUP” option will bring you back to the boot up procedure with all the changes you just recorded in the CMOS RAM.

4-12 Exit Without Saving

The “EXIT WITHOUT SAVING” option will bring you back to normal boot up

procedure without saving any data into CMOS RAM.

All old data in the CMOS will not be destroyed.

Page 52

BIOS

EP-3VBM+

Page 4-28

Page Left Blank

Page 53

Appendix

EP-3VBM+

A-1

Appendix A:

A-1 MEMORY MAP

Address Range Size Description

[00000-7FFFF] 512K Conventional memory

[80000-9FBFF] 127K Extended Conventional memory

[9FC00-9FFFF] 1K Extended BIOS data area if PS/2 mouse is

installed

[A0000-C7FFF] 160K Available for Hi DOS memory

[C8000-DFFFF] 96K Available for Hi DOS memory and adapter

ROMs

[E0000-EEFFF] 60K Available for UMB

[EF000-EFFFF] 4K Video service routine for Monochrome & CGA

adaptor

[F0000-F7FFF] 32K BIOS CMOS setup utility

[F8000-FCFFF] 20 K BIOS runtime service routine (2)

[FD000-FDFFF] 4K Plug and Play ESCD data area

[FE000-FFFFF] 8K BIOS runtime service routine (1)

A-2 I/O MAP

[000-01F] DMA controller.(Master)

[020-021] INTERRUPT CONTROLLER.(Master)

[022-023] CHIPSET control registers. I/O ports.

[040-05F] TIMER control registers.

[060-06F] KEYBOARD interface controller.(8042)

[070-07F] RTC ports & CMOS I/O ports.

[080-09F] DMA register.

[0A0-0BF] INTERRUPT controller.(Slave)

[0C0-0DF] DMA controller.(Slave)

[0F0-0FF] MATH COPROCESSOR.

[1F0-1F8 ] HARD DISK controller.

[278-27F] PARALLEL port 2.

[2B0-2DF] GRAPHICS adapter controller.

[2F8-2FF] SERIAL port 2.

[360-36F] NETWORK ports.

[378-37F] PARALLEL port 1.

Page 54

Appendix

EP-3VBM+

A-2

[3B0-3BF] MONOCHROME & PARALLEL port adapter.

[3C0-3CF] EGA adapter.

[3D0-3DF] CGA adapter.

[3F0-3F7] FLOPPY DISK controller.

[3F8-3FF] SERIAL port 1.

A-3 TIMER & DMA CHANNELS MAP

TIMER MAP:

TIMER Channel 0 System timer interrupt.

TIMER Channel 1 DRAM REFRESH request.

TIMER Channel 2 SPEAKER tone generator.

DMA CHANNELS:

DMA Channel 0 Available.

DMA Channel 1 Onboard ECP (Option).

DMA Channel 2 FLOPPY DISK (SMC CHIP).

DMA Channel 3 Onboard ECP (default).

DMA Channel 4 Cascade for DMA controller 1.

DMA Channel 5 Available.

DMA Channel 6 Available.

DMA Channel 7 Available

A-4 INTERRUPT MAP

NMI :

Parity check error.

IRQ (H/W):

0 System TIMER interrupt from TIMER 0.

1 KEYBOARD output buffer full.

2 Cascade for IRQ 8-15.

3 SERIAL port 2.

4 SERIAL port 1.

5 PARALLEL port 2.

6 FLOPPY DISK (SMC CHIP).

7 PARALLEL port 1.

8 RTC clock.

9 Available.

10 Available.

11 Available.

Page 55

Appendix

EP-3VBM+

A-3

1 2 PS/2 Mouse.

1 3 MATH coprocessor.

14 Onboard HARD DISK (IDE1) channel.

15 Onboard HARD DISK (IDE1) channel.

A-5 RTC & CMOS RAM MAP

RTC & CMOS:

00 Seconds.

01 Second alarm.

0 2 Minutes.

03 Minutes alarm.

0 4 Hours.

0 5 Hours alarm.

06 Day of week.

07 Day of month.

08 Month.

09 Year.

0A Status register A.

0B Status register B.

0C Status register C.

0D Status register D.

0E Diagnostic status byte.

0F Shutdown byte.

10 FLOPPY DISK drive type byte.

11 Reserve.

12 HARD DISK type byte.

13 Reserve.

14 Equipment type.

15 Base memory low byte.

16 Base memory high byte.

17 Extension memory low byte.

18 Extension memory high byte.

19-2d

2E-2F

3 0 Reserved for extension memory low byte.

3 1 Reserved for extension memory high byte.

32 DA TE CENTUR Y byte.

33 INFORMA TION FLAG.

Page 56

Appendix

EP-3VBM+

A-4

Appendix B:

B-1 POST CODES

ISA POST codes are typically output to I/O port address 80h.

POST (hex) DESCRIPTION

01-02 Reserved.

C0 Turn off OEM specific cache, shadow.

03 1. Initialize EISA registers (EISA BIOS only).

2. Initialize all the standard devices with default values

Standard devices includes.

- DMA controller (8237).

- Programmable Interrupt Controller (8259).

- Programmable Interval Timer (8254).

- RTC chip.

04 Reserved

0 5 1. Keyboard Controller Self-Test.

06 2. Enable Keyboard Interface.

0 7 Reserved.

0 8 Verifies CMOS's basic R/W functionality.

C1 Auto-detection of onboard DRAM & Cache.

C5 Copy the BIOS from ROM into E0000-FFFFF shadow RAM so

thatPOST will go faster.

0 8 Test the first 256K DRAM.

0 9 OEM specific cache initialization. (if needed)

0A 1. Initialize the first 32 interrupt vectors with corresponding

Interrupt handlers. Initialize INT numbers from 33-120 with

Dummy (Spurious) Interrupt Handler.

2. Issue CPUID instruction to identify CPU type.

3. Early Power Management initialization. (OEM specific)

0B 1. Verify the RTC time is valid or not.

2. Detect bad battery.

3. Read CMOS data into BIOS stack area.

4. PnP initializations including. (PnP BIOS only)

- Assign CSN to PnP ISA card.

- Create resource map from ESCD.

5. Assign IO & Memory for PCI devices. (PCI BIOS only)

Page 57

Appendix

EP-3VBM+

A-5

0C Initialization of the BIOS Data Area. (40:ON - 40:FF)

0D 1. Program some of the Chipset's value according to Setup.

(Early Setup Value Program)

2. Measure CPU speed for display & decide the system clock

speed.

3. Video initialization including Monochrome, CGA, EGA/VGA.

If no display device found, the speaker will beep.

0E 1. Test video RAM. (If Monochrome display device found)

2. Show messages including.

- Award Logo, Copyright string, BIOS Data code & Part No.

- OEM specific sign on messages.

- Energy Star Logo. (Green BIOS ONLY)

- CPU brand, type & speed.

- Test system BIOS checksum. (Non-Compress Version only)

0F DMA channel 0 test.

10 DMA channel 1 test.

11 DMA page registers test.

12-13 Reserved.

1 4 Test 8254 Timer 0 Counter 2.

1 5 Test 8259 interrupt mask bits for channel 1.

1 6 Test 8259 interrupt mask bits for channel 2.

1 7 Reserved.

1 9 Test 8259 functionality.

1A-1D Reserved.

1E If EISA NVM checksum is good, execute EISA initialization.

(EISA BIOS only)

1F-29 Reserved.

3 0 Detect Base Memory & Extended Memory Size.

3 1 1. Test Base Memory from 256K to 640K.

2. Test Extended Memory from 1M to the top of memory.

32 1. Display the Award Plug & Play BIOS Extension message.

(PnP BIOS only)

2. Program all onboard super I/O chips (if any) including COM

ports, LPT ports, FDD port ... according to setup value.

33-3B Reserved.

3C Set flag to allow users to enter CMOS Setup Utility.

3D 1. Initialize Keyboard.

2. Install PS2 mouse.

Page 58

Appendix

EP-3VBM+

A-6

3E Try to turn on Level 2 cache.

Note: Some chipset may need to turn on the L2 cache in this

stage. But usually, the cache is turn on later in POST 61h.

3F-40 Reserved.

BF 1. Program the rest of the Chipset's value according to Setup.

(Later Setup Value Program)

41 2. If auto-configuration is enabled, program the chipset with

pre-defined Values.

4 2 Initialize floppy disk drive controller.

4 3 Initialize Hard drive controller.

45 If it is a PnP BIOS, initialize serial & parallel ports.

4 4 Reserved.

4 5 Initialize math coprocessor.

46-4D Reserved.

4E If there is any error detected (such as video, kb...), show all error

messages on the screen & wait for user to press <F1> key.

4F 1. If password is needed, ask for password.

2. Clear the Energy Star Logo. (Green BIOS only)

50 Write all CMOS values currently in the BIOS stack area back

into the CMOS.

5 1 Reserved.

52 1. Initialize all ISA ROMs.

2. Later PCI initializations. (PCI BIOS only)

- assign IRQ to PCI devices.

- initialize all PCI ROMs.

3. PnP Initialzations. (PnP BIOS only)

- assign IO, Memory, IRQ & DMA to PnP ISA devices.

- initialize all PnP ISA ROMs.

4. Program shadows RAM according to Setup settings.

5. Program parity according to Setup setting.

6. Power Management Initialization.

- Enable/Disable global PM.

- APM interface initialization.

53 1. If it is NOT a PnP BIOS, initialize serial & parallel ports.

2. Initialize time value in BIOS data area by translate the RTC

time value into a timer tick value.

6 0 Setup Virus Protection. (Boot Sector Protection) functionality

according to Setup setting.

Page 59

Appendix

EP-3VBM+

A-7

61 1. Try to turn on Level 2 cache.

Note: If L2 cache is already turned on in POST 3D, this part will

be skipped.

2. Set the boot up speed according to Setup setting.

3. Last chance for Chipset initialization.

4. Last chance for Power Management initialization. (Green`

BIOS only)

5. Show the system configuration table.

62 1. Setup daylight saving according to Setup value.

2. Program the NUM Lock, typematic rate & typematic speed

according to Setup setting.

63 1. If there is any changes in the hardware configuration, update

the ESCD information. (PnP BIOS only)

2. Clear memory that have been used.

3. Boot system via INT 19H.

FF System Booting. This means that the BIOS already pass the

control right to the operating system.

B-2 Unexpected Errors:

POST (hex) DESCRIPTION

B0 If interrupt occurs in protected mode.

B1 Unclaimed NMI occurs.0

Page 60

Appendix

EP-3VBM+

A-8

Page Left Blank

Page 61

Appendix

EP-3VBM+

A-9

Appendix C

NOTE:

The "LOAD SETUP DEFAULTS" function loads the system default data directly from

ROM and initializes the associated hardware properly. This function will be necessary

when you accept this mainboard, or the system CMOS data is corrupted.

LOAD SETUP DEF AULTS

ROM PCI/ISA BIOS(2A6LGPAA)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC.

Load SETUP Default (Y/N)? Y

STANDARD CMOS SETUP SUPERVISOR PASSWORD

BIOS FEATURES SETUP USER PASSWORD

CHIPSET FEATURES SETUP IDE HDD AUTO DETECTION

POWER MANAGEMENT SETUP HDD LOW LEVEL FORMAT

PNP/PCI CONFIGURA ETUP

INTEGRATED PERIPH SAVING

LOAD SETUP DEFAULTS

ESC: QUIT :SELECT ITEM

F10:Save & Exit Setup (Shift)F2 :Change Color

Load Setup Defaults Except Standard COMS SETUP

é

ê

è

Page 62

Appendix

EP-3VBM+

A-10

Page Left Blank

Page 63

AppendixEP-3VBM+

A-11