EON EN29F002T90TI, EN29F002T90JI, EN29F002T70TI, EN29F002T70JI, EN29F002T55TI Datasheet

...

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

1

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

FEATURES

•

5.0V ± 10% for both read/write operation

•

Read Access Time

- 45ns, 55ns, 70ns, and 90ns

•

Fast Read Access Time

- 70ns with C

load

= 100pF

- 45ns, 55ns with C

load

= 30pF

•

Sector Architecture:

One 16K byte Boot Sector, Two 8K byte

Parameter Sectors, one 32K byte and

three 64K byte main Sectors

•

Boot Block Top/Bottom Programming

Architecture

•

High performance program/erase speed

- Byte program time: 10µs typical

- Sector erase time: 500ms typical

- Chip erase time: 3.5s typical

•

Low Standby Current

- 1µA CMOS standby current-typical

- 1mA TTL standby current

•

Low Power Active Current

- 30mA active read current

- 30mA program / erase current

•

JEDEC Standard program and erase

commands

•

JEDEC standard

DATA

polling and toggle

bits feature

•

Hardware

RESET

Pin (n/a for EN29F002N)

•

Single Sector and Chip Erase

•

Sector Protection / Temporary Sector

Unprotect (

RESET

= VID)

•

Sector Unprotect Mode

•

Embedded Erase and Program Algorithms

•

Erase Suspend / Resume modes:

Read and program another sector during

Erase Suspend Mode

•

0.4 µm double-metal double-poly

triple-well CMOS Flash Technology

•

Low Vcc write inhibit < 3.2V

•

100K endurance cycle

•

Package Options

- 32-pin PDIP

- 32-pin PLCC

- 32-pin TSOP (Type 1)

•

Commercial and Industrial Temperature

Ranges

GENERAL DESCRIPTION

The EN29F002 / EN29F002N is a 2-Megabit, electrically erasable, read/write non-volatile flash memory.

Organized into 256K words with 8 bits per word, the 2M of memory is arranged in seven sectors (with

top/bottom configuration), including one 16K Byte Boot Sector, two 8K Byte Parameter sectors, and four main

sectors (one 32K Byte and three 64K Byte). Any byte can be programmed typically at 10µs. The EN29F002 /

EN29F002N features 5.0V voltage read and write operation. The access times are as fast as 45ns to eliminate

the need for WAIT states in high-performance microprocessor systems.

The EN29F002 / EN29F002N has separate Output Enable (

OE

), Chip Enable (CE), and Write

Enable (

WE

) controls which eliminate bus contention issues. This device is designed to allow

either single sector or full chip erase operation, where each sector can be individually protected

against program/erase operations or temporarily unprotected to erase or program. The device can

sustain a minimum of 100K program/erase cycles on each sector.

EN29F002 / EN29F002N

2 Megabit (256K x 8-bit) Flash Memory

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

2

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

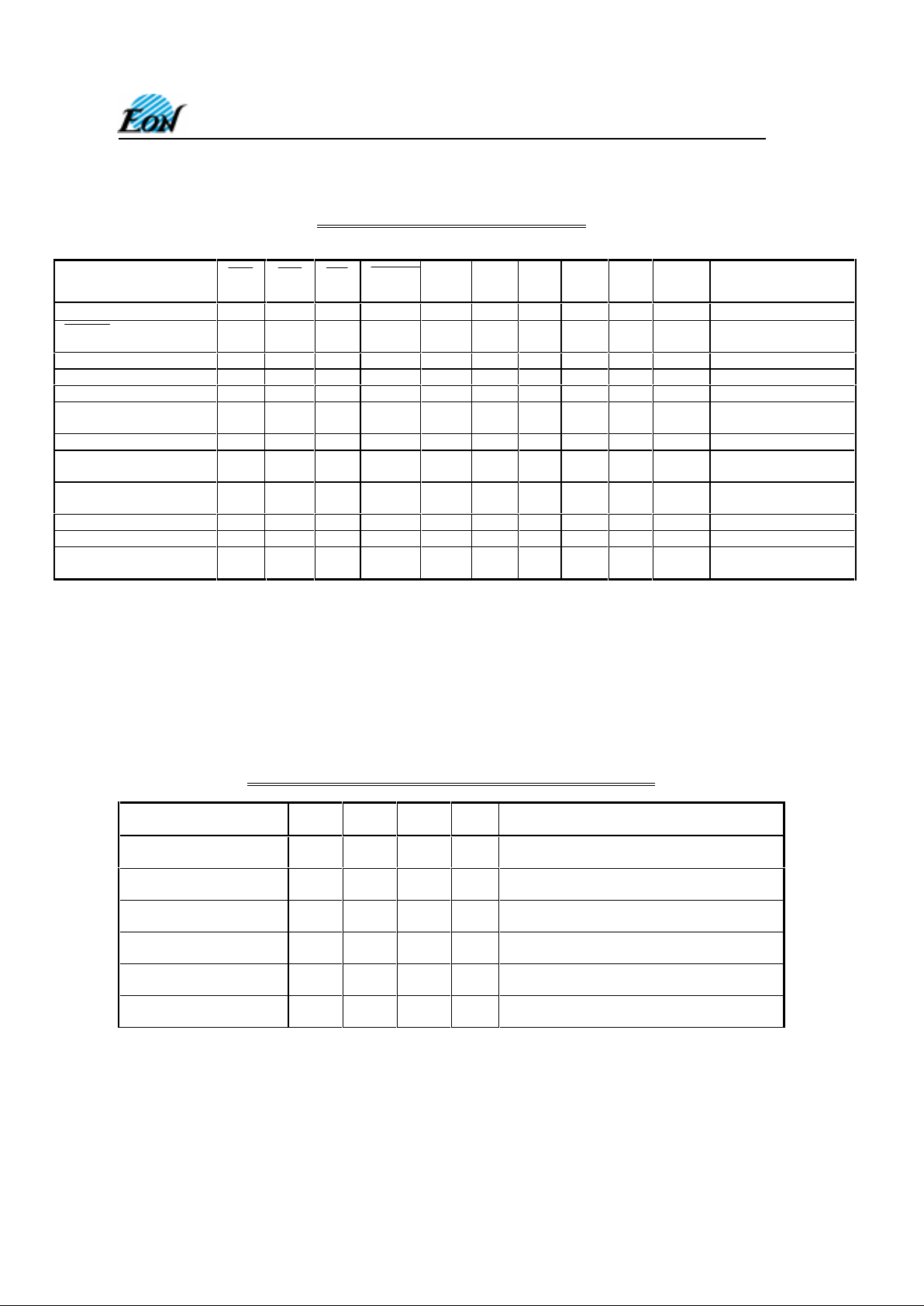

TABLE 1. PIN DESCRIPTION FIGURE 1. LOGIC DIAGRAM

Pin Name Function

A0-A17 Addresses

DQ0-DQ7 Data Input/Outputs

CE

Chip Enable

OE

Output Enable

WE

Write Enable

RESET

(n/a for

EN29F002N)

Hardware Reset

Sector Unprotect

Vcc Supply Voltage

(5V ± 10% )

Vss Ground

TABLE 2. BLOCK ARCHITECTURE

TOP BOOT BLOCK BOTTOM BOOT BLOCK

SECTOR ADDRESSES

SIZE (Kbytes)

ADDRESSES

SIZE (Kbytes)

6 3C000h - 3FFFFh 16 30000h - 3FFFFh 64

5 3A000h - 3BFFFh 8 20000h - 2FFFFh 64

4 38000h - 39FFFh 8 10000h - 1FFFFh 64

3 30000h - 37FFFh 32 08000h - 0FFFFh 32

2 20000h - 2FFFFh 64 06000h - 07FFFh 8

1 10000h - 1FFFFh 64 04000h - 05FFFh 8

0 00000h - 0FFFFh 64 00000h - 03FFFh 16

EN29F002T/B

8

DQ0 - DQ7A0 - A17

18

Vcc

WE

CE

OE

RESET

Vss

NC on EN29F002N

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

3

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

BLOCK DIAGRAM

RESET

WE

CE

OE

State

Control

Command

Register

Erase Voltage Generator

Input/Output Buffers

Program Voltage

Generator

Chip Enable

Output Enable

Logic

Data Latch

Y-Decoder

X-Decoder

Y-Gating

Cell Matrix

TimerVcc Detector

A0-A17

Vcc

Vss

DQ0-DQ7

Ad

d

r

e

s

s

L

a

t

c

h

Block Protect Switches

STB

STB

N/A on EN29F002N

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

4

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

FIGURE 2. PDIP

FIGURE 3. TSOP

EN29F002

FIGURE 4. PLCC

PLCC Top View

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

5

6

7

8

9

10

11

12

13

29

28

27

26

25

24

23

22

21

A14

A13

A8

A9

A11

OE

A10

CE

DQ7

4232

3131

30

14 16 18

15 17 19

20

DQ1 VSS DQ4

DQ2 DQ3 DQ5

DQ6

A12 A16 VCC

A15 VPP PGM

NC

PDIP Top View

VPP

A16

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

VSS

VCC

PGM

NC

A14

A13

A8

A9

A11

OE

A10

CE

DQ7

DQ6

DQ5

DQ4

DQ3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

A17

WE

RESET

WE

RESET

A15 RESET WE

A12 A16 V

CC

A17

N/A for EN29F002N

N/A for EN29F002N

RESET is not applicable for EN29F002N

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

5

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

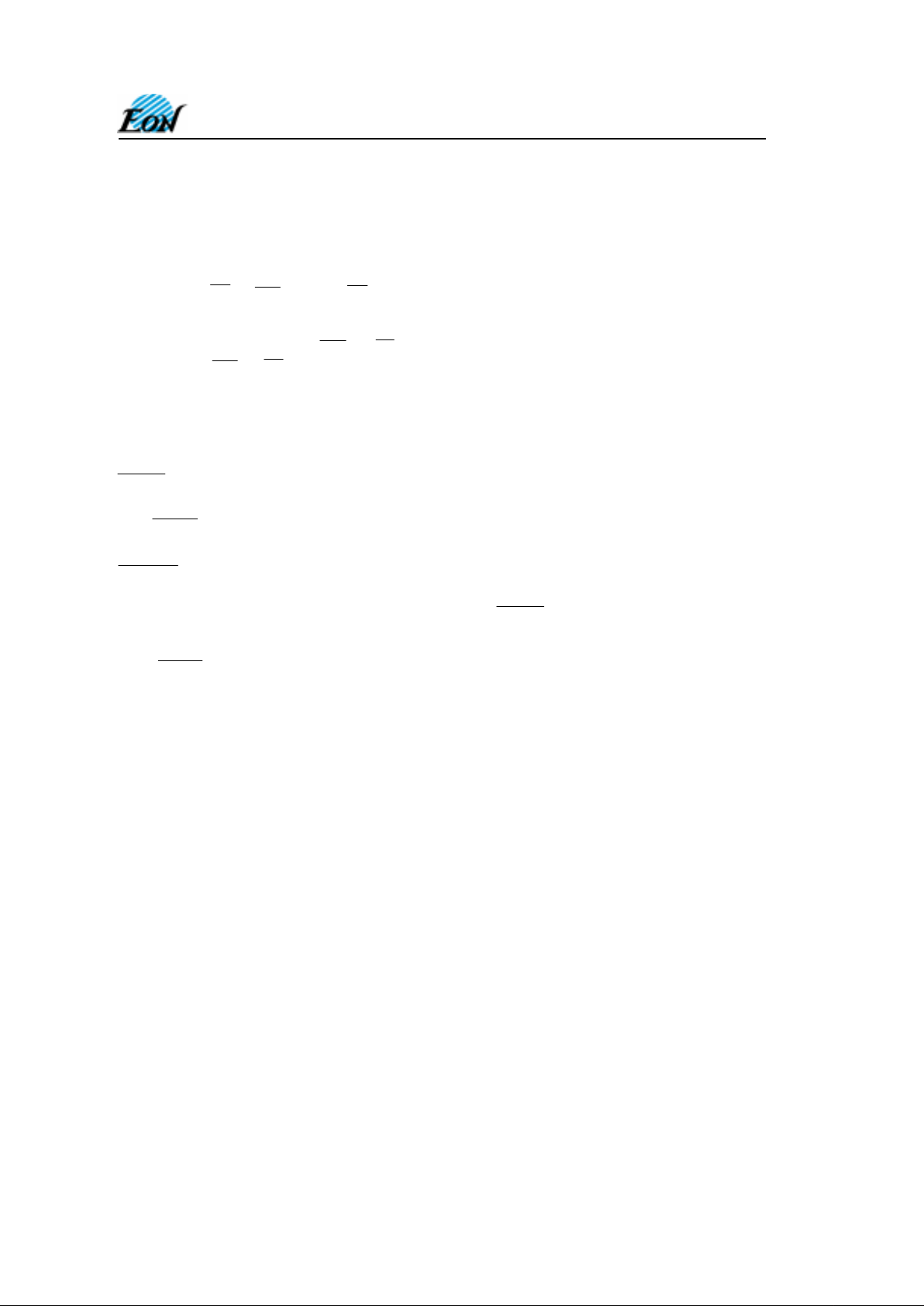

TABLE 3. OPERATING MODES

2M FLASH USER MODE TABLE

CE

WE OE

RESET

A9 A8 A6 A1 A0 Ax/y DQ(0-7)

USER MODE

RESET

(n/a for EN29F002N)

X X X L X X X X X X HI-Z

STANDBY H X X H X X X X X X HI-Z

READ L H L H A9 A8 A6 A1 A0 Ax/y DQ(0-7)

OUTPUT DISABLE L H H H A9 A8 A6 A1 A0 Ax/y HI-Z

READ

MANUFACTURER ID

L H L H VID L/H L L L X MANUFACTURER

ID

READ DEVICE ID L H L H VID L/H L L H X DEVICE ID(T/B)

VERIFY SECTOR

PROTECT

L H L H VID X L H L X CODE

ENABLE SECTOR

PROTECT

L L VID H VID X L X X X X

SECTOR UNPROTECT L L VID H VID X H H L X X

WRITE L L H H A9 A8 A6 A1 A0 Ax/y DIN(0-7)

TEMPORARY SECTOR

UNPROTECT

X X X VID X X X X X X X

NOTES:

1) L = V

IL

, H = VIH, VID = 11.0V ± 0.5V

2) X = Don’t care, either V

IH

or VIL

TABLE 4. DEVICE IDENTIFICTION

2M FLASH MANUFACTURER/DEVICE ID TABLE

A8 A6 A1 A0 DQ(7-0)

HEX

READ

MANUFACTURER ID

L L L L MANUFACTURER ID

7F

READ

MANUFACTURER ID

H L L L MANUFACTURER ID

1C

READ DEVICE ID

(Top Architecture)

L L L H DEVICE ID

7F

READ DEVICE ID

(Top Architecture)

H L L H DEVICE ID

92

READ DEVICE ID

(Bottom Architecture)

L L L H DEVICE ID

7F

READ DEVICE ID

(Bottom Architecture)

H L L H DEVICE ID

97

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

6

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

USER MODE DEFINITIONS

Reset Mode

EN29F002 features a Reset mode that res ets the program and erase operation immediately to read

mode. If reset (

RESET

= L) is executed when program or erase operation were in progress, the

program or erase which was term inated should be repeated since data will be corrupted. This pin is

not available for EN29F002N.

Standby Mode

The EN29F002 / EN29F002N has a CMOS-com patible standby mode which reduces the

current to <

1µA (typical). It is placed in CMOS-com patible standby when

CE

and the

RESET

pins are at VCC ±

0.5 V (

CE

pin only, for EN29F002N). The device also has a T TL-c ompatible standby mode which

reduces the maxim um V

CC

current to < 1m A. It is placed in TTL-c ompatible standby when CE and

RESET

pins are at VIH. Another method of entering standby mode uses only the

RESET

pin (n/a for

EN29F002N). When

RESET

pin is at VSS ± 0.3V, the device enters CMOS- compatible standby with

current typically reduced to < 1 µA. W hen

RESET

pin is at VIL, the device enters TTL-c ompatible

standby with current reduced to < 1mA. When in standby modes, the outputs are in a highimpedance state independent of the

OE

input.

Read Mode

The EN29F002 / EN29F002N has two control functions which m ust be satisfied in order to obtain

data at the outputs. Chip Enable (

CE

) is the power control and should be used for device selection.

Output Enable (

OE

) is the output control and should be used to gate data to the output pins,

provided the device is selected. Read is s elected when both

CE

and OE pins are held at VIL with

the

WE

pin held at VIH. Address access time (t

ACC

) is equal to the delay from s table addresses to

valid output data. Assuming that addresses ar e stable, chip enable access tim e (t

CE

) is equal to the

delay from stable

CE

to valid data at output pins. Data is available at the outputs after output enable

access time (t

OE

) from the falling edge of OE, assuming the CE has been LOW and addresses

have been stable for at least t

ACC

- tOE.

Output Disable Mode

When the

CE

or OE pin is at a logic high level (VIH), the output from the EN29F002 / EN29F002N

is disabled. The output pins are placed in a high impedance state.

Auto Select Identification Mode

The manufac turer and device type can be identified by hardware or software operations. T his mode

allows applications or programming equipment automatically matching the device with its

corresponding interface characteristics.

To activate the Auto Select Identification mode, the programming equipment must force 12.0 V ±

0.5V on address line A9 of the EN29F002T/B. T wo identifier bytes can then be sequenced from the

device outputs by toggling address lines A0 and A8 from V

IL

to VIH.

The manufactur er and device identif ication may also be read via the command regis ter. By following

the command sequence referenced in the Command Definition Table (Table 5). This method is

desirable for in-system identification (using only + 5.0V).

When A0 = A1 = A6 = V

IL

and by toggling A8 from VIL to V

IH,

the Manufacturer ID can be read as Eon

= 7F, 1C (hex) to identify EON . When A0 = V

IH

, A1 = A6 = V

IL,

and by toggling A8 from V

IL

to VIH, the

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

7

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

Device Code can be r ead as 7F, 92 (hex) for EN29F002T or as 7F, 97 (hex) for EN29F002B (See

Table 4). All identif iers for manufacturer and device codes possess odd par ity with the DQ7 defined

as the parity bit.

Write Mode

Write is used for device programming and erase through the command register. This mode is

selected with

CE

= WE = L and OE = H. The contents of the comm and register are the inputs to

the internal state machine. T he command register is a set of latches used to store the com mands

along with the addresses and data information needed to execute that com mand. Address latching

occurs on the falling edge of

WE

or CE (whichever occurs later) and data latching occur s on the

rising edge of

WE

or CE (whichever occurs first).

Temporary Sector Unprotect Mode

EN29F002 allows protected sectors to be tempor arily unprotected for m ak ing changes to data stored

in a protected sector in system (n/a f or EN29F002N). T o activate the tem por ary sector unprotect, the

RESET

pin must be set to a high voltage of VID (11V). In this mode, protected sectors can be

programmed or er ased by selecting the sector addresses. Once the high voltage, V

ID

, is removed

from

RESE

T

pin, all previously protected sectors will revert to their protected state.

RESET Hardware Reset Mode (not available on EN29F002N)

Resetting the EN29F002 device is perform ed when the

RESET

pin is set to VIL and kept low for at

least 500ns. The internal state machine will be reset to the read mode. Any program/erase

operation in progress during hardware reset will be terminated and data may be corrupted.

If the

RESET

pin is tied to the system r eset command, the device will be autom atically reset to the

read mode and enable the system’s m icroprocessor to read the boot-up firmware from the FLASH

memory.

COMMAND DEFINITIONS

The operations of the EN29F002 are selected by one or m ore commands written into the command

register to perform Read/Reset Mem ory, Read ID, Read Sector Protection, Program , Sector Eras e,

Chip Erase, Erase Suspend and Erase Resume. Commands are made up of data sequences

written at specific addresses via the c omm and register . The sequences for the specified operation

are defined in the Command Table (Table 5). Incorrect addresses, incorrect data values or

improper sequences will reset the device to the read mode.

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

8

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

Table 5. EN29F002 Command Definitions

Command

Sequence

Read/Reset

Write

Cycles

Req’d

1

st

Write Cycle

2

nd

Write Cycle

3

rd

Write Cycle

4

th

Write Cycle

5

th

Write Cycle

6th

Write Cycle

Addr Data Addr Data Addr Data Addr Data Addr Data Addr Data

Read/Reset

1 XXXh F0h RA RD

Read/Reset

4 555h AAh AAAh 55h 555h F0h RA RD

AutoSelect

Manufacturer ID

4 555h AAh AAAh 55h 555h 90h 000h/

100h

7Fh/

1Ch

AutoSelect Device ID

(Top Boot)

4 555h AAh AAAh 55h 555h 90h 001h/

101h

7Fh/

92h

AutoSelect Device ID

(Bottom Boot)

4 555h AAh AAAh 55h 555h 90h 001h/

101h

7Fh/

97h

AutoSelect Sector

Protect Verify

4 555h AAh AAAh 55h 555h 90h SA &

02h

00h/

01h

Byte Program

4 555h AAh AAAh 55h 555h A0h PA PD

Chip Erase

6 555h AAh AAAh 55h 555h 80h 555h AAh AAAh 55h 555h 10h

Sector Erase

6 555h AAh AAAh 55h 555h 80h 555h AAh AAAh 55h SA 30h

Sector Erase Suspend

1 xxxh B0h

Sector Erase Resume

1 xxxh 30h

Notes:

RA = Read Address: address of the memory location to be read. This one is a read cycle.

RD = Read Data: data read from locat i on RA duri ng Read operation. This one is a read cycle.

PA = Program Address: address of the memory loc ation to be programmed

PD = Program Data: data to be programmed at location PA

SA = Sector Address: address of the sector to be erased. Address bits A17-A13 uniquely select any sector.

Byte Programming Command

Programming the EN29F002 is per formed on a byte-by-byte basis using a four bus-cycle operation

(two unlock write c ycles followed by the Program Setup command and Program Data W rite cycle).

When the progr am comm and is ex ecuted, no additional CPU c ontr ols or timings are necessary. The

program operation is terminated autom atically by an internal timer. Address is latched on the f alling

edge of

CE

or

WE

, whichever is last; data is latched on the rising edge of CE or WE, whichever is

first. The program operation is completed when EN29F002 returns the equivalent data to the

programmed location.

Programming status may be checked by sampling data on DQ7 (

DATA

polling) or on DQ6 (toggle

bit). Changing data from 0 to 1 requires an erase operation. When programming time limit is

exceeded, DQ5 will produce a logical “1” and a Reset command can return the device to Read mode.

EN29F002 ignores commands written during Byte Programming. If a hardware

RESET

occurs

during Byte Programming, data at the programmed location may get corrupted. Programming is

allowed in any sequence and across any sector boundary.

Chip Erase Command

An auto Chip Erase algorithm is em ployed when the Chip Erase command sequence is perfor med.

Although the Chip Erase command requires six bus cycles: two unlock write cycles, a setup

command, two additional unlock write cycles and the chip erase command, the user does not need to

do anything else after that, except check to see if the operation has com pleted. The Auto Chip Erase

algorithm automatically program s and verifies the entire mem ory array for an all “0” pattern prior to

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

9

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

the erase. Then the EN29F002 will automatically time the eras e pulse width, verify the erase, return

the sequence count, provide a erase status through

DATA

POLLING (data on DQ7 is “0” dur ing the

operation and “1” when completed, provided the status is not read from a protected sector), and

returns to the READ mode after completion of Chip Erase.

Sector Erase Command

Sector Erase requires six bus cycles: two unlock write cycles, a setup command, two additional

unlock write cycles, and the Sector Erase command. Any sector may be erased by latching any

address within the desired sector on the falling edge of

WE

while the Erase Command (30H) is

latched on the rising edge of

WE

. This devic e does not support multiple sec tor erase comm ands.

Sector Erase operation will comm ence immediately after the firs t 30h command is written. The first

sector erase operation must finish before another sector erase command can be given.

The EN29F002 device automatically programs and verifies all memory locations in the selected

sector for an all “0” pattern prior to the erase. Unselected sectors are unaffected by the Sector Erase

command. T he EN29F002 requires no timing signals during sector erase. Erase is completed

when data on DQ7 becomes “1”, and the device returns to the READ mode after completion of

Sector Erase.

Erase Suspend / Resume Command

Erase suspend allows inter ruption of sector erase operations to perform data reads f rom sector not

being erased. Erase suspend applies only to Sector Erase operations.

EN29F002 ignores any commands during erase suspend other than the assertion of the

RESET

pin (n/a for EN29F002N) or Erase Resume commands. Writing erase resume continues erase

operations. Addresses are DON’T CARE when writing Erase Suspend or Erase Resume

commands.

EN29F002 takes 0.1 - 15 µs to suspend erase operations after receiving Erase Suspend com m and.

Check completion of erase suspend by polling DQ7 and/or DQ6. EN29F002 ignores redundant

writes of erase suspend command.

EN29F0002 defaults to eras e-suspend-read mode while an erase operation has been suspended.

While in erase-suspend-read mode, EN29F002 allows reading data in any sector not undergoing

sector erase, which is treated as standard read mode.

Write the Resume command 30h to continue operation of Sector erase. En29F002 ignores

redundant writes of the Resume com mand. En29F002 perm its multiple suspend/resum e operations

during sector erase.

Sector Protect and Unprotect

The hardware sector protection feature disables both program and erase operations in any sector.

The hardware sector unprotection feature re- enables both pr ogr am and erase operation in previously

protected sectors.

Sector protection/unprotection mus t be implem ented using progr amm ing equipm ent. The proc edure

requires a high voltage (V

ID

) on address pin A9 and the control pins. Contact Eon Silicon Devic es,

Inc. for an additional supplement on this feature.

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

10

EN29F002 / EN29F002N

Rev. C, Issue Date: 2001/ 07/05

WRITE OPERATION STATUS

DQ7

DAT

A

Polling

The EN29F002 provides

DATA

Polling on DQ7 to indicate to the host system the status of the

embedded operations. The

DATA

Polling feature is active during the Byte Programm ing, Sector

Erase, Chip Erase, Erase Suspend. (See Table 6)

When the Byte Programming is in progress, an attempt to read the device will produce the

complement of the data last written to DQ7. Upon the completion of the Byte Programming, an

attempt to read the device will produce the tr ue data last written to DQ7. For the Byte Programm ing,

DATA

polling is valid after the rising edge of the fourth

WE

or CEpulse in the four-cycle sequence.

When the em bedded Erase is in progress, an attempt to read the device will produce a “0” at the

DQ7 output. Upon the completion of the em bedded Erase, the device will produce the “1” at the DQ7

output during the read. For Chip Erase, the

DATA

polling is valid after the rising edge of the six th

WE

or CE pulse in the six-c ycle sequence. For Sector Erase,

DATA

polling is valid after the last

rising edge of the sector erase

WE

or CEpulse.

DATA

Polling must be performed at any address within a sector that is being programmed or erased

and not a protected sector. Otherwise,

DATA

polling may give an inaccurate result if the address

used is in a protected sector.

Just prior to the com pletion of the embedded operations, DQ7 may change asynchronously when the

output enable (

OE

) is low. This means that the device is driving status information on DQ7 at one

instant of time and valid data at the next instant of time. Depending on when the system samples the

DQ7 output, it may read the status of valid data. Even if the device has c ompleted the embedded

operations and DQ7 has a valid data, the data output on DQ0-DQ6 may be still invalid. The valid

data on DQ0-DQ7 will be read on the subsequent read attempts.

The flowchart for

DATA

Polling (DQ7) is shown on Flowchart 5. The

DATA

Polling (DQ7) timing

diagram is shown in Figure 8.

DQ6

Toggle Bit I

The EN29F002 provides a “Toggle Bit” on DQ6 to indicate to the host system the status of the

embedded programming and erase operations. (See Table 6)

During an embedded Program or Erase operation, suc cessive attem pts to read data from the device

at any address (by toggling

OE

or CE) will result in DQ6 toggling between “zero” and “one”. Once

the embedded Program or Erase operation is com plete, DQ6 will stop toggling and valid data will be

read on the next successive attem pts. During Byte Programming, the Toggle Bit is valid after the

rising edge of the fourth

WE

pulse in the four-cycle sequence. For Chip Erase, the T oggle Bit is valid

after the rising edge of the sixth-cycle sequence. For Sector Erase, the T oggle Bit is valid after the

last rising edge of the Sector Erase Command (30h)

WE

pulse.

In Byte Programming, if the sector being written to is protected, DQ6 will toggle for about

2µs, then stop toggling without the data in the sector having changed. In Sector Erase or Chip

Erase, if all selected sectors ar e protec ted, DQ 6 will toggle for about 100 µs . The chip will then return

to the read mode without changing data in all protected sectors.

Toggling either

CE

or OE will cause DQ6 to toggle.

Loading...

Loading...