EON EN27C01055T, EN27C01055PI, EN27C01055P, EN27C01055JI, EN27C01055J Datasheet

...

EN27C010 1Megabit EPROM (128K x 8)

FEATURES

EN27C010

•

Fast Read Access Time

:

-45, -55, -70, and -90ns

•

Single 5V Power Supply

•

Programming Voltage +12.75V

•

QuikRite

•

Typical programming time 20µs

•

Low Power CMOS Operation

• 1µ

•

30mA Operation (Max.)

•

CMOS- and TTL-Compatible I/O

•

High-Reliability CMOS Technology

TM

Programming Algorithm

A Standby (Typical)

•

Latch-Up Immunity to 100mA

from -1V to V

•

Two-Line Control (

•

Standard Product Identification Code

•

JEDEC Standard Pinout

•

32-pin PDIP

•

32-pin PLCC

•

32-pin TSOP (Type 1)

•

Commercial and Industrial Temperature

CC

+ 1V

OE & CE)

Ranges

GENERAL DESCRIPTION

The EN27C010 is a low-power 1-Megabit, 5V-only one-time-programmable (OTP) read-only

memory (EPROM). Organized into 128K words with 8 bits per word, it features QuikRite

address location programm ing, typically at 20µs per byte. Any byte can be accessed in less than

45ns, eliminating the need for W AIT states in high-performance microprocessor systems. The

EN27C010 has separate Output Enable (

OE ) and Chip Enable ( CE ) controls which eliminate

bus contention issues.

TM

single-

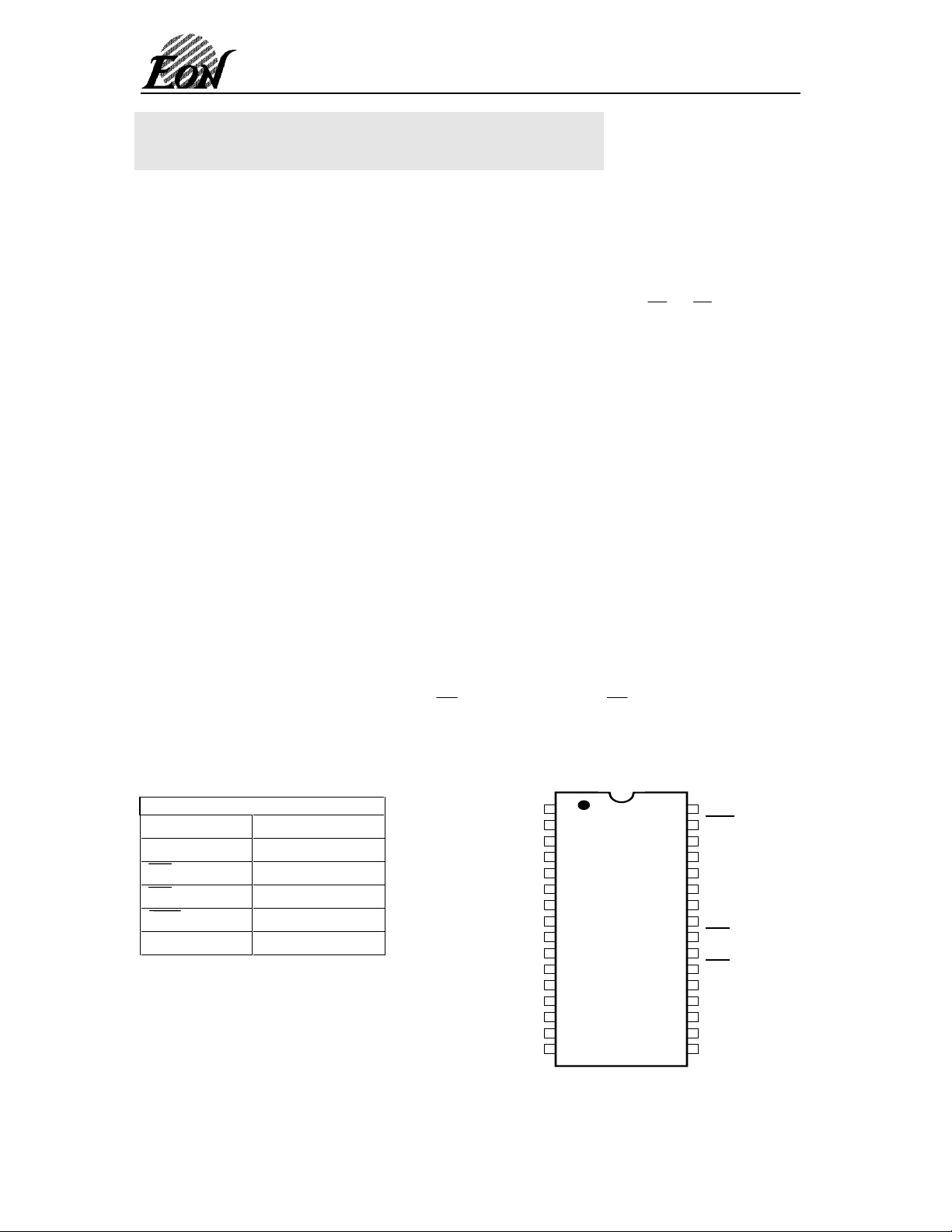

A7

A6

A5

A4

A3

A2

A1

A0

PDIP Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

VCC

PGM

NC

A14

A13

A8

A9

A11

OE

A10

CE

DQ7

DQ6

DQ5

DQ4

DQ3

FIGURE 1. PDIP

Pin Name Function

A0-A16 Addresses

DQ0-DQ7 Outputs

VPP

A16

A15

A12

CE Chip Enable

OE Output Enable

PGM Program Strobe

NC No Connect

DQ0

DQ1

DQ2

VSS

4800 Great America Parkway Ste 202 Tel: 408-235-8680

Santa Clara, CA. 95054 Fax: 408-235-8685

1

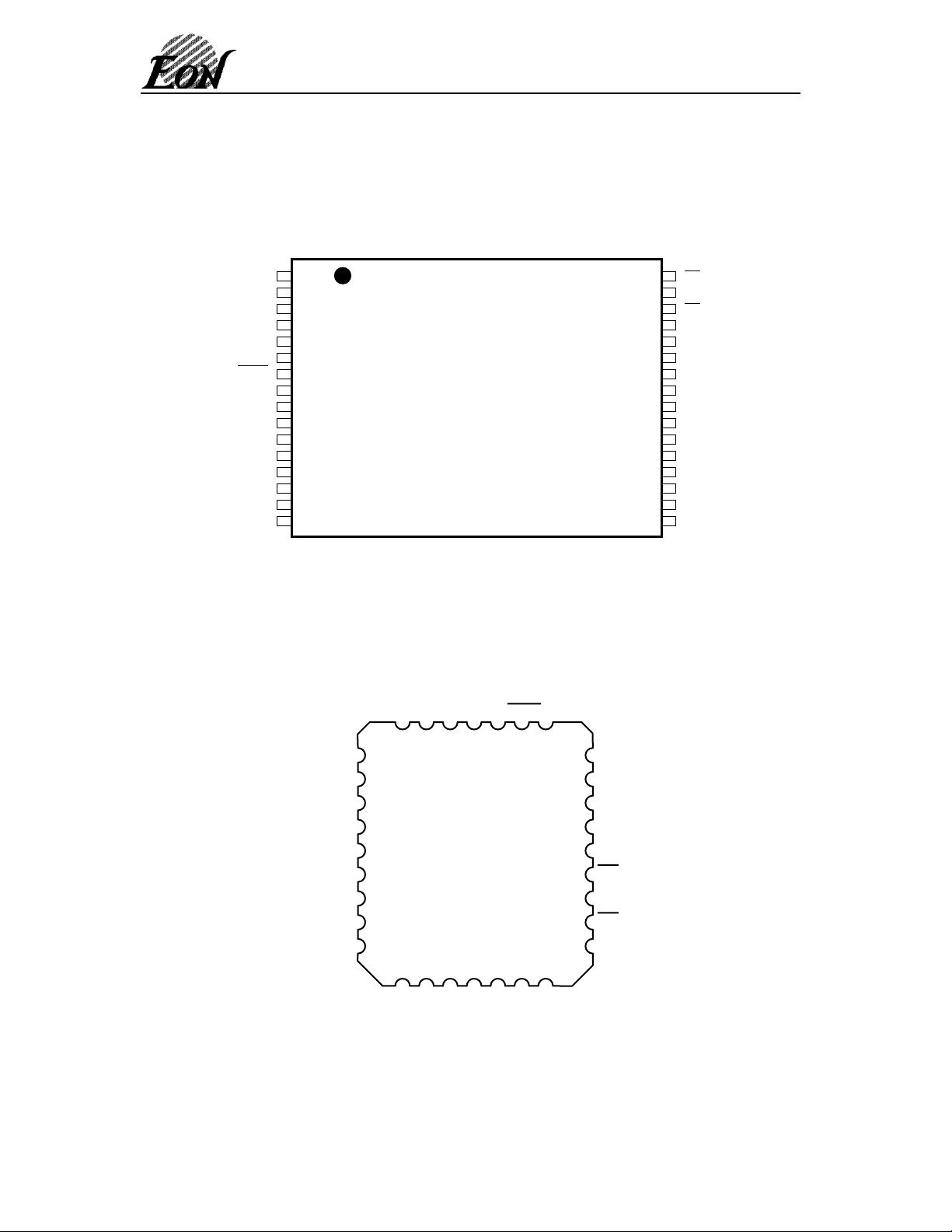

FIGURE 2. TSOP

TSOP

EN27C010

A11

A9

A8

A13

A14

NC

PGM

V

CC

V

PP

A16

A15

A12

A7

A6

A5

A4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

EN27C010

FIGURE 3. PLCC

PLCC Top View

A12 A16 VCC

A15 VPP PGM

NC

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

OE

A10

CE

DQ7

DQ6

DQ5

DQ4

DQ3

V

SS

DQ2

DQ1

DQ0

A0

A1

A2

A3

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

4232

5

3131

6

7

8

9

10

11

12

13

15 17 19

14 16 18

30

20

29

28

27

26

25

24

23

22

21

A14

A13

A8

A9

A11

OE

A10

CE

DQ7

DQ2 DQ3 DQ5

DQ1 VSS DQ4

4800 Great America Parkway Ste 202 Tel: 408-235-8680

Santa Clara, CA. 95054 Fax: 408-235-8685

2

DQ6

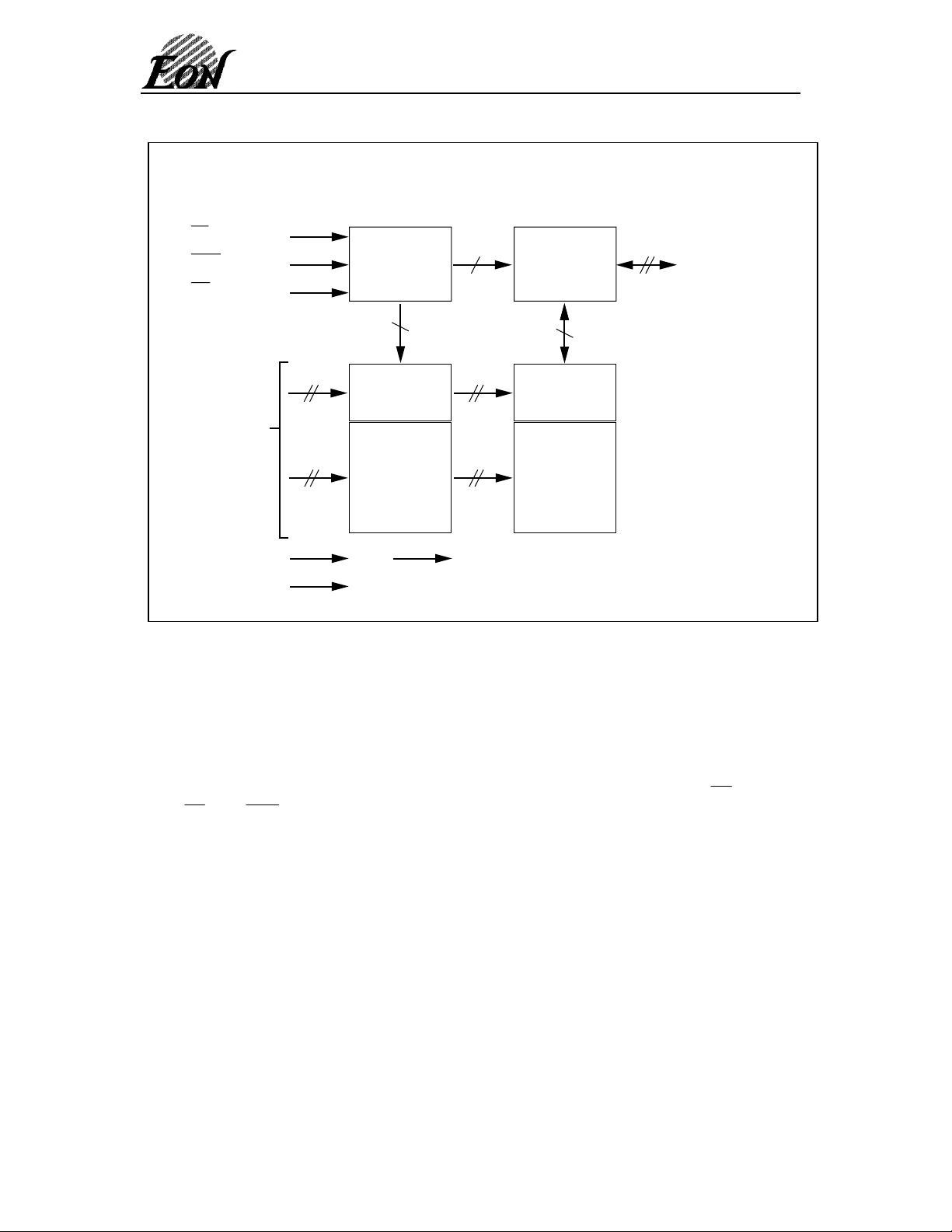

FIGURE 4. BLOCK DIAGRAM

EN27C010

CE

PGM

CONTROL

LOGIC

OE

Y-DECODER Y-SELECT

A0-A16

ADDRESS

INPUTS

X-DECODER

VCC

VPP

VSS

FUNCTIONAL DESCRIPTION

1024

1024

INPUT/

OUTPUT

BUFFERS

8

1M BIT

CELL

MATRIX

8

DQ0 - DQ7

THE QUIKRITETM PROGRAMMING OF THE EN27C010

When the EN27C010 is delivered, the chip has all 1M bits in the “ONE”, or

HIGH state. “ZEROs” are loaded into the EN27C010 through the procedure of programming.

The programming mode is entered when 12.75 ± 0.25V is applied to the V

and

CE and PGM are at V

. For programming, the data to be pr ogramm ed is applied with 8

IL

bits in parallel to the data pins.

The QUIKRITE

TM

programming flowchart in Figure 5 shows Eon’s interactive programming

algorithm. The interactive algorithm reduces programming time by using 20 µs to 100 µs

programming pulses and giving each address only as many pulses as is necessary in order to

reliably program the data. After each pulse is applied to a given address, the data in that

address is verified. If the data is not verified, additional pulses are given until it is verified or

until the maximum number of pulses is reached. This process is repeated while sequencing

through each address of the EN27C010. This part of the programming algorithm is done at

V

= 6.25V to assure that each EPROM bit is programmed to a sufficiently high threshold

CC

voltage. This ensures that all bits have sufficient margin. After the final address is completed,

the entire EPROM memory is read at V

4800 Great America Parkway Ste 202 Tel: 408-235-8680

Santa Clara, CA. 95054 Fax: 408-235-8685

CC

= V

= 5.25 ± 0.25V to verify the entire memory.

PP

3

pin, OE is at VIH,

PP

EN27C010

PROGRAM INHIBIT MODE

Programming of multiple EN27C010 in parallel with different data is also easily accomplished

by using the Program Inhibit Mode. Except for

may be common. A TTL low-level program pulse applied to an EN27C010

V

= 12.75 ± 0.25V, PGM LOW, and OE HIGH will program that EN27C010. A high-level

PP

CE input inhibits the other EN27C010 from being programmed.

PROGRAM VERIFY MODE

Verification should be performed on the programmed bits to determining that they were

correctly programmed. The verification should be performed with

V

, and VPP at it programming voltage.

IH

CE, all like inputs of the parallel EN27C010

CE input with

OE and CE at V

, PGM at

IL

AUTO PRODUCT IDENTIFICATION

The Auto Product Identification mode allows the reading out of a binary code from an EPROM that

will identify its manufacturer and type. This mode is intended for use by programming equipment

for the purpose of automatically matching the device to be programmed with its corresponding

programming algorithm. This mode is functional in the 25°C ± 5°C ambient temperature range

that is required when programming the EN27C010.

To activate this mode, the programming equipment must force 12.0 V ± 0.5V on address line A9

of the EN27C010. Two identifier bytes may then be sequenced from the device outputs by

toggling address line A0 from V

V

during Auto Product Identification mode.

IL

Byte 0 (A0 = V

) represents the manufacturer code, and byte 1 (A0 = VIH), the device code. For

IL

the EN27C010, these two identifiers bytes are given in the Mode Select Table. All identifiers for

manufacturer and device codes will possess odd parity, with the MSB (DQ7) defined as the parity

bit.

When A1 = VIL, the EN27C010 will read out the binary code of 7F, continuation code, to

signify the unavailability of manufacturer ID codes.

to VIH, when A1 = VIH. All other address lines must be held at

IL

4800 Great America Parkway Ste 202 Tel: 408-235-8680

Santa Clara, CA. 95054 Fax: 408-235-8685

4

Loading...

Loading...