Endura KP915GV User Manual

Endura KP915GV

Product Manual

www.radisys.com

007-01542-0001 December 2005

KP915GV Product Manual

Copyright © 2005 by RadiSys Technology (Ireland) Ltd.

All rights reserved.

EPC and RadiSys are registered trademarks of RadiSys Corporation. ASM, Brahma, DAI, DAQ, MultiPro, SAIB, Spirit,

and ValuePro are trademarks of RadiSys Corporation.

DAVID, MAUI, OS-9, OS-9000, and SoftStax are registered trademarks of RadiSys Microware Communications

Software Division, Inc. FasTrak, Hawk, and UpLink are trademarks of RadiSys Microware Communications Software

Division, Inc.

†

All other trademarks, registered trademarks, service marks, and trade names are the property of their respective

owners.

2

KP915GV Product Manual

Preface

Revision History

No. Date Description

1.0 September 2005

2.0 December 2005

Notational Conventions

This manual uses the following conventions:

• Screen text and syntax strings appear in this font.

• All numbers are decimal unless otherwise stated.

Revision history

• First Release

• Updates to clarify jumper default positioning, non-support

for S/PDIF In and Out on board, BIOS update to P28 version,

and editorial changes to some tables. Added details to OEM

Features section. No functional changes.

Notes indicate important information

about the product.

Tips indicate alternate techniques or

procedures that you can use to save

time or better understand the product.

The globe indicates a World Wide

Web address.

The book indicates a book or file.

ESD cautions indicate situations that

may cause damage to hardware via

electro-static discharge (ESD).

Cautions indicate potentially hazardous

situations which, if not avoided, may result

in minor or moderate injury or damage to

data or hardware. It may also alert you

about unsafe practices.

Warnings indicate potentially hazardous

situations which, if not avoided, can result

in death or serious injury.

Danger indicates imminently hazardous

situations which, if not avoided, will result

in death or serious injury.

Installation Notes

When installing this motherboard into a suitable chassis, refer to the following notes:

• Read and save all instructions.

•

• Pay attention to the safety warnings included in this document.

• When installing expansion cards, pay attention to the maximum loads detailed in this

• Route wiring away from sharp edges, heat sources and cooling fans.

• Pay attention to the thermal issues described in this document. The motherboard requires

Always disconnect Cord/Plug before installation or upgrade. Parts of the motherboard can

remain powered even when the power supply is switched off unless the cord is disconnected.

document. Use only UL approved peripheral cards.

suitable airflow to maintain an ambient temperature within its operating range.

3

KP915GV Product Manual

Safety and Approval Notices

LAN (Local Area

Network) Connector

Thermal Interface

Anti-static

Precautions

Electromagnetic

Compatibility

Legal Directives

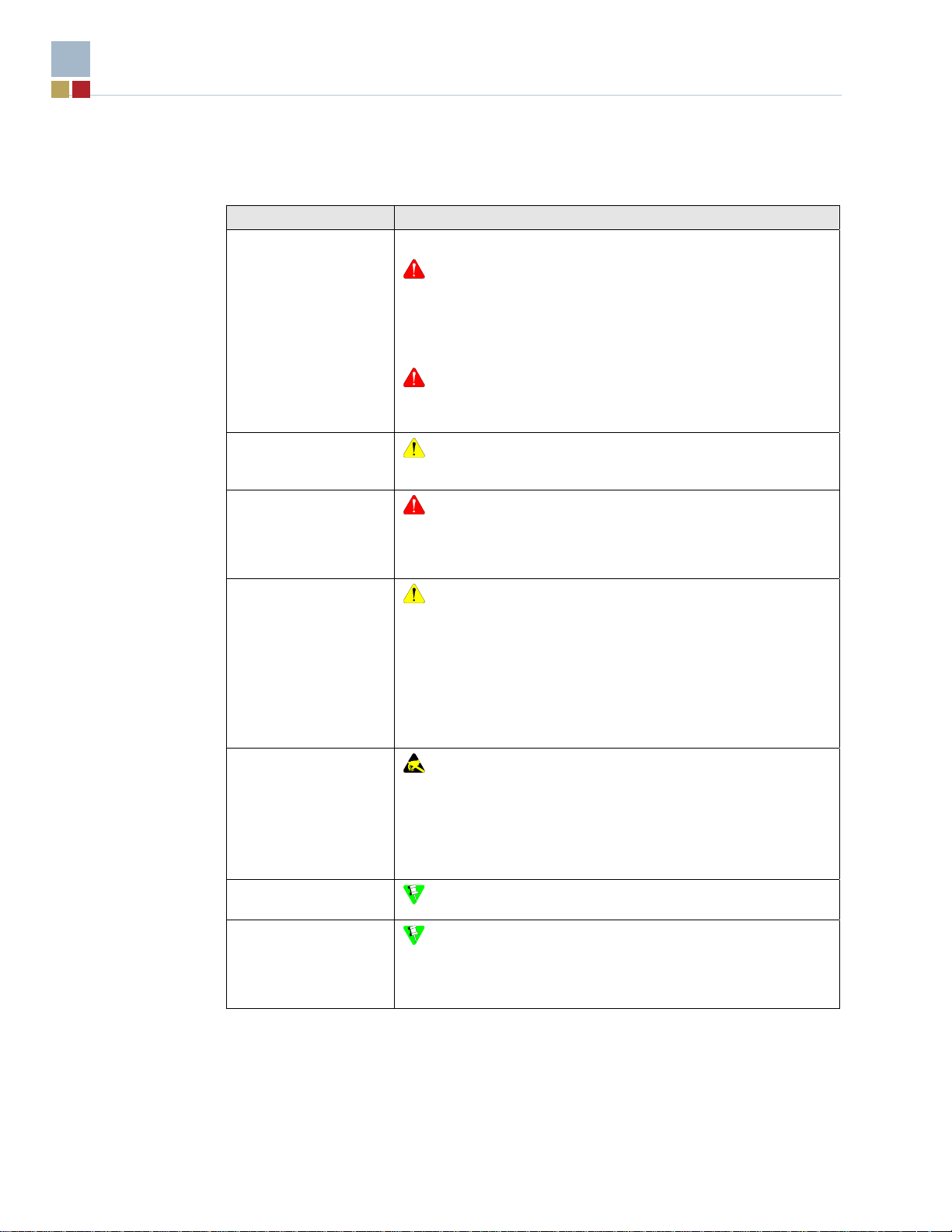

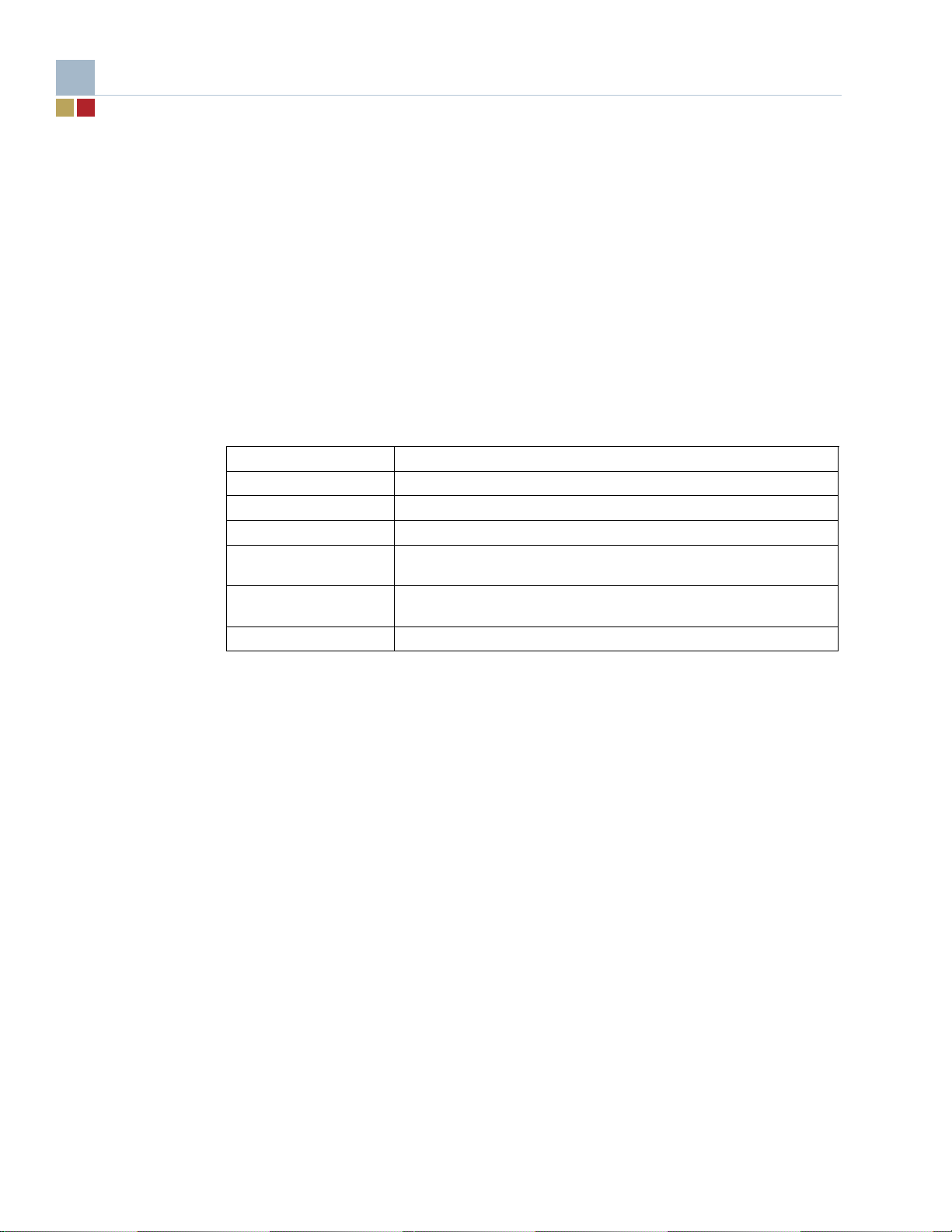

Safety and approval notices

Item Description

Battery

Material

Safety

This product contains a lithium cell.

• When removing or replacing the lithium cell, do not use a

conductive instrument as a short-circuit may cause the cell

to explode. Always replace the cell with one of the same

type. This product uses a CR2032 cell. Dispose of a spent

cell promptly – do not recharge, disassemble or incinerate.

Keep cells away from children.

• CAUTION! Danger of explosion if battery is incorrectly

replaced. Replace only with the same or equivalent type

recommended by the manufacturer. Dispose of batteries

according to the manufacturer's instructions.

This product may include an RJ45 LAN connector (see

product options). Do not connect to anything other than an

Ethernet LAN.

This product may contain thermal interface material between

devices and heatsinks. This can cause irritation and can stain

clothing. Avoid prolonged or repeated contact with the skin

and wash thoroughly with soap and water after handling. Avoid

contact with eyes and inhalation of fumes. Do not ingest.

This product contains static-sensitive components and should

be handled with care. It is recommended that the product be

handled in a Special Handling Area (SHA) as defined in

EN100015-1:1992. Such an area has working surfaces, floor

coverings and chairs connected to a common earth reference

point. An earthed wrist strap should be worn whilst handling.

Other examples of static-sensitive devices are the memory

modules and the processor. Failure to employ adequate antistatic measures can cause irreparable damage to components

on the motherboard.

This product is designed to meet the following EMC standards

when installed in a suitable chassis.

• FCC Class B (Title 47 of Code of Federal Regulations,

parts 2 & 15, subpart B)

• EN55022 Class B

• EN55024

This product complies with the American Safety Standard

UL60950 when installed in a suitable chassis.

This product complies with the relevant clauses of the

following European Directives.

Low Voltage Directive 73/23/EEC

EMC Directive 89/336/EEC

4

KP915GV Product Manual

Contents

1 OVERVIEW ................................................................................................................10

1.1 Accessories ………………………………………………………………………………………….. 11

1.2 Motherboard Layout................................................................................................................12

1.3 Block Diagram.........................................................................................................................14

1.4 Configuration ………………………………………………………………………………………….15

1.4.1 Operation Mode Selection Jumper (JP3) ................................................................................15

1.4.2 BIOS Boot Block Write Protection Jumper (JP2).....................................................................16

1.4.3 Clear CMOS Jumper (JP1) .....................................................................................................16

1.4.4 Front Panel Connections......................................................................................................... 16

1.4.5 Alternate Power LED............................................................................................................... 17

1.5 Installation of CPU ..................................................................................................................17

2 MOTHERBOARD DESCRIPTION............................................................................. 24

2.1 Processor Support ..................................................................................................................24

2.2 System Clocks ........................................................................................................................24

2.3 On board Clocking Block Diagram .......................................................................................... 25

2.4 Mechanical ……………………………………………………………………………………………25

2.5 Expansion Slot Types .............................................................................................................25

2.6 915GV Chipset Feature ..........................................................................................................26

2.7 Video .………………………………………………………………………………………………….27

2.8 Disks …………………………………………………………………………………………………..28

2.9 Audio …………………………………………………………………………………………………..28

2.10 Network ……………………………………………………………………………………………….29

2.11 I/O ……………………………………………………………………………………………………...30

2.12 Power Management ................................................................................................................ 30

2.13 System management ..............................................................................................................30

2.14 Security ………………………………………………………………………………………………..30

2.15 Programmable Controller (PLD).............................................................................................. 31

2.16 CMOS RAM and RTC ............................................................................................................. 31

2.17 Configuration ………………………………………………………………………………………….31

2.18 BIOS …………………………………………………………………………………………………..31

2.19 Operating Systems Support .................................................................................................... 32

2.20 Power Supplies .......................................................................................................................32

2.21 Reliability and Environmental..................................................................................................33

2.22 Regulatory Compliance...........................................................................................................34

3 SPECIFICATIONS .....................................................................................................35

3.1 Product Basis …………………………………………………………………………………………35

3.2 Non-Core Integrated Sub-systems..........................................................................................35

3.2.1 I/O Controller Hub 6 (ICH6).....................................................................................................35

3.2.2 Flash BIOS..............................................................................................................................38

3.3 Major Sub-systems .................................................................................................................39

3.3.1 Audio Interface ........................................................................................................................ 39

3.3.2 Hardware Management Interface............................................................................................41

3.3.3 Ethernet Interface....................................................................................................................42

3.3.4 Super I/O Interface..................................................................................................................43

3.4 Motherboard Power Consumption...........................................................................................48

5

KP915GV Product Manual

4 MOTHERBOARD BIOS.............................................................................................51

4.1 BIOS Features ........................................................................................................................51

4.2 Post and Boot ………………………………………………………………………………………..51

4.2.1 Hotkeys ...................................................................................................................................52

4.3 Setup Utility ………………………………………………………………………………………….. 52

4.3.1 Enter Setup .............................................................................................................................52

4.3.2 Configuration Reset ................................................................................................................52

4.3.3 Keyboard Command ...............................................................................................................52

4.3.4 Setup Configuration ................................................................................................................53

4.4 Power Management................................................................................................................ 93

4.4.1 ACPI Wake-up Support...........................................................................................................93

4.5 Hardware Monitor and Auto Fan Control.................................................................................93

4.5.1 Hardware Monitor....................................................................................................................93

4.5.2 Automatic Fan Control ............................................................................................................93

4.6 Power LED ……………………………………………………………………………………………93

4.7 CPLD …………………………………………………………………………………………………. 94

4.7.1 POST Code Display ................................................................................................................94

4.7.2 BIOS Protection ......................................................................................................................94

4.7.3 LAN Controller.........................................................................................................................94

4.8 TPM ……………………………………………………………………………………………………94

4.9 Normal, Configure and Recovery Mode..................................................................................94

4.9.1 Normal Mode ..........................................................................................................................95

4.9.2 Configure Mode.......................................................................................................................95

4.9.3 Recovery Mode ....................................................................................................................... 95

4.10 Update and Recovery Diskette ...............................................................................................95

4.10.1 Update Diskette.......................................................................................................................95

4.10.2 Recovery Diskette ................................................................................................................... 95

4.11 Tamper Detection....................................................................................................................95

4.12 OEM Features......................................................................................................................... 95

4.12.1 POST Logo Change................................................................................................................95

4.12.2 CMOS Default Change ...........................................................................................................96

4.13 PXE ……………………………………………………………………………………………………96

4.14 BIOS Flash Usage Map ..........................................................................................................97

4.15 Processor Microcode Support.................................................................................................97

4.16 SMBIOS ……………………………………………………………………………………………… 97

4.17 Post Code Technical Description ..........................................................................................102

4.18 POST Beep ………………………………………………………………………………………….104

4.19 SMBus Device Configuration ................................................................................................104

5 CUSTOMER SUPPORT...........................................................................................105

A TECHNICAL REFERENCE......................................................................................106

A.1 I/O Map ………………………………………………………………………………………………106

A.2 PCI Interrupt Allocation .........................................................................................................107

A.3 PCI Device Assignments.......................................................................................................108

A.4 SMBus Resource Allocation..................................................................................................108

A.5 ISA Interrupt Allocation .........................................................................................................109

A.6 ISA DMA Channel Allocation ................................................................................................109

A.7 BIOS Organization ................................................................................................................110

6

KP915GV Product Manual

B CONTROL REGISTERS.......................................................................................... 111

B.1 Index Register.......................................................................................................................111

B.2 Watchdog Control ................................................................................................................. 111

B.3 Watchdog Kick ......................................................................................................................112

B.4 Watchdog Status................................................................................................................... 112

B.5 Watchdog Timeout Period..................................................................................................... 113

B.6 General Purpose I/O Port 1...................................................................................................113

B.7 General Purpose I/O Port 2 and Control ...............................................................................113

B.8 PWM Control ………………………………………………………………………………………..114

B.9 Processor Identification......................................................................................................... 114

B.10 Controller Part Number .........................................................................................................115

C CONNECTOR DESCRIPTIONS .............................................................................. 116

C.1 Connector Part Numbers ...................................................................................................... 116

C.2 PCI-E Expansion Slot (ADD2 card mode) ............................................................................. 117

C.3 PCI Expansion Slot ...............................................................................................................118

C.4 PCI Express x1 Slot ..............................................................................................................119

7

KP915GV Product Manual

Figures

Figure 1. KP915GV Board Layout.............................................................................................12

Figure 2. KP915GV Block diagram ...........................................................................................14

Figure 3. Jumpers .....................................................................................................................15

Figure 4. Clocking Block Diagram.............................................................................................25

Figure 5. KP915GV Board Slot Layout......................................................................................28

Figure 6. Audio Jack Socket and ATAPI Connectors................................................................29

Figure 7. SST 49LF004B Functional Block Diagram.................................................................38

Figure 8. SigmaTel STAC9200 High Definition Block Diagram.................................................40

Figure 9. NS LM96000CIM Block Diagram ...............................................................................41

Figure 10. PC8374K Block Diagram ...........................................................................................43

Figure 11. BIOS ROM Addresses .............................................................................................110

Tables

Revision history .................................................................................................................................3

Safety and approval notices ..............................................................................................................4

Product Specification Overview .......................................................................................................10

Table 1. KP915GV Motherboard ...................................................................................................26

Table 3. ACPI Power States..........................................................................................................30

Table 4. Power Supply Connector.................................................................................................32

Table 5. Environmental Specifications...........................................................................................33

Table 6. Regulatory Testing* .........................................................................................................34

Table 7. References ....................................................................................................................105

Table 8. I/O Map..........................................................................................................................106

Table 9. PCI Interrupt Allocation..................................................................................................107

Table 10. PCI Device Assignments .............................................................................................108

Table 11. SMBus Resource Allocation ........................................................................................108

Table 12. ISA Interrupt Allocation ................................................................................................109

Table 13. ISA DMA Channel Allocation .......................................................................................109

Table 14. Connector part numbers ..............................................................................................116

Table 15. ADD2 Expansion Slot ..................................................................................................117

Table 16. PCI Expansion Slot......................................................................................................118

Table 17. PCI Express x1 Slot (PCI-E x1) ...................................................................................119

Table 18. P/S2 Mouse and P/S2 Keyboard .................................................................................119

Table 20. Serial Port....................................................................................................................120

Table 21. VGA Port .....................................................................................................................120

Table 22. 2 x Dual Stack USB Ports............................................................................................120

Table 24. 3 x Audio Jack .............................................................................................................121

Table 25. 1394 Header................................................................................................................121

Table 26. Front Panel Header .....................................................................................................121

Table 27. General Purpose I/O Headers ......................................................................................122

Table 28. Power Supply Connector .............................................................................................122

Table 29. Floppy Disk Connector ................................................................................................122

Table 30. ATA/100 Hard Drive Disk Connector ...........................................................................123

Table 32. 3X Internal Audio Headers...........................................................................................123

Table 33. TPM Header ...............................................................................................................124

8

KP915GV Product Manual

Table 34. Complex Programmable Logic Device (CPLD) JTAG Header....................................124

Table 35. Serial Port 2 Header ...................................................................................................124

Table 36. 4 X Internal USB Headers ...........................................................................................124

Table 37. Remote Thermal Sensor..............................................................................................125

Table 38. 3 X Fan Connector.......................................................................................................125

Table 39. SMBus Connector........................................................................................................125

Table 40. PS/2 Keyboard Header................................................................................................125

Table 41. PS/2 Mouse Header ....................................................................................................125

9

KP915GV Product Manual

1 Overview

Target applications are transaction terminals, medical, test & measurement, gaming, industrial

automation applications and other enterprise systems. This motherboard is part of the RadiSys

Endura product line, which is specifically targeted at embedded applications with a lifetime of 5

years. Products are fully revision controlled and any change to form, fit or function will be notified to

customers in advance via a Product Change Notification procedure

Item Description

Form Factor

Processor

Chipset

Memory

Video

Audio

Expansion

Capabilities

Power

Management

System

Management

Security

BIOS

I/O

Firewire

ATX 12” x 9.6”, 6 expansion slots

Support for an Intel® Pentium® 4 or Celeron D processor in a LGA775 socket

with an 800MHz or 533MHz FSB

Embedded processor requirements:

Intel® Pentium® 4 Processor 551 (3.4GHz 800MHz FSB 1MB L2)

Intel® Celeron™ D Processor 341 (2.93GHz 533MHz FSB 256KB L2)

Intel 915GV GMCH and Intel ICH6 I/O hub

Four DIMM sockets for DDR2 400/533 modules

Intel® GMA900 video controller integrated within chipset

Two channel stereo audio using the Sigmatel STAC9200 audio controller with

Intel HD Audio interface operation option

Two plug and play jacks on I/O panel (default MIC, line-out)

Three ATAPI connectors – line input, line output, and microphone input

On-board PC speaker (beep)

915GV ATX Three PCI, two x1 PCI-E, one ADD2 slots

(No PCI riser extension connector)

ACPI 2.0 supporting states S0, S3, S4, S5, and C0, C1, C2, C3

Voltage, temperature and fan monitoring (3 fans)

Lithium cell voltage monitoring

Automatic fan speed control (3 fans)

Programmable watchdog timer

SMBus header

Header for TPM 1.1 compliant module

Phoenix Award BIOS for the Intel 915G/GV chipset

Includes video BIOS and network boot

4Mbit Firmware Hub

Build option for socketed BIOS with write-protect jumper (enabled by the PLD

logic)

User defined BIOS default settings

Eight USB 2.0 ports - four on I/O panel and four on locking headers

General purpose I/O lines (13) with LCD character display support

Available with IEEE 1394b function with single port via an on-board header

connector (based on TI TSB82AA2 controller and TSB81BA3 transceiver)

.

Product Specification Overview

10

KP915GV Product Manual

Product Specification Overview

Item Description

Network

Disks

Super I/O &

H/W Monitor

Header

Connectors

I/O Panel

Intel 82573V (or ‘L) PCI-E Gbit Ethernet controller, co-lay with Intel 82562GZ

10/100 PHY (using the integrated MAC)

Available with second Intel 82573V (or ‘L) Gbit Ethernet controller

Four SATA ports with locking headers

Single Ultra ATA/100 interface supporting hard disks and ATAPI drives

One FDD interface

Nat Semiconductor PC8374K Super I/O and Nat Semiconductor LM9600

hardware monitoring device

Automatic fan speed control based on thermal monitoring (note that the BIOS

Setup is used for configuration and status information)

GPIO 2 x 10 pin with housing

SMbus 1 x 4 pin with housing

COM2 2 x 5 pin with housing

Kbd/Mouse 1 x 4 pin with housing

Remote thermal sensor 1 x 2 pin with housing

FDD 1 x FDD connector

1394b 2 x 5 pin connector

PS/2 keyboard and mouse

Analog VGA

Bi-directional/EPP/ECP parallel port

COM1 RS232

One or two dual USB + RJ45 stacks

Audio jack stack (2 jacks)

RadiSys PLD

Lattice LC4128ZC-75TN100C PLD for watchdog, GPIO, BIOS write-protect

support

1.1 Accessories

There are two I/O shields, one for the single Ethernet configuration and one for the dual Ethernet

configuration, and an available fan heat sink for the processor. These are separately orderable

product codes.

ATX-L KP IOSHLD ATX I/O Shield for KP915GV

11

KP915GV Product Manual

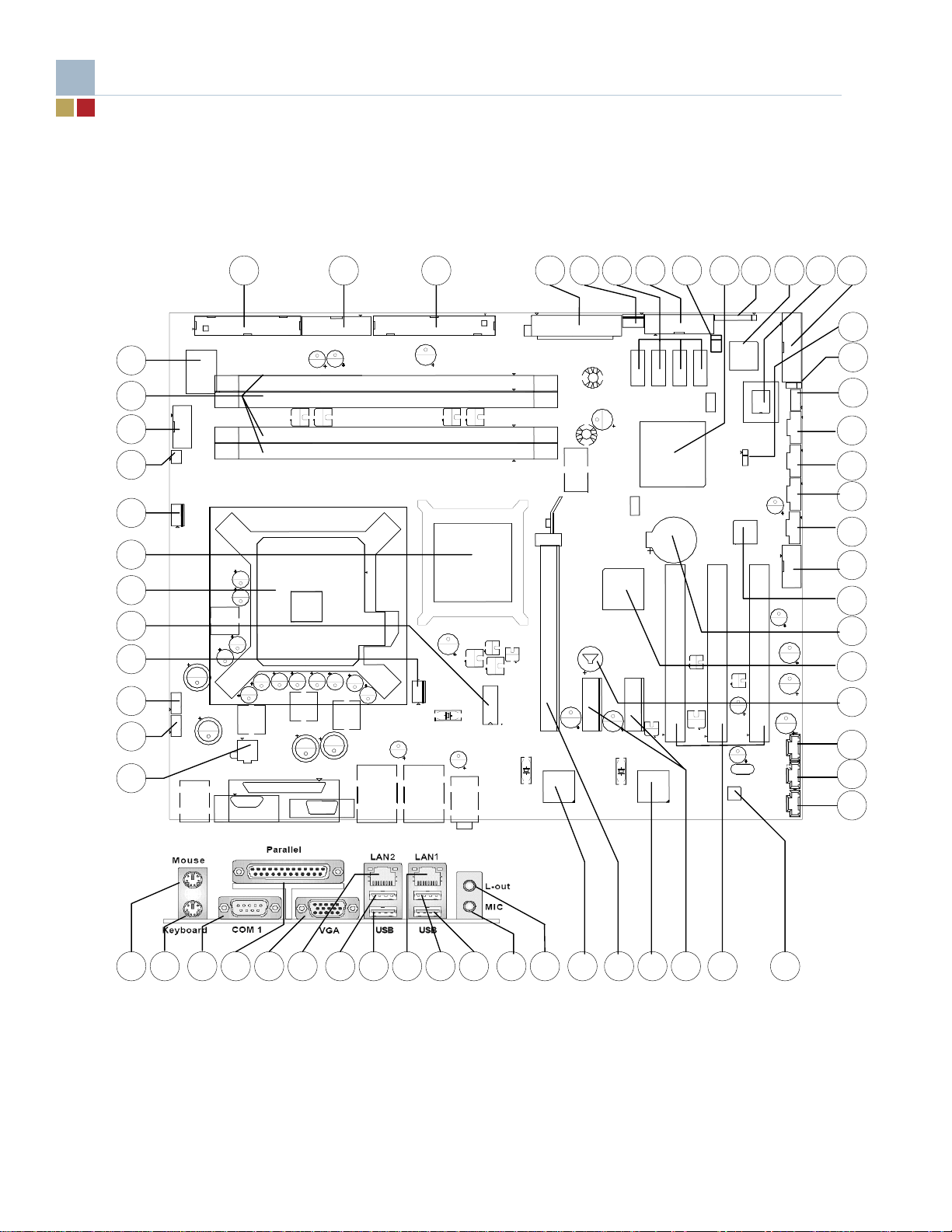

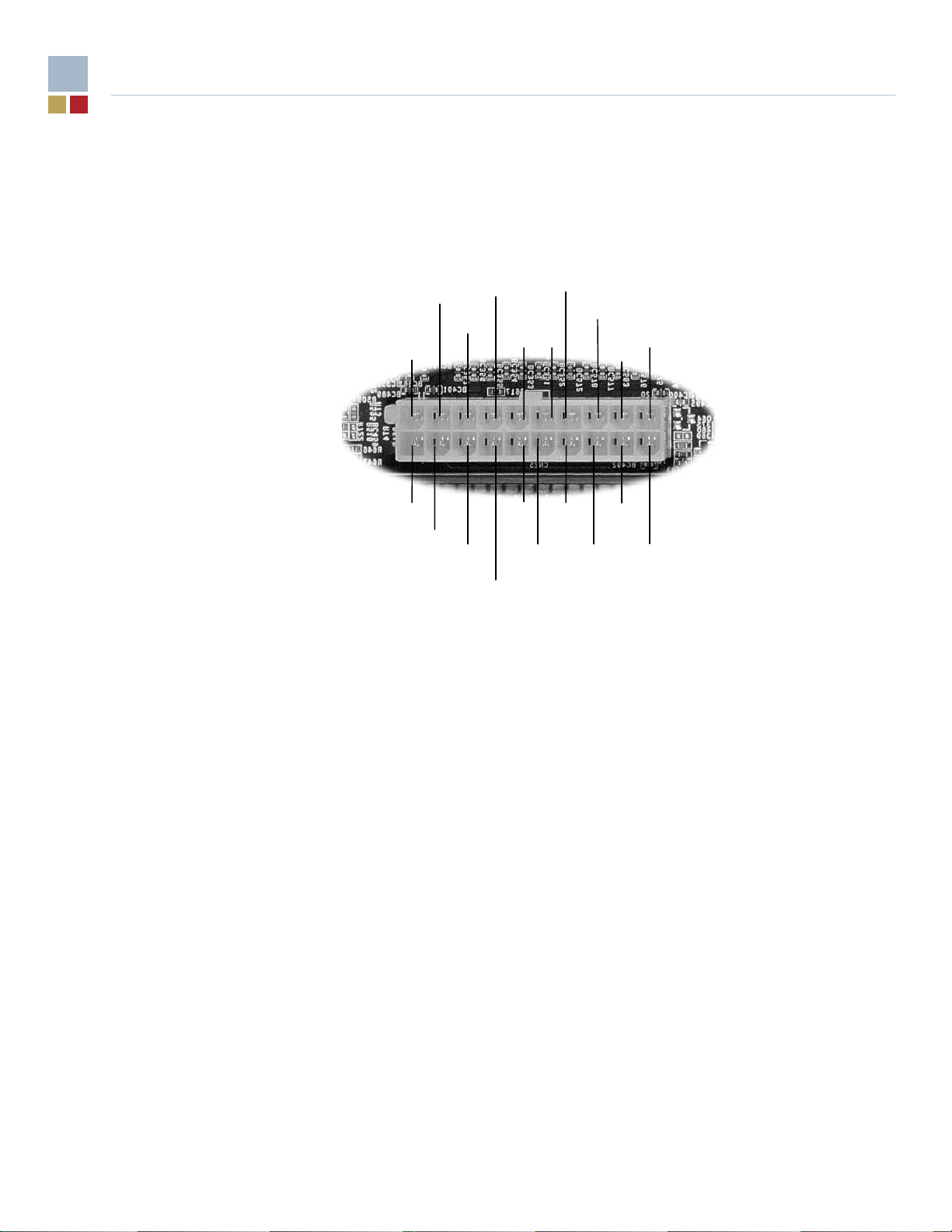

1.2 Motherboard Layout

Figure 1 shows the layout of the KP915GV motherboard with the major components identified.

Figure 1. KP915GV Board Layout

1

2

3

4

5

6

7

8

9

10

57 56

53545859

4950515255

4748

46

45

44

43

42

41

40

39

38

37

36

35

11

12

34

33

32

(Optional)

13 14 15 16 17 18 19 20 21 22 23 24 25

12

2726 28 29 30 31

KP915GV Product Manual

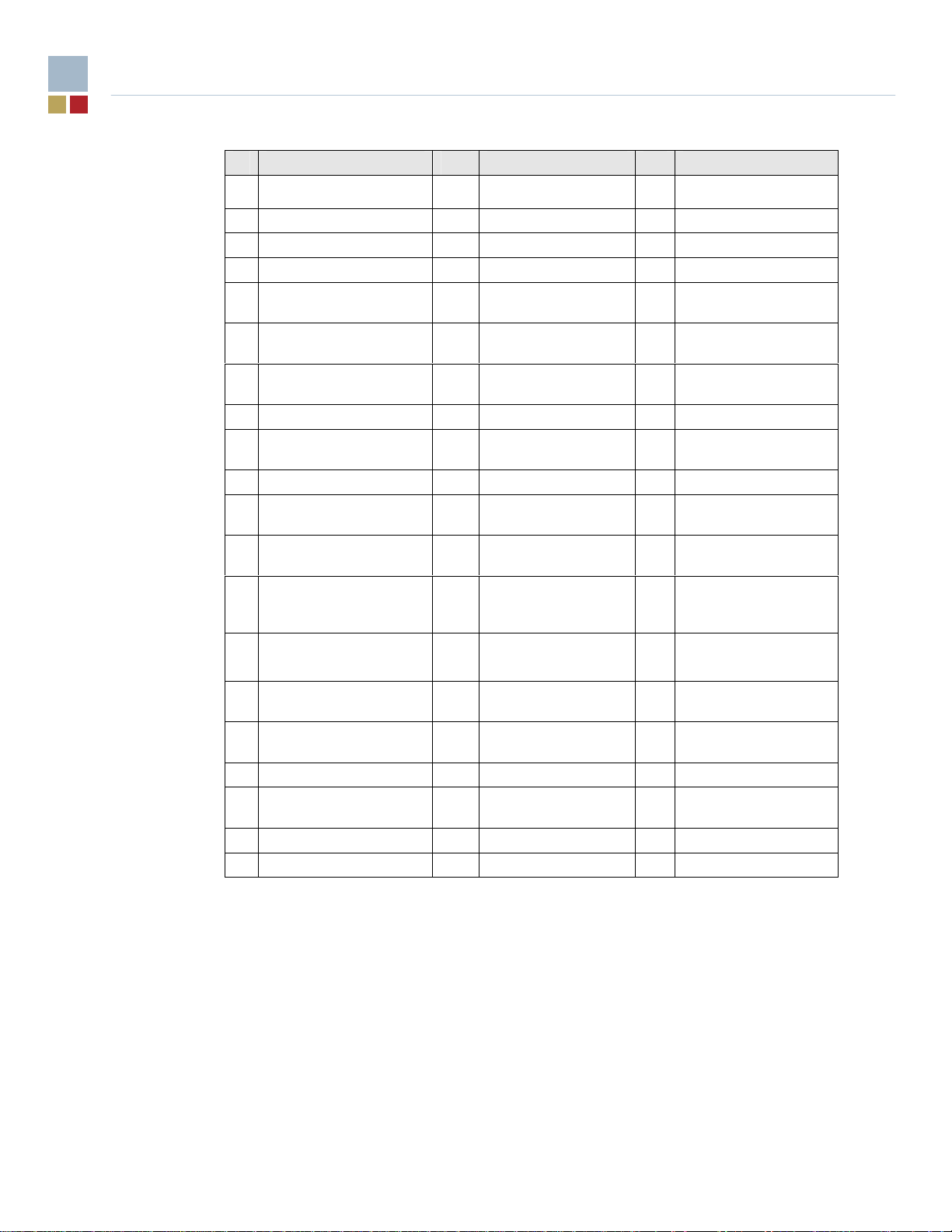

Component Identification

Description

1

Super IO

2

Memory sockets

3

Serial port 2 header

4

Remote thermal sensor

5

CPU FAN power

connector

6

Chipset GMCH

Description

Ethernet port 1

21

(option)

22

I/O panel USB port 7

23

I/O panel USB port 8

24

Microphone input jack

25

Audio line output jack

26

Ethernet controller 1

Description

41

USB port 2 header

42

USB port 3 header

43

USB port 4 header

44

SMBus header

45

BIOS ROM writeprotect jumper

46

Clear CMOS Jumper

(option)

7

775-pin socket for

27

ADD2 slot

47

GPIO header

processor

8

Clock generator

9

System fan power

28

Ethernet controller 2

29

PCI Express x1 slot

48

BIOS ROM (FWH)

49

CPLD control logic

connector

10

PS/2 mouse header

11

PS/2 keyboard header

30

PCI slot 2.3

31

HD Audio CODEC

50

JTAG header

51

I/O controller hub

(ICH6)

12

12V power connector

13

PS/2 mouse (green)

32

Stereo audio (CD) line

input header

33

Stereo audio

52

Operation Mode

Jumper

53

Front panel header

(microphone) input

header

14

PS/2 keyboard (purple)

15

Serial port

34

Stereo audio line

output header

35

Buzzer

54

SATA connectors

55

Chassis fan power

connector

16

Parallel port

36

1394 controller

56

Primary power supply

connector

17

VGA monitor

18

Ethernet port 2

37

38

RTC battery

1394 PHY

57

IDE connector

58

TPM header

(TSB81BA3I)

19

I/O panel USB port 5

20

I/O panel USB port 6

39

1394 header

40

USB port 1 header

59

FDD connector

13

KP915GV Product Manual

K

A

k

E

A

A

A

A

A

A

A

A

A

ATA

5

3

2

L

P

I-E

2

P

8

V

I

t

6

3

A

r

7

I-E

M

A

S

4

d

G

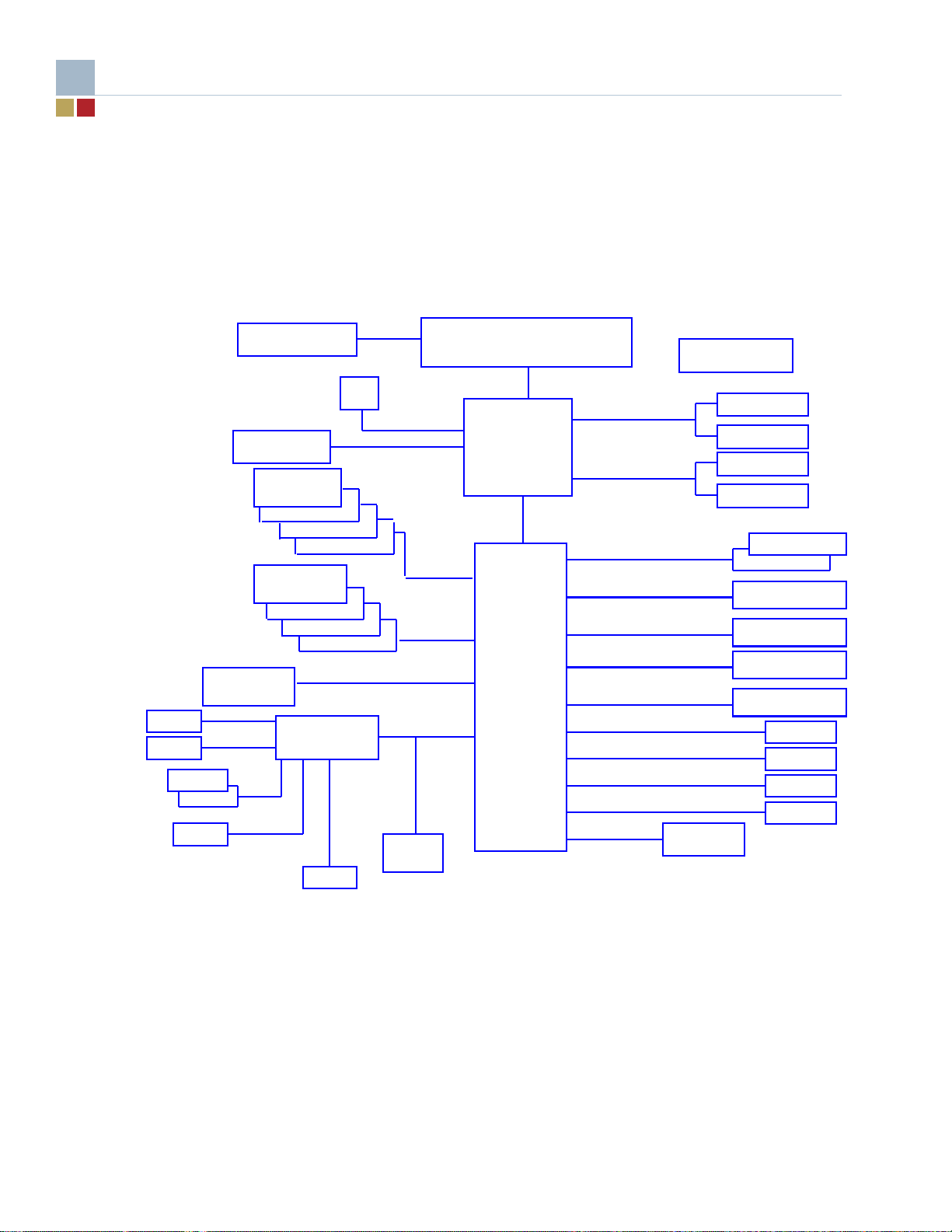

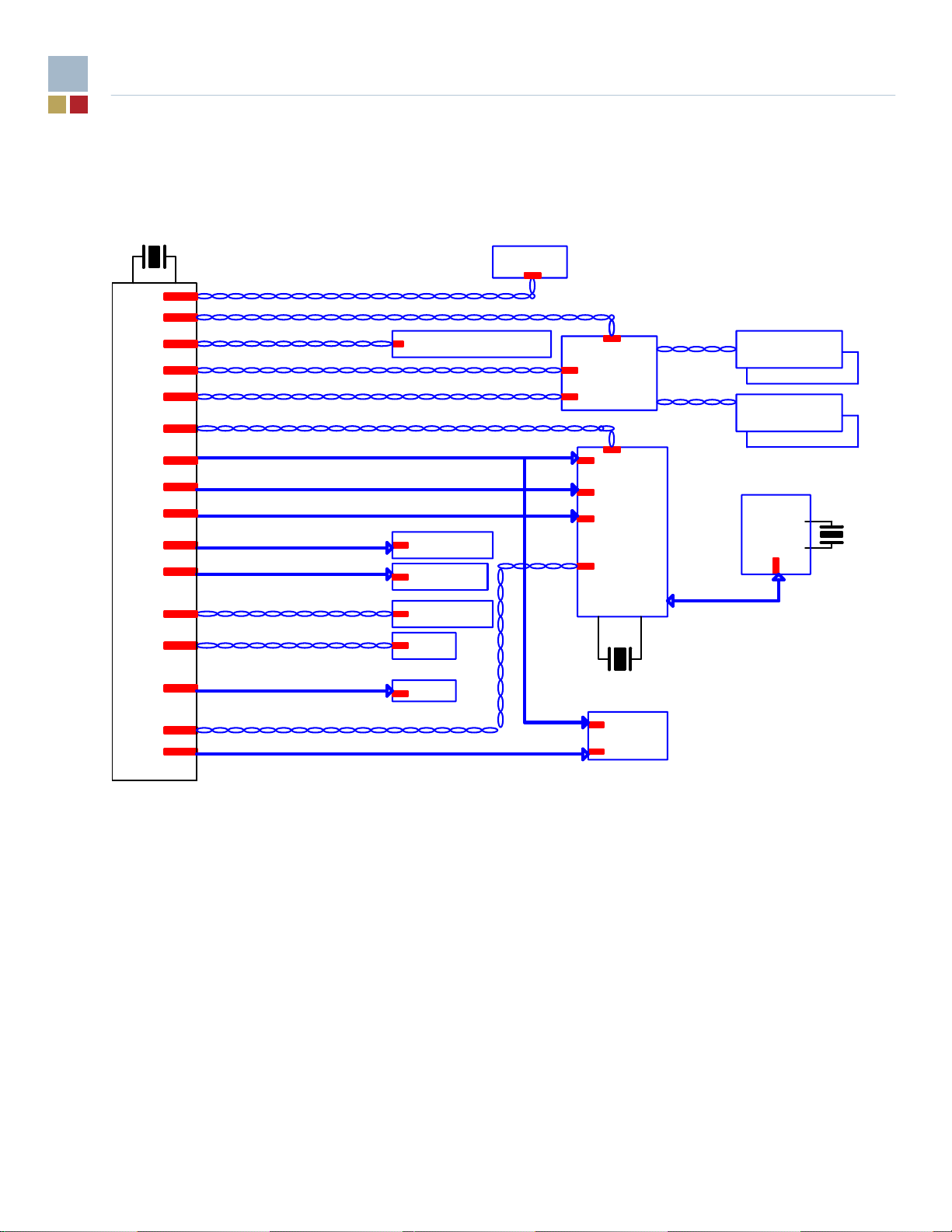

1.3 Block Diagram

Figure 2 shows the block diagram of the KP915GV motherboard.

Figure 2. KP915GV Block diagram

rescott, Tejas

entium 4 EE

GA775 processor

ocket T

800/533 FSB

GMCH

rantsdale

4 Lanes

Direct Media Interface (DMI)

ICH6

400/533MHz

400/533MHz

PCIE x1 Interface

PCIE x1 Interface

LAN-Lin

PCI Interface

PCI Interface

SAT

SAT

SAT

SAT

High Definition Audio

CK-410 Clock

Channel A DDR-2

Channel A DDR-2

Channel B DDR-2

Channel B DDR-2

zalia Codec

STAC9200

DIMM1

DIMM2

DIMM3

DIMM4

PC

Slot 1

PC

Slot

Intel 82573

Intel 82562GZ

TX Form Facto

PCI Slot 1,2&

1394

TSB82AA2

Serial AT

Port 1

Serial AT

Port 2

Serial AT

Port 3

Serial AT

Port 4

Keyboard

Mouse

Serial Port1

Serial Port2

Parallel

4 Phase PW

Intel SDVO Car

I/O Panel

USB2.0 Port

Header

USB2.0 Port1

TA100

IDE CONN 1

RD 10.1

USB2.0 Port

USB2.0 Port

USB2.0 Port

USB2.0 Port

USB2.0 Port

USB2.0 Port4

SUPER I/O

NS PC8374

Floppy

CRT

VG

PCIEx16 Por

USB2.0

USB2.0

LPC

FWH Flash

BIOS

Mb

14

KP915GV Product Manual

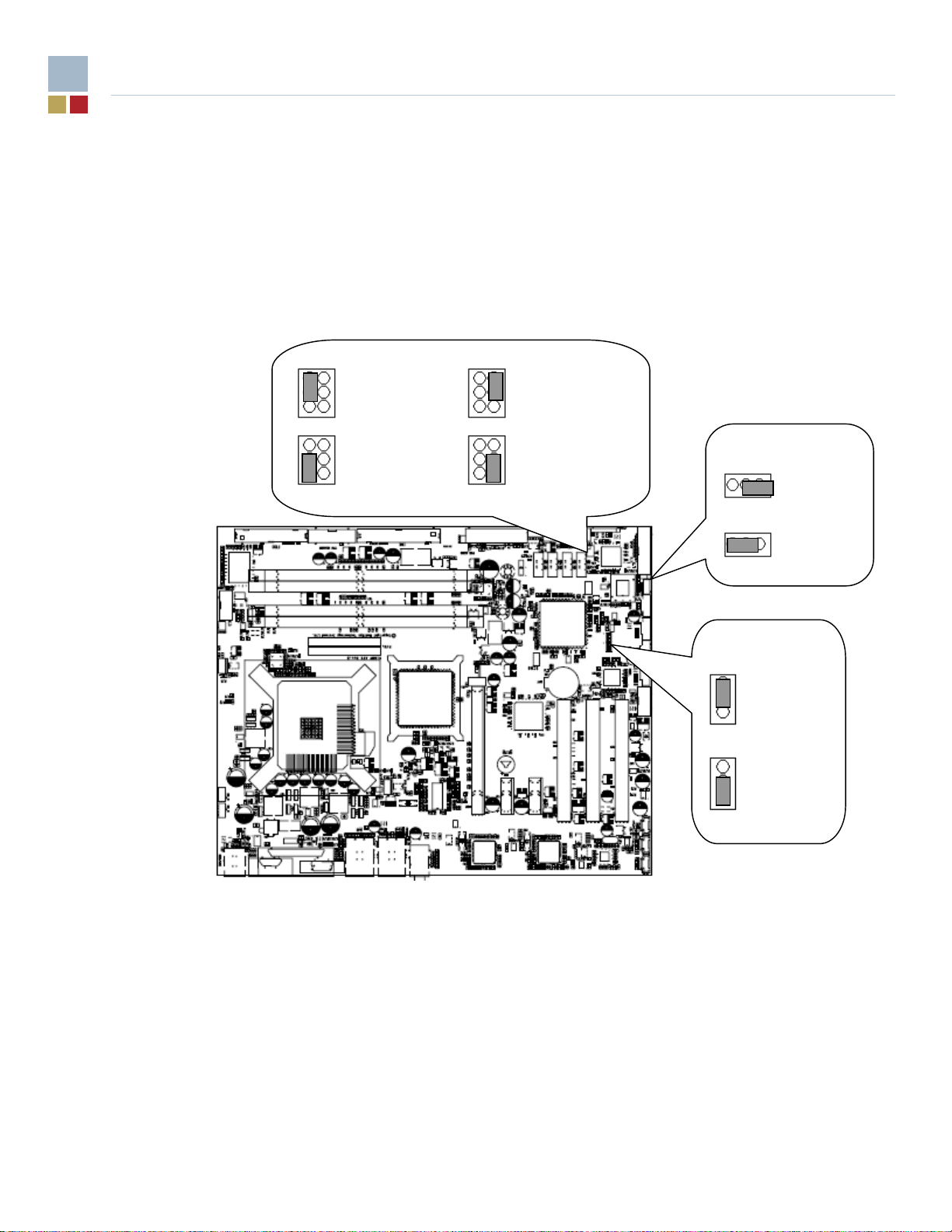

1.4 Configuration

The majority of the configuration of the motherboard is done through the Setup utility built into the

BIOS – discussed later in this document. There are, however, a number of jumpers that control the

operation of the motherboard as described below. Some jumpers are not fitted to certain products.

Figure 3. Jumpers

1 (No jumper = Recover) JP3 (No jumper = Protected)

Normal CPLD Write Enable

JP2

Configure CPLD Write

Protected

BIOS Unlock

1

1.4.1 Operation Mode Selection Jumper (JP3)

This jumper selects one of the following operating modes for the motherboard (pins 1, 3, 5) and

controls write capability for the CPLD content (pins 2, 4, 6).

Normal Mode (Jumper between pins 1 & 3) This is the factory default position the jumper

should be in for normal operation of the motherboard.

Configure Mode (Jumper between pins 3 & 5) With the jumper in this position the motherboard

automatically runs the BIOS Setup utility regardless of the state of the Setup

disable flag that can be set in the BIOS defaults. In this mode, the CMOS RAM

contents are ignored and the defaults are used to configure the motherboard.

(No jumper = Unlock)

BIOS Lock

1 JP1

Clear CMOS

Normal

(No jumper = Normal)

15

KP915GV Product Manual

Recover Mode (No jumper) With no jumper installed on pins 1, 3, and 5 recovery mode is entered.

The motherboard does not boot and waits until a valid recovery diskette is

detected and then copies new BIOS into the ROM. The motherboard must be

powered down and then re-powered with the jumper in the normal position before

normal operation can resume.

CPLD Write Enabled (Jumper between pins 2 & 4) In this position the contents of the CPLD can

be reprogrammed.

CPLD Write Protected (Jumper between pins 4 & 6) This is the factory default position. In this

position, or with no jumper on pins 2, 4, and 6, the contents of the CPLD are

protected from reprogramming.

1.4.2 BIOS Boot Block Write Protection Jumper (JP2)

(Jumper between pins 1 & 2) This is the factory default position. A jumper installed in this position.

or no jumper installed, enables changes to contents of BIOS ROM boot block (unlocked position).

Some motherboard applications may want to have boot block write-protected BIOS. This can be

provided via the BIOS boot block write protection jumper. If a jumper is installed between pins 2 &

3 (locked position), the contents of BIOS ROM boot block cannot be changed in any way.

1.4.3 Clear CMOS Jumper (JP1)

(Jumper between pins 2 & 3) This is the factory default position. Either this position or no jumper

installed, is the normal operating configuration. Installing a jumper between pins 1 & 2 clears

(resets) the CMOS.

1.4.4 Front Panel Connections

The primary controls and indicators for the motherboard are connected via the front panel

connector using either a single ribbon cable to a ‘front panel’ assembly, or using a number of small

PC-standard connectors. The functions are described below. See appendix B for the connector pinout information.

Power LED

Connects either a single-color LED (usually green) or a two-terminal bi-color LED (usually

green/yellow) to indicate the powered status of the motherboard. In both cases, the ‘green’ anode

should be attached to pin 2 of the front panel connector. Refer to the Enhanced Power

Management LED portion in section 3.3.4.4 of this document for further information.

Power Switch

If the motherboard is used with a soft-switch power supply, a momentary switch should be

connected between pins 6 and 8 of the power switch connections on the front panel connector. If

the switch is closed for greater than approximately 4 seconds, the motherboard powers off

immediately, regardless of the state of the operating system, losing any system context information.

This input is redundant when using a hard-switch power supply.

Reset Switch

If used, a momentary switch connected between pins 5 and 7 will cause the motherboard to restart

when closed.

Hard Disk LED

To indicate hard disk activity on either of the two ATA channels, a single color LED should be

connected between pins 1 (anode) and 3.

Speaker

Connect an external speaker between pins 10 and 12 or 10 and 16. This is used only for the PC

‘beep’ functions. The speaker should typically be 8Ω.

16

KP915GV Product Manual

r

p

Tamper Switch

To make use of the tamper detection logic of the motherboard, connect a momentary switch

between pins 18 and 20. The switch should be open when the chassis is closed.

1.4.5 Alternate Power LED

The power LED function on the front panel connector is duplicated on the Alternate Power LED

connector for use with LEDs cabled to a 3-pin connector. Do not use both the primary (front panel)

and alternate connectors simultaneously.

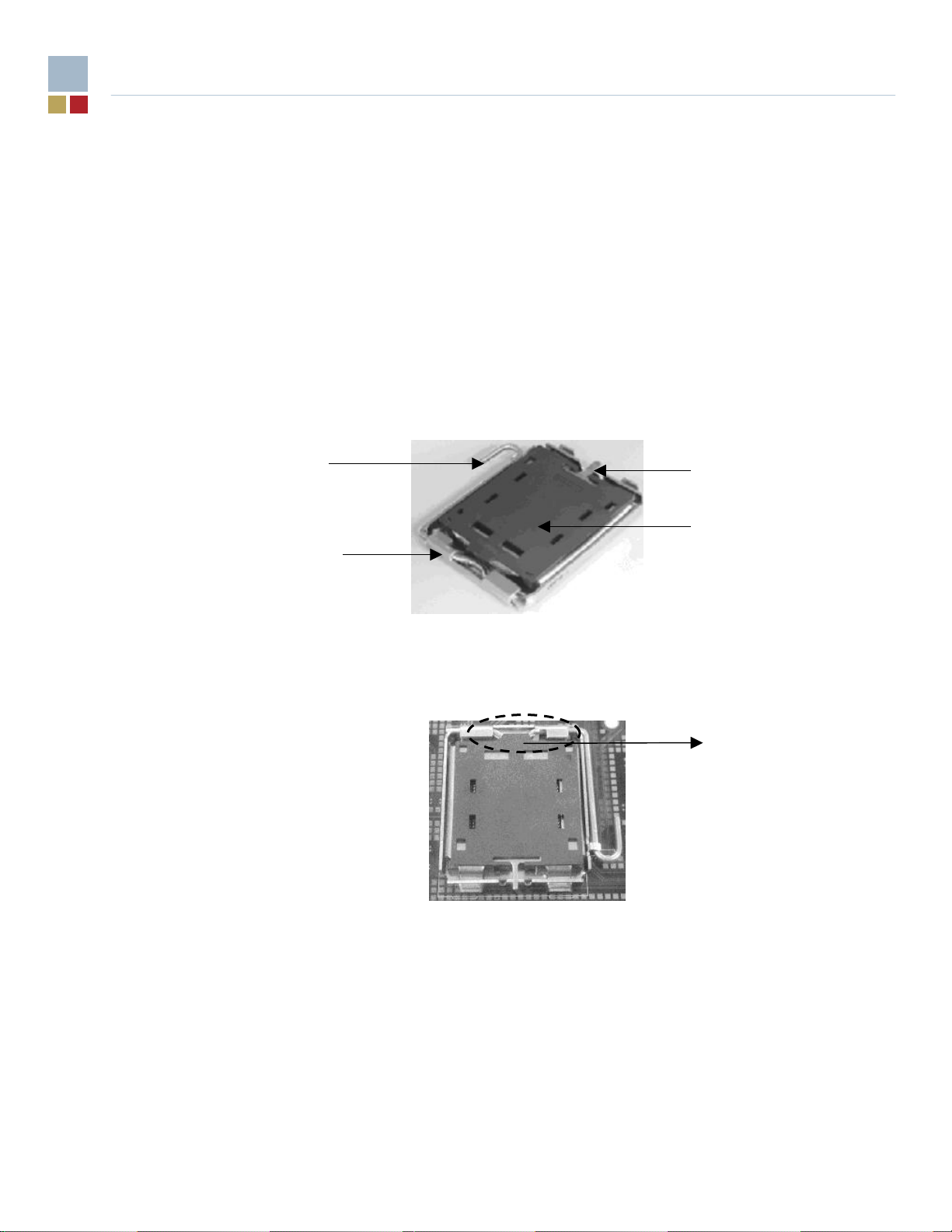

1.5 Installation of CPU

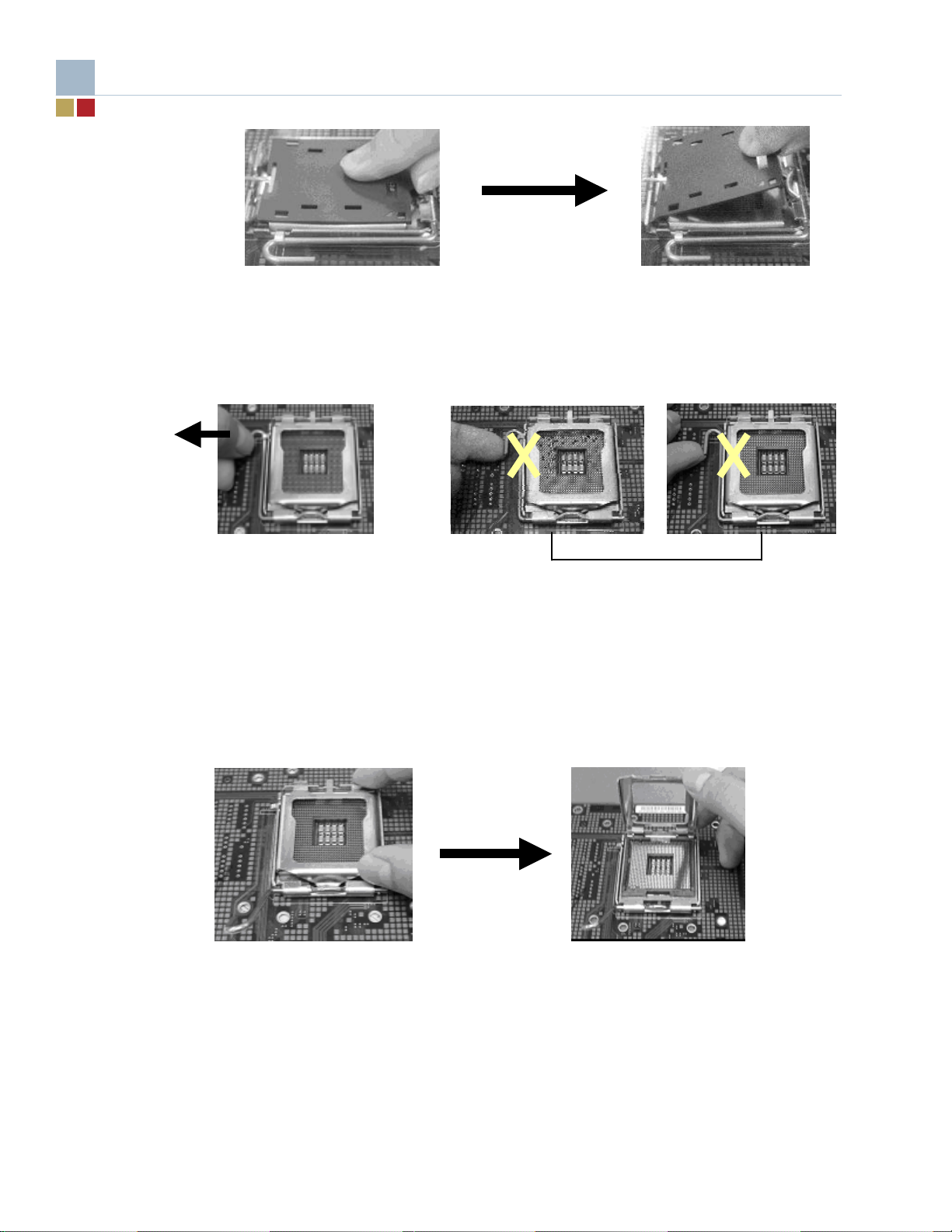

1.5.1 Installation of CPU

Below is the CPU socket illustration. Follow these procedures to install a CPU.

Load leve

Load Stiffener

1. Use thumb & forefinger to hold the lifted tab of the cap.

Load plate

Load ca

Lifted tab

2. Lift the cap up and pick to upload the cap completely from the socket.

17

KP915GV Product Manual

3. Use thumb & forefinger to hold the hook of the load lever and pull the lever sideways to unlock it.

Correct

Warning:

DO NOT use finger to lift the locking lever, as injury could occur to the finger and the SKT could be

damaged.

4. Lift up the lever. Use thumb to open the load plate. Be careful not to touch the contacts.

Wrong

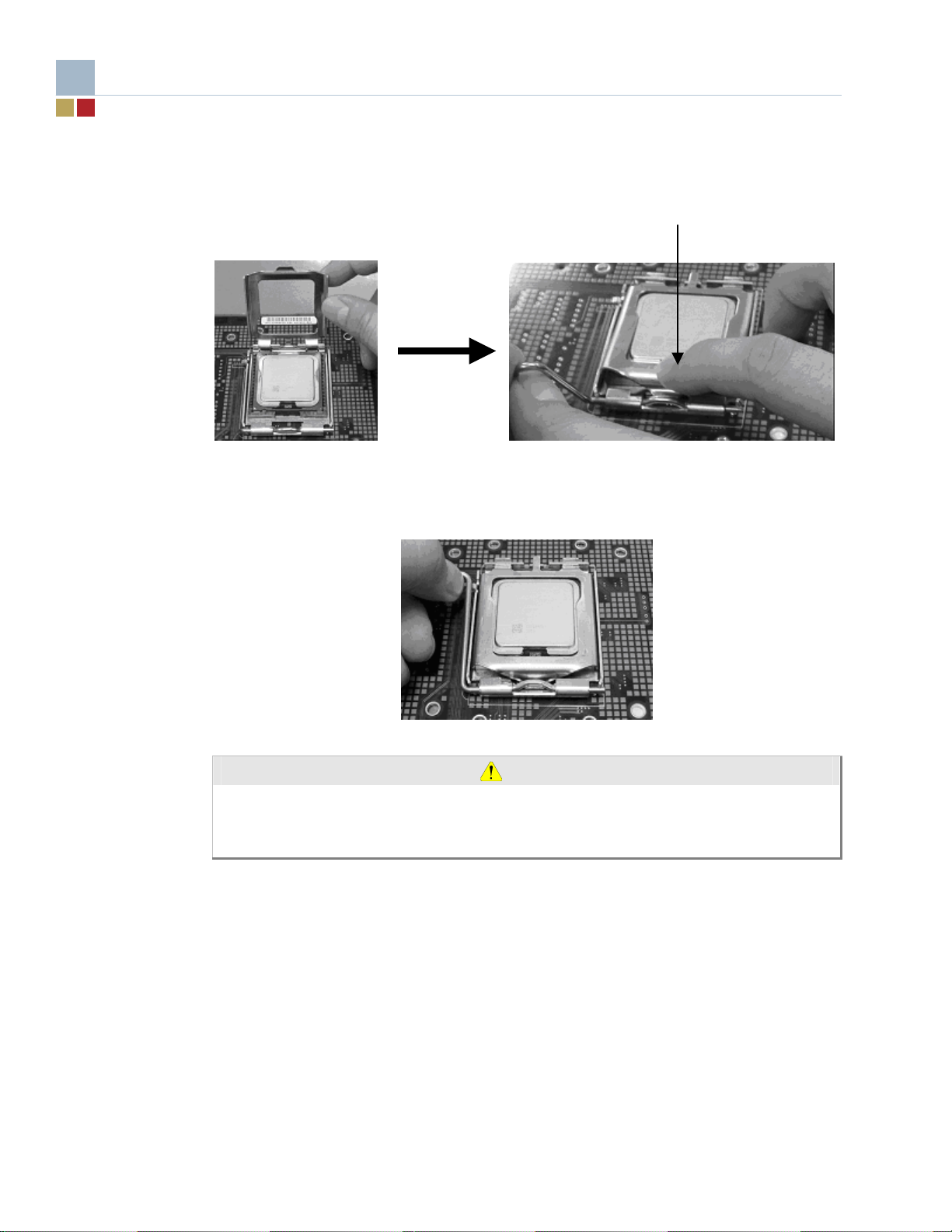

5. Hold the CPU and tilt it to some degree since the contacts are designed to be hooked, and

then match the triangle marker to Pin 1 position as shown below. Carefully insert the CPU

into the socket until it fits in place.

18

KP915GV Product Manual

Alig

y

r

nment ke

Pin 1 indicato

19

KP915GV Product Manual

6. Close the load plate, and slightly push down the tongue side.

7. Lower the lever and lock it to the load plate, then the CPU is locked in place.

Slightly push down

the tongue side

Excessive temperatures will severely damage the CPU and system. Therefore, you should install

CPU cooling fan and make sure that the cooling fan works normally at all times in order to prevent

overheating and damaging to the CPU. Please refer to your CPU fan user guide to install it

properly.

1.5.2 Installation of Memory

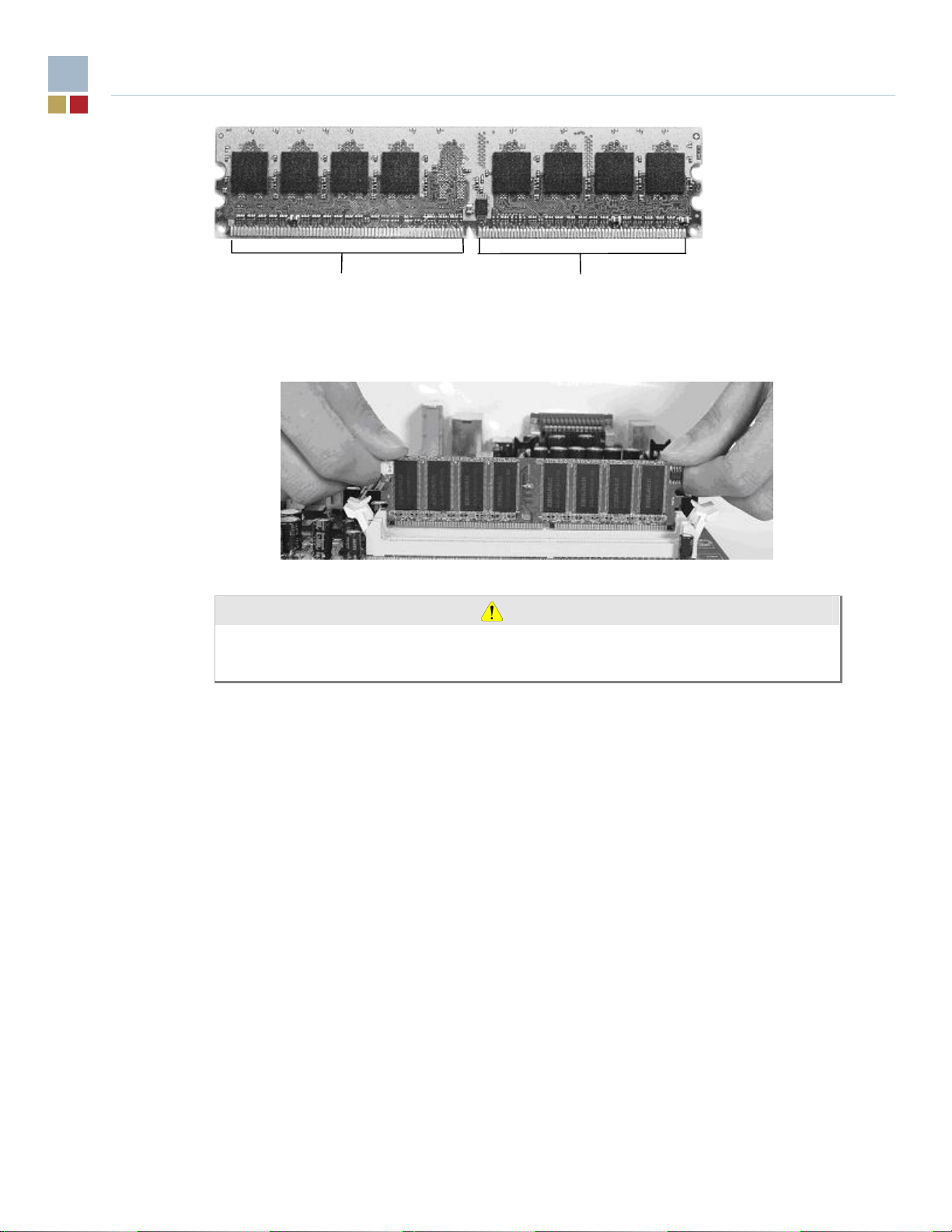

This motherboard includes four 240-pin slots with 1.8V for DDR2. You must install at least one

memory bank to ensure normal operation.

Installation of DDR2 Memory

1. There is only one gap in the middle of the DIMM slot, and the memory module can be fixed in

one direction only. Unlock a DIMM slot by pressing the module clips outward.

2. Align the memory module to the DIMM slot, and insert the module vertically into the DIMM slot.

CAUTION

20

KP915GV Product Manual

DDR2 Memory bank

128 Pins 112 Pins

3. The plastic clips at both sides of the DIMM slot will lock automatically.

CAUTION

Be sure to unplug the AC power supply before adding or removing expansion cards or other

system peripherals, especially the memory devices, otherwise the motherboard or the system

memory might be seriously damaged.

21

KP915GV Product Manual

1

1.5.3 Power Supply

In order to avoid damaging any devices, make sure that they have been installed properly prior to

connecting the power supply.

It is recommended that the board be used with a power supply that supports a minimum

current load of 0.3A or less on the 5V supply rail and 2A or less on the 3.3V supply rail.

This board with CPU and memory may draw as little as 400mA of 5V and 2 A of 3.3V during

start-up (increases depend on installed devices). The power supply under consideratio n must

be verified as compatible with the projected total system start-up loads for these supply rails.

If the power supply minimum current level requirements are not at or below the level of

current loads that are actually drawn, unpredictable start-up operation may result, such as the

power supply latching off. If this occurs, the AC input to the power supply must be removed

and re-attached or the power supply switch cycled off and on, in order to turn the system

back on.

4-pin ATX 12V Power Connector:

The ATX power supply connects here and provides power to the CPU.

GND GND

3

4

12V 12V

2

4-pin ATX 12V power connector

22

KP915GV Product Manual

V

V+5V

V

V

V

V

V5V

KP915GV 20-pin ATX power connector:

Below is the ATX power supply connector. Make sure that the power supply cable and pins are

properly aligned with the connector on the motherboard. Firmly plug the power supply cable into

the connector and make sure it is secure

.

GND

-5

5

GND GND

PS-ON

GND

3.3

-12

12V

5VSB

Pw-OK

5

GND

GND

3.3

3.3

GND

20-pin ATX power connector

23

KP915GV Product Manual

2 Motherboard Description

2.1 Processor Support

• Single processor support

• Intel® Pentium® 4 Processor 550/551 (3.4GHz 800MHz FSB 1MB L2)

• Intel® Celeron™ D Processor 340/341 (2.93GHz 533MHz FSB 256Kb L2)

• Follow the Design Guide in the Intel(R) Pentium(R) 4 Processor in the 775-land Package on 90

nm Process EMTS REV. NO. 1.1 and Grantsdale Chipset (915-GV) Platform Design Guide

REV NO. 1.2

• Supports Pentium® 4 Processor Front Side Bus (FSB) at 533MHz (133MHz bus clock) and

800MHz (200MHz bus clock)

• Supports Hyper-Threading Technology and FSB Dynamic Bus Inversion (DBI)

• Supports 32-bit host bus addressing, allowing the CPU to access the entire 4 GB of the

GMCH’s memory address space

2.2 System Clocks

All clocks must comply with CK410 specifications. System clocks include as below:

• Host system (FSB 533/800MHz) 133/200MHz

• DMI (Direct Media Interface) 100 MHz

• Memory system DDR2 SDRAM 400/533MHz

• CPU/MCH/ITP CONNECTOR 200MHz

• MCH/ICH6/LAN/SATA/PCI-E slot 100MHz

• DOTCLK 96 MHz

• PCI slot/SIO/FWH/ICH6/TPM/CPLD 33 MHz

• USB/ICH6 48 MHz

• HD Audio 24.576 MHz

• ICH6/SIO 14 MHz

• RTC (OSC) 32.768 KHz

• LAN (OSC) 25 MHz

24

KP915GV Product Manual

2.3 On board Clocking Block Diagram

14.318MHz

CPU

CPU 133/200 MHz Diff Pair

CK-410

MCH 133/200 MHz Diff Pair

PCI Express 100 MHz Diff Pair

DOT 96 MHz Diff Pair

PCI Express/DMI 100 MHz Diff Pair

PCI Express/DMI 100 MHz Diff Pair

USB/SIO 48 MHz

ICH 33 MHz

REF 14 MHz

PCI Express x16 SDVO

GMCH

Grantsdale

DDR 4 Slots 12 Diff Pair CLKs

Channel A DDR2

DIMM1

DIMM2

Channel B DDR2

DIMM1

DIMM2

FWH 33 MHz

PCI 33 MHz

PCI Express 100 MHz Diff Pair

PCI Express 100 MHz Diff Pair

1394 33 MHz

SATA 100 MHz Diff Pair

SIO 33 MHz

Figure 4. Clocking Block Diagram

2.4 Mechanical

• Compliant with the ATX 2.03 specification

• Lead-free design

• 4-layer PCB, components top side only, immersion silver surface finish

• Screen printing includes RadiSys product code, RadiSys part number, RadiSys branding,

selected component reference designators, and UL and WEEE directive logos.

FWH

PCI Slot

1,2&3

PCI-E SLOT

1,2

LAN

1394

ICH6

32.768KHz

Super I/O

Azalia

24.576MHz

Azalia Bit Clock

2.5 Expansion Slot Types

25

KP915GV Product Manual

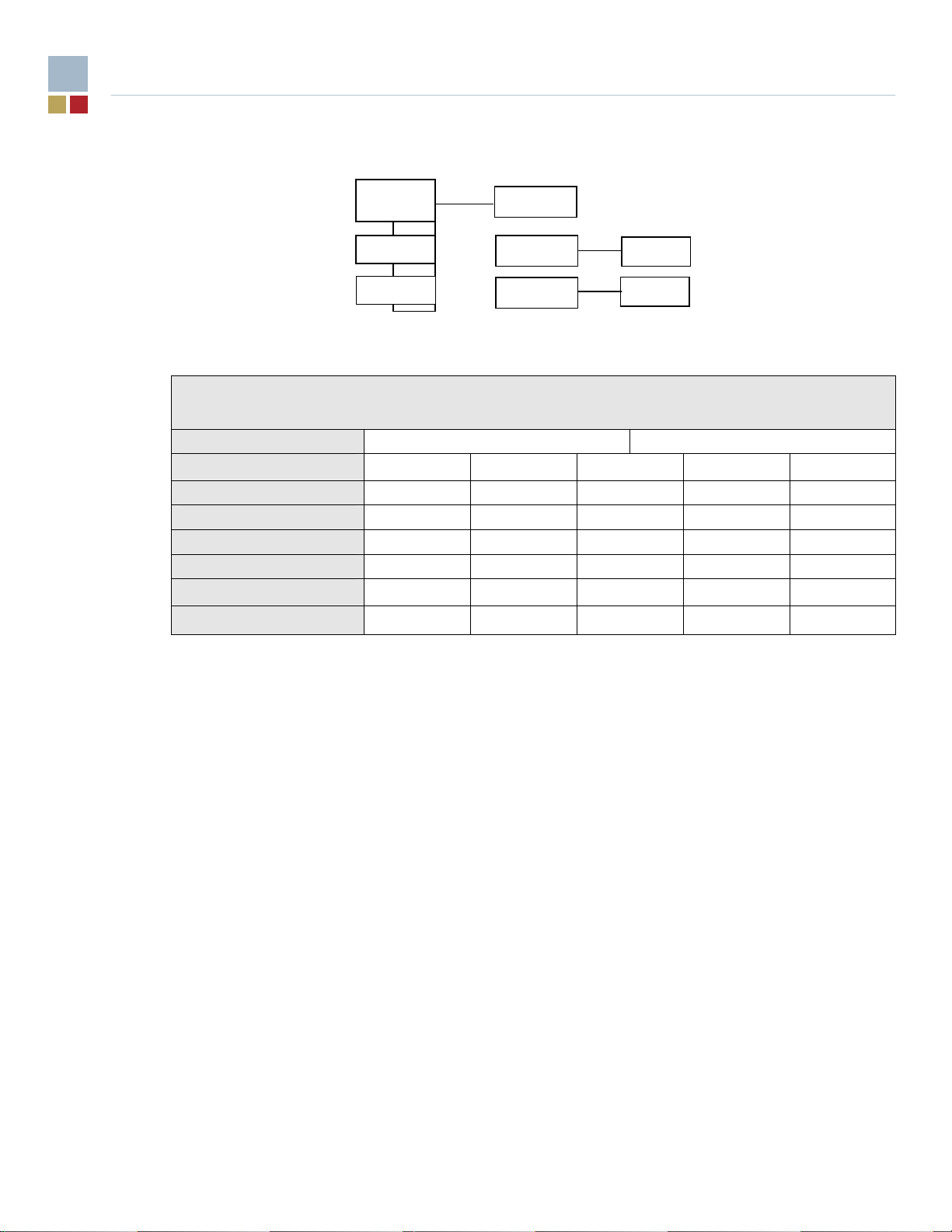

Table 1. KP915GV Motherboard

Chipset

915GV ATX 1 2 3 N/A

Form

Factor

PCI-E x16

or ADD2

• See Figure 5 for slot configurations

• ADD2 will be a green connector

2.6 915GV Chipset Feature

The 915GV is a Memory Controller Hub (MCH) designed for use with the Prescott processors in

desktop platforms. The role of a MCH is a system is to manage the flow of information between its

four interfaces: the CPU interface (FSB), the DDR/DDR2 System Memory interface (DRAM

controller), the External Graphics interface (PCI Express-G), and the I/O Controller through Direct

Media Interface (DMI). It’s 1210 Flip Chip Ball Grid Array (FCBGA) package.

PCI-E

x1

PCI

PCI Riser

Extension

Processor/Host interface (FSB)

•

Supports a single Pentium 4 processor with 1-MB L2 cache in the 90 nm process, in an

LGA775 package.

• The primary enhancements over the Compatible Mode P6 bus protocol are:

1- Source synchronous double-pumped (2x) Address

2- Source synchronous quad-pumped (4x) Data

• Supports Pentium 4 processor FSB interrupt delivery.

• Supports Pentium 4 processor Front Side Bus (FSB) at the following Frequency Ranges:

533/800MT/s (133/200MHz)

• Supports Hyper-Threading Technology (HT Technology)

• Supports FSB Dynamic Bus Inversion (DBI)

• Supports 36-bit host bus addressing, allowing the CPU to access the entire 4GB of the MCH’s

memory address space.

• 12-deep In-Order Queue to support up to twelve outstanding pipelined address requests on

the host bus.

• 1-deep Defer Queue.

• Utilizes GTL+ bus driver with integrated GTL termination resistors.

• Supports a Cache Line Size of 64 bytes.

• At 133/200MHz bus clock the address signals run at 266/400MT/s, the data is quad pumped

and an entire 64B cache line can be transferred in two bus clocks. At 133/200MHz bus clock

the data signals run at 533/800MT/s for a maximum bandwidth of 4.3GB/s.

System Memory Controller

•

The MCH System Memory Controller directly supports dual channel of memory (each channel

consisting of 64 data lines)

1- The memory channels are asymmetric: “Stacked” channels are assigned address serially.

Channel B addresses are assigned after all Channel A addresses.

2- The memory channels are interleaved: Addresses are ping-ponged between the channels

after each cache line (64-B boundary).

• Supports DDR2 memory DIMM frequencies of 400 and 533MHz. The speed used in all

channels is the speed of the slowest DIMM in the system.

26

KP915GV Product Manual

• Support for non-ECC memory, unbuffered DIMMs only, in 256MB, 512MB, 1GB, and 2GB

sizes, which may be installed as single DIMMs if desired. If a total of 4GB of DIMMs is

installed, the maximum available memory will be approximately 3.24GB, with the balance of

the address space being consumed by other resources in the system.

• I/O Voltage of 1.8V for DDR2.

• Directly support only two channels of non-ECC DDR2 DIMMs.

• Supports maximum memory bandwidth of 4.2GB/s in single-channel or dual channel

asymmetric mode, or 8.5GB/s in dual-channel interleaved mode assuming DDR2 533MHz.

• For dual interleaved mode, DIMMs must be installed in matched pairs, installed in DIMM

sockets with identical color (e.g. locations DIMM1 and DIMM3, then DIMM2 and DIMM4).

• Supports 256Mb, 512Mb, and 1Gb technologies for x8 and x16 non-ECC DDR2 devices.

• Supports four banks for all DDR2 devices up to 512Mb densities. Supports eight banks for 1Gb

DDR2 devices.

• Maximum DRAM address decode space of 4GB. (Assuming 32-bit addressing)

• Supports opportunistic refresh scheme.

• Supports page sizes of 4KB, 8KB, 16KB and 32 KB. Note 32KB is for dual-channel operation

only.

• Supports up to 16 simultaneous open pages per channel

• Serial Presence Detect (SPD) scheme for DIMM detection support.

• Dual channel DDR2 for 4 X 240 pin DIMM connectors

• Support for Serial Presence Detect (SPD)

• Support for Suspend to RAM (STR) using CKE, S3 ACPI state

PCI Express Graphics Interface

One, 16-lane PCI Express port intended for Graphics Attach, fully compliant to the PCI

•

Express Base Specification revision 1.0a

• A base PCI Express frequency of 2.5Gb/s only.

• Raw bit-rate on the data pins of 2.5Gb/s, resulting in the real bandwidth per pair of 250MB/s

given the 8b/10b encoding used to transmit data across this interface.

• Maximum theoretical realized bandwidth on the interface of 4GB/s in each direction

simultaneously, for an aggregate of 8GB/s when x16.

• PCI Express Enhanced Addressing Mechanism. Accessing the device configuration space in

the flat memory mapped fashion.

• Automatic discovery, negotiation, and training of link out of reset.

• Supports traditional PCI style traffic (asynchronous snooped, PCI ordering).

DMI

A chip-to-chip connection interface to Intel ICH6.

•

• 2GB/s point-to-point DMI to ICH6 (1GB/s each direction).

• 100MHz reference clock (shared with PCI Express Graphics Attach).

• 32-bit downstream addressing.

2.7 Video

• Integrated Intel® GMA900 video controller

1. Intel Infrastructure Processor Division (IPD) group Embedded Graphics or Graphics Media

Accelerator (GMA) (Extreme) drivers and video BIOS

• Analog RGB output with DDC2B

1. Graphics resolution up to 2048 x 1536 pixels with 32-bit color support at 75Hz

2. 15-pin D-sub connector

27

KP915GV Product Manual

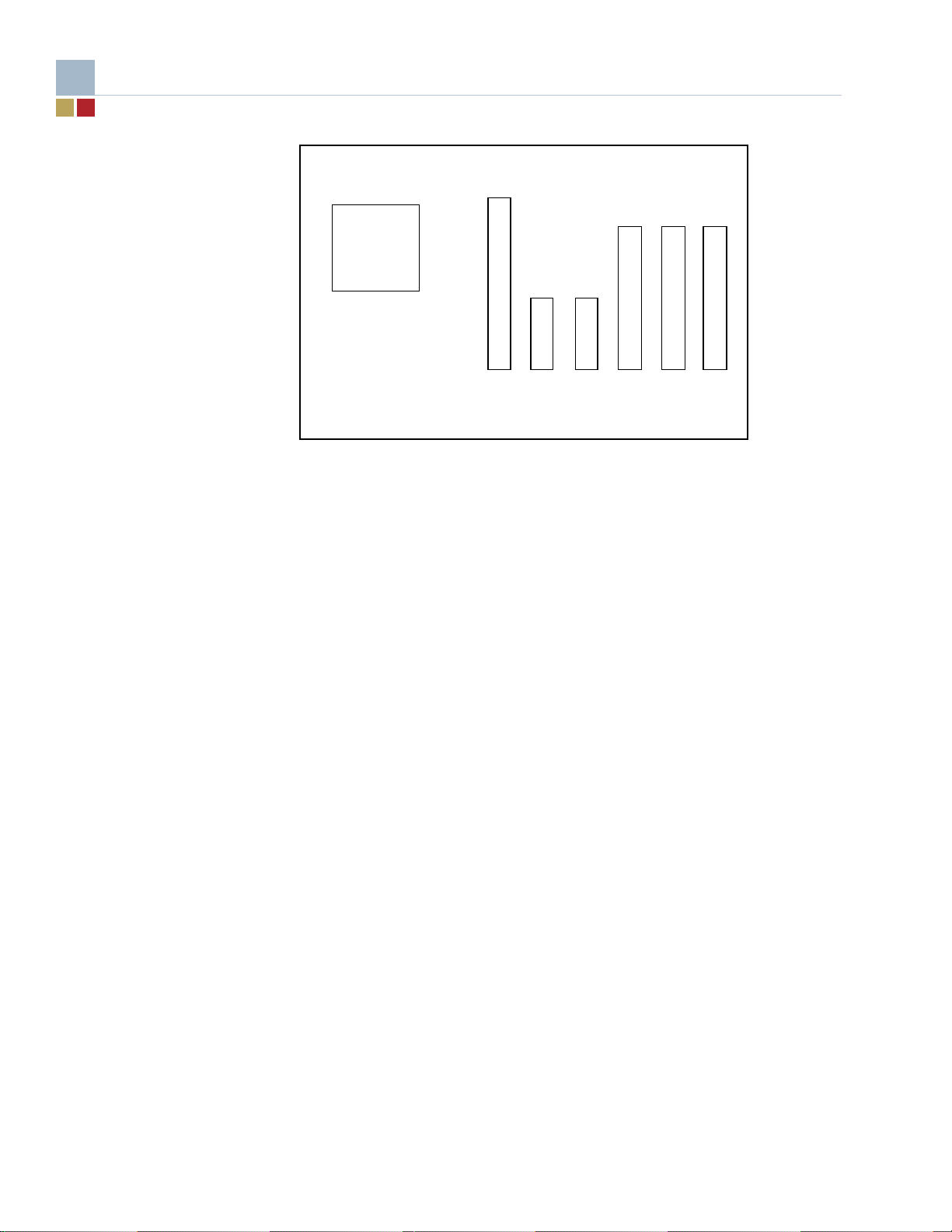

2.8 Disks

• Four 150MB/s SATA ports with locking headers

• One Ultra ATA/100 interface via on-board 40-way boxed header

• 40/80-pin cable host-side detection or forced in BIOS

• Support for hard disks and ATAPI drives

Processor

ADD2 x1

x1

PCI-E

PCI-E

PCI

PCI PCI

Figure 5. KP915GV Board Slot Layout

• BIOS support for 48-bit LBA (ATA drives >137GB)

• Support for USB drives including boot

2.9 Audio

SigmaTel STAC9200 audio controller with Intel High Definition Audio (HDA) compatible mode

• On-board ATAPI connectors

• ATAPI 1: Line input connector (black)

• ATAPI 2: Stereo AUX/MIC input connector (white)

• ATAPI 3: Stereo Line output connector (yellow)

• Two I/O panel 3.5mm plug and play audio jacks – default connections:

• Stereo microphone input (with support for microphone bias)

• Stereo line output with headphone drive capability

(Note: an option exists for a three jack connector – refer to Table 2 and comments below.)

• On-board PC beeper

28

KP915GV Product Manual

External Internal

Optional*

Line in

ATAPI 1

Line out

ATAPI 3

Line out

I/O panel jack color

ATAPI header color

Nominal function

Line In capability

Line Out capability

Microphone capability

Headphone Out Capability

MIC in

Figure 6. Audio Jack Socket and ATAPI Connectors

Table 2: Audio Channel Allocation

I/O panel jack Internal header

Pink Lime Blue*

Black* White Yellow

Microphone Line Out Line In* Microphone Line Out

X X

X X

X X

X

ATAPI 2

MIC in

* If a 3 jack external connector is needed, an option could be made available, for which the

added blue jack would be Line In, displacing the Line In black internal header (deleted) on

the standard configuration.

2.10 Network

• One Ethernet controller configured as either 10/100 or 10/100/Gbit at build-time

• Available with a second Ethernet controller configured as 10/100/Gbit

• 10/100Mbps Ethernet solution IEEE 802.3 10Base-T and 100Base-TX compatible

• MAC integrated into ICH with Intel 82562GZ transceiver

• Remote boot, PXE and Wake-On-LAN support

• Gbit Ethernet solutions IEEE 802.3 10Base-T, 100Base-TX, 1000Base-T compatible

• Intel 82573V (or ‘L) PCI Express Ethernet controller connected via I/O hub x1 lane

• Full line-speed operation

• Remote boot, PXE and Wake-On-LAN support

• On-board RJ45 connector (RJ45 over dual USB connector) with two integral LEDs showing

combined link integrity and activity (yellow) plus line speed (green/amber)

• Available with a second RJ45 over dual USB connector

29

KP915GV Product Manual

2.11 I/O

• Four USB 2.0 ports on I/O panel via two dual stacked USB over RJ45 connectors

• Four USB 2.0 ports on internal locking headers

• Available with IEEE 1394b controller with support for 1394a

• Single port via a header connector

• Based on Texas Instruments TSB82AA2 controller and TSB81BA3 transceiver

2.12 Power Management

• Supports ACPI 2.0 with power states S0, S3, S4 (not S4BIOS), S5 and C0, C1, C2, C3

• Supports PCI PME and PCI Express power management event signaling

Table 3. ACPI Power States

G0/S0/C0 Full on

G0/S0/C1 Processor is halted

G0/S0/C2 Processor stops internal clocks

G0/S0/C3 Processor clocks are disabled and processor in sleep state

G1/S3 System context is saved to RAM and power removed from all circuits

except that required to maintain system RAM and resume

G1/S4 System context is saved to disk and power removed from all circuits

except that required to resume

G2/S5 Soft off, only resume logic and RTC remain powered

2.13 System management

• System monitoring of voltage, temperature, fans

• Temperature monitoring of processor die, board and remote sensor

• Direct monitoring of lithium cell voltage

• Automatic fan control for 3 fans - CPU, System 1, System 2

• Fan configuration held in BIOS customization block

• Fans can be assigned to any of three thermal zones for automatic control - each zone

• monitored by one of the three thermal sensors

• 450mA drive capability for each system fan, 2.2A for the CPU fan

• Anti-tamper security (trigger for chassis intrusion detect)

• Programmable watchdog timer with range of 1 second to 1 hour

• Access to SMBus via 4-pin 2mm header

2.14 Security

• Header for Trusted Platform Module (TPM)

• TCG 1.1 compliant

30

Loading...

Loading...