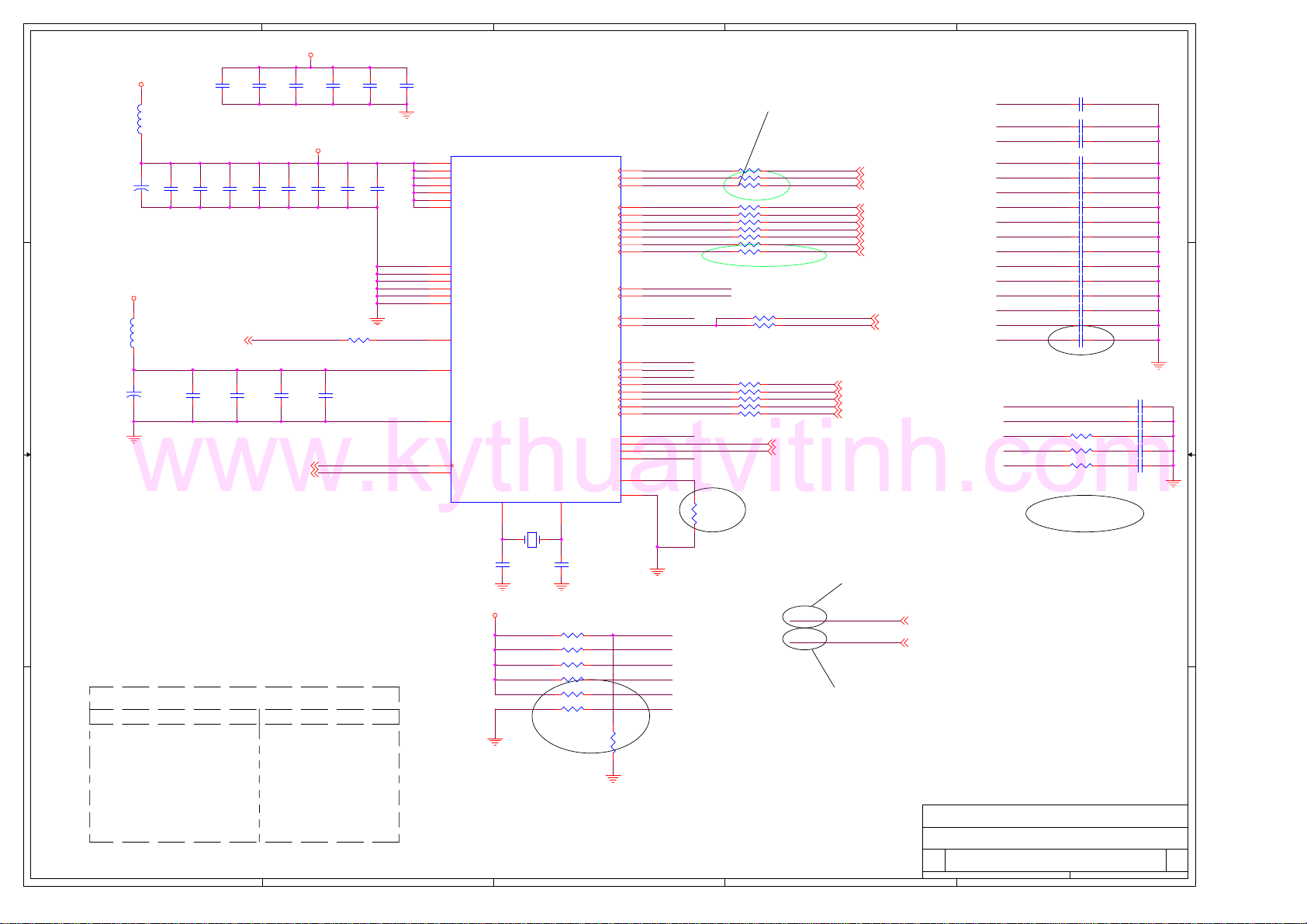

Page 1

8

www.kythuatvitinh.com

Digitally signed by

fdsf

DN: cn=fdsf, o=fsdfsd,

ou=ffsdf,

email=fdfsd@fsdff,

c=US

Date: 2010.01.06

06:06:12 +07'00'

7

6

5

4

3

2

1

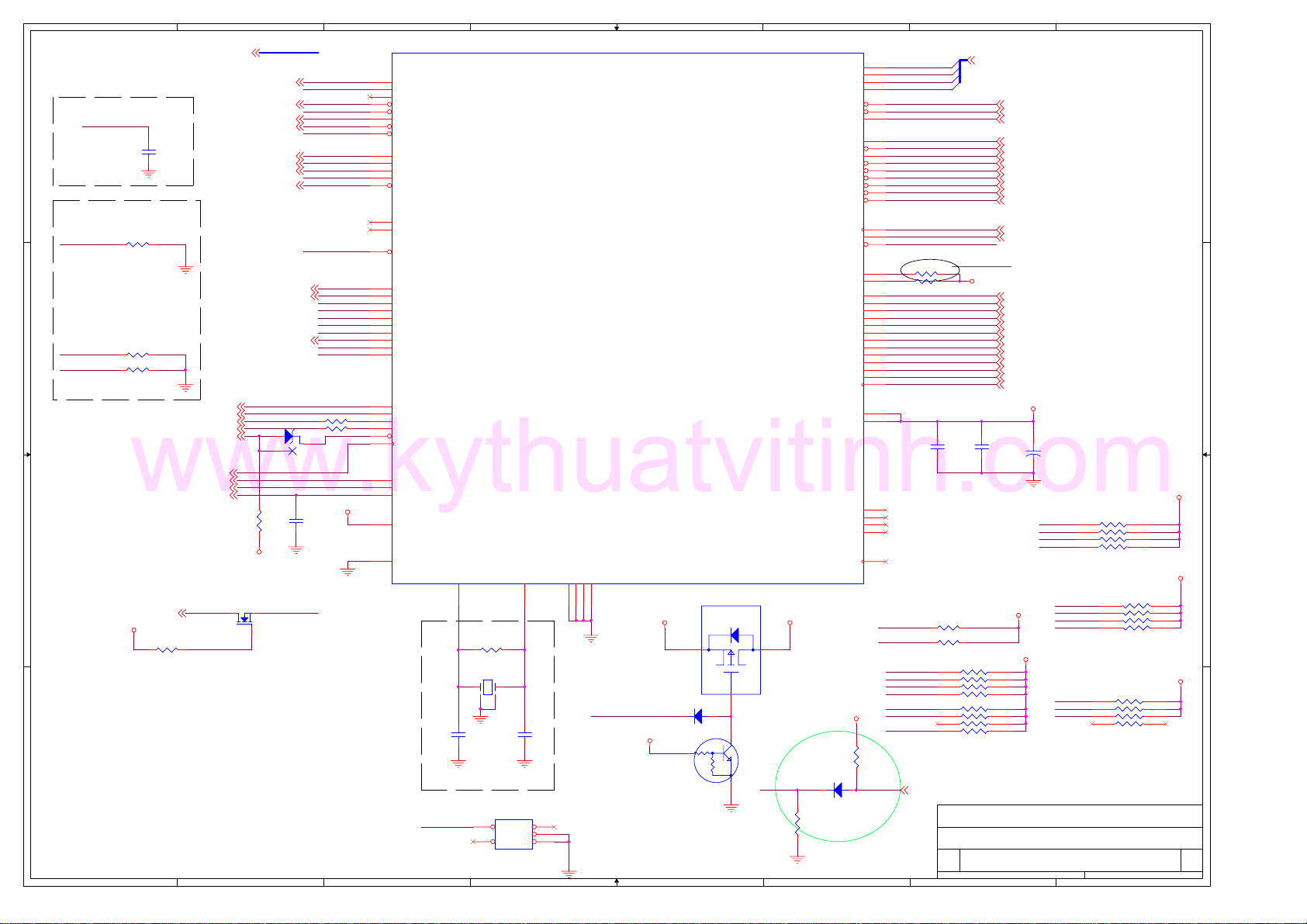

G510 SCHEMATICS

D D

01.THIS PAGE

02.uFCPGA Tualatin CPU

03.uFCPGA Tualatin CPU

04.uFCPGA Tualatin CPU

05.CLOCK GENERATOR

06.SIS630ST(HOST/MEMORY)

07.SIS630ST(PCI/IDE)

08.SIS630ST(VGA/AGP)

09.SIS630ST(SOUTH BRIDGE)

10.SIS630ST(POWER)

C C

11.SODIMM & ON BOARD SDRAM

12.CRT & USB CONN.

13.HDD & CDROM CONN.

14.COM & LPT PORT

15.AC'97 CODEC

16.OP AMPLIFIER & AUDIO JACK

17.NS87393 & IR MODULE

18.M38867

19.BIOS ROM & POWER GOOD

B B

20.RTC BATTERY & POWER SW

21.TI1410 & CARDBUS CONN.

22.LVDS TRANSMITTER & LCD CONN.

23.MINI PCI

PCB NO. :KK0G510011020

24.CHARGER

25.CPU VORE VCC

REV. : 2.0

26.DC-DC MP5V/+3VALWAYS/+12VA

A A

PAGE

1 2 3 4 5 6 7 8 9 101112131415161718192021222324

VER

2.A

DATE

11/9 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 10/30 11/9 10/30 10/30 10/30

27.DC-DC VCC1.8V/ALWAYS VOLTAGE

28.uP

29.REVISION HISTROY

2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.A 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0

8

7

6

5

25 26 27 28 29PAGE

VER

2.0 2.0 2.0 2.0 2.A

DATE

10/30

10/30 10/30 10/30 11/9

P.leader

ALPHA-TOP CORP.

10/30 10/30 10/30

4

3

Title

G510 MAIN BOARD

Size Document Number Rev

B

G510-1-4-01 2.A

Date: Sheet

2

Check by Design byAppr.by

129Friday, November 09, 2001

of

1

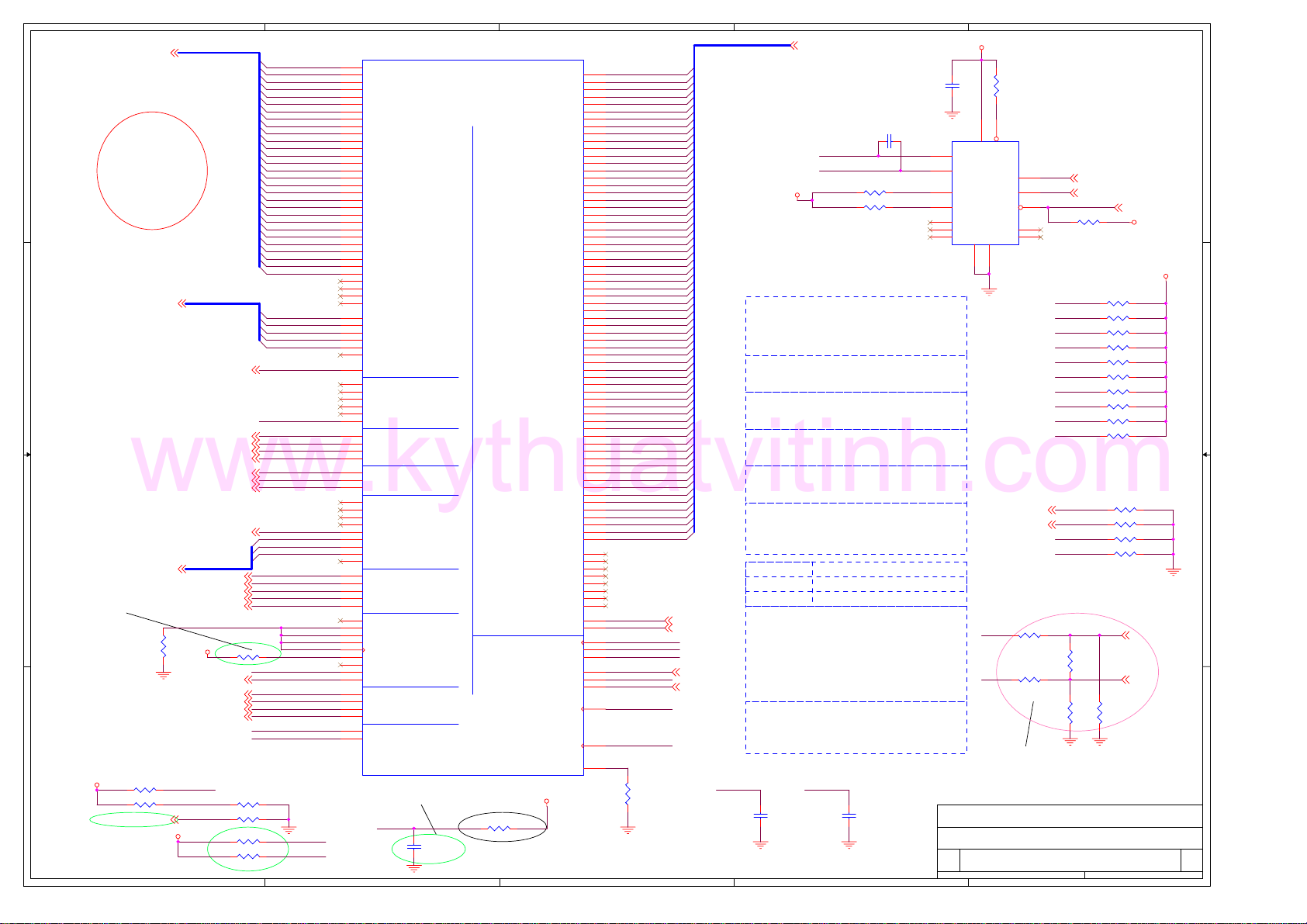

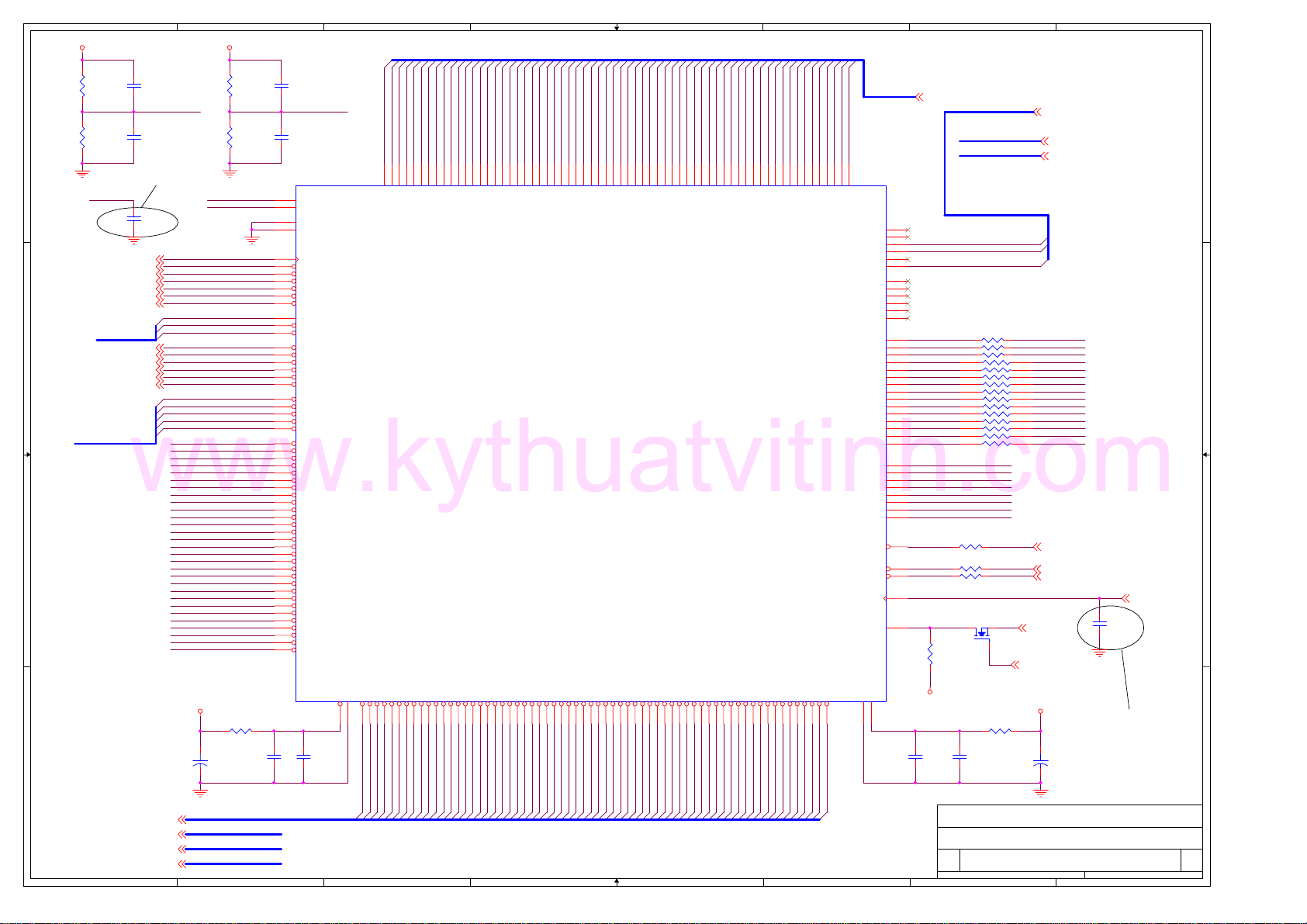

Page 2

5

www.kythuatvitinh.com

HA[3..31]6

D D

del R500,R501,C583

-HREQ[0..4]6

C C

B B

A A

-RS[0..2]6

Add for Mobile Tualatin

VCC3

R523 1K

R525 1K

PICCLK5

Add for Mobile Tualatin

HA[3..31]

-HREQ[0..4]

BREQ0-6

HLOCK-6

HIT-6

HITM-6

DEFER-6

HTRDY-6

-RS[0..2]

A20M-9

FERR-9

IGNNE-9

CPUPWGD19

SMI-9

R521

1K

VCC1.5V

R522 270

BSEL15

INTR9

NMI9

STPCLK-9

DPSLP-4,25

BSEL0

BSEL1

R526 0R

PICCLK

R593 100

VCC1.5V

R594 150

R601 150

5

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

ADS-6

IERR-

BREQ0-

BPRI-6

BNR-6

-RS0

-RS1

-RS2

A20MFERR-

IGNNE-

SMI-

BSEL0

BSEL1

THERMDA

THERMDC

PICD0

PICD1

Add for Mobile Tualatin

B11

A10

A13

C12

C10

A15

A14

B13

A12

AA3

AB3

C14

AF23

AF4

AA2

AF22

AE20

AD22

AD21

AC3

AF6

AD9

AB4

AD3

AD11

AD7

AF7

AF15

AD10

AF19

AE22

AE12

AF10

AD15

AE14

AE4

AF8

AF13

AF14

K1

J1

G2

K3

J2

H3

G1

A3

J3

H1

D3

F3

G3

C2

B5

C6

B9

B7

C8

A8

B3

A9

C3

A6

R1

L3

T1

U1

L1

T4

W2

P3

A7

R2

L2

V3

U2

T3

W1

Y3

V1

U3

M5

4

U39A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

RP#

ADS#

AERR#

AP0#

AP1#

BERR#

BINIT#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BP2#

BP3#

BPM0#

BPM1#

TRDY#

RS0#

RS1#

RS2#

RSP#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TDO

TDI

TMS

TRST#

TCK

PREQ#

PRDY#

BSEL0

BSEL1

INTR/LINT0

NMI/LINT1

STPCLK#

DPSLP#

THERMDA

THERMDC

TUALATIN

Delete for Mobile

Tualatin above 1Ghz

CPURST-

4

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

C584

0.1UFR

TUALATIN

1 OF 3

R527 56.2 1%

CLOSE TO CPU

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

DBSY#

DRDY#

PICCLK

PICD1

PICD0

INIT#

FLUSH#

RESET#

BCLK

BCLK#

EDGECTRLP

VTT

3

HD0

A16

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

B17

A17

D23

B19

C20

C16

A20

A22

A19

A23

A24

C18

D24

B24

A18

E23

B21

B23

E26

C24

F24

D25

E24

B25

G24

H24

F26

L24

H25

C26

K24

G26

K25

J24

K26

F25

N26

J26

M24

U26

P25

L26

R24

R26

M25

V25

T24

M26

P24

AA26

T26

U24

Y25

W26

V26

AB25

T25

Y24

W24

Y26

AB24

AA24

V24

AE24

AD25

AE25

AC24

AF24

AD26

AC26

AD24

W3

Y1

AF20

AD17

AD19

AE6

AF5

B15

AC1

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

CPUINITFLUSHCPURST-

+HCLK

PICCLK

PICD1

PICD0

DBSY- 6

DRDY- 6

CPUINIT- 9

CPURST- 6

HD[0..63]

HD[0..63] 6

VCC3

1.5V CMOS INPUT

A20M# ,DPSLP# ,FLUSH# ,IGNNE# ,INIT#

,LINT0/INTR ,LINT1/NMI ,PREQ# ,SMI#

,STPCLK#

1.25V CMOS INPUT

GHI# ,VTTPWRGD

1.8V CMOS INPUT

PWRGOOD

1.5V OPEN DRAIN OUTPUT

FERR# ,IERR#

3.3V OPEN DRAIN OUTPUT

BSEL[1:0] ,VID[4:0]

2.5V CLOCK INPUT(Signle End

Mode)

BCLK

BSEL[1:0]

11

1

0

AGTL I/O

A[35:3]# ,ADS# ,AERR# ,AP[1:0]#

,BERR# ,BINIT# ,BNR# ,BP[3:2]#

,BPM[1:0]# ,BREQ0#, D[63:0]# ,DBSY#

,DEP[7:0]# ,DRDY# ,HIT# ,HITM#

,LOCK# ,REQ[4:0]# ,RP# ,RS[2:0]#

,TRDY#

AGTL INPUT

2

C581

0.1UF

C582 2200PF

THERMDA

THERMDC

1 2

R502 1K

R503 1K

STSEM BUS FREQUE N C Y

133MHZ

100MHZ

VCC3

R499

10K

2

15

U40

3

VCC

DXP

DXN

ADD1

ADD0

NC1

NC2

NC3

SMBDATA

GND

7

STBY

SMBCLK

ALERT

NC4

NC5

GND

8

14

12

11

13

16

Philips1617

4

6

10

1

5

9

1

SMCLK 18,28

SMDA 18,28

R504 10K

THRM- 18

VCC3

Default use Philips 1617

A20M-

R505 1.5K

FERR-

R506 1.5K

IGNNE-

R507 1.5K

NMI

R508 1.5K

INTR

R509 1.5K

STPCLK-

R510 680

SMI-

R512 270

CPUINIT-

R513 1.5K

FLUSH-

R514 3K

IERR-

R517 1.5K

BREQ0HA15

R584

R518 1K

R519 1K

R520 10

R573 10K

R582 475 1%

12

12

12

R585

61.9 1%

CPUCLK+ 5

CPUCLK- 5

TESTLO13

TESTLO23

+HCLK

-HCLK

R581 33

R583 33

12

12

61.9 1%

BPRI# ,DEFER# ,RESET# ,RSP#

-HCLK

AD1

AF16

AGTL OUTPUT

R524

110 1%

3

+HCLK -HCLK

C714

CAP

PRDY#

2

C725

CAP

Add R581,R583=33

Add R582=475 1%

Add R584,R585=61.9 1%

ALPHA-TOP CORP.

Title

G510 MAIN BOARD

Size Document Number Rev

G510-1-4-01 2.0

Date: Sheet

229Friday, November 09, 2001

1

of

VCC1.5V

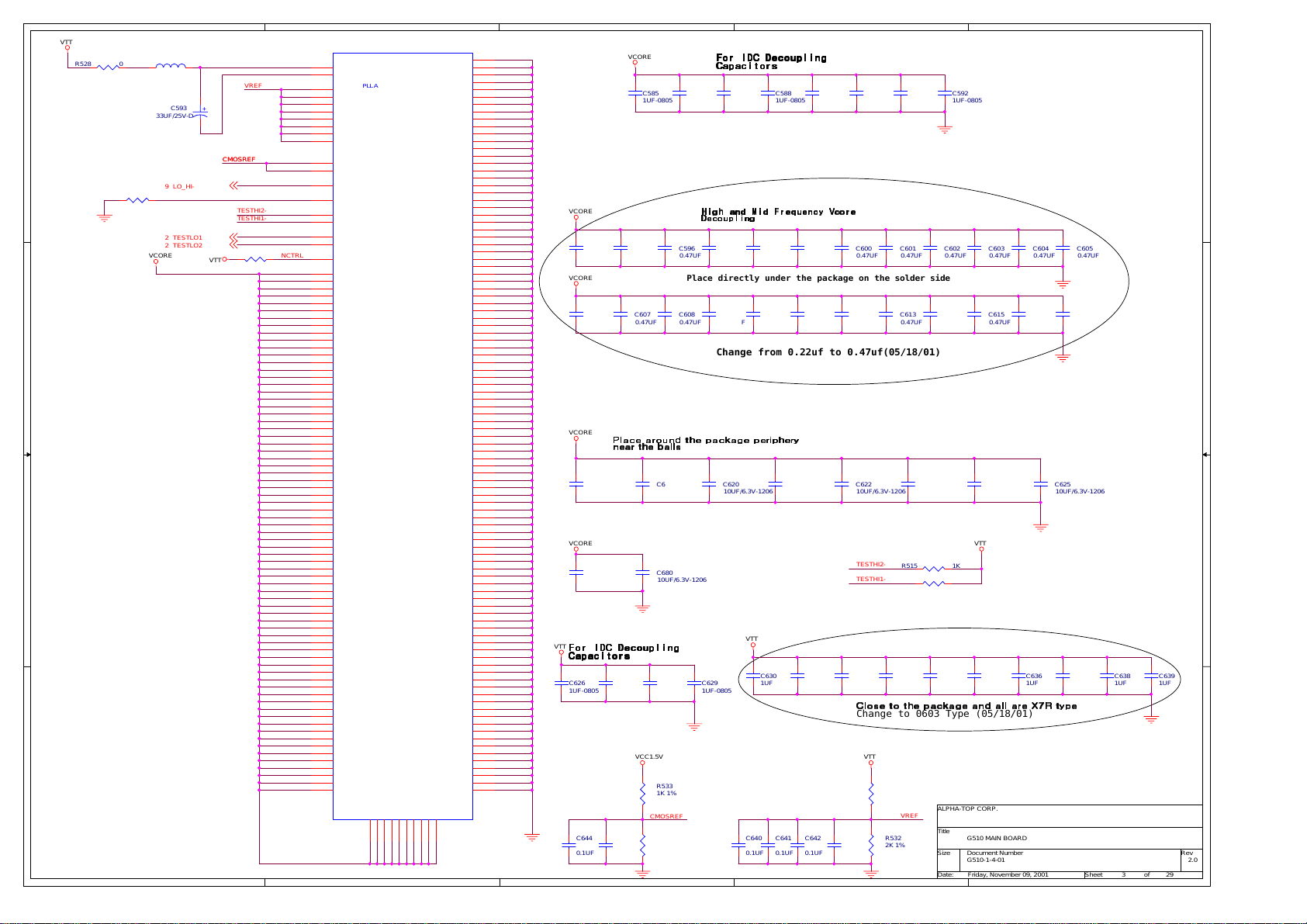

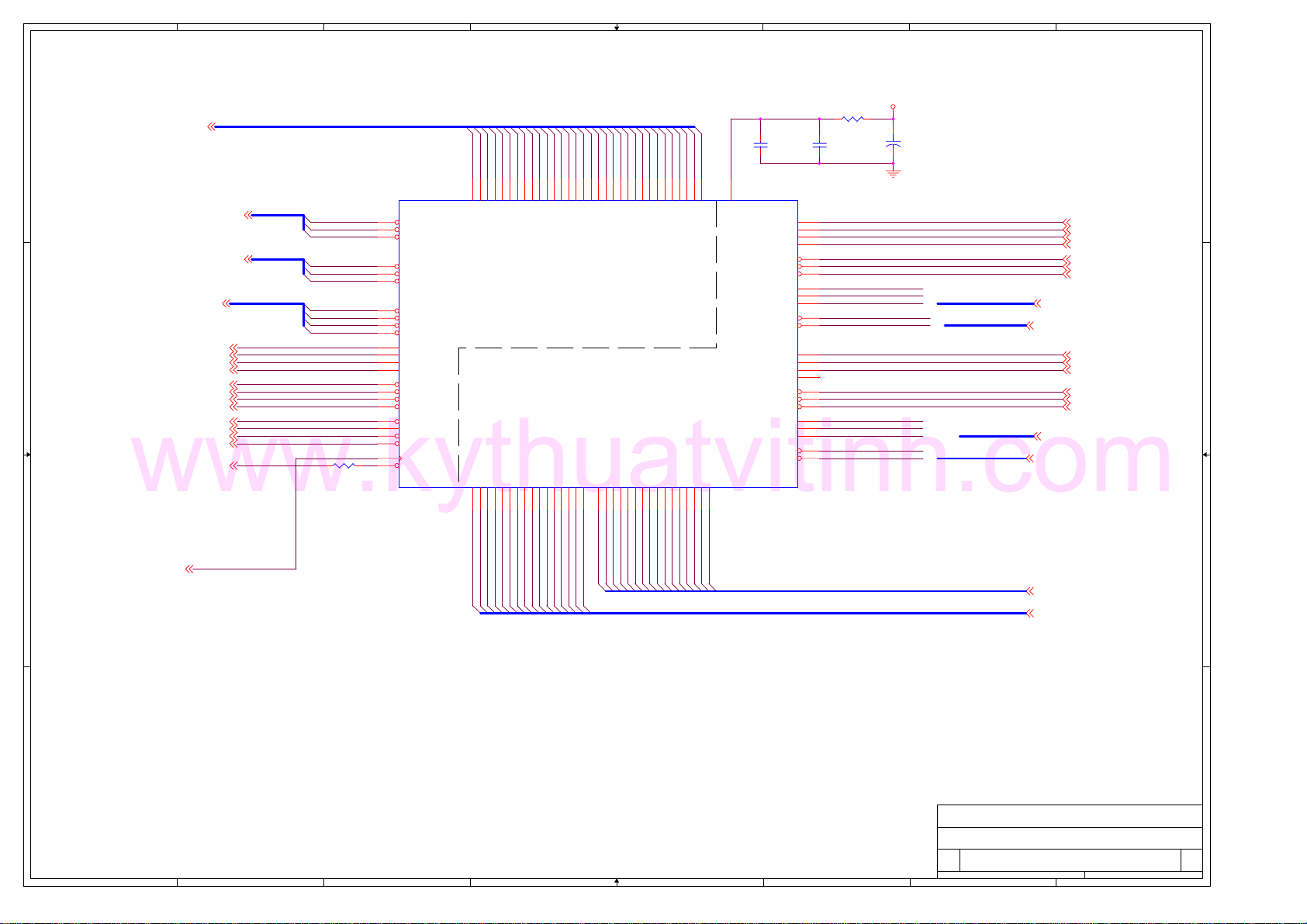

Page 3

R529

www.kythuatvitinh.com

56.2 1%

5

L48

1 2

4.7UH-0805

C593

33UF/25V-D

LO_HI-9

TESTLO12

TESTLO22

VCORE

5

+

VTT

VREF

CMOSREFCMOSREF

TESTHI2TESTHI1-

R530 15 1%

U39B

N3

N2

A4

A21

N1

AF9

AF21

AA1

AB26

H26

AD5

AF12

L5

AE16

E2

AF11

M1

Y4

NCTRL

AD16

12

M22

N21

P22

R21

U21

V22

W21

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

D10

D12

D14

D16

D18

D20

D22

E11

E13

E15

E17

E19

E21

F10

F12

F14

F16

F18

F20

F22

G21

H22

J21

K22

L21

T22

Y22

D6

D8

E5

E7

E9

F6

F8

G5

H6

J5

K6

M6

N5

P6

R5

T6

U5

V6

W5

Y6

VTT

R528 0

D D

C C

B B

A A

VCCA

VSSA

VREF0

VREF1

VREF2

VREF3

VREF4

VREF5

VREF6

VREF7

CMOSREF1

CMOSREF2

GHI#

RTTIMPEDP

TESTHI1

TESTHI2

TESTLO1

TESTLO2

NCTRL

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

4

PLL ANALOG VOLTAGE

TUALATIN

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

VCC71

VCC72

VCC73

VCC74

VCC75

AB22

AC5

AC7

AC9

AC11

4

VCC76

AC13

VCC77

AC15

VCC78

AC17

VCC79

AC19

VCC80

AC21

VSS01

VSS02

VSS03

VSS04

VSS05

VSS06

VSS07

VSS08

VSS09

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

Tualatin

A25

B2

B4

B6

B8

B10

B12

B14

B16

B18

B20

B22

B26

C23

C25

D2

D4

D7

D9

D11

D13

D15

D17

D19

D21

E8

E10

E12

E14

E16

E18

E20

E22

E25

F2

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F23

G6

G22

G25

H2

H4

H21

H23

J6

J22

J25

K2

K4

K5

K21

K23

L6

L22

L25

M2

M3

M4

M21

M23

N6

N22

N25

P2

P21

P23

R4

R6

R22

R25

T2

T5

T21

T23

U4

U6

U22

U25

V2

V5

V21

V23

W4

W6

W22

W25

Y2

Y5

Y21

Y23

AA6

VCORE

VCORE

C594

0.47UF

C606

0.47UF

3

VCORE

C595

0.47UF

C585

1UF-0805

ࣜࣿࣜ

ࣜࣿࣜ

ࣜࣿࣜࣜࣿࣜ

ࣿ

ࣿ

ࣿࣿ

C587

1UF-0805

C588

1UF-0805

C598

0.47UF

C586

1UF-0805

ࣜࣜࣜ

ࣜࣜࣜࣜ

ࣜࣜࣜࣜࣜࣜ

C596

C597

0.47UF

0.47UF

Place directly under the package on the solder side

C608

0.47UF

C609

0.47UF

C610

0.47UF

C607

0.47UF

C589

1UF-0805

ࣜ

ࣜࣜ

C599

0.47UF

C611

0.47UF

2

C600

0.47UF

C612

0.47UF

C590

1UF-0805

C591

1UF-0805

C601

0.47UF

C613

0.47UF

C602

C614

Change from 0.22uf to 0.47uf(05/18/01)

VCORE

ΝΒΔΖΒΣΠΦΟΕΥΙΖΡΒΔΜΒΘΖ

ΝΒΔΖΒΣΠΦΟΕΥΙΖΡΒΔΜΒΘΖΡΖΣΚΡΙΖΣΪ

ΝΒΔΖΒΣΠΦΟΕΥΙΖΡΒΔΜΒΘΖΝΒΔΖΒΣΠΦΟΕΥΙΖΡΒΔΜΒΘΖ

ΟΖΒΣΥΙΖΓΒΝΝΤ

ΟΖΒΣΥΙΖΓΒΝΝΤ

ΟΖΒΣΥΙΖΓΒΝΝΤΟΖΒΣΥΙΖΓΒΝΝΤ

C627

1UF-0805

C645

0.1UF

3

C619

10UF/6.3V-1206

C680

10UF/6.3V-1206

C628

1UF-0805

R533

1K 1%

CMOSREF

R534

2K 1%

C629

1UF-0805

C618

10UF/6.3V-1206

VCORE VTT

C679

10UF/6.3V-1206

VTT

ࣜࣿࣜ

ࣜࣿࣜ

ࣜࣿࣜࣜࣿࣜ

ࣿ

ࣿ

ࣿࣿ

C626

1UF-0805

C644

0.1UF

ΡΖΣΚΡΙΖΣΪ

ΡΖΣΚΡΙΖΣΪΡΖΣΚΡΙΖΣΪ

C620

10UF/6.3V-1206

VTT

C640

0.1UF

C630

1UF

C621

10UF/6.3V-1206

C641

0.1UF

C631

1UF

C642

0.1UF

C622

10UF/6.3V-1206

TESTHI2TESTHI1-

C632

1UF

ʹΝΠΤΖΥΠΥΙΖΡΒΔΜΒΘΖΒΟΕΒΝΝΒΣΖΉΥ

ʹΝΠΤΖΥΠΥΙΖΡΒΔΜΒΘΖΒΟΕΒΝΝΒΣΖΉΥΪΡΖ

ʹΝΠΤΖΥΠΥΙΖΡΒΔΜΒΘΖΒΟΕΒΝΝΒΣΖΉΥʹΝΠΤΖΥΠΥΙΖΡΒΔΜΒΘΖΒΟΕΒΝΝΒΣΖΉΥ

Change to 0603 Type (05/18/01)

VTTVCC1.5V

C643

0.1UF

2

R515 1K

R516 1K

C633

1UF

R531

1K 1%

VREF

R532

2K 1%

C623

10UF/6.3V-1206

C634

1UF

ALPHA-TOP CORP.

Title

Size Document Number Rev

Date: Sheet

1

C592

1UF-0805

C603

0.47UF

0.47UF

C615

0.47UF

0.47UF

C624

10UF/6.3V-1206

C636

C635

1UF

1UF

G510 MAIN BOARD

G510-1-4-01 2.0

C604

0.47UF

C616

0.47UF

C605

0.47UF

C617

0.47UF

C625

10UF/6.3V-1206

C637

1UF

ΪΡΖ

ΪΡΖΪΡΖ

1

C638

1UF

329Friday, November 09, 2001

of

C639

1UF

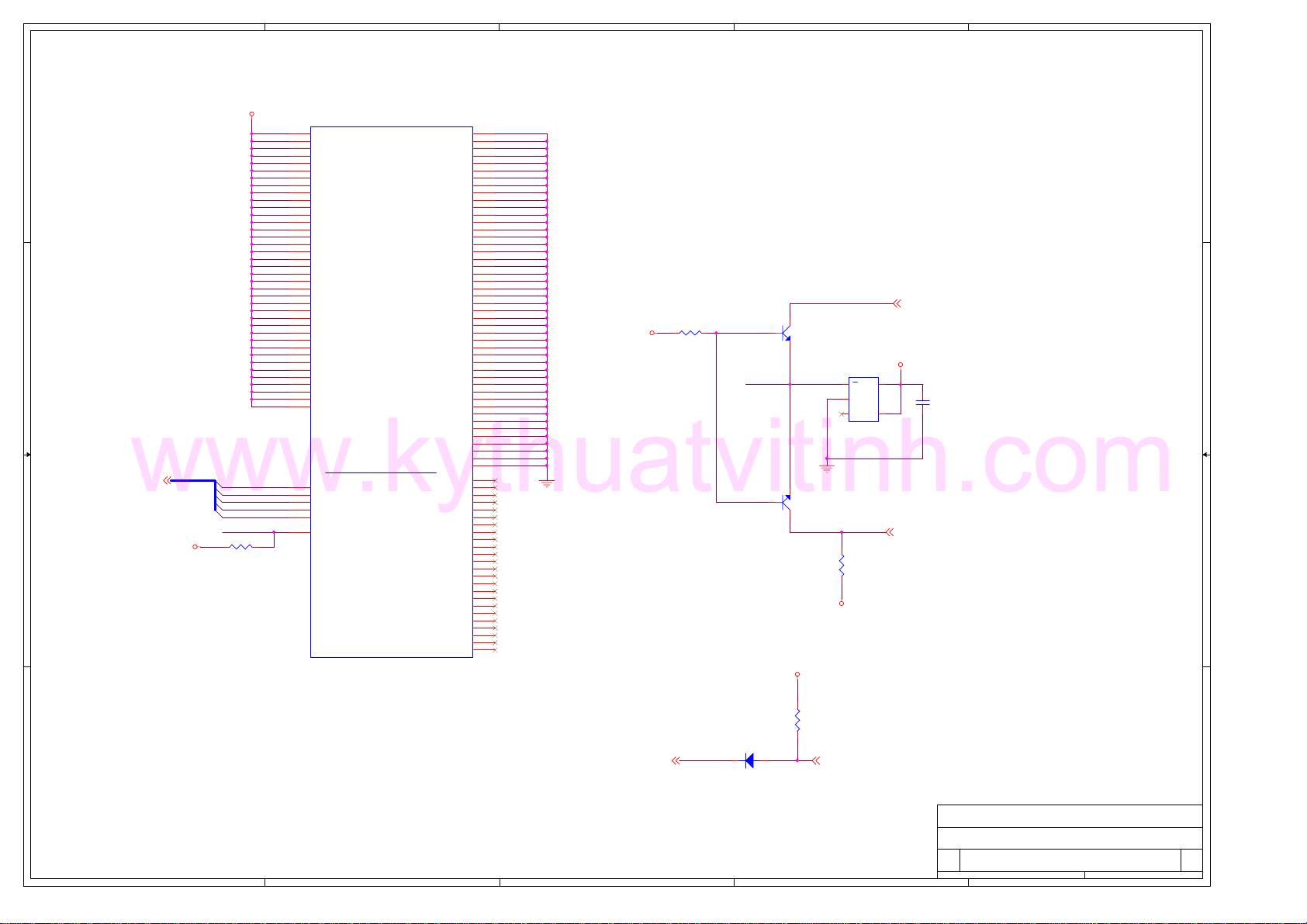

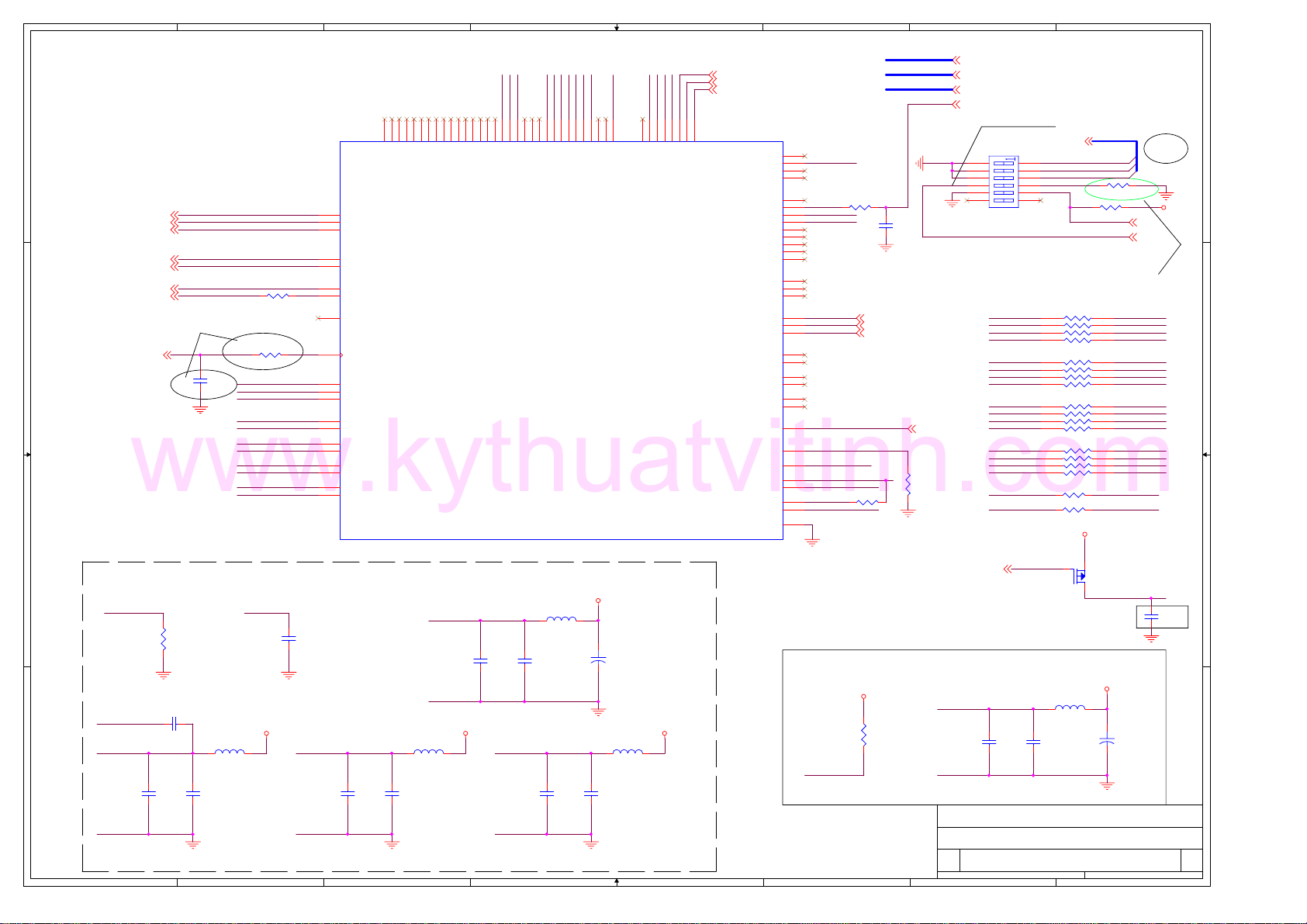

Page 4

5

www.kythuatvitinh.com

4

3

2

1

VTT

D D

C C

VD[0..4]25

B B

VD[0..4]

VTT

R537

1K

VTTPWRGD

VD0

VD1

VD2

VD3

VD4

A26

C11

C13

C15

C17

C19

C21

G23

N23

R23

U23

W23

AA4

AA23

AC4

AC23

AD6

AD8

AD12

AD14

AD18

AD20

AE3

AE18

AF1

AF2

AB1

AC2

AE2

AF3

C5

C7

C9

D5

E4

E6

G4

J4

J23

L4

L23

V4

R3

E3

U39C

VCCT1

VCCT2

VCCT3

VCCT4

VCCT5

VCCT6

VCCT7

VCCT8

VCCT9

VCCT10

VCCT11

VCCT12

POWER, GROUND AND NC

VCCT13

VCCT14

VCCT15

VCCT16

VCCT17

VCCT18

VCCT19

VCCT20

VCCT21

VCCT22

VCCT23

VCCT24

VCCT25

VCCT26

VCCT27

VCCT28

VCCT29

VCCT30

VCCT31

VCCT32

VCCT33

VCCT34

VCCT35

VCCT36

VCCT37

VCCT38

VID0

VID1

VID2

VID3

VID4

VTTPWRGD

TUALATIN

3 OF 3

VID

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

TUALATIN_5

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB2

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC6

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC25

AD2

AE1

AE5

AE7

AE9

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AE26

AF25

AF26

H5

A2

A5

A11

B1

C1

C4

C22

D1

D26

E1

F1

N4

N24

P1

P4

P5

P26

AD4

AD13

AD23

AE8

AE10

AF17

AF18

VTT

R536 100

B

VTTPWRGD

B

Q57

3904

E C

EC

Q63

3904

VCC1.5V

1

VDDGR

2

3 4

RWDI

U42

TPS3125J12DBVR

MARKING:PBTI

R595

100K

VCC3

VR_ON 25

VTT

5

VTTPWGD 5

C646

0.1UF

R597

1.5K

A A

5

4

CPU_STP-5,9

3

D53

ASD500V

DPSLP- 2,25

2

ALPHA-TOP CORP.

Title

G510 MAIN BOARD

Size Document Number Rev

G510-1-4-01 2.0

Date: Sheet

429Friday, November 09, 2001

1

of

Page 5

5

www.kythuatvitinh.com

VCCLK

VCC3

L32

FCM2012K-600-0805

D D

C460

C478

0.001UF

+

L17

FCM2012K-600-0805

C130

+

0.1UF

VOSCI8

C458

0.1UF

C484

10UF/10V-A

VCC2.5V

C C

10UF/10V-A

B B

C561

CAP

C475

0.1UF

C457

0.001UF

C562

CAP

C459

0.001UF

VOSCI

SMBC9,11

SMBD9,11

C123

0.1UF

C563

CAP

VCCLK

C476

C477

0.001UF

0.1UF

R358 33

C564

CAP

C129

0.001UF

C462

0.1UF

4

C565

CAP

C461

0.001UF

C566

CAP

3

5

9

18

22

30

37

4

12

17

25

31

36

11

44

46

26

43

CLK1

ICS950104AF

VDDCPU

AVDD

VDDREF

VDDPCI

AVDD48MHZ

VDD

VDD

GND

GND

GND

GND

GND

GND

REF2

VDDL

GNDL

SCLK

SDATA

X1

6

14.318MHz

C455

10PF

MULTISEL/24_48MHZ

Y5

CPUCLK

CPUC0

CPUT0

FS2/PCICLK_F

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

FS0/REF0

FS1/REF1

FS3/48MHZ/ZSEL

SDRAM7

SDRAM6

SDRAM5

SDRAM4

SDRAM3

SDRAM2

SDRAM1

SDRAM0

PCI_STOP#

CPU_STOP#

PD#/Vtt_PWRGD

SDRAM_STOP#

X2

7

C451

10PF

IREF

GND

3

45

1

2

13

14

15

16

19

20

21

8

10

23

24

32

33

34

35

38

39

40

41

29

28

27

SDRAM_STOP-

42

47

48

MULTISEL

FS3

SDRAM7

SDRAM6

SDRAM5

PCI_STOP-

R115

R113

R587

R363

R364

R366 33

R369 33

R371

R374

R376

FS0

FS1

R142

R139

R135

R134

R133

R125

R124

CPU_STP-

R386

221 1%

2

CPUCLK "+" and "-"

exchange

630SCCLK

0

5.1

5.1

630PCLKFS2

33

TIPCI

33

MINICLK

SIOPCLK

VGACLK

33

MINI2CLK

33

PICCLK

33

22

22

10

10

10

18

15

CPU_STP- 4,9

VTTPWGD 4

CPUCLKCPUCLK+

Add for Mobile Tualatin

SIO48M

UCLK48M

630SCCLK 6

CPUCLK- 2

CPUCLK+ 2

630PCLK 7

TIPCI 21

MINICLK 23

SIOPCLK 17

VGACLK 8

MINI2CLK 23

PICCLK 2

SIO48M 17

UCLK48M 9

630SDCLK 6

SDCLK0 11

SDCLK1 11

SDCLK2 11

SDCLK3 11

Adjust SDRAM CLOCK

1

By-Pass Capacitors

Place near to the Clock Gernerator

630SCCLK

630PCLK

TIPCI

VOSCI

SIO48M

UCLK48M

SDCLK3

SDCLK2

SDCLK0

630SDCLK

SDCLK1

MINICLK

CPUCLK+

CPUCLKVGACLK

SIOPCLK

MINI2CLK

PICCLK

SDRAM7

SDRAM6

SDRAM5

C147 10PFR

C466 10PF

C467 10PF

C454 10PF

C190 10PF

C188 10PF

C175 18PF

C178 10PF

C184 10PF

C174 10PF

C181 10PF

C468 10PF

C142 10PFR

C724 10PFR

C469 10PF

C715 10PF

Add from G510

R120

R122

R123

DEL R348,C449

10

10

10

C470 10PF

C473 10PF

C165 10PF

C166 10PF

C171 10PF

VCC3

10K

10K

MULTISEL

PCI_STOP-

SDRAM_STOP-

CPU_STP-

FS3

R385

10K

3

FS0

R143 10KR

R380 10K

R379 10K

R538 10K

(FS3)

A A

1

1

1

1

1

1

1

1

1

0

0

0

0 31.7

0

0

0

0

5

1

10

1

0

1

1

0

1

0

1

0

0

0

0

0

1 33.4

1

1

1

0

1

1

0

0

1

1

0

0

0

0

0

SIS630S CLOCK

(FS1)

(FS2)

(FS0)

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

CPU

(MHz)

66.6

100

150

133.3

66.8

100

100

133.3

66.8

97.0

70.0

95.0

95.0

112

97.0

96.2

SDRAM

(MHz)

100

100

100

100

133.6

133.3

150

133.3

66.8

97.0

105

95.0

126.7

112

129.3

96.2

PCI

(MHz)

33.3

33.3

37.5

33.3

33.4

33.3

37.5

33.3

32.3

35.0

31.7

37.3

32.2

32.1

4

R588

R589

FS2

FS1

Adjust CPU CLK from BSEL1

2

SDCLKSEL 8

BSEL1 2

ALPHA-TOP CORP.

Title

CLOCK GENERATOR

Size Document Number Rev

G510-1-4-01 2.0

Date: Sheet

529Friday, November 09, 2001

1

of

Page 6

8

www.kythuatvitinh.com

VTT

7

VTT

6

5

4

3

2

1

R99

75 1%

R103

D D

C C

B B

150 1%

630SCCLK

-RS[0..2]

-HREQ[0..4]

630SCCLK5

HLOCK-2

DEFER-2

HTRDY-2

CPURST-2

BPRI-2

BREQ0-2

ADS-2

HITM-2

DRDY-2

DBSY-2

BNR-2

CB5

0.001UF

GTLVREFA

CB6

0.001UF

For EMI test

C708

CAP

630SCCLK

HLOCKDEFERHTRDYCPURST-

BPRI-

BREQ0-

-RS2

-RS1

-RS0

ADS-

HITM-

HIT-

HIT-2

DRDYDBSY-

BNR-

-HREQ4

-HREQ3

-HREQ2

-HREQ1

-HREQ0

HA31

HA30

HA29

HA28

HA27

HA26

HA25

HA24

HA23

HA21

HA20

HA19

HA18

HA17

HA16

HA15

HA14

HA13

HA12

HA11

HA10

HA9

HA8

HA7

HA6

HA5

HA4

HA3

GTLVREFA

GTLVREFB

R312

75 1%

150 1%

R310

P29

A24

B24

P26

V29

T29

R26

P25

G27

R29

G28

V26

R25

U29

U26

R24

U28

T27

U27

P28

R27

T26

T28

R28

P27

M24

H26

G29

H29

H27

K27

H28

K26

K28

L26

L27

L28

K29

M25

M26

M27

L29

N25

N28

M28

M29

N29

N26

P24

N27

J26

J29

J27

J28

CB2

0.001UF

GTLVREFB

CB3

0.001UF

GTLVREFA

GTLVREFB

VSSQA

VSSQB

CPUCLK

HLOCK#

DEFER#

HTRDY#

CPURST#

BPRI#

BREQ0#

RS#[2]

RS#[1]

RS#[0]

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ#[4]

HREQ#[3]

HREQ#[2]

HREQ#[1]

HREQ#[0]

HA#[31]

HA#[30]

HA#[29]

HA#[28]

HA#[27]

HA#[26]

HA#[25]

HA#[24]

HA#[23]

HA#[22]

HA#[21]

HA#[20]

HA#[19]

HA#[18]

HA#[17]

HA#[16]

HA#[15]

HA#[14]

HA#[13]

HA#[12]

HA#[11]

HA#[10]

HA#[9]

HA#[8]

HA#[7]

HA#[6]

HA#[5]

HA#[4]

HA#[3]

MD63

T25

MD63

MD62

W28

MD62

MD61

W27

MD61

MD60

Y29

MD60

MD59

Y27

MD59

MD58

Y26

MD58

MD57

AA28

MD57

MD56

AA26

MD56

MD55

AB28

MD54

AB26

MD55

MD53

AC29

MD54

MD52

AC27

MD53

MD51

AC25

MD52

MD50

AD28

MD51

MD49

AD27

MD50

MD48

Y25

MD49

MD47

AG22

MD48

AJ22

MD47

MD45

AF21

MD46

MD44

AH21

MD45

MD43

AF20

MD44

MD42

AH20

MD43

MD41

AJ20

MD42

MD40

AG19

MD41

MD39

AJ19

MD40

MD39

MD38

AF18

MD38

MD37

AH18

MD37

MD36

AF17

MD36

MD35

AG17

MD35

MD34

AJ17

MD34

MD33

AF16

MD33

MD32

AH16

MD46

MEMORY

630S-1

HOST

MD31

T24

MD32

MD30

W29

MD31

MD29

U25

MD30

MD28

W26

MD29

MD27

Y28

MD28

MD26

V25

MD27

MD25

AA29

MD26

MD24

AA27

MD25

MD23

AB29

MD24

MD22

AB27

MD23

MD21

V24

MD22

MD20

AC28

MD21

MD19

AC26

MD20

MD18

AD29

MD19

MD17

W25

MD18

MD16

AD26

MD17

MD15

AF22

MD16

MD14

AH22

MD15

MD13

AE23

MD14

MD12

AG21

MD13

MD11

AJ21

MD12

MD10

AG20

MD11

MD9

AE22

MD10

MD9

MD8

AF19

MD8

MD7

AH19

MD7

MD6

AE18

MD6

MD5

AG18

MD5

MD4

AJ18

MD4

MD3

AD20

MD3

MD2

AH17

MD2

MD1

AE21

MD1

MD0

AG16

MD0

CSA#[5]

CSA#[4]

CSA#[3]

CSA#[2]

CSA#[1]

CSA#[0]

CSB#[5]

CSB#[4]

CSB#[3]

CSB#[2]

CSB#[1]

CSB#[0]

MA[14]

MA[13]

MA[12]

MA[11]

MA[10]

DQM[7]

DQM[6]

DQM[5]

DQM[4]

DQM[3]

DQM[2]

DQM[1]

DQM[0]

SRAS#

SCAS#

SDCLK

MA[9]

MA[8]

MA[7]

MA[6]

MA[5]

MA[4]

MA[3]

MA[2]

MA[1]

MA[0]

WE#

CKE

MD[0..63]

CHIPSET1

AE24

AG24

AF24

AJ25

AH25

AG25

AF28

AF29

AA25

AE25

AE26

AE27

AB25

AF27

AF26

AG29

AG28

AG27

AH28

AB24

AH27

AD24

AJ27

AG26

AH26

AJ26

AF25

Y24

AE28

AF23

AG23

AD25

AE29

AJ24

AD22

AH23

AH24

AJ23

AJ16

E9

MD[0..63] 11

CSA-3

CSA-2

CSA-0

R367 10

R373 10

R377 10

RP43

10X4

RP44

10X4

RP45

10X4

R150

R148

R149

12

R88

8.2K

CSA-[0..3]

MA[0..14]

DQM[0..7]

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

DQM7

DQM6

DQM5

DQM4

DQM3

DQM2

DQM1HA22

DQM0

10

10

10

630SDCLK

Q30

D

2N7002

G

RAMW-

SRASSCAS-

SD

CSA-[0..3] 11

MA[0..14] 11

DQM[0..7] 11

MA14

MA13

MA12

MA11

MA10

MA9

MA8

MA7

MA6

MA5

MA4

MA3

MA2

MA1

MA0

RAMW- 11

SRAS- 11

SCAS- 11

CKE 19

ON_OFF 28

630SDCLK 5

C709

CAP

CPUAVDD

HD#62

HD#63

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HD#53

HD#52

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

HD#11

HD#10

HD#9

HD#8

HD#7

HD#6

HD#5

HD#4

HD#3

HD#2

HD#1

L25

HD5

K25

HD4

F29

HD3

F28

HD2

G26

HD1

G25

HD0

HD#0

SDAVDD

SDAVSS

SIS_ALS

630S-1

AE19

AE20

C167

0.01UF

3

R147 0

C168

1UF-0805

ALPHA-TOP CORP.

Title

SIS630S HOST/DRAM

Size Document Number Rev

G510-1-4-01 2.0

Date: Sheet

2

+

C195

10UF/10V-A

For EMI test

629Friday, November 09, 2001

of

1

C148

0.01UF

V27

V28

CPUAVSS

A19

E21

HD63

HD62

C19

HD61

B20

HD60

B21

HD59

B19

HD58

6

A21

HD57

A20

HD56

D19

HD55

E20

HD54

D20

HD53

B22

HD52

C22

HD51

C20

HD50

A22

HD49

D21

HD48

A23

HD47

C21

HD46

B23

HD45

C23

HD44

A25

HD43

E22

HD42

D22

HD41

D24

HD40

D23

HD39

5

C25

HD38

B25

HD37

C24

HD36

E25

HD35

F22

HD34

D25

HD33

E23

HD32

B26

HD31

E24

HD30

C26

HD29

A26

HD28

A27

HD27

D26

HD26

B27

HD25

C27

HD24

B28

HD23

F24

HD22

C28

HD21

D28

HD20

H24

HD19

4

C29

HD18

E26

HD17

D27

HD16

J25

HD15

E28

HD14

D29

HD13

E27

HD12

H25

HD11

K24

HD10

F25

HD9

F27

HD8

E29

HD7

F26

HD6

VCC3 VCC3

R117 0

C463

+

A A

HD[0..63]2

HA[3..31]2

-HREQ[0..4]2

-RS[0..2]2

8

10UF/10V-A

HD[0..63]

HA[3..31]

-HREQ[0..4]

-RS[0..2]

C145

1UF-0805

7

Page 7

8

www.kythuatvitinh.com

D D

AD[0..31]21,23

AD[0..31]

7

6

AD29

AD31

AD30

AD28

AD27

AD26

AD25

AD24

AD23

5

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

4

AD0

AD1

C479

0.001UF

3

C480

0.1UF

R381

0

(For internal PLL)

VCC1.8V

C483

+

10UF/10V-A

2

1

ICHRDYA

IDREQ[A]

IIRQA

CBLIDA

IIOR#[A]

IIOW#[A]

IDACK#[A]

IDSAA[2]

IDSAA[1]

IDSAA[0]

IDECSA#[1]

IDECSA#[0]

ICHRDYB

IDREQ[B]

IIRQB

CBLIDB

IIOR#[B]

IIOW#[B]

IDACK#[B]

IDSAB[2]

IDSAB[1]

IDSAB[0]

IDECSB#[1]

IDECSB#[0]

CHIPSET2

AE13

AG8

AF9

AH9

AH8

AF8

AJ8

AD14

AE14

AG9

AF10

AJ9

AH13

AD17

AF15

AG15

AG13

AF13

AJ13

AG14

AF14

AD18

AJ14

AH14

630S-2

IDESAA2

IDESAA1

IDESAA0

IDECS-A1

IDECS-A0

IDESAB2

IDESAB1

IDESAB0

IDECS-B1

IDECS-B0

IDESAA[0..2]

IDECS-A[0..1]

IDESAB[0..2]

IDECS-B[0..1]

IDEDA[0..15]

IDEDB[0..15]

ICHRDYA

IDEREQA

IDEIRQA

CBLIDA

IDEIOR-A

IDEIOW-A

IDACK-A

ICHRDYB

IDEREQB

IDEIRQB

IDEIOR-B

IDEIOW-B

IDACK-B

ICHRDYA 13

IDEREQA 13

IDEIRQA 13

CBLIDA 13

IDEIOR-A 13

IDEIOW-A 13

IDACK-A 13

IDESAA[0..2] 13

IDECS-A[0..1] 13

ICHRDYB 13

IDEREQB 13

IDEIRQB 13

IDEIOR-B 13

IDEIOW-B 13

IDACK-B 13

IDESAB[0..2] 13

IDECS-B[0..1] 13

IDEDA[0..15] 13

IDEDB[0..15] 13

M4M2M3

N5

AD16

IDB15

AJ12

IDEDB15

AD15

AE8

IDEDA0

AD14

IDA0

AE12

IDEDA1

AD13

IDA1

AG7

L3K1K2M5K3K4L5G1G2G3G4F1K5F2F4E1E2K6E3J4E4

AD11

AD12

IDA3

IDA2

AD12

AJ6

IDEDA2

IDEDA3

N6

L2

AD9

AD8

AD10

IDE

IDA6

IDA5

IDA4

AH5

AE11

AF6

IDEDA4

IDEDA7

IDEDA6

IDEDA5

M1N4P6N3AH15

AD3

AD7

AD4

AD5

AD6

IDA11

IDA10

IDA9

IDA8

IDA7

AH6

AG6

AE6

AJ5

IDEDA10

IDEDA11

IDEDA8

IDEDA9

AD2

AD1

IDA13

IDA12

AH7

AF7

IDEDA13

IDEDA12

AD0

IDA14

IDA15

AJ7

AD13

IDEDA14

IDEDA15

IDEAVDD

D1

PREQ-[0..2]19,21,23

PGNT-[0..2]19,21,23

C/BE-[0..3]21,23

C C

FRAME-19,21,23

DEVSEL-19,21,23

PLOCK-19

PCIRST-8,17,18,19,21,23

B B

630PCLK5

PREQ-[0..2]

PGNT-[0..2]

C/BE-[0..3]

INT-A19,21

INT-B19

INT-C19,23

INT-D19,23

IRDY-19,21,23

TRDY-19,21,23

STOP-19,21,23

SERR-19,21,23

PAR21,23

FRAME-

DEVSELPLOCK-

PCIRST-

IRDYTRDYSTOP-

INT-A

INT-B

INT-C

INT-D

SERR-

PAR

PREQ-2

PREQ-1

PREQ-0

PGNT-2

PGNT-1

PGNT-0

C/BE-3

C/BE-2

C/BE-1

C/BE-0

R311 33

AJ15

C1

PREQ#[2]

C2

PREQ#[1]

C3

PREQ#[0]

D2

PGNT#[2]

D3

PGNT#[1]

D4

PGNT#[0]

F3

C/BE#[3]

H4

C/BE#[2]

J1

C/BE#[1]

L1

C/BE#[0]

N1

INTA#

P4

INTB#

P5

INTC#

P3

INTD#

H3

FRAME#

H2

IRDY#

H1

TRDY#

J2

STOP#

B11

SERR#

M6

PAR

J3

DEVSEL#

L4

PLOCK#

PCICLK

C11

PCIRST#

AD31

PCI

IDB0

AE17

AG12

IDEDB0

AD24

AD25

AD26

AD27

AD28

AD29

AD30

630S-2

IDB1

IDB2

IDB3

IDB4

IDB5

IDB6

IDB7

AF12

AH11

AE16

AJ10

AD15

AE15

AG10

IDEDB4

IDEDB1

IDEDB6

IDEDB2

IDEDB7

IDEDB3

IDEDB5

AD22

AD23

IDB8

IDB9

AH10

IDEDB9

IDEDB8

AD20

AD21

IDB10

IDB11

AF11

AG11

IDEDB10

IDEDB11

AD18

AD19

IDB12

IDB13

AJ11

AD16

IDEDB13

IDEDB12

AD17

IDB14

AH12

IDEDB14

A A

ALPHA-TOP CORP.

Title

SIS630S PCI/IDE

Size Document Number Rev

G510-1-4-01 2.0

8

7

6

5

4

3

Date: Sheet

2

729Friday, November 09, 2001

of

1

Page 8

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

RR[2..7]

LVDSPD- 22

VBVSYNC 22

VBHSYNC 22

VCC3

R368

59 1%

GG[2..7]

BB[2..7]

C143

10PF

ENPVDD- 22 GG[2..7] 22

G2

R2

R3

B3

AAD18/B3

AAD19/B0

AAD20/B1

AAD21/R1

AAD22/R2

L14

1 2

FCM2012K-600-0805

C90

1UF-0805

C110

0.01UF

5

R4

AAD23/R3

AAD24/R4

B5

B2

AE4

AE3

AE2

AE1

AD5

AD4

AD1

AC4

AC3

AC2

AC5

AD6

AG1

AF3

AF2

D D

B14

ROUT12

GOUT12

BOUT12

HSYN12

VSYN12

DDC1DATA12,22

DDC1CLK12,22

R318

0

For EMI test

C C

B B

A A

Place these circuits near to SiS-630S

VRSET

VCOMP

DACAVDDC

DACAVSSC

8

VOSCI5

R68

140 1%

C413 1UF-0805

C106

0.01UF

R575 0

C718

CAP

L28

1 2

FCM2012K-600-0805

C435

1UF-0805

VRSET

VVREF

VCOMP

ECLKAVDD

DCLKAVDD

DCLKAVSS

DACAVDDC

DACAVSSC

DACAVDDB

DACAVSSB

VVREF

C414

0.1UF

VCC3 VCC3

DACAVDDB

DACAVSSB

7

A14

A15

D15

A16

C15

B16

C16

A11

E19

C14

B15

F15

F16

E16

F18

F20

E14

D14

ROUT

GOUT

BOUT

HSYNC

VSYNC

DDC1DATA

DDC1CLK

SSYNC

VOSCI

RSET

VREF

COMP

ECLKAVDD

DCLKAVDD

DCLKAVSS

DACAVDDC

DACAVSSC

DACAVDDB

DACAVSSB

CHIPSET3

630S-3

C99

0.01UF

AF1

AAD5

AAD0

AAD1

AAD2

AAD3

AAD4

L15

1 2

FCM2012K-600-0805

C89

1UF-0805

6

AAD6

AAD7

AAD8

VGA

DCLKAVDD

DCLKAVSS

AAD9

AA4Y5Y4Y3Y2Y1W4W3V5V4V3V2V1U5U4

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16/B5

AAD17/B2

630S-3

C109

0.01UF

ECLKAVDD

ECLKAVSS

R5

R6

AAD25/R5

AAD26/R6

R7

AAD27/R7

G3

W5

AAD28/G2

AAD29/G0

AAD30/G1

AAD31/G3

AGP

VCC3

CE3

+

10UF/10V-A

L29

1 2

FCM2012K-600-0805

C429

1UF-0805

G6

G7

G4

G5

U2U1T5T4T1R1R2

SBA7

SBA6/G4

SBA5/G5

SBA4/G6

VCC3

ENBLT- 22

VBBLANK- 22 BB[2..7] 22

R3

U3

SBA3/G7

SBA2/DDC2CLK

SBA1/DDC2DAT

SBA0/VBBLANK#

4

R0/ACBE3#

B4/ACBE2#

ACBE1#

ACBE0#

VBCAD/AREQ#

VGCLK/AGNT#

B7/AFRAME#

B6/AIRDY#

ATRDY#

ADEVSEL

ASERR#

APAR

ASTOP#

VBHCLK/RBF#

VBCTL0/WBF#

VBCTL1/PIPE#

VBCLK/ST2

VBVSYNC/ST1

VBHSYNC/ST0

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

AGPCLKECLKAVSS

AGPVREF

AGPRCOMP

AGPAVDD1

AGPAVSS1

AGPAVDD2

AGPAVSS2

AGPVSSREF

AA3

AC1

AG2

R6

T6

AB2

Y6

AB3

AB4

AB6

AA5

AB5

P2

P1

U6

R4

R5

V6

T2

T3

AD2

AD3

W1

W2

AJ3E15

AA1

AB1

AE10

AD10

AE9

AD8

AA2

B4

R114 22

B7

B6

VGACLKECLKAVSS

AGPRCOMP

AGPAVDD1

AGPAVSS1

R461 0R

AGPAVDD2

AGPAVSS1 BB7

AGPRCOMP

3

RR[2..7] 22

LVDSCLK 22

Adjust SDRAM CLK

PID[0..2]

PID0

PID1

PID2

R586 10K

R497 10K

KBSEL 18

SDCLKSEL 5

1

2

3

4

5

SW DIP-6

PID[0..2]9

S1

12

11

10

9

8

76

1(OPEN)<---------------->0(CLOSE,DEFAULT)

Pull Low for ClkGen's bug

R5

R4

R2

G3

G2

R7

R6

R3

G5

G6

G7

VGACLK 5

R365

8.2K

AGPAVDD1

AGPAVSS1

Place these circuits near to SiS-630S

ALPHA-TOP CORP.

Title

Size Document Number Rev

Date: Sheet

G4

B3

B2

B4

B5

B6

B7

PCIRST-7,17,18,19,21,23

C170

0.01UF

SIS630S VGA/DFP

G510-1-4-01 2.0

2

RP4 22X4

1 8

2 7

3 6

4 5

RP38 22X4

RP36 22X4

RP40 22X4

R361 22

R372 22

VCC3

G

CLOSE TO SiS630S

L19

1 2

FCM2012K-600-0805

C186

1UF-0805

D S

18

27

36

45

18

27

36

45

18

27

36

45

NDS356P

Q55

AGPAVDD2

VCC3

+

CE2

10UF/10V-A

829Friday, November 09, 2001

1

RR5

RR4

RR2

GG3

GG2

RR7

RR6

RR3

GG5

GG6

GG7

GG4

BB3

BB2

BB4

BB5

BB6

of

DEL RP55

VCC5

C560

0.1UF

Page 9

8

www.kythuatvitinh.com

PID[0..2]8

Place near to 630S

BIT_CLK

D D

NEDD NOT to place

near to 630S

ENTEST

AC'97 Pull-Down

In order to stabilize

630S AC,97 controller

pull-down resistors on

SDATI1 and SDATI0 can

not be removed.

C C

SDATI1

SDATI0

B B

A A

R317 100K

R319 100K

8

PSON-20,26,27

SIS_ALS

R351

4.7K

C100

10PFR

R452

10K

1 2

AC_RESET-15,23

BIT_CLK15,23

PWROK19

PSON-

7

PID[0..2]

SPKR16

KBSMI-18

RING14

PME-17,21,23

GMUXSEL25

LO_HI-3

GV_GATE19

VCORE1.4V-25

SWI-18

SCI18

SPDIF15,16

D27 BAT54

VCC3

Q50

2N7002

SD

D

G

7

SDATI1

SDATI0

SDATO

SYNC

A

NC

BIT_CLK

AUXOK

BATOK

R170

10K

SIS_PSON-

SDATI123

SDATI015

SDATO15,23

SYNC15,23

AUXOK20

BATOK20

SPKR

SIS_PSON-

KBSMIRING

PMETHERM-

LO_HIGV_GATE

GPIO13

ENTEST

SWISCI

GPIO2

PID0

PID1

PID2

GPIO6

SPDIF

GPIO8

GPIO9

R87 0

R316 0

C

RTCVDD

C505

0.1UF

6

CHIPSET4

630S-4

E18

SPK

E11

PSON#

C7

ACPILED

B12

EXTSMI#

E10

PWRBTN#

B6

RING

A6

PME#

D13

THERM#

B7

KBDAT/GP10

A7

KBCLK/GP11

D8

PMDAT/GP12

C8

PMCLK/GP13

B8

KLOCK#/GP14/TXD

AE7

RESERVE2

AH2

RESERVE1

N2

ENTEST

C12

GP0/PREQ#3/TXD[

D12

GP1/PGNT#3/TXD[

E17

GP2/LDRQ1#/TXD[

F12

GP3/RXER

C10

GP4/TXCLK

F14

GP5/COL

C6

GP6/CRS

E12

GP7/SPDIF

D9

GP8/MDC

D10

GP9/RXCLK

B10

AC_SDIN[1]

A10

AC_SDIN[0]

A13

AC_SDOUT

B13

AC_SYNC

D11

AC_RESET#

C13

AC_BIT_CLK

A5

AUXOK

C5

BATOK

C4

PWROK

A4

RTCVDD

A3

RTCVSS

6

ACPI

KBC

AC97

RTC

OSC32KHI

B4

R79

1 2

10M

Y2

32.768K

1 4

2

C88

10PF

Place close to 630S

PWRBTN-

OSC32KHO

B5

3

C87

10PF

JP8

12

5

34

Power Button

5

630S-4

VSSA

VSSB

VSSC

VSSD

F13

F17

N24

U24

PWRBTN-

5

ON3_5

+3VALWAYS

D43

1SS355 SOD323

4

LPC

CPU_S

SMB

USB

3

LAD0

LAD1

LAD2

LAD3

LDRQ#

LFRAME#

SIRQ

SMI#

INTR

A20M#

INIT#

IGNNE#

FERR#

STPCLK#

CPUSTOP#/CPUSLP

SMCLK

SMBDAT

TXEN/GP15/SMBAL

RXDV/OC0#

MDIO/OC1#

UV0-

UV0+

UV1-

UV1+

UV2-

UV2+

UV3-

UV3+

UV4-

UV4+

UV5-

UV5+

USBCLK48M

USBVDD0

USBVDD1

2

SMBD

GPIO15

LAD[0..3] 17

LDRQ- 17

LFRAME- 17

SERIRQ 17,21

NMI 2

SMI- 2

INTR 2

A20M- 2

CPUINIT- 2

IGNNE- 2

FERR- 2

STPCLK- 2

CPU_STP- 4,5

SMBC 5,11

SMBD 5,11

+3VAUX

UV0- 12

UV0+ 12

UV1- 12

UV1+ 12

UV2- 12

UV2+ 12

UV3- 12

UV3+ 12

UV4- 12

UV4+ 12

UV5- 12

UV5+ 12

UCLK48M 5

CB1 1UF-0805

Over current disable

+3VAUX

CE4

+

10UF/10V-A

AG4

AF4

AJ4

AE5

AF5

AH4

AG5

C18

NMI

D16

D18

B17

A17

B18

A18

C17

D17

AH3

AG3

A8

F10

D6

H5

J5

G5

H6

E5

F5

E6

F6

F8

E7

E8

D7

A12

B2

B3

LAD0

LAD1

LAD2

LAD3

LDRQLFRAME-PWRBTNSERIRQ

SMBC

R578 10K

1 2

1 2

R462 10K

CB4

0.1UF

1

MII

C9

RXD[0]

B9

RXD[1]

E13

RXD[2]

A9

RXD[3]

D54

ASD500V

3

SIS_ALS

R607

56K

D5

PWRBTN-

PME-

PID0

PID1

PID2

GPIO6

GPIO8

GPIO9

GPIO15

R428 20K

1 2

R11 10K

1 8

2 7

3 6

4 5

RP19 4.7KX4

1 8

2 7

3 6

4 5

RP35 4.7KX4

GMUXSEL 25

ALPHA-TOP CORP.

Title

SIS630S SOUTH BRIDGE

Size Document Number Rev

G510-1-4-01 2.0

Date: Sheet

2

LANCLK25M

Q45

SIS_ALS

DS

NDS352AP

G

Q49

B

4

DTC114EKA SOT-23

GPIO13 GMUXSEL

E C

R600

4.7K

1 2

Add for SiS's bug

+3VALWAYS

SIS_ALS

SERIRQ

SMBC

SMBD

THERM-

LAD3

LAD2

LAD0

LAD1

SWILDRQGPIO2

RP50

1 8

2 7

3 6

4 5

4.7KX4

RP16

4.7KX4

RP51

1 8

2 7

3 6

4 5

4.7KX4

929Friday, November 09, 2001

of

1

VCC3

VCC3

18

27

36

45

VCC3

Page 10

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

VCC3

VCC1.8V

C137

1UF-0805

C155

1UF-0805

C146

0.1UF

C150

0.1UF

10UF/10V-A

SIS_ALS

CE1

+

+1.8VALWAYS

VTT

C107

0.1UF

C132

1UF-0805

C127

1UF-0805

C139

0.1UF

C126

0.1UF

C115

1UF-0805

C120

1UF-0805

C121

0.1UF

C105

0.1UF

C108

0.01UF

VCC1.8V

VCC3

AA11

AA12

AA13

AA18

AA19

AA20

AA22

AB12

AB19

AB21

AB22

W21

W22

AB10

AB11

AB13

AB18

AB20

AA10

AA14

AA17

AA21

AB14

AB17

M21

VCC3

AA8

AA9

AB8

AB9N8P8P9U8V8V9W8W9Y8Y9

OVDD

OVDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

OVDD

H10

OVDD

H17

OVDD

J11

OVDD

J12

OVDD

J9

OVDD

K8

OVDD

K9

OVDD

M9

OVDD

U21

OVDD

U22

OVDD

V21

OVDD

V22

OVDD

OVDD

OVDD

Y21

OVDD

PVDD

PVDD

PVDD

PVDD

PVDD

H11

PVDD

H12

PVDD

H18

PVDD

J18

PVDD

L8

PVDD

M8

PVDD

N22

PVDD

T22

PVDD

Y22

PVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

H13

IVDD

H16

IVDD

J10

IVDD

J13

IVDD

J16

IVDD

J17

IVDD

J19

IVDD

J20

IVDD

K21

IVDD

L21

IVDD

L9

IVDD

IVDD

N21

IVDD

N9

IVDD

T21

IVDD

U9

IVDD

H9

AUX3.3V

J8

AUX1.8V

CHIPSET5

630S-5

630S-5

POWER

VDDQ

H19

H20

GTLVTT

H21

H22

GTLVTT

GTLVTT

J21

J22

GTLVTT

GTLVTT

VTT

K22

L22

GTLVTT

GTLVTT

M22

GTLVTT

GTLVTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

L13

L14

L15

L16

L17

M12

M13

M14

M15

M16

M17

M18

N11

N12

N13

N14

N15

N16

N17

N18

N19

P14

P15

P18

P19

R14

R15

T14

T15

U14

U15

V14

V15

W13

W14

W15

P16

P17

R16

R17

R18

R19

T16

T17

T18

T19

U16

U17

U18

U19

V16

V17

V18

W16

W17

P11

P12

P13

R11

R12

R13

T11

T12

T13

U11

U12

U13

V12

V13

VCC3

R159

R167

R204

R411

R412

R592

C135

1UF-0805

C161

1UF-0805

C117

0.1UF

C169

0.1UF

4.7KR

4.7K

4.7K

4.7KR

4.7K

4.7K

D D

MD63: AGP DLL Enable

MD62: PCI PLL Enable

C C

B B

MD61: SDRAM DLL Enable

MD60: CPU DLL Enable

MD[59..58]: PLL ER[1..0]

MD[57..56]: DLL ER[1..0]

MD[55..53]: Clock skew control of AGP

MD37: Enable External CLKGEN

MD36: Enable Ext-PLink

MD35: Multi-function Select

MD34: Enable Multi-function

MD33: Enable Video Bridge

MD32: PAL/NTSC Select

MD31: Quick Start Function

1: Enable

0: Disable

MDD[0..63]11

(Default 00)

(Default 00)

inner-outer loop

(Default 001)

MDD[0..63]

C156

1UF-0805

C116

1UF-0805

C134

0.1UF

C149

0.1UF

(Default: Enable)

(Default: Enable)

(Default: Enable)

MDD37

MDD36

MDD31

MDD38

MDD39

MDD33

10UF/10V-A

A A

8

7

6

+

5

0.1UF

0.01UF

ALPHA-TOP CORP.

Title

SIS630S POWER

Size Document Number Rev

G510-1-4-01 2.0

4

3

Date: Sheet

2

10 29Friday, November 09, 2001

of

1

C124

C450

CE7

Page 11

8

www.kythuatvitinh.com

RP3 10X4

MDD31

1 8

MDD63

2 7

MDD29

3 6

MDD21

4 5

RP5 10X4

MDD26

1 8

MDD17

2 7

MDD48

3 6

MDD28

4 5

RP7 10X4

MDD54

MDD19

MDD51

MDD16

MDD58

MDD56

MDD24

MDD22

MDD30

MDD62

MDD61

MDD60

MDD27

MDD25

MDD57

MDD23

MDD55

MDD53

MDD20

MDD52

MDD18

MDD50

MDD49

MDD13

MDD9

MDD15

MDD47

MDD1

MDD45

MDD3

MDD43

MDD10

MDD8

MDD6

MDD38

MDD35

MDD36

MDD0

MDD33

MDD14

MDD46

MDD12

MDD44

MDD11

MDD42

MDD41

MDD40

MDD7

MDD39

MDD5

MDD37

VCC3

12

+

VCC3

1 8

2 7

3 6

4 5

RP6 10X4

1 8

2 7

3 6

4 5

RP37 10X4

RP39 10X4

RP41 10X4

RP42 10X4

RP12 10X4

1 8

2 7

3 6

4 5

RP13 10X4

1 8

2 7

3 6

4 5

RP14 10X4

1 8

2 7

3 6

4 5

RP15 10X4

1 8

2 7

3 6

4 5

RP46

RP47 10X4

10X4

RP48 10X4

C227

47UF/6.3V-B

C229

0.01UF

C231

0.01UF

8

D D

C C

B B

A A

FOR DIMM1

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

C232

0.01UF

FOR DIMM1

MD31

MD63

MD29

MD21

MD26

MD17

MD48

MD28

MD54

MD19

MD51

MD16

MD58

MD56

MD24

MD22

MD30

MD62

MD61

MD60

MD27

MD59

MD25

MD57

MD23

MD55

MD53

MD20

MD52

MD18

MD50

MD49

MD13

MD9

MD15

MD47

MD1

MD45

MD3

MD43

MD10

MD8

MD6

MD38

MD35

MD36

MD0

MD33

MD14

MD46

MD12

MD44

MD11

MD42

MD41

MD40

MD7

MD39

MD5

MD37

C230

0.01UF

DQMM2

DQMM6

DQMM7

DQMM3

DQMM0

DQMM4

DQMM5

DQMM1

CSAA-0

CSAA-2

CSAA-3

C193

0.01UF

MDD4

MDD2

MDD34

MDD32

C238

0.01UF

7

RP49 10X4

RP9 10X4

1 8

2 7

3 6

4 5

RP10 10X4

1 8

2 7

3 6

4 5

RP11 10X4

1 8

2 7

3 6

4 5

C239

0.01UF

C245

0.01UF

7

MD4

18

MD2

27

MD34

36

MD32

45

DQM2

DQM6

DQM7

DQM3

DQM0

DQM4

DQM5

DQM1

CSA-0

CSA-2

CSA-3

SDCLK2

SDCLK3

C711

CAP

For EMI test

C240

0.01UF

6

MA[0..14]6

DQM[0..7]6

SRAS-6

RAMW-6

SCAS-6

CKE219 SMBD5,9

CKE319

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

DQMM0

DQMM1

DQMM2 MDD11

DQMM3

DQMM4

DQMM5

DQMM6

DQMM7

CSAA-2

CSAA-3

RAMWSRAS-

SCASCKE2

CKE3

SMBC

SMBD

C712

CAP

VCC3

29

31

33

30

32

34

103

104

105

109

111

106

23

25

115

117

24

26

116

118

69

71

67

65

66

62

68

61

74

142

141

11

12

27

28

45

46

63

64

81

82

101

102

113

114

129

130

143

144

1

2

22

35

36

55

56

75

76

91

92

107

108

119

120

21

139

140

MA[0..14]

DQM[0..7]

SRASRAMWSCASCKE2

CKE3

U36

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

CAS#0

CAS#1

CAS#2

CAS#3

CAS#4

CAS#5

CAS#6

CAS#7

RAS#0/S#0

RAS#1/SI#1

WE#

SRAS#

SCAS#

CKE

CKEB

CK0

CK1

SCL

SDA

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

DIMM 144P(ECC)

AMP C-353871

5

NC/A12

NC/A13

MECC0

MECC4

MECC1

MECC5

MECC2

MECC6

MECC3

MECC7

NC/A12

NC/A13

OE#

MD[0..63]6

CSA-[0..3]6

SDCLK25

SDCLK35

SMBC5,9

MDD[0..63]10

3

D0

5

D1

7

D2

9

D3

13

D4

15

D5

17

D6

19

D7

37

D8

39

D9

41

D10

43

D11

47

D12

49

D13

51

D14

53

D15

83

D16

85

D17

87

D18

89

D19

93

D20

95

D21

97

D22

99

D23

121

D24

123

D25

125

D26

127

D27

131

D28

133

D29

135

D30

137

D31

4

D32

6

D33

8

D34

10

D35

14

D36

16

D37

18

D38

20

D39

38

D40

40

D41

42

D42

44

D43

48

D44

50

D45

52

D46

54

D47

84

D48

86

D49

88

D50

90

D51

94

D52

96

D53

98

D54

100

D55

122

D56

124

D57

126

D58

128

D59

132

D60

134

D61

136

D62

138

D63

70

72

57

58

59

60

77

78

79

80

110

112

73

MD[0..63]

CSA-[0..3]

SDCLK2

SDCLK3

SMBC

SMBD

MDD[0..63]

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD6

MDD7

MDD8

MDD9

MDD10

MDD11

MDD12

MDD13

MDD14

MDD15

MDD16

MDD17

MDD18

MDD19

MDD20

MDD21

MDD22

MDD23

MDD24MDD59

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

MDD31

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

MDD48

MDD49

MDD50

MDD51

MDD52

MDD53

MDD54

MDD56 MA13

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63

SDCLK05

For EMI test

MA14

MA12

SDCLK15

MA12

MA13

VCC3

4

CKE019

C710

CAP

C713

CAP

DIMM1

C226

0.01UF

C206

C242

0.01UF

6

C241

0.01UF

5

0.1UF

MA14

C219

0.1UF

Every 3 capacitors put every sdram cell

R179 0

1 2

4

VCC3

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD6

MDD7

MDD8

MDD9

MDD10

MDD12

MDD13

MDD14

MDD15

DQMM0

DQMM1

RAMWSCASSRASCSAA-0

SDCLK0

CKE0

VCC3

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

DQMM4

DQMM5

RAMWSCASSRASCSAA-0

SDCLK1

CKE0

MAA14

For EMI test

C201

0.1UF

MAA14

3

U34

1

VDD

14

VDD

27

VDD

3

VDDQ

9

VDDQ

43

VDDQ

49

VDDQ

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

42

DQ8

44

DQ9

45

DQ10

47

DQ11

48

DQ12

50

DQ13

51

DQ14

53

DQ15

15

LDQM

39

UDQM

16

WE

17

CAS

18

RAS

19

CS

38

CLK

37

CKE

36

NC

SDRAM

U35

1

VDD

14

VDD

27

VDD

3

VDDQ

9

VDDQ

43

VDDQ

49

VDDQ

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

42

DQ8

44

DQ9

45

DQ10

47

DQ11

48

DQ12

50

DQ13

51

DQ14

53

DQ15

15

LDQM

39

UDQM

16

WE

17

CAS

18

RAS

19

CS

38

CLK

37

CKE

36

NC

SDRAM

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

A10(AP)

A12(BA1)

A13(BA0)

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

A10(AP)

A12(BA1)

A13(BA0)

28

41

54

6

12

46

52

MA0

23

A0

MA1

24

A1

MA2

25

A2

MA3

26

A3

MA4

29

A4

MA5

30

A5

MA6

31

A6

MA7

32

A7

MA8

33

A8

MA9

34

A9

MA10

22

MA13

35

A11

MA12

21

MA11

20

28

41

54

6

12

46

52

MA0

23

A0

MA1

24

A1

MA2

25

A2

MA3

26

A3

MA4

29

A4

MA5

30

A5

MA6

31

A6

MA7

32

A7

MA8

33

A8

MA9

34

A9

MA10

22

35

A11

MA12

21

MA11

20

VCC3

VCC3

2

MDD16

MDD17

MDD18

MDD19

MDD20

MDD21

MDD22

MDD23

MDD24

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

MDD31

DQMM2

DQMM3

RAMWSCASSRASCSAA-0MAA14

SDCLK0

CKE0

MAA14

MDD48

MDD49

MDD50

MDD51

MDD52

MDD53

MDD54

MDD55

MDD56

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63

DQMM6

DQMM7

RAMWSCASSRASCSAA-0

SDCLK1

CKE0

MAA14

1

U33

1

VDD

14

VDD

27

VDD

3

VDDQ

9

VDDQ

43

VDDQ

49

VDDQ

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

42

DQ8

44

DQ9

45

DQ10

47

DQ11

48

DQ12

50

DQ13

51

DQ14

53

DQ15

15

LDQM

39

UDQM

16

WE

17

CAS

18

RAS

19

CS

38

CLK

37

CKE

36

NC

SDRAM

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

A10(AP)

A12(BA1)

A13(BA0)

28

41

54

6

12

46

52

MA0

23

A0

MA1

24

A1

MA2

25

A2

MA3

26

A3

MA4

29

A4

MA5

30

A5

MA6

31

A6

MA7

32

A7

MA8

33

A8

MA9

34

A9

MA10

22

MA13

35

A11

MA12

21

MA11

20

SDCLK0

For EMI test

U32

1

VDD

14

VDD

27

VDD

3

VDDQ

9

VDDQ

43

VDDQ

49

VDDQ

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

42

DQ8

44

DQ9

45

DQ10

47

DQ11

48

DQ12

50

DQ13

51

DQ14

53

DQ15

15

LDQM

39

UDQM

16

WE

17

CAS

18

RAS

19

CS

38

CLK

37

CKE

36

NC

SDRAM

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

A10(AP)

A12(BA1)

A13(BA0)

28

41

54

6

12

46

52

MA0

23

A0

MA1

24

A1

MA2

25

A2

MA3MDD55

26

A3

MA4

29

A4

MA5

30

A5

MA6

31

A6

MA7

32

A7

MA8

33

A8

MA9

34

A9

MA10

22

MA13

35

A11

MA12

21

MA11

20

SDCLK1

For EMI test

C220

0.1UF

C192

0.1UF

3

C202

0.1UF

C207

0.1UF

ALPHA-TOP CORP.

Title

Size Document Number Rev

Date: Sheet

C194

0.1UF

SODIMM & ON BOARD SDRAM

G510-1-4-01 2.0

2

11 29Friday, November 09, 2001

of

1

C716

CAP

C717

CAP

Page 12

8

www.kythuatvitinh.com

D D

ROUT8

GOUT8

BOUT8

C C

VCC3

6 1

D3A

IMN10

DDC1DATA8,22

DDC1CLK8,22

HSYN8

VSYN8

R430 15K

R431 15K

RP32 15KX4

1 8

2 7

3 6

4 5

Pull Low When no use

52

D3B

IMN10

Change Component

7

VCC3 VCC3

4 3

D3C

IMN10

UV3- 9

UV3+ 9

UV4- 9

UV5- 9

UV4+ 9

UV5+ 9

61

D4A

IMN10

D4B

IMN10

5 2

C720

1UF/16V-A

D4C

IMN10

6

VCC3

43

D2A

IMN10R

UV0-9

UV0+9

MP5V

12

+

VCC3

52

6 1

D2B

IMN10R

D2C

IMN10R

3

4

2

RTL9701-CBL

U46

VIN

VIN

GND

4 3

C452

100PF

R251

75 1%

VOUT

VOUT

61

D30A

IMN10

5

1

R252

75 1%

R346 33

R352 33

C448

22PF

OUTA

OUTB

5

R253

75 1%

C289

22PFR

C290

22PFR

CLOSE TO SIS630S

L21 FCM2012V-121RC10-0805

FCM2012V-121RC10-0805

L22

FCM2012V-121RC10-0805

L23

1 2

1 2

1 2

R227

100

R230

100

33

33

R347

15K

R353

15K

R228

R229

C291

22PFR

22PF

4

R1

2.2K

C276

C4

22PF

C2

22PF

C1

22PF

1 2

L37 FCM1608K-680

1 2

L38 FCM1608K-680

1 2

12

C22

+

C26

100UF/10V-D

0.1UF

CLOSE TO CONN

VCC3

C6

22PF

L10

D39

ASD500V

R3

2.2K

22PF

C3

BLM21P300S

C24

47PF

C5

22PF

C23

47PF

USBGND0

3

DDC2BD

DDC2BC

HSYNC

VSYNC

CON1

1

2

3

4

5

6

7

8

SUYIN 7535S-15G2T

JP1

1

1

2

2

3

3

4

4

C25

0.1UF

L39 FCM1608K-680

HEADER 4_1

1 2

2

VCC5

12

L24

FCM2012V-121RC10-0805R

9

10

11

DDC2BD

12

HSYNC

13

VSYNC

14

DDC2BC

15

C7

0.1UFR

1

1

JH1

REED

USBGND0

1