Page 1

8

www.kythuatvitinh.com

Digitally signed by fdsf

DN: cn=fdsf, o=fsdfsd,

ou=ffsdf,

email=fdfsd@fsdff,

c=US

Date: 2010.01.06

7

6

5

4

3

2

1

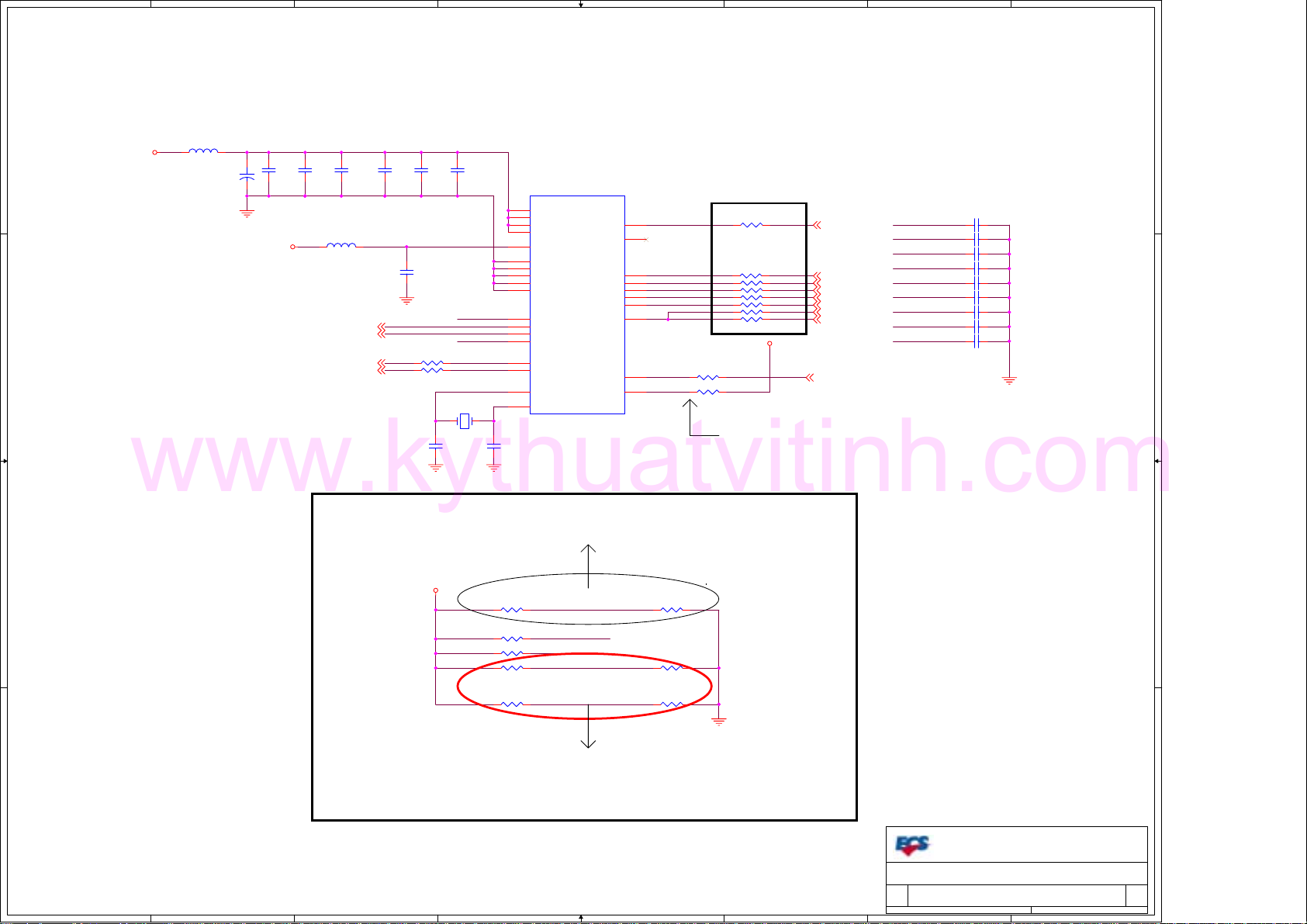

A531 SCHEMATICS

D D

01.THIS PAGE

02.TM5800 DDR Interface

03.TM5800 PCI Interface

04.TM5800 SIDEBAND

05.TM5800 POWER&GND

06.CKE SW& TDM DEBUG PORT

07.DDR DIMM MOUDLE

08.PARALLEL&SERIAL ROM&DEBUG PORT

09.CLOCK GENERATOR

10.M1535+(PCI+IDE)

30.LPC ROM&LED&PWRGD

31.POWER-SW&PLLVDD&VCPU33/25

32.AUDIO CODEC

33.OPA & AUDIO JACK

34.CHARGER AND SELECTOR

35.DC-DC MAX1817

36.VCORE FAN5250

37.BAT. LOW & OVER T.& LDO PWR

38.DDR POWER

39.HISTORY

11.M1535+ MISC.

C C

12.M1535+(AUDIO/IO)

13.M1535+(POWER+GPIO)

14.HDD & CDROM CONN.

15.M1535+(AUDIO/IO/KB/IR)

16.SIS315E-1

17.SIS315E-2

18.SIS315E-3

19.VIDEO MEMORY

20.LCD POWER & BL CONTROL

21.LVDS TRANSMITTER

B B

22.CRT Connector

23.ALI M5273

24.USB PORT

25.KBC & T/P

26.AUDIO OP AMPLIFIER

27.RJ45

PCB NO. :

REV. :

15-F22-011001

V1.0

28.MINIPCI

29.RTC

VER

DATE

A A

VER

DATE

28 15

8/28

8/28 8/28 8/28 8/28 8/28 8/28 8/28 8/28 8/28 8/28 8/28

21PAGE 26 292823 2422 25

8/28 8/28 8/28 8/28 8/28 8/28 8/28 8/28 8/28

27

9 16510 173 11 184 19126

30 32

1.01.01.01.01.01.01.01.01.0

1.0 1.0 1.0

8/28 8/28318/28

1.01.01.01.01.01.01.01.01.01.01.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0

8

7

6

13 20PAGE 1 7 14

8/28 8/28 8/28 8/28 8/28 8/28 8/28 8/28

33 35

1.0 1.0 1.0

8/28 8/28348/28

5

36

37 38 39

1.0 1.0 1.0

8/28 8/28 8/28

4

P.leader

Check by Design byAppr.by

Elitegroup Computer Systems

Title

Size Document Number Re v

B

3

Date: Sheet

THIS PAGE

A531-1-4-01

2

V1.0

of

139Thursday, Augus t 28, 2003

1

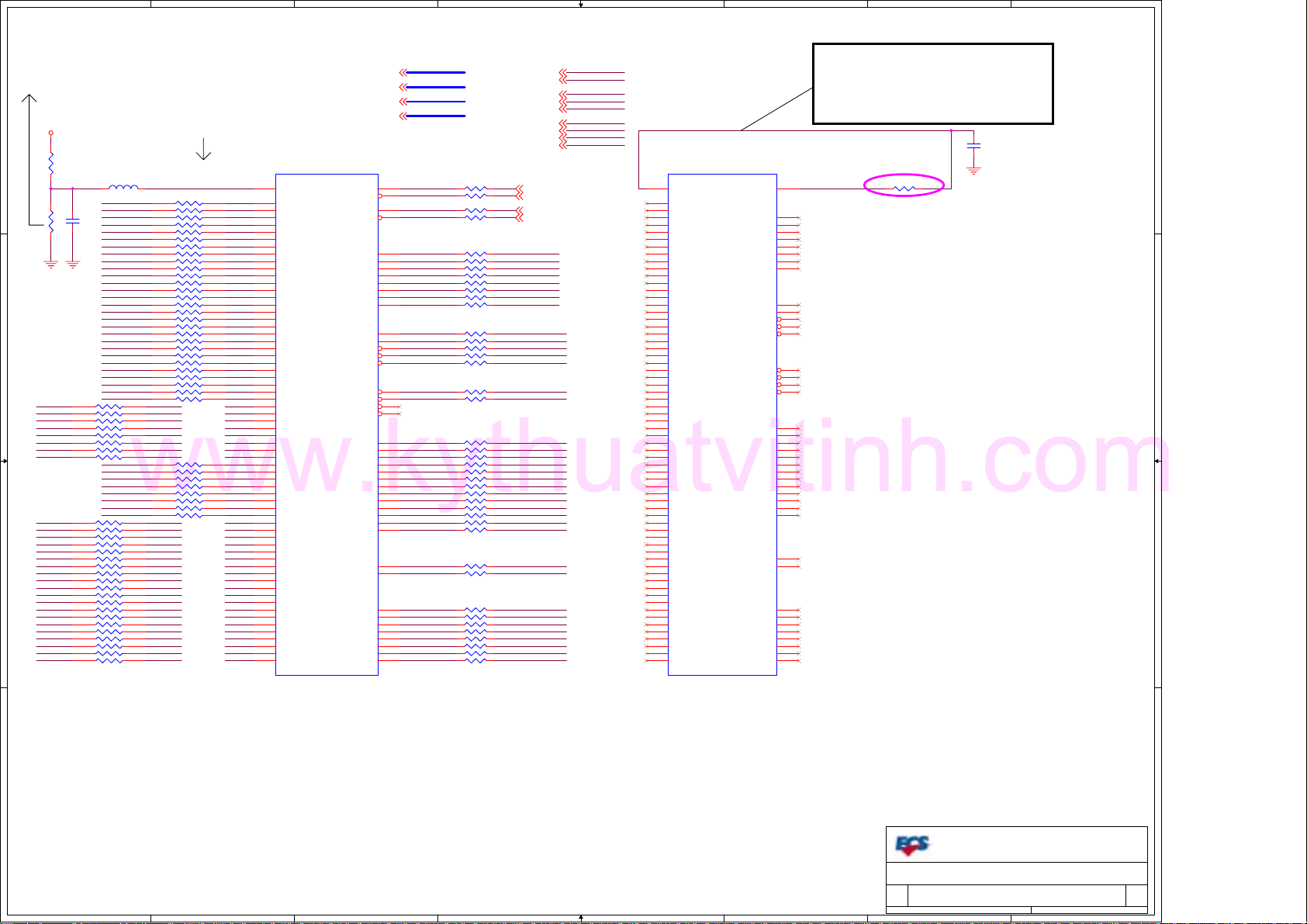

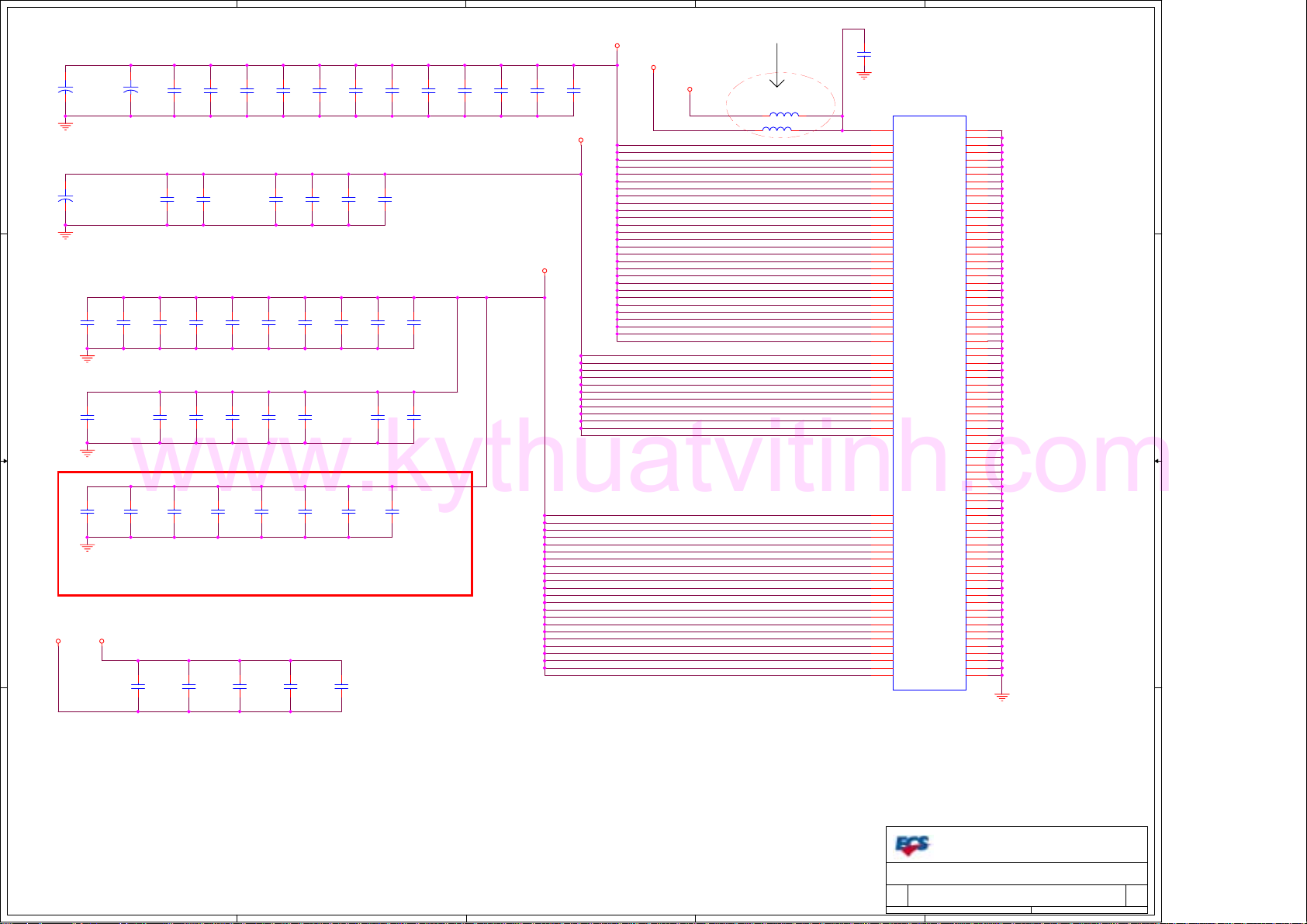

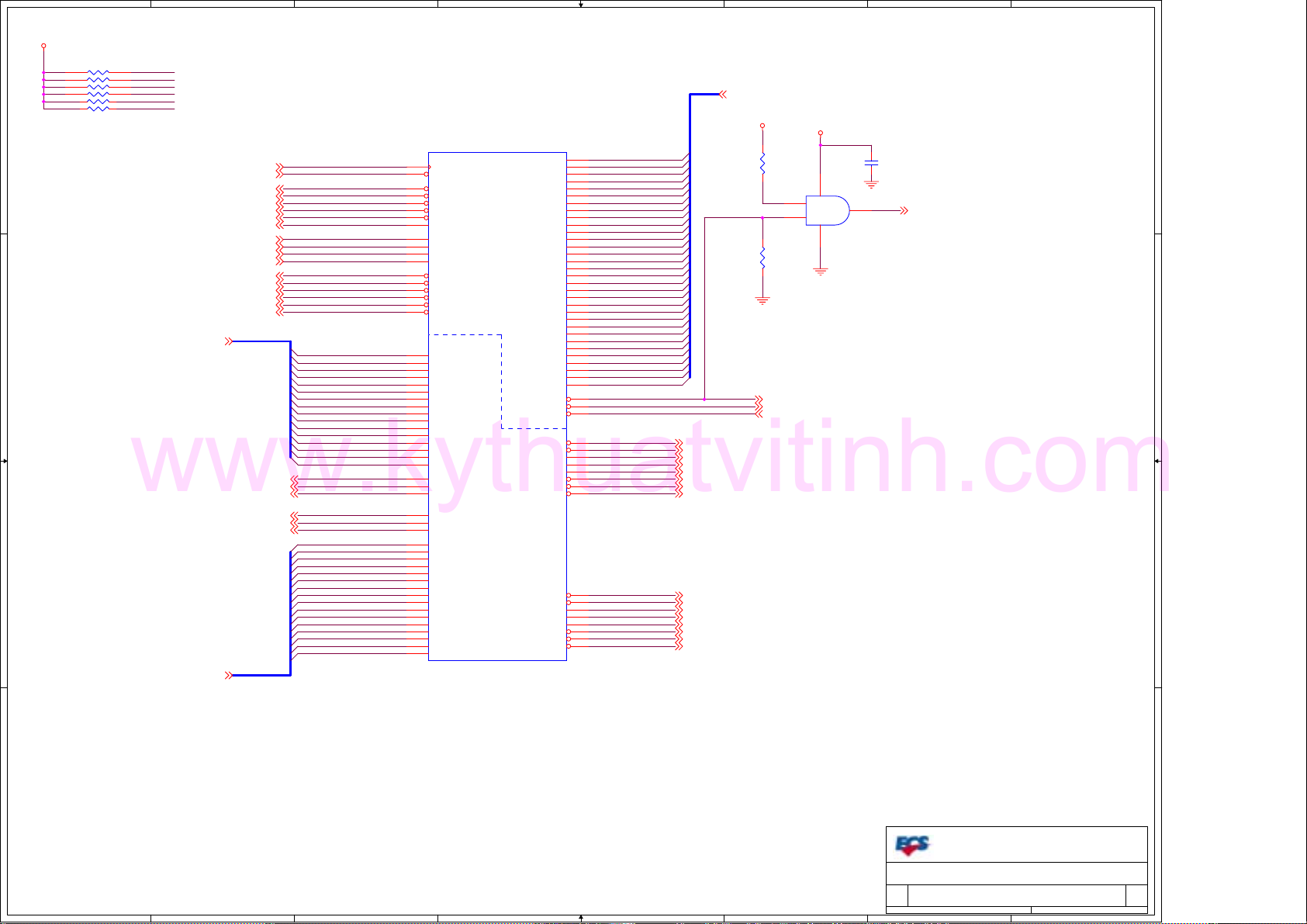

Page 2

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

2.80k_1% FOR C_VREF SPEC=1.4V +/- 7% FOR TM5800 VER /1.X ( UNDER 933MHz )

FOR TM5800 VER 2.X ( ABOVE 1GHz )2.15K_1% FOR C_VREF SPEC=1.2V +/- 1.25%

DDR_A[12..0]7

DDR_DQM[7..0]7

D D

VCPU25

C_VREF

2.15K 1%

R81

C C

DDR_DQ29 C_DQ29

DDR_DQ28

DDR_DQ31

DDR_DQ30

DDR_DQ32 C_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ46 C_DQ46

DDR_DQ44

DDR_DQ45

DDR_DQ47

DDR_DQ48 C_DQ48

DDR_DQ51

DDR_DQ49

DDR_DQ53

B B

DDR_DQ50 C_DQ50

DDR_DQ54

DDR_DQ52

DDR_DQ55

DDR_DQ56 C_DQ56

DDR_DQ59

DDR_DQ58

DDR_DQ61

DDR_DQ57 C_DQ57

DDR_DQ60

DDR_DQ63

DDR_DQ62

PART NUMBER-->16-100-101160

R91

2.15K 1%

L20

FB.100 OHM.SMD

DDR_DQ0

RP24

33X4

RP25

33X4

RP22

33X4

RP20

33X4

RP18

33X4

RP12

33X4

RP9

33X4

C_DQ28

C_DQ31

C_DQ30

C_DQ33

C_DQ34

C_DQ35

SRP5

33X4

SRP8

33X4

C_DQ44

C_DQ45

C_DQ47

C_DQ51

C_DQ49

C_DQ53

C_DQ54

C_DQ52

C_DQ55

C_DQ59

C_DQ58

C_DQ61

C_DQ60

C_DQ63

C_DQ62

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

DDR_DQ1

DDR_DQ2

DDR_DQ3

C95

0.1UF

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

RP8

1 8

33X4

2 7

3 6

4 5

SRP4

1 8

33X4

2 7

3 6

4 5

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

SRP12

1 8

33X4

2 7

3 6

4 5

SRP13

1 8

33X4

2 7

3 6

4 5

SRP14

1 8

33X4

2 7

3 6

4 5

SRP16

1 8

33X4

2 7

3 6

4 5

SRP17

1 8

33X4

2 7

3 6

4 5

C_DQ0

C_DQ1

C_DQ2

C_DQ3

C_DQ4

C_DQ5

C_DQ6

C_DQ7

C_DQ8

C_DQ9

C_DQ10

C_DQ11

C_DQ12

C_DQ13

C_DQ14

C_DQ15

C_DQ16

C_DQ17

C_DQ18

C_DQ19

C_DQ20

C_DQ21

C_DQ22

C_DQ23

C_DQ24

C_DQ25

C_DQ26

C_DQ27

C_DQ28

C_DQ29

C_DQ30

C_DQ31

C_DQ32

C_DQ33

C_DQ34

C_DQ35

C_DQ36

C_DQ37

C_DQ38

C_DQ39

C_DQ40

C_DQ41

C_DQ42

C_DQ43

C_DQ44

C_DQ45

C_DQ46

C_DQ47

C_DQ48

C_DQ49

C_DQ50

C_DQ51

C_DQ52

C_DQ53

C_DQ54

C_DQ55

C_DQ56

C_DQ57

C_DQ58

C_DQ59

C_DQ60

C_DQ61

C_DQ62

C_DQ63

AD12

AE13

AD13

AE14

AD14

AE15

AD15

AE16

AD19

AD18

AC19

AC18

AB19

AB18

AA19

AA18

W19

W18

W15

W16

AA15

AA17

AA16

AB16

AB14

AA13

AB13

AC13

AA12

AB12

AA11

AB11

K19

Y19

Y18

V19

V18

U19

U18

P19

P18

N19

N18

M19

M18

L19

L18

K16

M15

M16

M17

N15

N16

P15

P16

T16

T17

U15

U16

V15

V16

V17

Y15

Y16

Y17

U3A

Crusoe BGA474

(PART 1 OF 5)

C_VREF

C_DQ0

C_DQ1

C_DQ2

C_DQ3

C_DQ4

C_DQ5

C_DQ6

C_DQ7

C_DQ8

C_DQ9

C_DQ10

C_DQ11

C_DQ12

C_DQ13

C_DQ14

C_DQ15

C_DQ16

C_DQ17

C_DQ18

C_DQ19

C_DQ20

C_DQ21

C_DQ22

C_DQ23

C_DQ24

C_DQ25

C_DQ26

C_DQ27

C_DQ28

C_DQ29

C_DQ30

C_DQ31

C_DQ32

C_DQ33

C_DQ34

C_DQ35

C_DQ36

C_DQ37

C_DQ38

C_DQ39

C_DQ40

C_DQ41

C_DQ42

C_DQ43

C_DQ44

C_DQ45

C_DQ46

C_DQ47

C_DQ48

C_DQ49

C_DQ50

C_DQ51

C_DQ52

C_DQ53

C_DQ54

C_DQ55

C_DQ56

C_DQ57

C_DQ58

C_DQ59

C_DQ60

C_DQ61

C_DQ62

C_DQ63

FB 100 OHM

DDR_DQ[0..63]7

DDR_DQS[7..0]7

DDR

C_CLKA

C_CLKA#

C_CLKB

C_CLKB#

C_DQS0

C_DQS1

C_DQS2

C_DQS3

C_DQS4

C_DQS5

C_DQS6

C_DQS7

C_CKE0

C_CKE1

C_RAS#

C_CAS#

C_WE#

C_CS0#

C_CS1#

C_CS2#

C_CS3#

C_A0

C_A1

C_A2

C_A3

C_A4

C_A5

C_A6

C_A7

C_A8

C_A9

C_A10

C_A11

C_A12

C_BA0

C_BA1

C_DQMB0

C_DQMB1

C_DQMB2

C_DQMB3

C_DQMB4

C_DQMB5

C_DQMB6

C_DQMB7

CLKDDRA

AA10

CLKDDRA-

AC11

CLKDDRB

AA9

CLKDDRB-

AB10

AD16

AE18

T19

R18

P17

T15

AC16

AA14

DDRCKE_MUX0

AE6

DDRCKE_MUX1

Y7

DDRRAS-

AE11

DDRCAS-

AD11

DDRMWE-

AE12

DDRCS0-

AD10

DDRCS1-

Y8

Y9

Y11

AD8

AE8

AD7

AE7

AD6

AC7

AB7

AA7

AB8

AA8

AE9

AC9

AB9

AE10

AD9

AE17

AD17

T18

R19

R15

R16

AB15

AC15

DDR_A[12..0]

DDR_DQM[7..0]

DDR_DQ[0..63]

DDR_DQS[7..0]

DDRDQS1

DDRDQS2

DDRDQS3

DDRDQS4

DDRDQS5

DDRDQS6

DDRDQS7

DDRA0

DDRA1

DDRA2

DDRA3

DDRA4

DDRA5

DDRA6

DDRA7

DDRA8

DDRA9

DDRA10

DDRA11

DDRA12

DDRBA0

DDRBA1

DDRDQM0

DDRDQM1

DDRDQM2

DDRDQM3

DDRDQM4

DDRDQM5

DDRDQM6

DDRDQM7

SR129 0

SR130 0

SR128 0

SR127 0

R156 10

R140 10

SR92 10

R109 10

SR96 10

SR108 10

SR137 10

SR133 10

R164 10

R154 10

R152 10

R161 10

R153 10

R160 10

SR131 10

R148 10

R157 10

R165 10

R147 10

R163 10

R146 10

R145 10

R162 10

R166 10

R144 10

R150 10

R158 10

R149 10

R151 10

R159 10

R155 10

R141 10

SR97 10

R113 10

SR91 10

SR102 10

SR132 10

SR134 10

DDR_CS0-7

DDR_CS1-7

DDR_RAS-7

DDR_CAS-7

DDR_MWE-7

DDR_BA07

DDR_BA17

DDR_CKE_MUX06

DDR_CKE_MUX16

CLK_DDRA 7

CLK_DDRA- 7

CLK_DDRB 7

CLK_DDRB- 7

DDR_DQS0DDRDQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_CKE_MUX0

DDR_CKE_MUX1

DDR_RASDDR_CASDDR_MWE-

DDR_CS0DDR_CS1-

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_BA0

DDR_BA1

DDR_DQM0

DDR_DQM1

DDR_DQM2

DDR_DQM3

DDR_DQM4

DDR_DQM5

DDR_DQM6

DDR_DQM7

DDR_CS0DDR_CS1-

DDR_RASDDR_CASDDR_MWE-

DDR_BA0

DDR_BA1

DDR_CKE_MUX0

DDR_CKE_MUX1

U3B

Crusoe BGA474

(PART 2 OF 5)

AB6

W5

AB4

AB5

AA5

Y5

AC4

AD3

AD2

AC2

AC1

AD1

AA4

AA3

Y4

Y3

W4

G4

G6

G5

E6

F5

D5

E5

D6

F4

F3

E3

E4

D4

B5

C5

C4

AA6

AC5

AD5

AD4

AE3

AE5

AE4

AE2

AB2

AB1

AA2

AA1

Y2

Y1

W2

W1

F1

F2

E1

D1

E2

C1

D2

C2

A5

A3

B4

A2

A4

B3

B2

B1

S_CLKIN

S_DQ0

S_DQ1

S_DQ2

S_DQ3

S_DQ4

S_DQ5

S_DQ6

S_DQ7

S_DQ8

S_DQ9

S_DQ10

S_DQ11

S_DQ12

S_DQ13

S_DQ14

S_DQ15

S_DQ16

S_DQ17

S_DQ18

S_DQ19

S_DQ20

S_DQ21

S_DQ22

S_DQ23

S_DQ24

S_DQ25

S_DQ26

S_DQ27

S_DQ28

S_DQ29

S_DQ30

S_DQ31

S_DQ32

S_DQ33

S_DQ34

S_DQ35

S_DQ36

S_DQ37

S_DQ38

S_DQ39

S_DQ40

S_DQ41

S_DQ42

S_DQ43

S_DQ44

S_DQ45

S_DQ46

S_DQ47

S_DQ48

S_DQ49

S_DQ50

S_DQ51

S_DQ52

S_DQ53

S_DQ54

S_DQ55

S_DQ56

S_DQ57

S_DQ58

S_DQ59

S_DQ60

S_DQ61

S_DQ62

S_DQ63

SDR

S_CLKOUT

S_CLK0

S_CLK1

S_CLK2

S_CLK3

S_CLK4

S_CLK5

S_CLK6

S_CLK7

S_CKE0

S_CKE1

S_RAS#

S_CAS#

S_WE#

S_CS0#

S_CS1#

S_CS2#

S_CS3#

S_A0

S_A1

S_A2

S_A3

S_A4

S_A5

S_A6

S_A7

S_A8

S_A9

S_A10

S_A11

S_A12

S_BA0

S_BA1

S_DQMB0

S_DQMB1

S_DQMB2

S_DQMB3

S_DQMB4

S_DQMB5

S_DQMB6

S_DQMB7

NOTE:

REFER TO SYSTEM DESIGN

GUIDE FOR TRACE LENGTH

SDR_CLKIN

03/06

V6

M3

M4

M5

L4

L5

K3

K4

K5

J2

J1

R5

V4

P5

T4

T3

T1

T2

P3

N4

V5

P4

N5

M1

P1

N1

P2

N2

M2

K1

K2

L2

L1

U1

U4

H4

H3

U5

U2

H2

H1

SDR_CLKOUT

SR116 33

SC179

47PF_R

PLACE RES CLOSE TO SOURCE,

PROCESSOR BALL V6

A A

Elitegroup Computer Systems

Title

TM5800 SDR Interface

Size Document Number Re v

8

7

6

5

4

3

B

Date: Sheet

2

A531-1-4-01

239Thursday, Augus t 28, 2003

1

V1.0

of

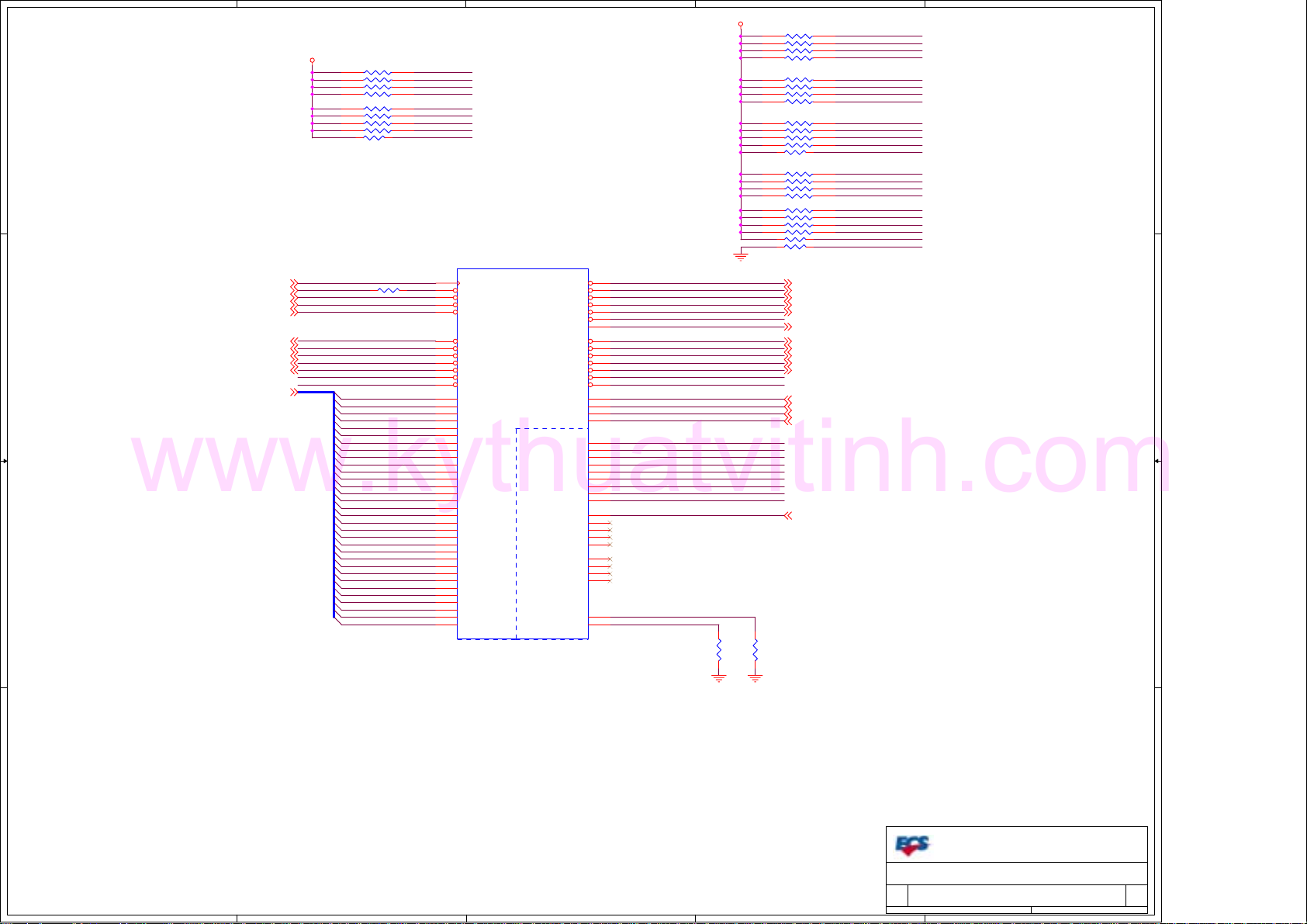

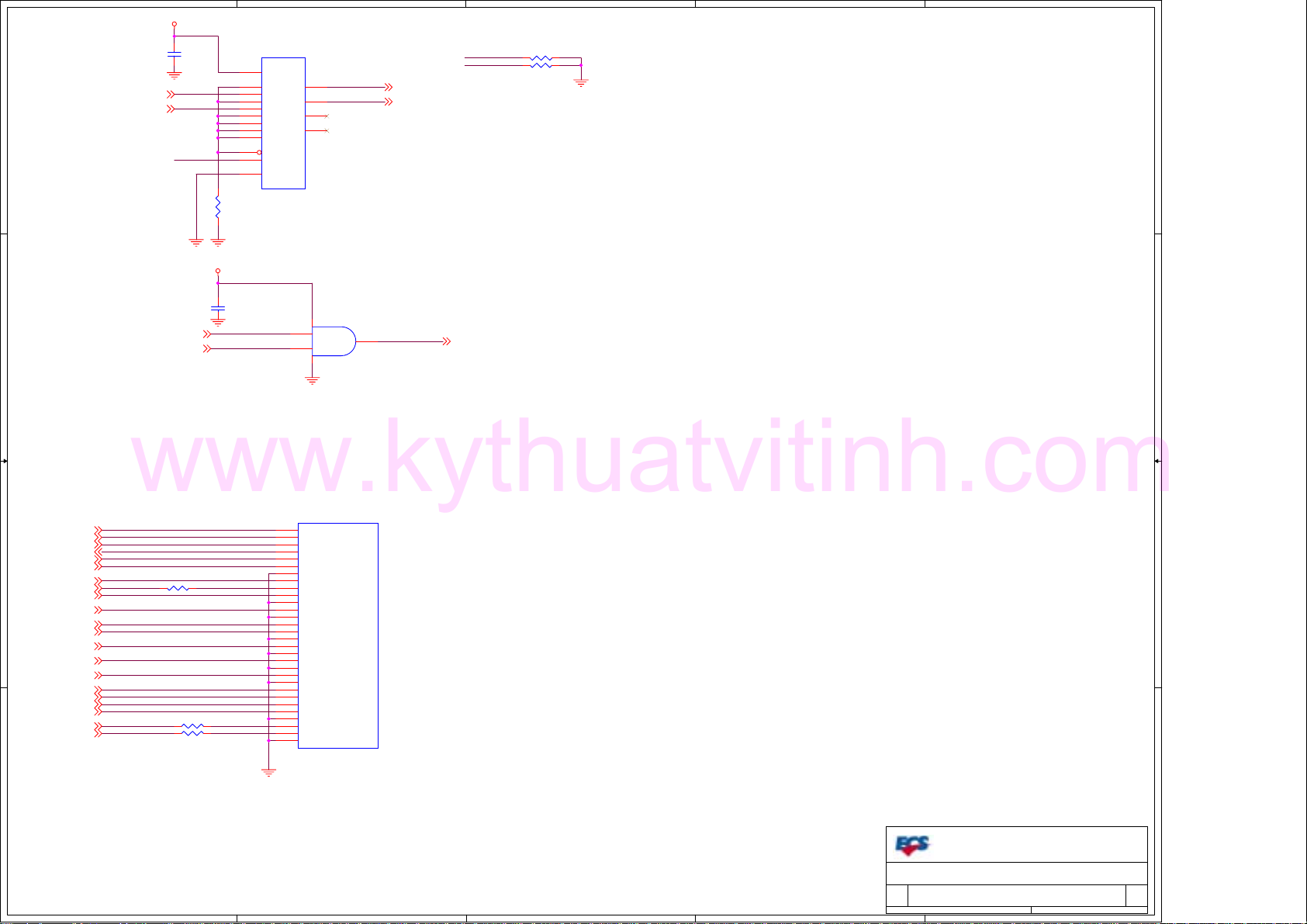

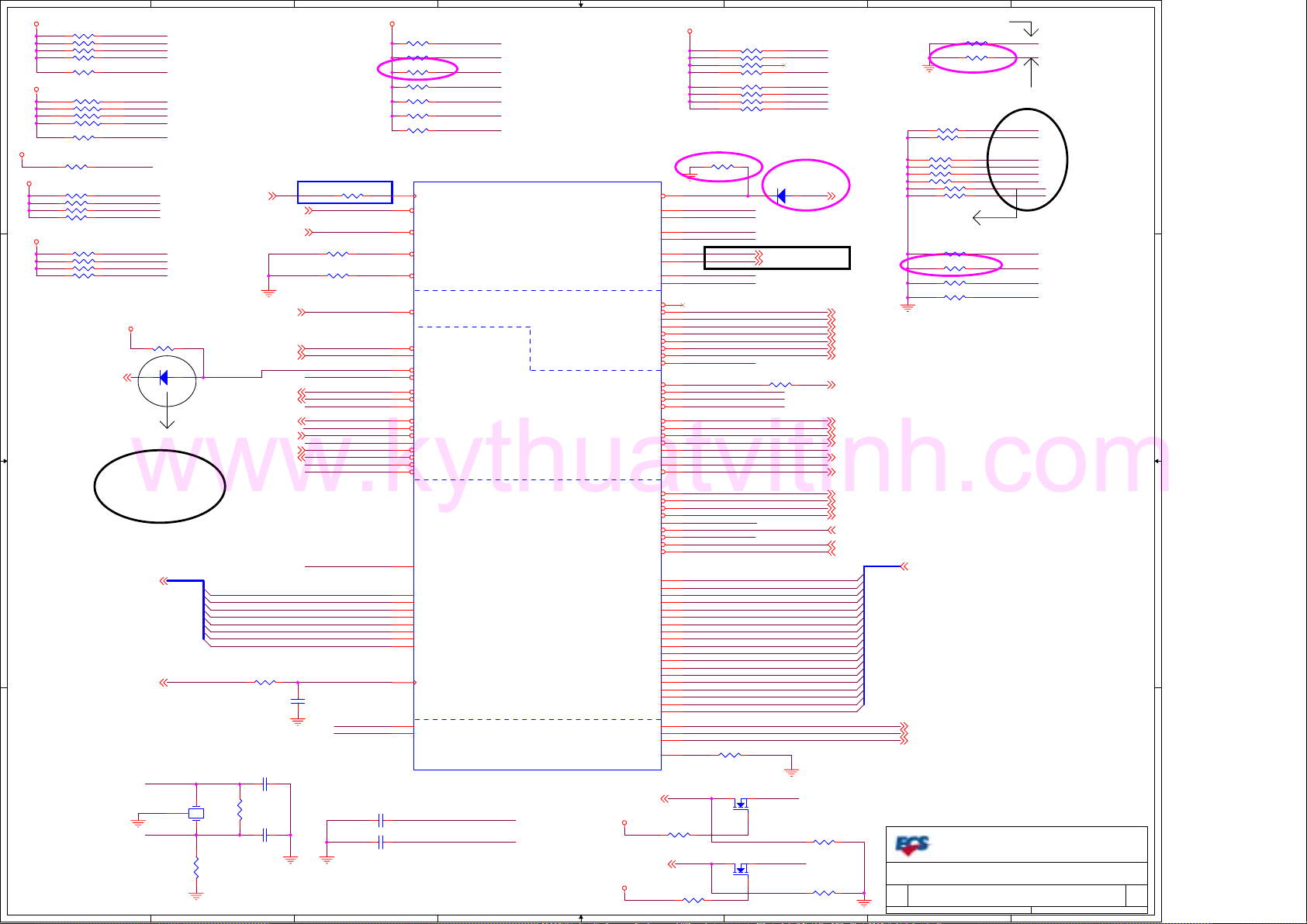

Page 3

5

www.kythuatvitinh.com

D D

PCICLKTM9

PCIRST-4,8,10,16,21,23,25,28,30

PCI_CLKRUN-11,23,28

PERR-23,26,28

SERR-10,23,26,28

PCI_HLD-10

C C

B B

PREQ-016,30

PREQ-126,30

PREQ-228,30

PREQ-323,30

AD[0..31]10,16,23,26,28

VCPU33

PREQ-0

PREQ-1

PREQ-2

PREQ-3

PREQ-4

PREQ-5

4

SRP2 10KX4

1 8

2 7

3 6

4 5

RP7 10KX4

1 8

2 7

3 6

4 5

R72 10K

R73 10K

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PERR-

PCI_HLDSERRPREQ-1

PREQ-4

PREQ-2

PREQ-3

PREQ-0

PREQ-5

F8

E8

J18

F12

D13

C19

D19

D18

E19

E18

F19

F18

B19

C18

B18

B17

D16

E16

E17

C16

F16

E15

D15

F15

C15

E14

D14

B15

E12

F11

E11

D11

D12

C11

E10

D10

F9

E9

D9

B8

C9

B9

A9

A10

(PART 3 OF 5)

P_PCLK

P_PCI_RST#

P_CLKRUN#

P_PERR#

P_SERR#

P_HOLD#

P_REQ0#

P_REQ1#

P_REQ2#

P_REQ3#

P_REQ4#

P_REQ5#

P_AD0

P_AD1

P_AD2

P_AD3

P_AD4

P_AD5

P_AD6

P_AD7

P_AD8

P_AD9

P_AD10

P_AD11

P_AD12

P_AD13

P_AD14

P_AD15

P_AD16

P_AD17

P_AD18

P_AD19

P_AD20

P_AD21

P_AD22

P_AD23

P_AD24

P_AD25

P_AD26

P_AD27

P_AD28

P_AD29

P_AD30

P_AD31

U3C

Crusoe BGA474

PCI

RESERVED

P_FRAME#

P_IRDY#

P_TRDY#

P_STOP#

P_DEVSEL#

P_LOCK#

P_PAR

P_HLDA#

P_GNT0#

P_GNT1#

P_GNT2#

P_GNT3#

P_GNT4#

P_GNT5#

P_C/BE0#

P_C/BE1#

P_C/BE2#

P_C/BE3#

RSVD_G2

RSVD_F7

RSVD_V2

RSVD_W6

RSVD_H5

RSVD_G1

RSVD_V1

RSVD_V3

RSVD_H6

RSVD_AE19

RSVD_R2

RSVD_R4

RSVD_R1

RSVD_G11

RSVD_D7

RSVD_J4

RSVD_J5

RSVD_T5

RSVD_G13

RSVD_E7

3

A13

B12

B13

C13

A17

A14

B14

E13

G15

A16

F13

A15

G16

F17

A12

B11

A11

B10

G2

F7

V2

W6

H5

G1

V1

V3

H6

AE19

R2

R4

R1

G11

D7

J4

J5

T5

RSVD_G13_PD

G13

RSVD_E7_PD

E7

VCPU33

UNPROTECT

RSVD_F7_PU

RSVD_V2_PU

RSVD_W6_PU

RSVD_H5_PU

RSVD_G1_PU

RSVD_V1_PU

RSVD_V3_PU

RSVD_H6_PU

SR51

4.7K

RP11 10KX4

RP10 10KX4

RP6 10KX4

R53 10K

SRP3 10KX4

RP5 10KX4

R71 10K_R

R103 10K

FRAMEIRDYTRDYSTOPDEVSELPLOCKPAR

PCI_HLDA-

PGNT-0

PGNT-1

PGNT-2

PGNT-3

PGNT-4

PGNT-5

2

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

FRAME- 10,16,23,26,28

IRDY- 10,16, 23,26,28

TRDY- 10,16,23,26,28

STOP- 10,16,23,26,28

DEVSEL- 10,16,23 ,26,28

PAR 10 ,16,23,26,28

PCI_HLDA- 10

PGNT-0 16

PGNT-1 26

PGNT-2 28

PGNT-3 23

C/BE-0 10,16,23,26,28

C/BE-1 10,16,23,26,28

C/BE-2 10,16,23,26,28

C/BE-3 10,16,23,26,28

SNIFF_VCORE 36

SR58

4.7K

RSVD_V1_PU

RSVD_V2_PU

RSVD_V3_PU

RSVD_W6_PU

RSVD_F7_PU

RSVD_G1_PU

RSVD_H5_PU

RSVD_H6_PU

STOPFRAMETRDYIRDYPLOCK-

PCI_HLDAPGNT-2

PGNT-0

PGNT-4

DEVSELPGNT-1

PGNT-3

PAR

PGNT-5

UNPROTECT

1

A A

Elitegroup Computer Systems

Title

TM5800 PCI Interface

Size Document Number Re v

5

4

3

2

B

Date: Sheet

A531-1-4-01

339Thursday, Augus t 28, 2003

1

V1.0

of

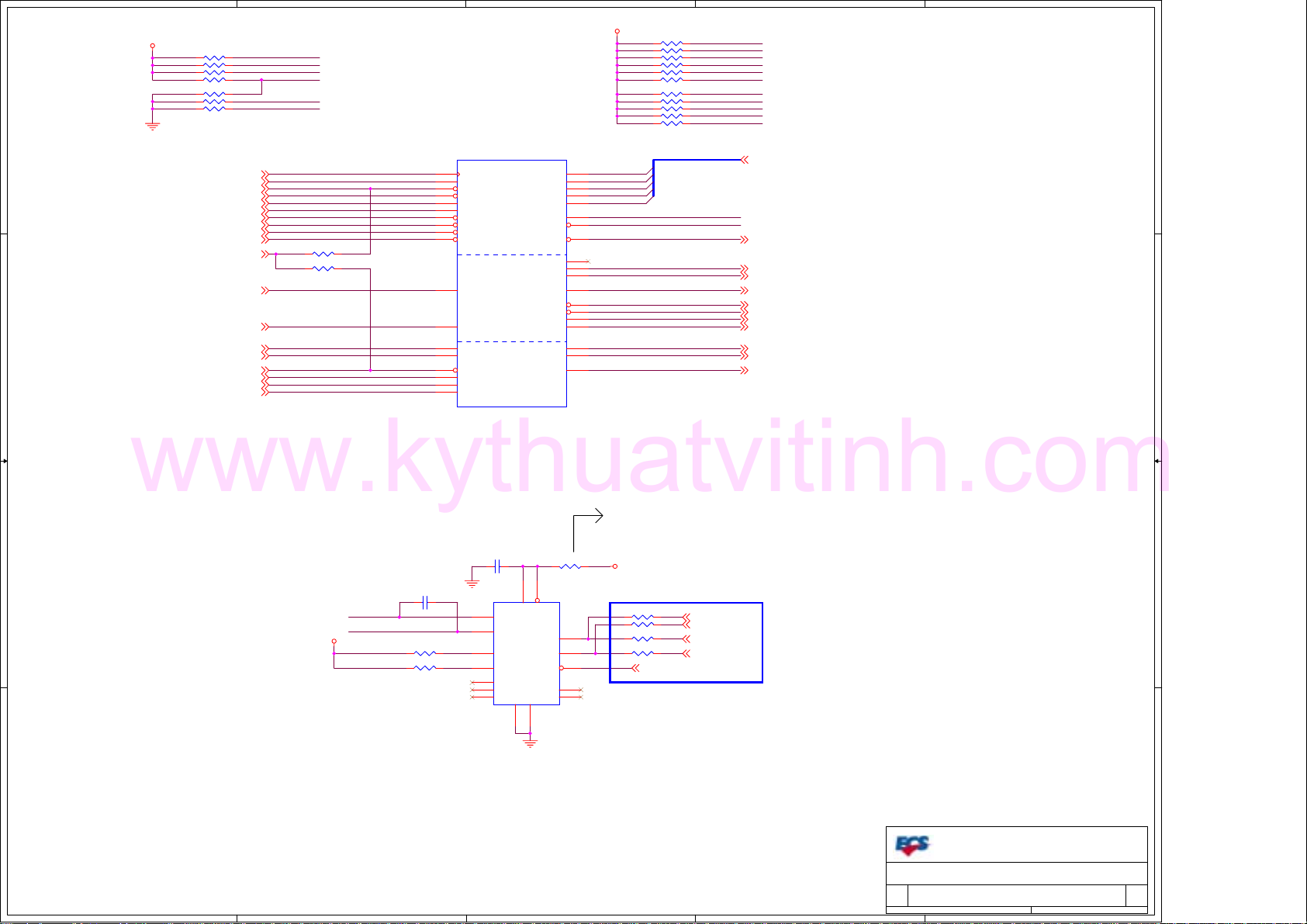

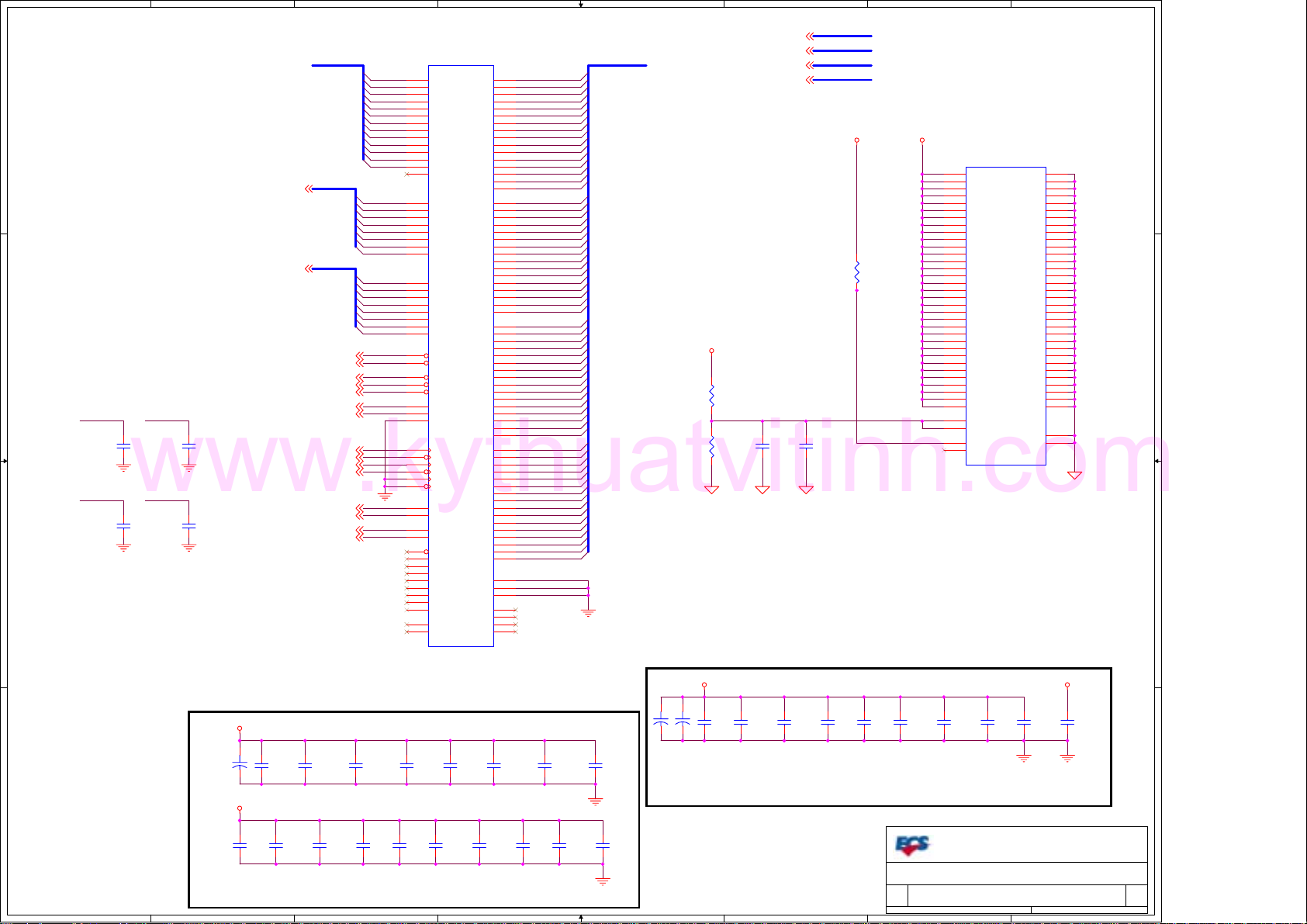

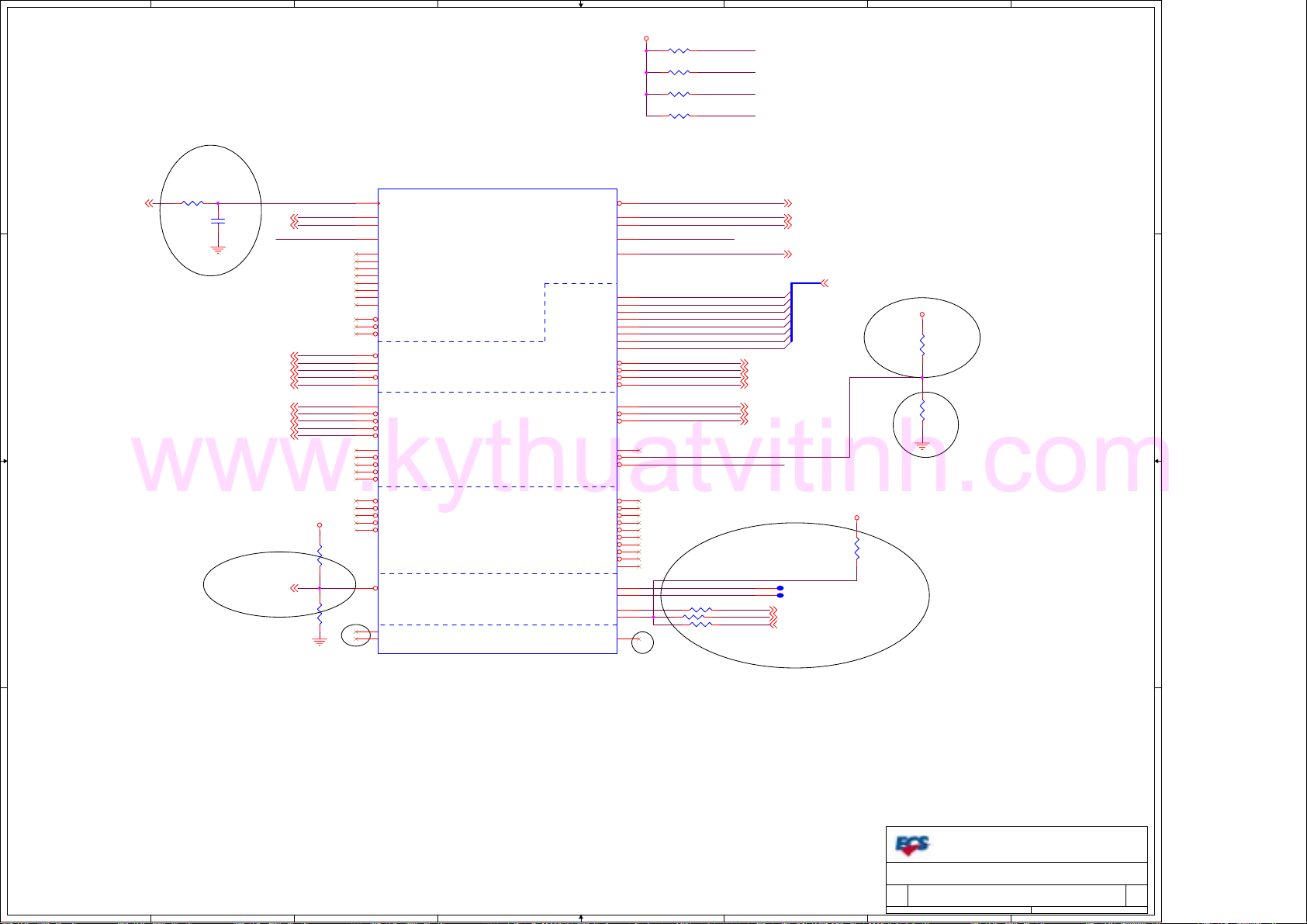

Page 4

5

www.kythuatvitinh.com

VCPU33

SR115 3.3K

R67 3.3K

SR114 3.3K

R97 4.7K_R

R96 4.7K_R

SR52 10K

D D

CPUCLK9

PWRGD11,29

TDM_RST-6

CPU_INIT-11

CPU_INTR11

CPU_NMI11

CPU_SMI-11

CPU_IGNNE-11

CPU_STPCLK-11

SUSPEND-6

PCIRST-3,8,10,16,21,23,25,28,30

SRDATA8

SROM_SIN6,8

C C

DEBUG_INT6

NM_DEBUG_INT6

TDM_TRST-6

TDM_TCK6

TDM_TMS6

TDM_TDI6

TDM_TCK

TDM_TMS

TDM_TDI

SRDATA

DEBUG_INT

NM_DEBUG_INT

R180 1.2K

R85 4.7K

SRDATA

4

U3D

Crusoe BGA474

(PART 4 OF 5)

C7

CLKIN

G7

PWRGOOD

H19

RESET#

G18

INIT#

G19

INTR

H17

NMI

G14

W11

H15

H18

D8

A8

K17

H14

G9

W7

A19

W9

SMI#

IGNNE#

STPCLK#

SLEEP#

CFG_SDATA

SROM_SIN

DEBUG_INT

NM_DEBUG_INT

TRST#

TCK

TMS

TDI

DIODE_ANODE

DIODE_CATHODE#

EPROMA0

EPROMA1

EPROMA2

CFG_SCLK

SROM_CS0#

SROM_CS1#

SROM_SCLK

SROM_SOUT

S_SDATA

VRDA0

VRDA1

VRDA2

VRDA3

VRDA4

FERR#

S_SCLK

TDO

Y12

Y13

V14

W14

W13

A18

B16

H16

J16

J15

J19

B7

K15

L15

L16

K18

A6

B6

AE1

3

VCPU33

VRDA0

VRDA1

VRDA2

VRDA3

VRDA4

SR63 10K

R78 10K

SR59 10K

SR35 10K

SR34 10K

R139 10K

R44 1K

R45 1K

R46 1KSR153 10K

R47 1K

R48 1K

VRDA[0..4]

SROM_CS1-

THERMDP

THERMDN

EPROMA1

EPROMA2

TDM_SCL

TDM_SDA

TDM_TDO

VRDA0

VRDA1

VRDA2

VRDA3

VRDA4

VRDA[0..4] 36

CPU_FERR- 11

EPROMA1 8

EPROMA2 8

SRCLK 8

SROM_CS0- 8

SROM_CS1- 6

SROM_SCLK 8

SROM_SOUT 8

TDM_SCL 6

TDM_SDA 6

TDM_TDO 6

2

1

SYSTEMS THAT DO NOT INSTALL MODE BIT ROM:

INSTALL PU R407 WHEN CMS IS IN THE SERIAL ROM

INSTALL PD R409 WHEN CMS IS IN THE PARALLEL ROM

change to 220 due to the spec.

15

2

VCC

SMBCLK

SMBDATA

ALERT

GND1

8

STBY

NC4

NC5

GMT_767

14

12

11

13

16

SR54

220

VCC3

SR253 0_R

SR254 0_R

SR88 0

SR87 0

THRM- 11

EC_SMBCLK1 25,34

EC_SMBDAT1 25,34

SMBC 7,13

SMBD 7,13

SC146

B B

THERMDP

THERMDN

VCC3

A A

SC82 2200PF

SR53 1K

SR89 1K

0.1UF

SU13

3

DXP

4

DXN

6

ADD1

10

ADD0

1

NC1

5

NC2

9

NC3

GND0

7

Elitegroup Computer Systems

Title

TM5800 SIDEBAND

Size Document Number Re v

5

4

3

2

B

Date: Sheet

A531-1-4-01

439Thursday, Augus t 28, 2003

1

V1.0

of

Page 5

5

www.kythuatvitinh.com

12

SC83

+

22UF/10V-B

D D

12

SC111

+

22UF/10V-B

C C

B B

PLACE ON BOTTOM NEAR CPU AND USE X7R CAP.

SC102

1UF-X5R

SC37

1UF-X5R

SC49

0.1UF-X7R

VCPU25VCC_DIMM

12

SC90

+

22UF/10V-B

SC152

1UF-X5R

SC178

0.1UF-X7R

SC120

1UF-X5R

SC42

1UF-X5R

C272

0.1UF-X7R

C74

1UF-X5R

SC150

1UF-X5R

SC103

0.1UF-X7R

C75

1UF-X5R

SC126

1UF-X5R

SC155

1UF-X5R

SC26

1UF-X5R

C280

0.1UF-X7R

SC45

1UF-X5R

SC54

1UF-X5R

SC132

0.1UF-X7R

SC172

1UF-X5R

0.1UF-X7R

C255

0.1UF-X7R

C146

1UF-X5R

SC174

1UF-X5R

SC121

1UF-X5R

SC19

1UF-X5R

SC104

C266

0.1UF-X7R

C148

1UF-X5R

SC135

1UF-X5R

SC142

1UF-X5R

SC109

1UF-X5R

SC130

0.1UF-X7R

4

SC75

1UF-X5R

SC177

1UF-X5R

SC131

1UF-X5R

SC119

0.1UF-X7R

C249

0.1UF-X7R

SC161

1UF-X5R

SC160

1UF-X5R

SC170

1UF-X5R

SC123

1UF-X5R

0.1UF-X7R

SC154

SC74

1UF-X5R

SC166

1UF-X5R

SC128

1UF-X5R

SC189

1UF-X5R

SC187

1UF-X5R

VCORE

SC164

1UF-X5R

3

SC151

1UF-X5R

VCPU25

PART NUMBER-->16-100-101160

VCPU33

VCORE

V_CPU_PLL

SL15

FB.100 OHM.SMD

SL6

FB.100 OHM.SMD_R

2

SC183

0.1UF_R

U3E

Crusoe BGA474

(PART 5 OF 5)

U1_A7

AB17

AC14

C14

D17

H13

K13

AB3

AC6

M13

N14

P13

R14

T13

U12

U14

V13

N17

U17

H11

K11

M11

N10

N12

P11

R10

R12

T11

U10

V11

A7

C6

D3

H7

J3

J6

J8

J12

J14

J17

K7

L6

L14

M7

N3

N6

P7

R6

T7

U3

U6

U8

V7

H9

J10

K9

L8

L10

L12

M9

N8

P9

R8

T9

V9

PLLVDD

IOVDD0

IOVDD1

IOVDD2

IOVDD3

IOVDD4

IOVDD5

IOVDD6

IOVDD7

IOVDD8

IOVDD9

IOVDD10

IOVDD11

IOVDD12

IOVDD13

IOVDD14

IOVDD15

IOVDD16

IOVDD17

IOVDD18

IOVDD19

IOVDD20

IOVDD21

IOVDD22

IOVDD23

IOVDD24

IOVDD25

IOVDD26

IOVDD27

IOVDD25_0

IOVDD25_1

IOVDD25_2

IOVDD25_3

IOVDD25_4

IOVDD25_5

IOVDD25_6

IOVDD25_7

IOVDD25_8

IOVDD25_9

IOVDD25_10

IOVDD25_11

CVDD0

CVDD1

CVDD2

CVDD3

CVDD4

CVDD5

CVDD6

CVDD7

CVDD8

CVDD9

CVDD10

CVDD11

CVDD12

CVDD13

CVDD14

CVDD15

CVDD16

CVDD17

CVDD18

CVDD19

CVDD20

CVDD21

CVDD22

GND0

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

GND19

GND20

GND21

GND22

GND23

GND24

GND25

GND26

GND27

GND28

GND29

GND30

GND31

GND32

GND33

GND34

GND35

GND36

GND37

GND38

GND39

GND40

GND41

GND42

GND43

GND44

GND45

GND46

GND47

GND48

GND49

GND50

GND51

GND52

GND53

GND54

GND55

GND56

GND57

GND58

GND59

GND60

GND61

GND62

GND63

GND64

GND65

GND66

GND67

GND68

GND69

GND70

GND71

GND72

GND73

GND74

GND75

L17

M6

M8

M10

M12

M14

N7

N9

N11

N13

P6

P8

P10

P12

P14

R3

R7

R9

R11

R13

R17

T6

T8

T10

T12

T14

U7

U9

U11

U13

V8

V10

V12

W3

W8

W10

W12

W17

Y6

Y10

Y14

AC3

AC8

AC10

AC12

AC17

C3

C8

C10

C12

C17

F6

F10

F14

G3

G8

G10

G12

G17

H8

H10

H12

J7

J9

J11

J13

K6

K8

K10

K12

K14

L3

L7

L9

L11

L13

1

A A

Elitegroup Computer Systems

Title

TM5800 CPU POWER&GND

Size Document Number Re v

5

4

3

2

B

Date: Sheet

A531-1-4-01

539Thursday, Augus t 28, 2003

1

V1.0

of

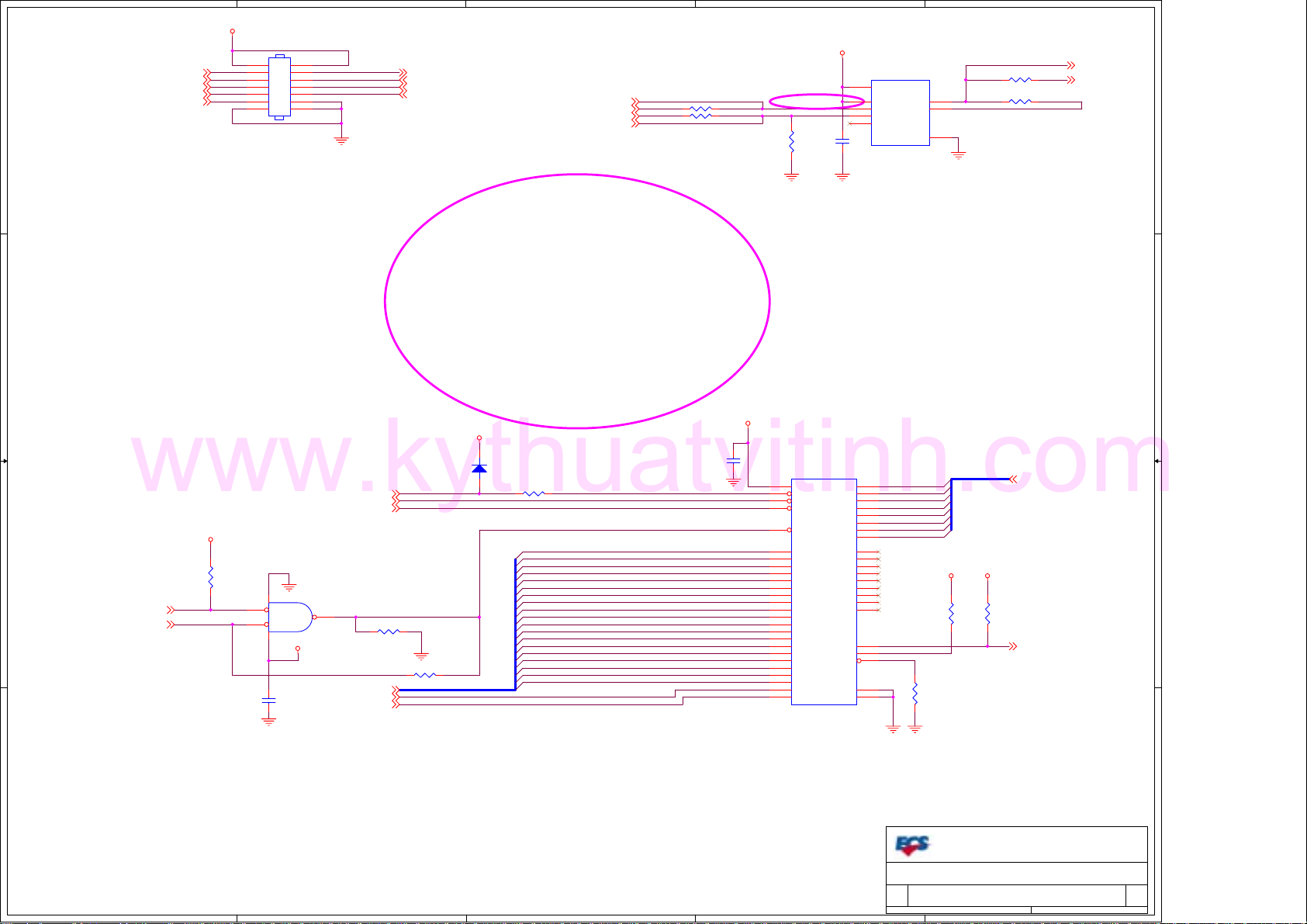

Page 6

5

www.kythuatvitinh.com

+5VAUX

U27

R336

C260

0.1UF

QS3257

16

VCC

2

1A

1Y

3

1B

5

2A

2Y

6

2B

11

3A

3Y

10

3B

14

4A

4Y

13

4B

15

G

1

A#/B

8

GND

1K

1

2

C313

0.1UF

DDR_CKE_MUX02

D D

C C

DDR_CKE_MUX12

SUSPEND-

VCC3

SUSP_ALI-11

AGP_STP-11

4

DDR_CKE0

R321 10K

DDR_CKE1

SR198 10K

DDR_CKE0

4

DDR_CKE1

7

9

12

53

7SZ08

4

U15

DDR_CKE0 7

DDR_CKE1 7

SUSPEND-

SUSPEND- 4

3

2

1

TRANSMETA DEBUG CONNECTOR

NOTE: Pinout depends on type of connector used. The pinout

below is for the vertical TDC connector. See the Design

Guide for the pinout of the right angle connector.

SJ1

52559_3092R_R

MOLEX

NM_DEBUG_INT4

DEBUG_INT4

TDM_RST-4

TDM_PWRGD29

TDM_SRCS8

B B

TDM_SRCLK8

TDM_SRDATA8

SROM_CS1-4

TDM_SROM_CS0-8

TDM_SROM_CLK8

TDM_SROM_OUT8

SROM_SIN4,8

TDM_SDA4

TDM_SCL4

TDM_TDI4

TDM_TDO4

TDM_TCK4

TDM_TMS4

TDM_TRST-4

SUSC-11,38

SUSB-11 ,31,36

SR141 220_R

SR140 0_R

SR139 0_R

1

NM_DEBUG_INIT

2

DEBUG_INIT

3

RESET#

4

SYS_RST#

5

CFG_CS

6

CFG_SCLK

7

GND0

8

CFG_SDATA

9

SROM_CS1#

10

SROM_CS0#

11

GND1

12

SROM_SCLK

13

GND2

14

SROM_SOUT

15

SROM_SIN

16

GND3

17

S_SDATA

18

GND4

19

S_SCLK

20

GND5

21

TDI

22

GND6

23

TDO

24

TCK

25

TMS

26

TRST#

27

GND7

28

SUSC#

29

SUSB#

30

GND8

A A

Elitegroup Computer Systems

Title

CKE SW& TDM DEBUG PORT

Size Document Number Re v

5

4

3

2

B

Date: Sheet

A531-1-4-01

639Thursday, Augus t 28, 2003

1

V1.0

of

Page 7

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

SC265

0.1UF

DDR_A[12..0]

DDR_DQM[7..0]

DDR_DQ[0..63]

DDR_DQS[7..0]

+3VAUX VCC_DIMM

12

12

C201

1000PF

SR219

0

SU20B

amp_c-1565618-1_DDR40-S

9

VDD_01

10

VDD_02

21

VDD_03

22

VDD_04

33

VDD_05

34

VDD_06

36

VDD_07

45

VDD_08

46

VDD_09

57

VDD_10

58

VDD_11

69

VDD_12

70

VDD_13

81

VDD_14

82

VDD_15

92

VDD_16

93

VDD_17

94

VDD_18

113

VDD_19

114

VDD_20

131

VDD_21

132

VDD_22

143

VDD_23

144

VDD_24

155

VDD_25

156

VDD_26

157

VDD_27

167

VDD_28

168

VDD_29

179

VDD_30

180

VDD_31

191

VDD_32

192

VDD_33

1

VREFA

2

VREFB

197

VDDSPD

199

VDDID

GND_01

GND_02

GND_03

GND_04

GND_05

GND_06

GND_07

GND_08

GND_09

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

GND_17

GND_18

GND_19

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_30

GND_31

GND_32

GND_33

GND_34

GND_35

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

201

202

DIMM1

SU20A

DDR_A[12..0]

D D

DDR_DQM[7..0]2

DDR_DQS[7..0]2

C C

CLK_DDRA CLK_DDRA-

SC193

10PF_R

CLK_DDRB CLK_DDRB-

SC196

10PF_R

B B

SC194

10PF_R

SC195

10PF_R

DDR_DQM[7..0]

DDR_DQS[7..0]

DDR_CS0-2

DDR_CS1-2

DDR_RAS-2

DDR_CAS-2

DDR_MWE-2

DDR_BA02

DDR_BA12

CLK_DDRA2

CLK_DDRA-2

CLK_DDRB2

CLK_DDRB-2

DDR_CKE06

DDR_CKE16

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_DQM7

DDR_DQM6

DDR_DQM0

DDR_DQM1

DDR_DQM5

DDR_DQM2

DDR_DQM4

DDR_DQM3

DDR_DQS7

DDR_DQS6

DDR_DQS0

DDR_DQS1

DDR_DQS5

DDR_DQS2

DDR_DQS4

DDR_DQS3

SMBC

SMBC4,13

SMBD

SMBD4,13

amp_c-1565618-1_DDR40-S

112

A_00

111

110

109

108

107

106

105

102

101

115

100

99

97

12

26

48

62

134

148

170

184

11

25

47

61

133

147

169

183

121

122

118

120

119

117

116

98

35

37

160

158

89

91

96

95

195

193

86

71

73

79

83

72

74

80

84

77

DQ_00

A_01

DQ_01

A_02

DQ_02

A_03

DQ_03

A_04

DQ_04

A_05

DQ_05

A_06

DQ_06

A_07

DQ_07

A_08

DQ_08

A_09

DQ_09

A_10

DQ_10

A_11

DQ_11

A_12

DQ_12

A_13

DQ_13

DQ_14

DQ_15

DM_0

DQ_16

DM_1

DQ_17

DM_2

DQ_18

DM_3

DQ_19

DM_4

DQ_20

DM_5

DQ_21

DM_6

DQ_22

DM_7

DQ_23

DQ_24

DQ_25

DQ_26

DQ_27

DQS_0

DQ_28

DQS_1

DQ_29

DQS_2

DQ_30

DQS_3

DQ_31

DQS_4

DQS_5

DQ_32

DQS_6

DQ_33

DQS_7

DQ_34

DQ_35

S0#

DQ_36

S1#

DQ_37

DQ_38

RAS#

DQ_39

CAS#

DQ_40

WE#

DQ_41

DQ_42

BA0

DQ_43

BA1

DQ_44

BA2

DQ_45

DQ_46

DQ_47

CK0

DQ_48

CK0#

DQ_49

CK1

DQ_50

CK1#

DQ_51

CK2

DQ_52

CK2#

DQ_53

DQ_54

DQ_55

CKE0

DQ_56

CKE1

DQ_57

DQ_58

SCL

DQ_59

SDA

DQ_60

DQ_61

RESET#

DQ_62

CBQ0

DQ_63

CBQ1

CBQ2

CBQ3

CBQ4

CBQ5

CBQ6

CBQ7

CBQS

CBDM78NC1

SA2

SA1

SA0

NC4

NC3

NC2

5

7

13

17

6

8

14

18

19

23

29

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

DDR_SOD1_SA2

198

DDR_SOD1_SA1

196

DDR_SOD1_SA0

194

200

124

123

85

DDR_DQ58

DDR_DQ59

DDR_DQ57

DDR_DQ56

DDR_DQ62

DDR_DQ63

DDR_DQ60

DDR_DQ61

DDR_DQ52

DDR_DQ55

DDR_DQ51

DDR_DQ48

DDR_DQ50

DDR_DQ54

DDR_DQ53

DDR_DQ49

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ45

DDR_DQ47

DDR_DQ46

DDR_DQ44

DDR_DQ19

DDR_DQ18

DDR_DQ23

DDR_DQ22

DDR_DQ16

DDR_DQ17

DDR_DQ20

DDR_DQ21

DDR_DQ33

DDR_DQ32

DDR_DQ34

DDR_DQ35

DDR_DQ39

DDR_DQ38

DDR_DQ37

DDR_DQ36

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ29

DDR_DQ28

DDR_DQ30

DDR_DQ31

DDR_DQ[0..63]

VCC_DIMM

DDR_A[12..0]2

DDR_DQM[7..0]2

DDR_DQ[0..63]2

DDR_DQS[7..0]2

12

R208

768_1%

1%

12

SR218

768_1%

1%

12

+3VAUXVCC_DIMM

+

C256

47UF/6.3V-B

4

+

C350

47UF/6.3V-B

C228

0.1UF

C230

0.1UF

C211

0.1UF

C265

0.1UF

C206

0.1UF

C207

0.1UF

C226

0.1UF

CLOSE TO SDRAM CELLS

Elitegroup Computer Systems

Title

SODIMM & ON BOARD RAM

Size Document Number Re v

B

3

Date: Sheet

2

C213

C234

0.1UF

0.1UF

A531-1-4-01

C279

0.1UF

V1.0

of

739Thursday, Augus t 28, 2003

1

VCC_DIMM

C236

+

C291

C239

0.01UF

100UF/10V-C

A A

VCC_DIMM

C204

0.1UF

8

7

0.01UF

C205

0.1UF

CLOSE TO DIMM1

C209

0.1UF

C233

0.01UF

6

C225

0.1UF

C208

0.1UF

C235

0.01UF

C229

0.1UF

C269

0.01UF

C231

0.1UF

C210

0.01UF

5

C243

0.1UF

C212

0.01UF

C227

0.1UF

C232

0.01UF

C241

0.1UF

Page 8

5

www.kythuatvitinh.com

VCPU33

JP1

2

1

4

SROM_WP13

SROM_CS0-4

SROM_SCLK4

SROM_SOUT4

PCIRST-3,4,10,16,21,23,25,28,30

D D

3

6

5

7

8

9

10

11

12

13

14

SUYIN_20088A_14G2_R

4

SROM_SIN 4,6

TDM_SROM_OUT 6

TDM_SROM_CS0- 6

TDM_SROM_CLK 6

3

TDM_SRCS6

PCIRST-3,4,10,16,21,23,25,28,30

SRCLK4

TDM_SRCLK6

R84 470

R95 470

R86

10K

03/06

2

C141

0.1UF

VCPU33

2Kb SROMFOR DEBUGGING

U2 93LC56B-1/SN

8

VCC

6

PE

1

CS

2

SK

7

PRE

VSS

1

R88 470

R80 33

3

DI

4

DO

5

TDM_SRDATA 6

SRDATA 4

DO_U6

UNPROTECT IS USED TO

ENABLE/DIAABLE APPLICATION OF

12V TO THE PARALLEL ROM.

C C

04/25 version 2.0

C299

0.1UF

VCC5

U24

37

VCC

12

RESET#

26

CE#

28

OE#

11

WE#

45

DQ15/A-1

25

A0

24

A1

23

A2

22

A3

21

A4

20

A5

19

A6

18

A7

8

A8

7

A9

6

A10

5

A11

4

A12

3

A13

2

A14

1

A15

48

A16

17

A17

16

A18

9

A19

MERITEC 980020-48-02

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

NC_10

NC_13

RY/BY#

NC_14

BYTE#

GND_0

GND_1

R306

10K

XD[7..0] 11,25,29,30

BIOS_BSY- 13

XD0

29

XD1

31

XD2

33

XD3

35

XD4

38

XD5

40

XD6

42

XD7

44

30

32

34

36

39

41

43

10

13

15

14

47

27

46

R283

10

VCC5VCC5

R307

10K

IF BIOS_BSY# SIGNAL

IS USED, CONNECT TO

GPI OF SOUTHBRIDGE OR

OTHER DEVICE.

VCC3

D24

1SS355_R

P N

R302 10K

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

ROM_WE-

U21

7SZ32

4

PCIRST0-10,14

ROMCS-11,25

XMEMR-11,30

SA[18..0]11,25,29,30

EPROMA14

EPROMA24

R298 10K_R

R297 0_R

GPIO CAN USED TO ALLOW

BIOS TO GATE WRITES TO THE

PARALLEL ROM

B B

GPIO13

XMEMW-11,30

VCC5

R275

10K

2

1

5 3

VCC5

C318

0.1UF

If used for System BIOS and CMS, install 2M.

In TM5X00 systems, the lower 3/4 of the ROM are protected and unable to be erased (i.e. by an 'erase all' command to

the ROM). The unprotect circuit allows CMS to reprogram protected sectors during a CMS upgrade (TM5X00 only). Note

A A

how EPROMA[2..1] signals are connected to the 2MB ROM. These signals act as bank selects to select either CMS

sectors or BIOS. When CMS has decompressed and is ready to run x86 code, these signals select the highest bank (11)

to allow access to the BIOS code.

Elitegroup Computer Systems

Title

PARALLEL&SERIAL ROM&DEBUG PORT

Size Document Number Re v

5

4

3

2

B

Date: Sheet

A531-1-4-01

839Thursday, Augus t 28, 2003

1

V1.0

of

Page 9

00

www.kythuatvitinh.com

D D

C C

8

VCC3

7

SL17 FCM2012K-600

SC206

10UF/10V-A

6

SC224

SC212

SC214

SC243

0.1UF

+

V25

0.1UF

0.1UF

SL19 FCM2012K-600

CPUSTP-11

PCISTP-11

SB_14M11

VGA_14M16

CAP

SR157

SR169

SC227

0.1UF

SC228

CAP

SEL_100/66-

PCI_STPPD-

REF0/SEL_SS-

22

REF1/SPREAD-

22

SY2

14.318MHz

SC211

10PF

SC241

CAP

5

SC213

10PF

SU19

8

VDDPCI

12

VDD48

19

VDD

28

VDDREF

25

VDDL

1

GNDREF

7

GNDPCI

15

GND48

21

GND

22

GNDL

16

SEL100/66#

18

CPU_STOP#

20

PCI_STOP#

17

PD#

27

REF0/SEL_SS#

26

REF1/SPREAD#

2

X1

3

X2

ICS9248-176

CPUCLK0

CPUCLK1

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK_F

48MHz_0

TS#/48MHz_1

4

Damping Resistors

Place near to the

Clock Outputs

RCPUCLK

23

24

5

6

9

10

11

4

13

14

SR172 22

RLPCLK

SR154 33

R8100BCLK

SR158 33

R315ECLK

SR170 33

RUSB20CLK

SR175 33

RMINICLK

SR179 33

PCICLK_F

SR145 33

SR148 33

SR191 33

SR192 10K

3

VCC3

USBCLK 11,23

Enable 48Mhz Output

CPUCLK 4

LPCLK 30

8100BCLK 26

315ECLK 16

USB20CLK 23

MINICLK 28

PCICLKTM 3

M1535+CLK 10

2

By-Pass Capacitors

Place near to the Clock

Gernerator

CPUCLK

LPCLK

8100BCLK

315ECLK

USB20CLK

MINICLK

PCICLKTM

M1535+CLK

USBCLK

SC239

SC215

SC220

SC225

SC231

SC236

SC201

SC207

SC242

CAP

CAP

CAP

CAP

CAP

CAP

CAP

CAP

CAP

1

SEL 100/66# = Logic "0" is use the 66.6MHz / Logic "1" is use the

100MHz

B B

VCC3

@100MHz

SR196 10K_R

SR187 10K

SR177 10K

SR156 10K_R

SR162 10K_R

SEL_100/66-

PD-

PCI_STP-

REF0/SEL_SS-

REF1/SPREAD-

@66MHz

SR194 10K

SR152 10K

SR161 10K

03/06

SPREAD# / High = Spectrum Off / Low = Spectrum ON

SEL_SS# / High = Down Spread -0.125% / Low = Down Spread -0.25%

A A

Elitegroup Computer Systems

Title

CLOCK GENERATOR

Size Document Number Re v

8

7

6

5

4

3

B

Date: Sheet

2

A531-1-4-01

939Thursday, Augus t 28, 2003

1

V1.0

of

Page 10

8

www.kythuatvitinh.com

VCC3

SRP23 8.2KX4

1

2

3

4 5

SR231 8.2K

SR227 8.2K

D D

INT-A

8

INT-D

7

INT-B

6

INT-C

INT-E

INT-F

INTA:VGA,USB

INTB.C.D:USB

INTC:LAN

INTE.F:MINPCI

C C

B B

7

M1535+CLK9

PCI_HLDA-3

FRAME-3,16,23,26,28

IRDY-3,16,23,26,28

TRDY-3,16,23,26,28

STOP-3,16,23,26,28

DEVSEL-3,16,23,26,28

PAR3,16,23,26,28

C/BE-03,16,23,26,28

C/BE-13,16,23,26,28

C/BE-23,16,23,26,28

C/BE-33,16,23,26,28

INT-A

INT-A16,21,23

INT-B

INT-B23

INT-C

INT-C23,26

INT-D

INT-D23

INT-E AD20

INT-E28

INT-F

INT-F28

IDEDA[0..15]14

IDEDB[0..15]14

IDEDA[0..15]

ICHRDYA14

IDEIRQA14

IDEREQA14

ICHRDYB14

IDEIRQB14

IDEREQB14

IDEDB[0..15]

IDEDA0

IDEDA1

IDEDA2

IDEDA3

IDEDA4

IDEDA5

IDEDA6

IDEDA7

IDEDA8

IDEDA9

IDEDA10

IDEDA11

IDEDA12

IDEDA13

IDEDA14

IDEDA15

IDEDB0

IDEDB1

IDEDB2

IDEDB3

IDEDB4

IDEDB5

IDEDB6

IDEDB7

IDEDB8

IDEDB9

IDEDB10

IDEDB11

IDEDB12

IDEDB13

IDEDB14

IDEDB15

6

E8

PCICLK

A10

PHLDA#

A3

FRAME#

D4

IRDY#

C4

TRDY#

A4

STOP#

B4

DEVSEL#

B5

PAR

B7

C_BE0#

A5

C_BE1#

B3

C_BE2#

D2

C_BE3#

F4

INTA#/M1

F5

INTB#/S0

G3

INTC#/S1/GPI27

G4

INTD#/S2/GPI28

G5

INTE#/GPI29

H4

INTF#/GPI30/MOTOR_ON#

G17

PIDED0

F20

PIDED1

F18

PIDED2

F16

PIDED3

E19

PIDED4

D20

PIDED5

D18

PIDED6

B20

PIDED7

C20

PIDED8

D19

PIDED9

E18

PIDED10

E20

PIDED11

F17

PIDED12

F19

PIDED13

G16

PIDED14

G18

PIDED15

H17

PIDERDY

N16

SIRQI

G19

PIDEDRQ

A18

SIDERDY

P16

SIRQII

C17

SIDEDRQ

A17

SIDED0

D16

SIDED1

B16

SIDED2

E15

SIDED3

C15

SIDED4

A15

SIDED5

D14

SIDED6

E13

SIDED7

D13

SIDED8

E14

SIDED9

B15

SIDED10

D15

SIDED11

A16

SIDED12

C16

SIDED13

E16

SIDED14

B17

SIDED15

5

U11A

ALI M1535

(Part 1 of 4)

Symbol ver 1

PCI

IDE

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PCIRST#

PHOLD#

SERR#

PIDECS1#

PIDECS3#

PIDEA0

PIDEA1

PIDEA2

PIDEIOR#

PIDEIOW#

PIDEDAK#

SIDECS1#

SIDECS3#

SIDEA0

SIDEA1

SIDEA2

SIDEIOR#

SIDEIOW#

SIDEDAK#

4

AD[0..31] 3,16,23,26,28

VCC3

AD0

A9

AD1

B9

AD2

C9

AD3

A8

AD4

B8

AD5

C8

AD6

D8

AD7

A7

AD8

C7

AD9

D7

AD10

E7

AD11

A6

AD12

B6

AD13

C6

AD14

D6

AD15

E6

AD16

C3

AD17

A2

AD18

B2

AD19

C2

A1

AD21

B1

AD22

C1

AD23

D3

AD24

D1

AD25

E3

AD26

E2

AD27

E1

AD28

F3

AD29

F2

AD30

F1

AD31

G2

C5

C11

D5

J17

J18

H20

H19

J16

H16

G20

H18

C19

A20

A19

C18

B19

E17

D17

B18

IDECS-A0 14

IDECS-A1 14

IDESAA0 14

IDESAA1 14

IDESAA2 14

IDEIOR-A 14

IDEIOW-A 14

IDACK-A 14

IDECS-B0 14

IDECS-B1 14

IDESAB0 14

IDESAB1 14

IDESAB2 14

IDEIOR-B 14

IDEIOW-B 14

IDACK-B 14

3

VCC3

R251

1K

R260

4.7K

PCIRST0- 8,14

PCI_HLD- 3

SERR- 3,23,26,28

147

1

2

U18A

74LCX08

2

C261

0.1UF

3

PCIRST- 3,4,8,16,21,23,25,28,30

1

A A

Elitegroup Computer Systems

Title

Size Document Number Re v

8

7

6

5

4

3

B

Date: Sheet

M1535+(PCI+IDE)

A531-1-4-01

2

V1.0

of

10 39Thursday, Augu st 28, 2003

1

Page 11

8

www.kythuatvitinh.com

R167 10K

R168 10K

SR173 10K

SR178 10K

SR215 10K

ALI_+3VALWAYS

RP28 10KX4

1 8

2 7

3 6

D D

VCPU25

ALI_+5VALWAYS

C C

4 5

SR183 10K

R213 10K

VCC3

R175 10K

SR204 10K

R233 10K

R204 10K

SR206 10K

R215 10K

SR207 10K_R

SR208 10K_R

PWRBTN-13,30

PID0

PID1

M/BID0

M/BID1

IOCHRDY

LLBPMESLPBTNACPWR

OFFCDPWR-

CPU_FERR-

AGPBUSYTHRMCPUSTP-

ZZ

SUSAALI_SUSBALI_SUSC-

+3VALWAYS

R226 10K

D18

1SS355

PUT SAME R208

DEL

R208,C215

B B

A A

XD[7..0]8,25,29,30

SB_14M9

32KII

32KI

R198

20M

8

PN

12

3

7

USBCLK9,23

03/27

PREVENT EMI

SR195 0

R200

Y3

20M

32.768KHZ

7

CPU_FERR-4

RSM_RST-29

PWRGD4,29

PID025

PID125

PCIREQ-30

C193

20PF

C187

20PF

SR174 10K_R

SR182 10K_R

LB-37

LLB-37

PME-2 3,26,28

THRM-4

IRQ8-29

03/06

SR205 0

PID0

PID1

CPU_FERR-

SLPBTN-

LBLLBACPWR

PMERI-

SERIRQ

THRM-

ZZ

AGPBUSY-

IOCHRDY

XD7

XD6

XD5

XD4

XD3

XD2

XD1

XD0

SC259

20PF_R

6

M/BID0

M/BID1

32KI

32KII

C199 180PF_R

C202 180PF_R

6

VCC5VCC5

SR159 10K

SR217 10K

R248 10K_R

R249 10K

R240 10K

SR216 10K

R256 10K

H5

T5

T6

U5

U6

A12

W10

U10

Y15

V10

W11

Y11

Y10

W12

V11

B11

N19

T18

Y12

E12

D11

M17

W19

Y19

V20

W20

Y20

U18

U19

U20

D10

W6

Y6

SQWO

USBSMI-

PCS0-

SERIRQ

ROMCS-

MCCS-

GPO30

U11B

ALI M1535

USBCLK

OVCR0#/SEL_MODE0/GPIO20

OVCR1#/SEL_MODE1/GPIO21

OVCR2#/INC_CCFT/GPIO22

OVCR3#/DEC_CCFT/GPIO23

FERR#/IRQ13I

RSM_RST#

PWG

PWRBTN#

SLPBTN#

LB#/RSM_ENT0

LLB#/RSM_ENT1

ACPWR/RSM_ENT8

PME#

RI#

PCIREQ#

IRQSER

THRM#

IRQ8#

ZZ/RATIO#

AGP_BUSY#/GPI26/CBLID_P

IOCHRDY/GPI24

XD7

XD6

XD5

XD4

XD3

XD2

XD1

XD0

OSC14M

OSC32KI

OSC32KII

SA0/LAD0/RUN_ENT16/EGPIO0/ERUN_ENT16/EEGPIO0

SA1/LAD1/RUN_ENT17/EGPIO1/ERUN_ENT17/EEGPIO1

SA2/LAD2/RUN_ENT18/EGPIO2/ERUN_ENT18/EE3GPIO2

SA3/LAD3/RUN_ENT19/EGPIO3/ERUN_ENT19/EEGPIO3

CPU_NMI

CPU_INTR

5

SUPPORT PENTIUM II CPU AND

SWITCH SLEEP/GPO32 PIN TO

SLEEP

Normal operation

DISABLE 4Mb ROM

Normal operation

OFFWR1&2 DESKTOP MODE

Normal operation

Normal operation

(Part 2 of 4)

USB_PWREN#/RSM_ENT2/GPI31/GPO38

USB

USBP2+/RSM_ENT5/GPI34/GPO41

USBP2-/RSM_ENT4/GPI33/GPO40

USBP3+/RSM_ENT7/GPI36/GPO43

USBP3-/RSM_ENT6/GPI35/GPO42

CPU Sideband

OFF_CDPWR#/RSM_ENT3/GPI32/GPO39

Power Control

X Bus

PCS1#/CVROFF/RUN_ENT6/GPIO6

SA4/RUN_ENT20/EGPIO4/ERUN_ENT20/EEGPIO4

SA5/RUN_ENT21/EGPIO5/ERUN_ENT21/EEGPIO5

SA6/RUN_ENT22/EGPIO6/ERUN_ENT22/EEGPIO6

SA7/RUN_ENT23/EGPIO7/ERUN_ENT23/EEGPIO7

SA10/SD10/EGPIO10/EEGPIO10

SA11/SD11/EGPIO11/EEGPIO11

SA12/SD12/EGPIO12/EEGPIO12

SA13/SD13/EGPIO13/EEGPIO13

SA14/SD14/EGPIO14/EEGPIO14

SA15/SD15/EGPIO15/EEGPIO15

RTC

5

prevent resume power flow out

03/06

USBP0+

USBP0-

USBP1+

USBP1-

CPURST#

IGNNE#

A20M#

STPCLK#

SLEEP#/GPO32

OFF_PWR0#/GPO36

OFF_PWR1#/GPO37

OFF_PWR2#

CPU_STP#/GPO44

PCI_STP#

SUSPEND#

CLKRUN#/GPIO20

SLOWDOWN/GPIO21

SPLED

AGP_STP#/GPO33/CBLID_S

PCS2#/BIOSA19/GPO29

SA8/SD8/EGPIO8/EEGPIO8

SA9/SD9/EGPIO9/EEGPIO9

BIOSA18/GPO24/CLK_OFF#

SQWO

IOR#/GPO27

IOW#/GPO28

MEMR#

MEMW#

AEN/GPO30

ROMKBCS#

PCS0#/GPO31

BIOSA16/GPO26

BIOSA17/GPO25

RTCAS

RTCDS

RTCRW

CLK32KO

SUSC-6,38

ALI_+5VALWAYS

SUSB-6,31,36

ALI_+5VALWAYS

INIT#

INTR

SMI#

NMI

4

V9

W8

V8

U9

Y7

W7

V7

U8

T8

B13

C14

B12

C12

A13

C13

A14

B14

D12

V14

W14

Y14

T9

C10

B10

W13

A11

D9

Y13

V6

E11

T13

U13

T14

U14

N18

T20

P20

R16

N17

V19

Y18

W18

V18

Y17

W17

V17

U17

T17

R17

Y16

W16

V16

U16

T16

W15

V15

U15

T15

R20

R18

R19

V13

SR136

10K

1 2

4

SR138

10K

1 2

VCPU25

SRP25 10KX4

6

7

8

RP29 10KX4

6

7

8

R202 10K

USBP0+

USBP0-

USBP1+

USBP1-

SCI

SWI

USBP3+

USBP3-

CPU_INITCPU_INTR

CPU_NMI

CPU_SMICPU_IGNNECPU_A20MCPU_STPCLKSLEEP-

SUSAALI_SUSBALI_SUSCOFFCDPWR-

CPUSTP-

PCI_CLKRUNSLOWDOWN

SPLED

SQWO

GPO30

ROMCSPCS0USBSMI-

R211 1K

SQ19

2N7002

D

SQ18

2N7002

D

3

CPU_STPCLK-

45

CPU_INTR

3

2

CPU_NMI

1

CPU_INIT-

45

CPU_SMI-

3

CPU_IGNNE-

2

SLEEP-

1

ADD N POLAR

D17

CH301H-40

PN

SCI 25

SWI 25

R216 0_R

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

ALI_SUSC-

SD

G

1 2

ALI_SUSB-

SD

G

1 2

3

1/21

SR135

10K_R

SR143

10K_R

03/06

03/27

LID- 30

03/06

CPU_INIT- 4

CPU_INTR 4

CPU_NMI 4

CPU_SMI- 4

CPU_IGNNE- 4

CPU_A20M- 23

CPU_STPCLK- 4

SPDIF 32,33

CPUSTP- 9

PCISTP- 9

SUSP_ALI- 6

PCI_CLKRUN- 3,23,28

SPLED 33

AGP_STP- 6

XIOR- 25,30

XIOW- 25,3 0

XMEMR- 8,30

XMEMW - 8, 30

ROMCS- 8,25

USBSMI- 23

MCCS- 25

Title

Size Document Number Re v

B

Date: Sheet

2

PREVENT LEAKAGE

CURRENT

R206 1K

R207 10K

OFF_PWR1 AND OFF_PWR2 LOW

ACTIVE TO POWER OFF

R203 10K

R201 10K

SRP24 10KX4

1

8

2

7

3

6

4 5

SR197 10K

SR200 10K

SCI

SWI

USBP1+

USBP1USBP3USBP3+

USBP0+

USBP0-CPU_A20M-

RI-

LB-

1/21

DISABLE

USB

FUNCTION

SR214 1K

R255 1K

SR188 0

R205 1K

ATX MODE :LOW

SPLED

PCS0-

ENABLE 4Mb ROM

SLOWDOWN

PCI_CLKRUN-

PCICLK ALWAYS

RUNNING

SA[18..0] 8,25,29,30

RTCAS 29

RTCDS 29

RTCRW 29

Elitegroup Computer Systems

M1535+ MISC.

A531-1-4-01

2

11 39Thursday, Augu st 28, 2003

1

V1.0

of

1

Page 12

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

VCC5

R182 10K

SR147 10K

SR165 10K

Y9

P4

U1

R4

T19

P2

P3

N1

N2

N3

N4

N5

M2

R2

R3

P1

R1

J5

H1

J3

K2

K3

L2

L19

L18

M19

L16

L17

K19

K20

K17

K18

J19

U11

U12

T11

T12

M1

11/27

SR164 10K

ACMIDI_TXDACMIDI_RXD

SR209 0_R

SR201 0_R

SR202 0

D D

12/17

U11C

SR203

BIT_CLK28,32

C C

B B

0

SC226

22PF_R

SDATI032

SDATI128

ACK-15

SLCT15

BUSY15

ERROR-15

PE15

RXDA15

CTSA-15

DSRA-15

DCDA-15

RIA-15

VCC5

OUT_IRQ123

12/5

R210

4.7K

R212

4.7K_R

P5

ACBIT_CLK

W9

ACSDATA_IN0

Y8

ACSDATA_IN1

T4

ACMIDI_RXD

V1

ACGAME0

V2

ACGAME1

V3

ACGAME2/GPIO16

W1

ACGAME3/GPIO17

W2

ACGAME4

W3

ACGAME5

Y1

ACGAME6/GPIO18

Y2

ACGAME7/GPIO19

U3

ACGP_UP#/RUN_ENT11/GPIO11

R5

ACGP_DOWN#/RUNENT12/GPIO12

U2

ACGP_MUTE#/RUN_ENT13/GPIO13

M3

PRNACK#

L5

SLCT

M4

BUSY

T1

ERROR#

M5

PE

H2

SIN1

J4

CTS1#

H3

DSR1#

G1

DCD1#

J2

RI1#

K4

SIN2/RUN_ENT8/GPIO8

K1

CTS2#/RUN_ENT12/GPIO12

K5

DSR2#/RUN_ENT13/GPIO13

J1

DCD2#/RUN_ENT14/GPIO14

L1

RI2#/RUN_ENT15/GPIO15

M20

DSKCHG#/RUN_ENT22/EGPIO6

M18

RDATA#/RUN_ENT16/EGPIO0

M16

WPROT#/EGPIO11

L20

TRK0#/EGPIO12

J20

INDEX#/EGPIO13

V12

KBINH/IRQ1I

L4

IRRXH

L3

IRRX

11/27

ALI M1535

(Part 3 of 4)

Parallel Port

Serial Ports

Floppy

Keyboard & Mouse

Infrared

Audio

SOUT2/RUN_ENT9/GPIO9

RTS2#/RUN_ENT10/GPIO10

DTR2#/RUN_ENT11/GPIO11

WGATE#/RUN_ENT17/EGPIO1

WDATA#/RUN_ENT18/EGPIO2

HDSEL#/RUN_ENT19/EGPIO3

FD_DIR#/RUN_ENT20/EGPIO4

STEP#/RUN_ENT21/EGPIO5

DRV0#/RUN_ENT23/EGPIO7

ACRESET#

ACSYNC

ACSDATA_OUT

ACMIDI_TXD

SPKR

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PRINIT#

SLCTIN#

STROB#

AUTOFD#

SOUT1

RTS1#/CONFIG

DTR1#

DRV1#/EGPIO8

MOT0#/EGPIO9

MOT1#/EGPIO10

DENSEL/EGPIO14

KBCLK/DISPLAY

KBDATA/CCFT

MSCLK/FPVEE

MSDATA/IRQ12I

IRTX

LPT0

LPT1

LPT2

LPT3

LPT4

LPT5

LPT6

LPT7

RTSA-

RTS2J

DTR2J

PS2CLK

PS2DATA

DTR2J

RTSA-

ACMIDI_RXD

ACMIDI_TXD

Internal KB PS2 Mode

Base addr. x3F0 for SIO

AC_RESET- 28,32

SYNC 28, 32

SDATO 28,32

PCBEEP 32

LPT[0..7]

INIT- 15

SLCTIN- 15

STB- 15

AFD- 15

TXDA 15

RTSA- 15

DTRA- 15

STP1

1

TEST POINT

STP2

1

TEST POINT

MSCLK 25

MSDATA 25

OUT_IRQ12 23

LPT[0..7] 15

11/29

VCC5

SR199

4.7K

VCC5

12/5

SR149

10K_R

SR151

1K

PD DISABLE INT. KB

PU ENABLE INT. KB

12/5

A A

Elitegroup Computer Systems

Title

Size Document Number Re v

8

7

6

5

4

3

B

Date: Sheet

M1535+(AUDIO/IO)

A531-1-4-01

2

12 39Thursday, Augu st 28, 2003

V1.0

of

1

Page 13

8

www.kythuatvitinh.com

D D

ALI_+3VALWAYS

0.1UF

SC249

0.1UF

C C

B B

SC258

0.1UF

SC262

0.1UF

SC264

0.1UF

SC263

0.1UF

SC234

0.1UF

SC233

0.1UF

SC235

0.1UF

SC252

ALI_+5VALWAYS

7

VCC5

VCC3

VCPU25

R177 10K

GPIO8

KBSMI-25

CBLIDA14

SROM_WP8

BIOS_BSY-8

6

SMB_ALERT-

FANIN2

LDRQ-

PDMA_REQ-

U11D

ALI M1535

E10

VCC_5A_0

G6

VCC_5A_1

N6

VCC_5A_2

N15

VCC_5A_3

R15

VCC_5A_4

G15

VCC_F_0

K16

VCC_F_1

P15

VCC_3B

F6

VCC_3C_0

F7

VCC_3C_1

F14

VCC_3C_2

P6

VCC_3C_3

F15

VCC_G

R7

VCCR_5D_0

R13

VCCR_5D_1

R6

VCCR_3E_0

R8

VCCR_3E_1

R14

VCCR_3E_2

T10

UPSPWR

T2

SMB_ALERT#/FANIN1/EM_OFF

Y5

FANIN2/RUN_ENT9/GPIO9

P17

LDRQ#/RUN_ENT4/GPIO4

E4

SCLK/PDMA_REQ#/RUN_ENT14/GPIO14

T3

PCMDATA/RUN_ENT10

Y3

RUN_ENT0/GPIO0/IN_STROB#

V4

RUN_ENT1/GPIO1

W4

RUN_ENT2/GPIO2

Y4

RUN_ENT3/GPIO3

E9

GPI25

5

(Part 4 of 4)

Power & Ground

FANOUT1/RUN_ENT7/GPIO7

FANOUT2/RUN_ENT8/GPIO8

LFRAME#/RUN_ENT5/GPIO5

LRCLK/PDMA_GNT#/RUN_ENT15/GPIO15

Miscellaneous

4

GND_0

GND_1

GND_2

GND_3

GND_4

GND_5

GND_6

GND_7

GND_8

GND_9

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

GND_17

GND_18

GND_19

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_30

GND_31

GND_32

GND_33

GND_34

GND_35

SMBCLK

SMBDATA

TEST#

GPIR#/GPO34

GPOW/GPO35

H8

H9

H10

H11

H12

H13

J8

J9

J10

J11

J12

J13

K8

K9

K10

K11

K12

K13

L8

L9

L10

L11

L12

L13

M8

M9

M10

M11

M12

M13

N8

N9

N10

N11

N12

N13

T7

U7

W5

V5

U4

N20

E5

P18

P19

3

SMBC

SMBC 4,7

SMBD

SMBD 4,7

FANON

FANOUT2

TEST-

LFRAME-

LFRAME- 30

LRCLK

GPIRGPOW

2

VCC5

SR176 1K

R241 1K

SR163 10K

VCC3

SRP22 1KX4

6

7

8

SR167 1K

R234 1K

R181 10K

R265 10K

SR166 1K

LRCLK

GPIR-

PDMA_REQ-

FANON

SMBD

TESTSMBC

FANOUT2

LFRAME-

SMB_ALERT-

LDRQFANIN2

VCC5

45

3

2

1

03/06

R270

1K_R

PULL HIGH:ENABLE LPC ROM

R264

10K

1

PULL LOW:DISABLE LPC ROM

12/17

PWRBTN-

+3VALWAYS

R250 100K

D20

1SS355

ON3_5

B

VCC5 VCC5

R137

1K

FANON

R138

A A

10K

Q15

SI2302DS

FOR CPU

C155

22UF/10V-B

CN9

1

+

2

DT_91-00147-003_02P125V

C159

0.1UF

Close FAN Connector

L24

HCB2012K-800T80

1 2

C156

+

4.7UF/25V

SC190

+

4.7UF/25V

Q20

ALI_+3VALWAYS

DS

NDS352AP

G

03/27

PN

Q26

DTC114EKA

E C

PWRBTN-11,30

PWRBTN-

+5VALWAYS

R259 100K

D19

1SS355

ON3_5

B

8

7

6

5

4

3

Q27

ALI_+5VALWAYS

DS

NDS352AP

G

03/27

PN

Q25

DTC114EKA

E C

Title

Size Document Number Re v

Date: Sheet

Elitegroup Computer Systems

M1535+(POWER+GPIO)

B

2

A531-1-4-01

V1.0

of

13 39Thursday, Augu st 28, 2003

1

Page 14

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

VCC5

IDERSTHDD7

HDD6

HDD5

HDD4

R326

5.6K

D D

IDEREQA10

IDEIOW-A10

IDEIOR-A10

ICHRDYA10

IDACK-A10

IDEIRQA10

IDESAA[0..2]10

IDECS-A010

C C

B B

IDESAA[0..2]

IDECS-B010

IDESAA2

IDESAA1

IDESAA0

IDESAB[0..2]10

R331 4.7K

RP31

33X4

IDESAB[0..2]

18

27

36

45

C322

47PF_R

R327 82

R237 22

R236 22

R328 82

SR220 22

R330 82

LED_HDD-30

HDA2

HIDECS0HDA1

HDA0

IDEIOW-B10

ICHRDYB10

IDEIRQB10

IDESAB2

IDESAB0

IDESAB1

HDA1

HDA0

VCC3

R329

10K

RP30

4 5

3 6

2 7

1 8

33X4

C323

47PF_R

SC271

47PF_R

ICHRDYA

VCC3

SC266

47PF_R

R346

10K

CIDECS0-

CDS2

CDS0

CDS1

C324

47PF_R

C328

47PF_R

C325

47PF_R

C326

47PF_R

HDD3

HDD2

HDD1

HDD0

HIDEREQ

HIDEIOWHIDEIORHICHRDY

HIDACKHIDEIRQ

CD_L32

CDGND32

R222 22

R348 82

R343 82

R342

4.7K

C320

0.1UF

CDGND

IDERST-

CDD7

CDD6

CDD5

CDD4

CDD3

CDD2

CDD1

CDD0

CDS1

CDS0

VCC5

C252

47PF_R

CIDEIOWCICHRDY

CIDEIRQ

CDCSEL

CSEL : "NC" ; "Hi" -->

Master(CDROM)/Slave(DVDROM)

VCC5

R279

Q23

PCIRST0-8,10

A A

S D

G

+3VAUX

10K

2N7002

IDERST-

SHIFT POWER LEVEL,

3.3V TO 5V

IDERST- 20

CSEL : "Low --> Slave(CDROM)/Master(DVDROM)

JP3

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

DT_91-00122-005_HDD44P

HDD

C253

47PF_R

SC294

0.1UF

CLOSE TO HDD

JP4

2

112

4

334

6

556

8

778

10

9910

12

111112

14

131314

16

151516

18

171718

20

191920

22

212122

24

232324

26

252526

28

272728

30

292930

32

313132

34

333334

36

353536

38

373738

40

393940

42

414142

44

434344

46

454546

48

474748

50

494950

SUYIN_80091A_050G1T_CDROMCONN

CDROM/DVDROM

VCC5

C319

+

100UF/10V-D

CLOSE TO CDROM/DVDROM

VCC5

SC293

2200PF

CDGND

CDD8

CDD9

CDD10

CDD11

CDD12

CDD13

CDD14

CDD15

CIDEREQ

CIDEIOR-

CIDACK-

CDS2

CIDECS1-

HDD8

HDD9

HDD10

HDD11

HDD12

HDD13

HDD14

HDD15

HIDECS1-

C321

47PF_R

+

R352 82

R221 22

R230 22

R247 33

C330

0.1UF

C332

2200PF

SR221 33

C327

SC267

47PF_R

47PF_R

C333

100UF/10V-D

IDEREQB

CD_R 32

C331

0.01UF

R332

100K_R

HDA2

R227

5.6K

IDEREQB 10

IDEIOR-B 10

IDACK-B 10

IDECS-B1 10

VCC5

IDEDA[0..15]

IDEDB[0..15]

CBLIDA 13

IDECS-A1 10

VCC5

C329

0.1UF

IDEDA[0..15] 10

IDEDB[0..15] 10

HDD15

HDD0

HDD14

HDD1

HDD9

HDD6

HDD8

HDD7

HDD11

HDD4

HDD10

HDD5

HDD13

HDD2

HDD12

HDD3

RP46

4 5

3 6

2 7

1 8

47X4

RP43

4 5

3 6

2 7

1 8

47X4

R325

10K_R

RP44

4 5

3 6

2 7

1 8

47X4

RP45

4 5

3 6

2 7

1 8

47X4

CLOSE TO HDD CONN.

IDEDB1

IDEDB14

IDEDB0

IDEDB15

IDEDB7

IDEDB8

IDEDB9

IDEDB10

CDD12

CDD5

CDD11

CDD6

CDD2

CDD13

CDD3

CDD4

SRP27

47X4

SRP30

47X4

SRP29

1 8

2 7

3 6

4 5

47X4

SRP28

1 8

2 7

3 6

4 5

47X4

45

36

27

18

45

36

27

18

CLOSE TO CDROM CONN.

IDEDA15

IDEDA0

IDEDA14

IDEDA1

IDEDA9

IDEDA6

IDEDA8

IDEDA7

IDEDA11

IDEDA4

IDEDA10

IDEDA5

IDEDA13

IDEDA2

IDEDA12

IDEDA3

CDD1

CDD14

CDD0

CDD15

CDD7

CDD8

CDD9

CDD10

SR272

10K_R

IDEDB12

IDEDB5

IDEDB11

IDEDB6

IDEDB2

IDEDB13

IDEDB3

IDEDB4

12/4

Elitegroup Computer Systems

Title

HDD & CDROM CONN.

Size Document Number Re v

8

7

6

5

4

3

B

Date: Sheet

2

A531-1-4-01

V1.0

of

14 39Thursday, Augu st 28, 2003

1

Page 15

8

www.kythuatvitinh.com

7

6

5

4

3

2

1

03/08

D D

C C

B B

A A

VCC5

SCN1

1 2

3 4

5 6

7 8

9 10

SW_5X2_2_54MM_R

xBUSY

C26680PF

xACK-

C25680PF

xAFD-

C13330PF

xSTB-

C12330PF

xSLCTIN-

C19

470PF/25V

470PF/25V

470PF/25V

470PF/25V

470PF/25V

470PF/25V

470PF/25V

470PF/25V

470PF/25V

VCC5 VCC5P

P N

XPD1

XPD0

XAFDXSTB-

XSLCT

XPE

XBUSY

XACK-

XPD3

XSLCTINXPD2

XINIT-

xPD7

xPD6

xPD5

xPD4

xERROR-

C14

C16

C18

C20

C21

C22

C23

C24

D2

1SS355

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 2

RP1

4.7KX4

RP4

4.7KX4

RP2

4.7KX4

RP3

4.7KX4

SR8

4.7K

xPD0

xPD1

xPD2

xPD3

xPD4

xPD5

xPD6

xPD7

12/2

DCDA- 12

RIA- 12

RXDA 12

RTSA- 12

TXDA 12

CTSA- 12

DTRA- 12

DSRA- 12

LPT[0..7]12

H6

CPU-HOLE104

1

H8

HOLE104

1

H1

HOLEC236D102-V8

2

3

4

5

1

H4

HOLEC315D102-V8

2

3

4

5

1

9

8

7

6

9

8

7

6

LPT[0..7]

H7

CPU-HOLE104

1

H5

HOLEC236D102-V8

2

3

4

5

1

H3

HOLEC236D102-V8

2

3

4

5

1

H2

HOLEC236D102-V8

2

3

4

5

1

9

8

7

6

9

8

7

6

9

8

7

6

LPT0

LPT1

LPT2

LPT3

LPT4

LPT5

LPT6

LPT7

H10

CPU-HOLE104

1

H15

HOLEC315D102-V8

2

3

4

5

1

H9

HOLEC315D102-V8

2

3

4

5

1

H16

HOLEC315D102-V8

2

3

4

5

1

STB-12

AFD-12

ERROR-12

INIT-12

SLCTIN-

SLCTIN-12

ACK-12

BUSY12

PE12

SLCT12

9

8

7

6

9

8

7

6

9

8

7

6

ACKBUSY

PE

SLCT

H11

CPU-HOLE104

1

H14

HOLEC315D102-V8

2

3

4

5

1

H12

HOLEC315D102-V8

2

3

4

5

1

H13

HOLEC315D102-V8

2

3

4

5

1

9

8

7

6

9

8

7

6

9

8

7

6

L6 FCM1608K-121

L7 FCM1608K-121

R21

R22

R6

R7

R8

R15

R16

R17

R18

R23

R24

R25

R26

R27

R28

xPD0

33

xERROR-

33

xPD1

33

xINIT-

33

xPD2

33

xSLCTIN-

33

xPD3

33

xPD4

33

xPD5

33

xPD6

33

xPD7

33

xACK-

33

xBUSY

33

xPE

33

xSLCT

33

C28

680PF

xSTBxAFD-

C15

680PF

C17

680PF

C27

680PF

P1

1

14

2

15

3

16

4

17

5

18

6

19

7

20

8

21

9

22

10

23

11

24

12

25

27

13

26

DT_91-00128-001_DSUB25P

Elitegroup Computer Systems

Title

Size Document Number Re v

8

7

6

5

4

3

B

Date: Sheet

COM & LPT PORT

A531-1-4-01

2

V1.0

of

15 39Thursday, Augu st 28, 2003

1

Page 16

8

www.kythuatvitinh.com

REFOSCI

SR190 0

ROMMD1

ROMMD5

ROMMA3

ROMMD4

D D

C C

B B

1.9V

BLM21P300S

A A

SC232

0.1UF

AVSS RSET

ROMMA3

REFOSCI

COMP

VREF

RSET

AVSS

AVSS

AVSS

AVSS

AVSS

AVSS

GND

SL21

SR189

R195

SR185

R196

A10

B10

B9

C9

A8

B8

C8

E9

E10

D8

E8

A7

B7

C7

A6

B5

C5

B3

A3

C4

H18

C1

B4

E6

D7

H20

H19

D3

ROMMA2

ROMMA3

ROMMA4