ELANT EL7571C Datasheet

EL7571C

Programmable PWM Controller

EL7571C

Features

• Pentium® II Compatible

• 5 bit DAC Controlled Output Voltage

• Greater than 90% Efficiency

• 4.5V to 12.6V Input Range

• Dual NMOS Power FET Drivers

• Fixed frequency, Current Mode

Control

• Adjustable Oscillator with External

Sync. Capability

• Synchronous Switching

• Internal Soft-Start

• User Adjustable Slope

Compensation

• Pulse by Pulse Current Limiting

• 1% Typical Output Accuracy

• Power Good Signal

• Output Power Down

• Over Voltage Protection

Applications

• Pentium® II Voltage Regulation

Modules (VRMs)

• PC Motherboards

• DC/DC Converters

• GTL Bus Termination

• Secondary Regulation

Ordering Information

Part No Temp. Range Package Outline #

EL7571C 0°C to +70°C 20-Pin SO MDP0027

General Description

The EL7571C is a flexible, high efficiency, current mode, PWM step

down controller. It incorporates five bit DAC adjustable output voltage

control which conforms to the Intel Voltage Regulation Module (VRM)

Specification for Pentium® II and Pentium® Pro class processors. The

controller employs synchronous rectification to deliver efficiencies

greater than 90% over a wide range of supply voltages and load conditions. The on-board oscillator frequency is externally adjustable, or may

be slaved to a system clock, allowing optimization of RFI performance in

critical applications. In single supply operation, the high side FET driver

supports boot-strapped operation. For maximum flexibility, system operation is possible from either a 5V rail, a single 12V rail, or dual supply

rails with the controller operating from 12V and the power FETs from

5V.

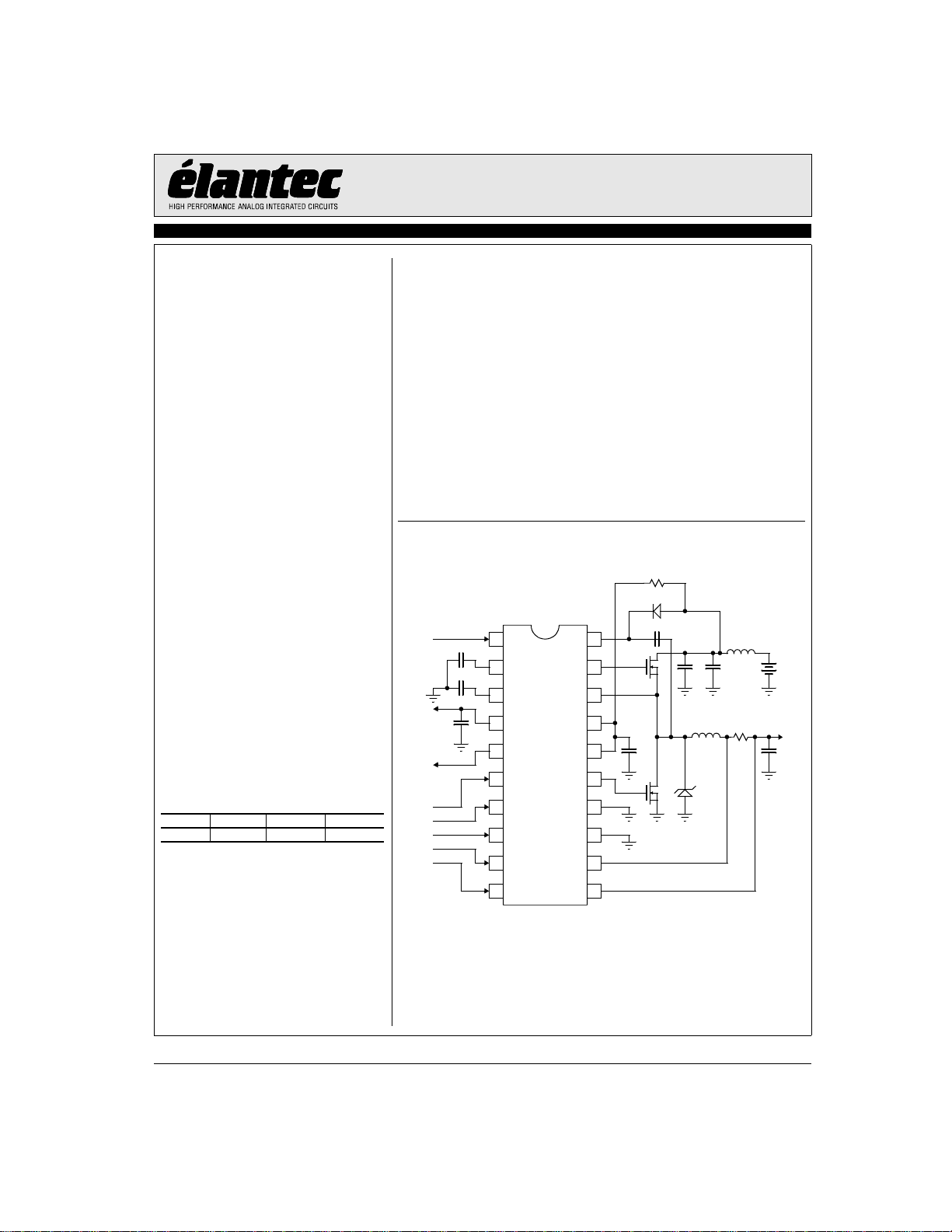

Connection Diagram

R2

5Ω

D1

ENABLE

1.4V

POWER

GOOD

Voltage

(VID

(0:4))

1

2

3

4

5

6

7

8

9

OTEN

CSLOPE

COSC

REF

PWRGD

VIDO

VID1

VID2

VID3

C3 240pF

C3 240pF

C3

0.1µF

I.D.

VH1

HSD

VIN

VINP

LSD

GNDP

GND

20

19

18

LX

17

16

15

14

13

12

CS

C6 0.1µF

Q1

C7

1µF

Q2 D2

1.5µH

C8

1µFC11000µF

x3

L1

5.1µH

L2

4.5V

to

12.6V

V

OUT

1.3V to

3.5V

R2

C2

5Ω

1000µF

x6

10

VID4

Q1, Q2: Siliconix, Si4410, x2

C1: Sanyo, 16MV 1000GX, 1000µF x3

C2: Sanyo, 6MV 1000GX, 1000µF x6

L1: Pulse Engineering, PE-53700, 5.1µH

L2: Micrometals, T30-26, 7T AWG #20, 1.5µH

R1: Dale, WSL-25-12, 15mΩ, x2

D1: BAV99

D2: IR, 32CTQ030

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a “controlled document”. Current revisions, if any, to these

specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

© 2001 Elantec Semiconductor, Inc.

11

FB

April 24, 2001

EL7571C

Programmable PWM Controller

EL7571C

Absolute Maximum Ratings (T

Supply Voltage: -0.5V to 14V

Input Pin Voltage: -.03 below Ground, +0.3 above Supply

VHI -0.5V to 27V

Storage Temperature Range: 65°C to +150°C

= 25°C)

A

Operating Temperature Range: 0°C to +70°C

Operating Junction Temperature: 125°C

Peak Output Current: 3A

Power Dissipation: SO20 500mW

Important Note:

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the

specified temperature and are pulsed tests, therefore: TJ = TC = TA.

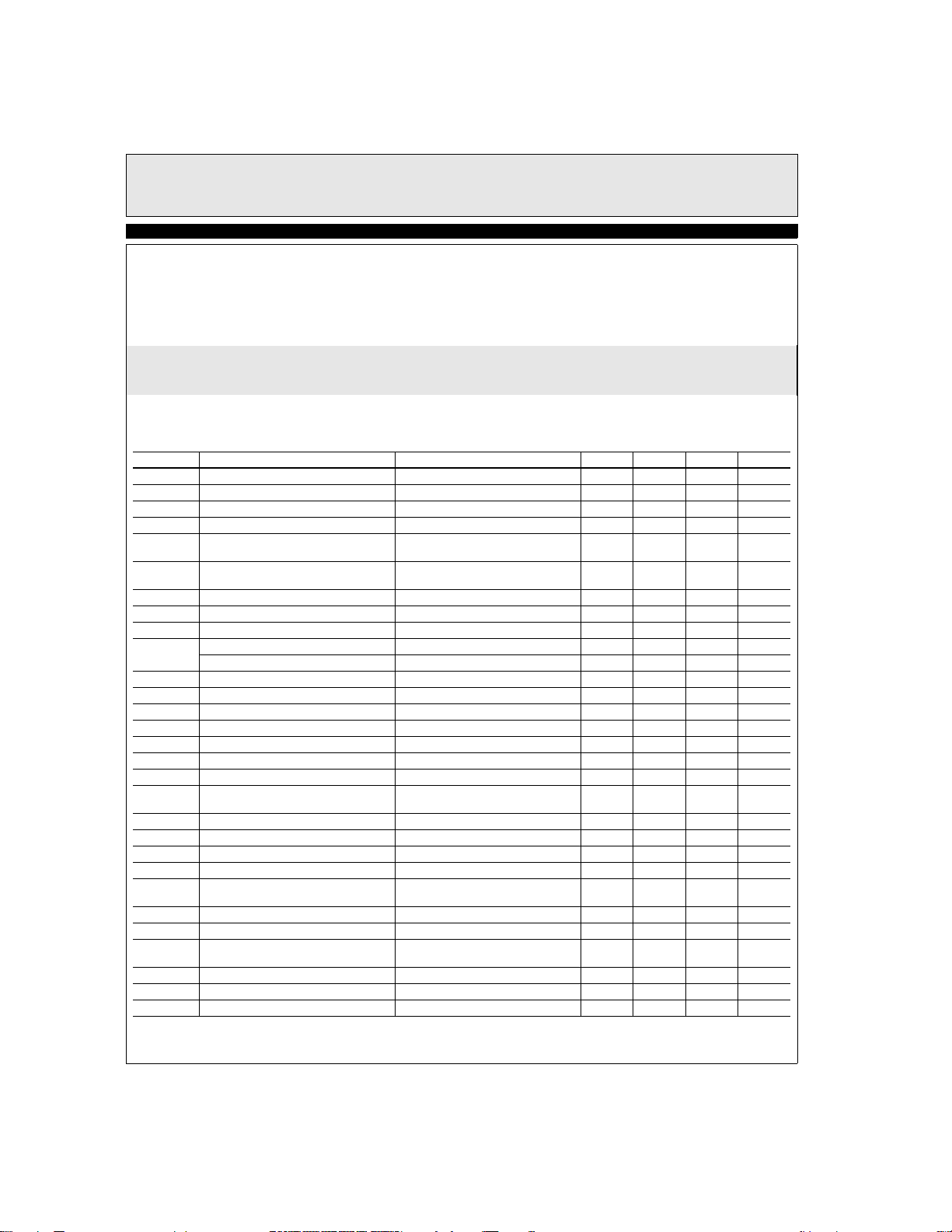

DC Electrical Characteristics

TA = 25°C, VIN = 5V, C

Parameter Description Condition Min Typ Max Unit

V

IN

V

UVLO HI

V

UVLO LO

V

OUT RANGE

V

OUT 1

V

OUT 2

V

REF

V

ILIM

V

IREV

V

OUT PG

V

OVP

V

OTEN LO

V

OTEN HI

V

ID LO

V

ID HI

V

OSC

V

PWRGD LO

R

DS ON

R

FB

R

CS

I

VIN

I

VIN DIS

I

SOURCE/SINK

I

RAMP

I

OSC CHARGE

I

OSC

DISCHARGE

I

REFMAX

I

VID

I

OTEN

= 330pF, C

OSC

SLOPE

= 390pF, R

= 7.5mΩ unless otherwise specified.

SENSE

Input Voltage Range 4.5 12.6 V

Input Under Voltage Lock out Upper Limit Positive going input voltage 3.6 4 4.4 V

Input Under Voltage Lock out Lower Limit Negative going input voltage 3.15 3.5 3.85 V

Output Voltage Range See VID table 1.3 3.5 V

Steady State Output Voltage Accuracy, VID =

10111

Steady State Output Voltage Accuracy, VID =

00101

IL = 6.5A, V

IL = 6.5A, V

= 2.8V 2.74 2.82 2.90 V

OUT

=1.8V 1.74 1.81 1.9 V

OUT

Reference Voltage 1.396 1.41 1.424 V

Current Limit Voltage V

Current Reversal Threshold V

Output Voltage Power Good Lower Level V

= (VCS-VFB) 125 154 185 mV

ILIM

= (VCS-VFB) -40 -5 20 mV

IREV

= 2.05V -18 -14 -10 %

OUT

Output Voltage Power Good Upper Level 8 12 16 %

Over-Voltage Protection Threshold +9 +13 +17 %

Power Down Input Low Level VIN = -10uA 1.5 V

Power Down Input High Level (VIN-1.5) V

Voltage I.D. Input Low Level 1.5 V

Voltage I.D. Input High Level (VIN-1.5) V

Oscillator Voltage Swing 0.85 V

Power Good Output Low Level I

HSD, LSD Switch On-Resistance VIN, V

= 1mA 0.5 V

OUT

INP

LX) = 12V

= 12V, I

= 100mA, (VHI-

OUT

4.8 6 Ω

FB Input Impedance 9.5 kΩ

CS Input Impedance 115 kΩ

Quiescent Supply Current V

Supply Current in Output Disable Mode V

Peak Driver Output Current VIN,V

C

Ramp Current High Side Switch Active 8.5 14 20 µA

SLOPE

Oscillator Charge Current 1.2>V

Oscillator Discharge Current 1.2>V

>(VIN-0.5)V 1.2 2 mA

OTEN

<1.5V 0.76 1 mA

OTEN

= 12V, Measured at HSD, LSD,

INP

(VHI-LX) = 12V

>0.35V 50 µA

OSC

>0.35V 2 mA

OSC

2.5 A

VREF Output Current 25 µA

VID Input Pull up Current 3 5 7 µA

OTEN Input Pull up Current 3 5 7 µA

P-P

2

EL7571C

Programmable PWM Controller

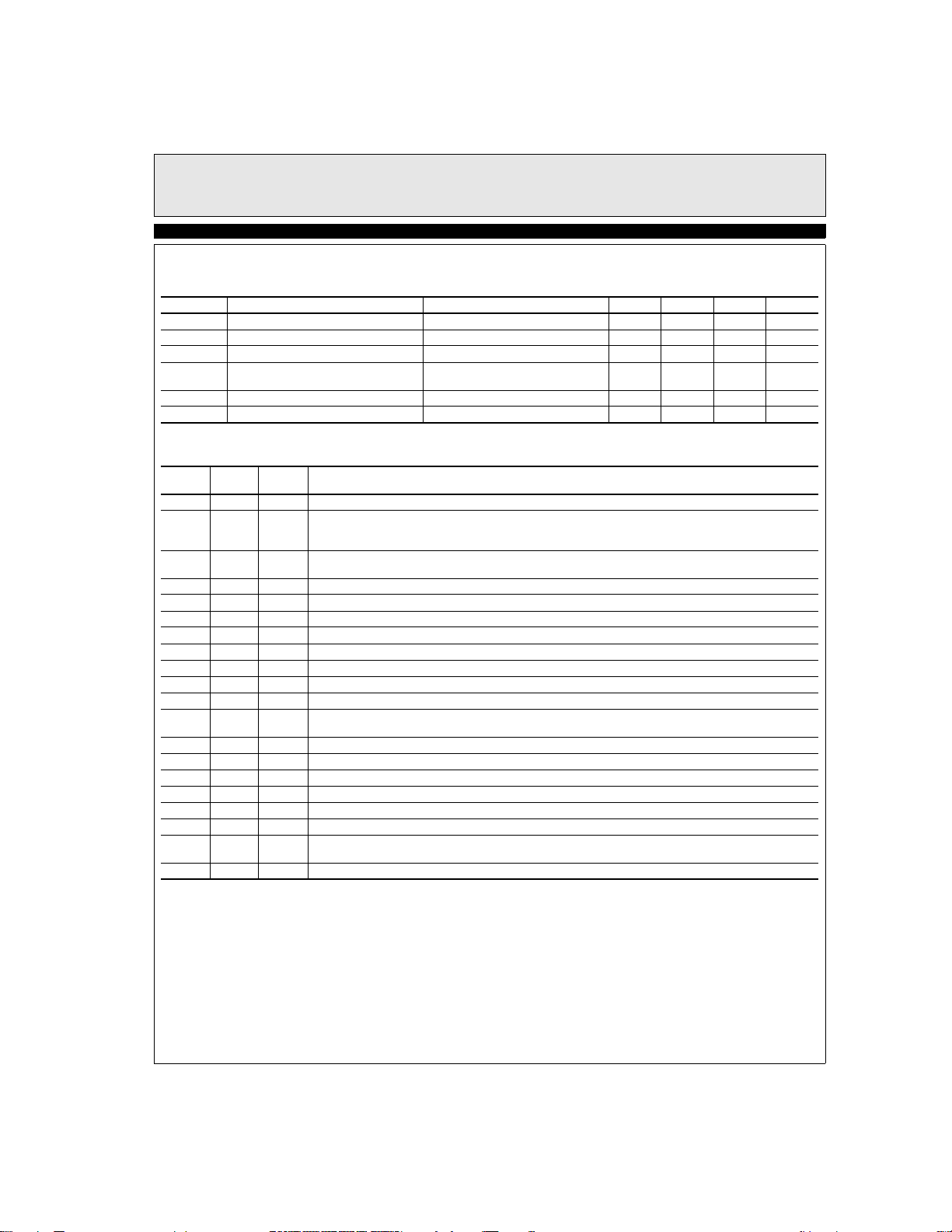

AC Electrical Characteristics

TA = 25°C, VIN = 5V, C

Parameter Description Conditions Min Typ Max Unit

f

OSC

f

CLK

t

OTEN

t

SYNC

T

START

D

MAX

Pin Descriptions

Pin No.

1. Pin designators: I = Input, O = Output, S = Supply

Pin

Name

1 OTEN I Chip enable input, internal pull up (5mA typical). Active high.

2 CSLOPE I With a capacitor attached from CSLOPE to GND, generates the voltage ramp compensation for the PWM current mode con-

3 COSC I Multi-function pin: with a timing capacitor attached, sets the internal oscillator rate fS (kHz) = 57/C

4 REF O Band gap reference output. Decouple to GND with 0.1uF.

5 PWRGD O Power good, open drain output. Set low whenever the output voltage is not within ±13% of the programmed value.

6 VID0 I Bit 0 of the output voltage select DAC. Internal pull up sets input high when not driven.

7 VID1 I Bit 1 of the output voltage select DAC. Internal pull up sets input high when not driven.

8 VID2 I Bit 2 of the output voltage select DAC. Internal pull up sets input high when not driven.

9 VID3 I Bit 3 of the output voltage select DAC. Internal pull up sets input high when not driven.

10 VID4 I Bit 4 of the output voltage select DAC. Internal pull up sets input high when not driven.

11 FB I Voltage regulation feedback input. Tie to V

12 CS I Current sense. Current feedback input of PWM controller and over current capacitor input. Current limit threshold set at

13 GND S Ground

14 GNDP S Power ground for low side FET driver. Tie to GND for normal operation.

15 LSD O Low side gate drive output.

16 VINP S Input supply voltage for low side FET driver. Tie to VIN for normal operation.

17 VIN S Input supply voltage for control unit.

18 LX S Negative supply input for high side FET driver.

19 HSD O High side gate drive output. Driver ground referenced to LX. Driver supply may be bootstrapped to enhance low controller

20 VH1 S Positive supply input for high side FET driver.

= 330pF, C

OSC

Nominal Oscillator Frequency C

Clock Frequency 50 500 1000 kHz

Shutdown Delay V

Oscillator Sync. Pulse Width Oscillator i/p (COSC) driven with HCMOS

Soft-start Period V

Maximum Duty Cycle 97 %

Pin

[1]

Type

= 390pF unless otherwise specified.

SLOPE

= 330pF 140 190 240 kHz

OSC

>1.5V 100 ns

OTEN

gate

= 3.5V 100/f

OUT

Function

troller. Slope rate is determined by an internal 14uA pull up and the C

the termination of the high side cycle.

low for a duration t

+154mV with respect to FB. Connect sense resistor between CS and FB for normal operation.

input voltage operation.

synchronizes device to an external clock.

SYNC

for normal operation.

OUT

20 800 ns

capacitor value. VC

SLOPE

CLK

SLOPE

OSC

is reset to ground at

(µF); when pulsed

EL7571C

us

3

EL7571C

Programmable PWM Controller

EL7571C

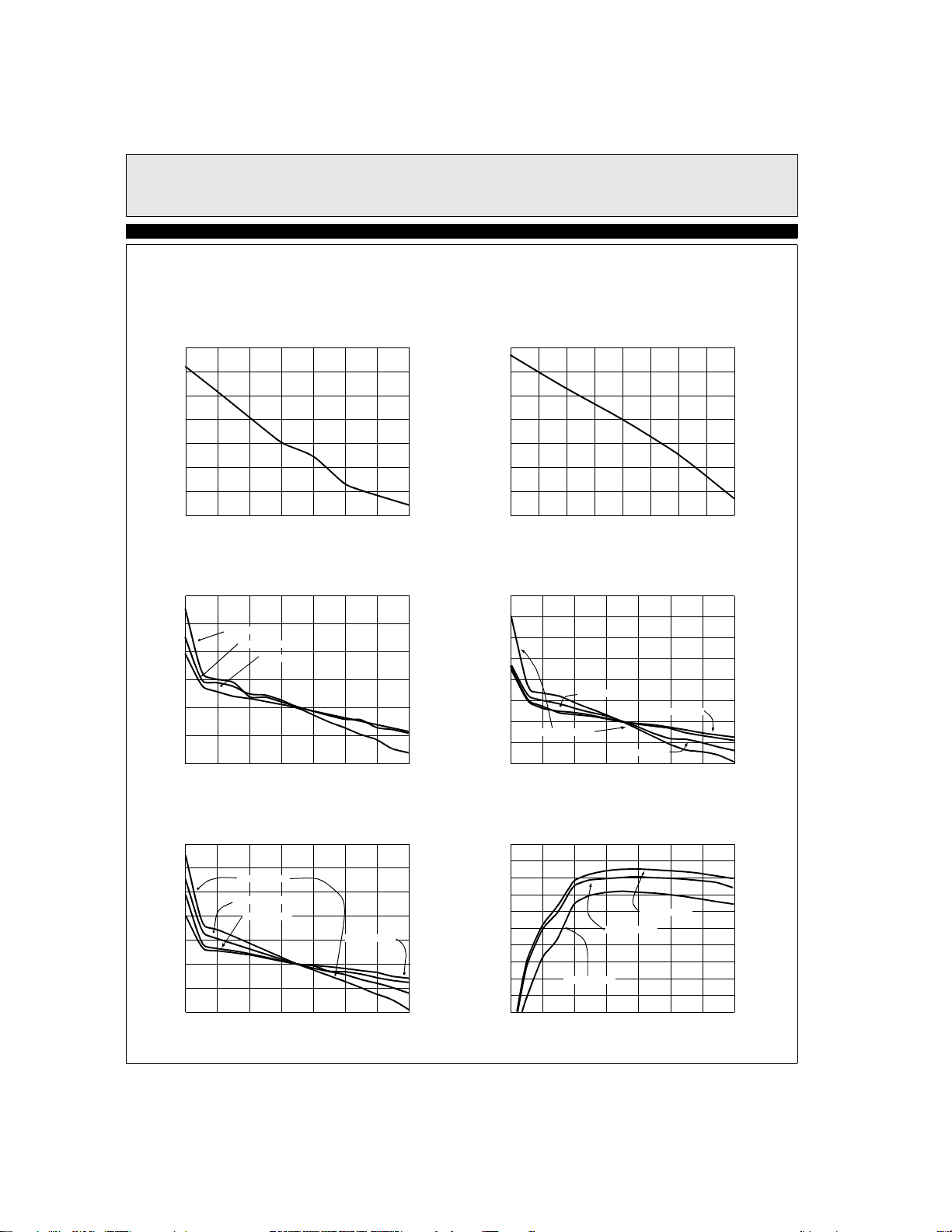

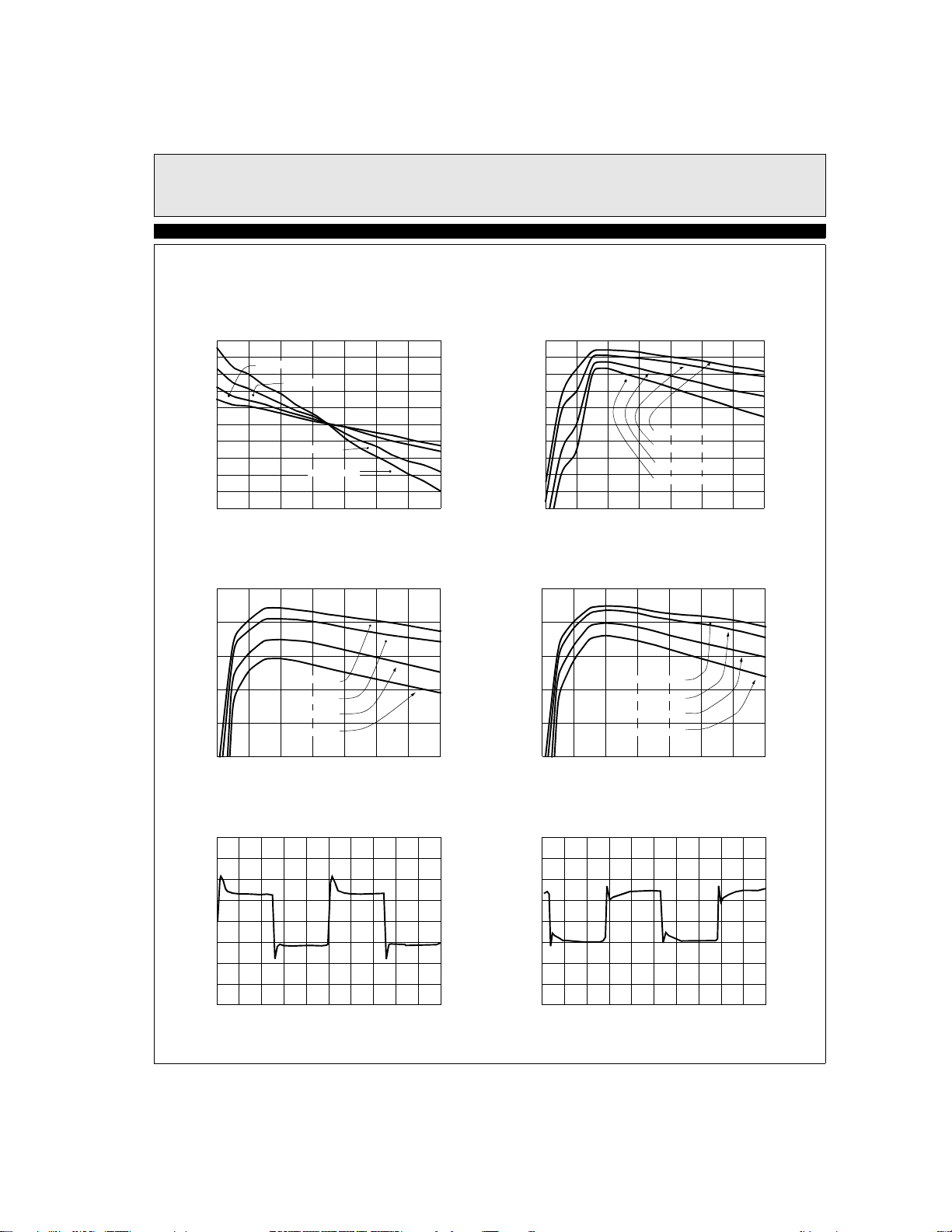

Typical Performance Curves

+12V Supply Sync Line Regulation

0.004

0.003

0.002

0.001

0

Line Regulation (%)

-0.001

-0.002

-0.003

13.5 10.011.5 11.0 10.513.0 12.5 12.0

+12V Supply Sync Load Regulation

0.04

0.03

0.02

0.01

0

Load Regulation (%)

-0.01

-0.02

V

= 1.8V

OUT

V

= 2.1V

OUT

V

0 1 3 5 11 1397

OUT

VIN (V)

= 2.8V

I

OUT

5V Supply Line Regulation

0.30

0.20

0.10

0.00

-0.10

Line Regulation (%)

-0.20

-0.30

-0.40

5.50 4.505.005.25 4.75

VRM +5V Supply +12V Controller Sync w/o

Schottky Load Regulation

6.00

5.00

4.00

3.00

2.00

1.00

Load Regulation (%)

0

V

-1.00

-2.00

(A)

OUT

0 1 3 5 11 1397

= 1.3V

VIN (V)

V

= 2.8V

OUT

V

= 3.5V

OUT

V

= 1.8V

OUT

I

(A)

OUT

+5V Supply Non-Sync Load Regulation

5.00

4.00

3.00

2.00

1.00

Load Regulation (%)

0

-1.00

-2.00

0 1 3 5 11 1397

V

= 1.3V

OUT

V

= 1.8V

OUT

V

= 2.8V

OUT

+12V Supply Sync Efficiency

1.0

0.9

0.8

V

= 3.5V

OUT

I

(A)

OUT

0.7

Efficiency (%)

0.6

0.5

0 1 3 5 11 1397

V

= 1.8V

OUT

V

= 3.5V

OUT

V

= 2.8V

OUT

I

(A)

OUT

4

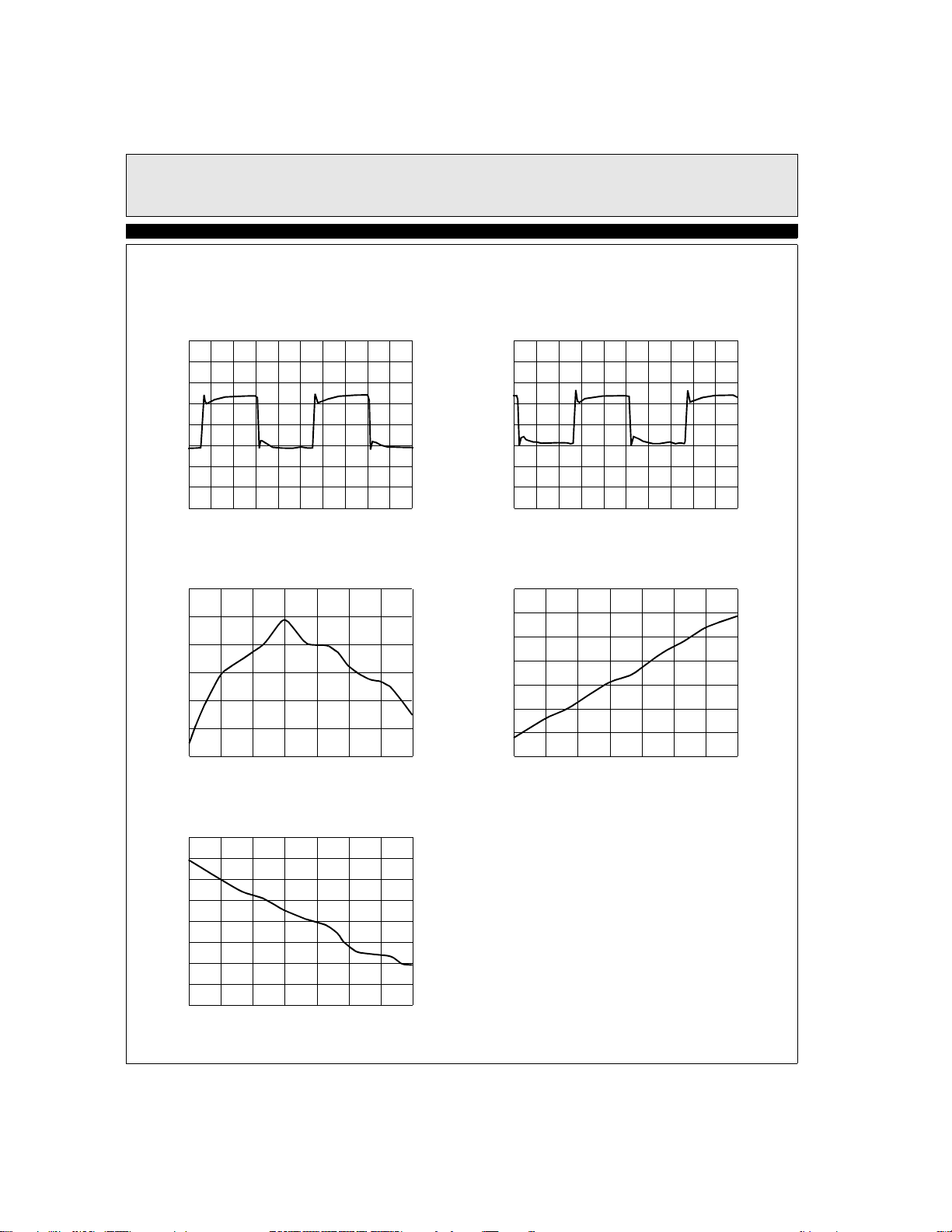

Typical Performance Curves

EL7571C

EL7571C

Programmable PWM Controller

+5V Supply Sync with Schottky Load

2.5

V

= 3.5V

1.5

0.5

0

-0.5

Load Regulation (%)

-1.5

-2.5

0

1.0

0.9

0.8

0.7

Efficiency (%)

0.6

0.5

0 1 3 5 11 1397 0 1 3 5 11 1397

OUT

V

= 2.8V

OUT

V

= 1.8V

OUT

V

= 1.3V

OUT

1 3 5 11 1397

I

(A)

OUT

+5V Supply Non-Sync VRM Efficiency

V

= 3.5V

OUT

V

= 2.8V

OUT

V

= 1.8V

OUT

V

= 1.3V

OUT

I

(A)

OUT

+5V Supply +12V Controller Sync w/o Schottky

VRM Efficiency

1.0

0.9

0.8

0.7

Efficiency (X)

0.6

0.5

0.02

1.02 3.04 5.04 11.04 13.049.047.04

+5V Supply Sync with Schottky VRM Efficiency

1.0

0.9

0.8

0.7

Efficiency (%)

0.6

0.5

V

= 3.5V

OUT

V

= 1.8V

OUT

V

= 2.8V

OUT

V

= 1.3V

OUT

I

(A)

OUT

V

= 3.5V

OUT

V

= 2.8V

OUT

V

= 1.8V

OUT

V

= 1.3V

OUT

I

(A)

OUT

12V Transient Response

1

5V Non-sync Transient Response

1

5

EL7571C

Programmable PWM Controller

EL7571C

Typical Performance Curves

5V Sync Transient Response

1

Efficiency vs Temperature

92.6

92.5

92.4

92.2

Efficiency (%)

92.0

91.8

91.6

-45 6015 30 45-30 -15 0

Temperature (°C)

5V Input 12V Controller Transient Response

1

V

vs Temperature

REF

1.425

1.420

1.415

1.410

(V)

REF

1.405

V

1.400

1.395

1.390

-45 6015 30 45-30 -15 0

Temperature (°C)

Frequency vs Temperature

280

270

260

250

240

230

Frequency (KHz)

220

210

200

-45 6015 30 45-30 -15 0

Temperature (°C)

6

Applications Information

Circuit Description

EL7571C

EL7571C

Programmable PWM Controller

General

The EL7571C is a fixed frequency, current mode, pulse

width modulated (PWM) controller with an integrated

high precision reference and a 5 bit Digital-to-Analog

Converter (DAC). The device incorporates all the active

circuitry required to implement a synchronous step

down (buck) converter which conforms to the Intel Pentium® II VRM specification. Complementary switching

outputs are provided to drive dual NMOS power FET’s

in either synchronous or non-synchronous configurations, enabling the user to realize a variety of high

efficiency and low cost converters.

Reference

A precision, temperature compensated band gap reference forms the basis of the EL7571C. The reference is

trimmed during manufacturing and provides 1% set

point accuracy for the overall regulator. AC rejection of

the reference is optimized using an external bypass

capacitor C

REF

.

Main Loop

A current mode PWM control loop is implemented in

the EL7571C (see block diagram). This configuration

employs dual feedback loops which provide both output

voltage and current feedback to the controller. The

resulting system offers several advantages over tradititional voltage control systems, including simpler loop

design, pulse by pulse current limiting, rapid response to

line variaion and good load step response. Current feedback is performed by sensing voltage across an external

shunt resistor. Selection of the shunt resistance value

sets the level of current feedback and thereby the load

regulation and current limit levels. Consequently, operation over a wide range of output currents is possible. The

reference output is fed to a 5 bit DAC with step weighing conforming to the Intel VRM Specification. Each

DAC input includes an internal current pull up which

directly interfaces to the VID output of a Pentium® II

class microprocessor. The heart of the controller is a triple-input direct summing differential comparator, which

sums voltage feedback, current feedback and compen-

sating ramp signals together. The relative gains of the

comparator input stages are weighed. The ratio of voltage feedback to current feedback to compensating ramp

defines the load regulation and open loop voltage gain

for the system, respectively. The compensating ramp is

required to maintain large system signal system stability

for PWM duty cycles greater than 50%. Compensation

ramp amplitude is user adjustable and is set with a single

external capacitor (CSLOPE). The ramp voltage is

ground referenced and is reset to ground whenever the

high side drive signal is low. In operation, the DAC output voltage is compared to the regulator output, which

has been internally attenuated. The resulting error voltage is compared with the compensating ramp and

current feedback voltage. PWM duty cycle is adjusted

by the comparator output such that the combined comparator input sums to zero. A weighted comparator

scheme enhances system operation over traditional voltage error amplifier loops by providing cycle-by-cycle

adjustment of the PWM output voltage, eliminating the

need for error amplifier compensation. The dominant

pole in the loop is defined by the output capacitance and

equivalent load resistance, the effect of the output inductor having been canceled due to the current feedback. An

output enable (OUTEN) input allows the regulator output to be disabled by an external logic control signal.

Auxiliary Comparators

The current feedback signal is monitored by two additional comparators which set the operating limits for the

main inductor current. An over current comparator terminates the PWM cycle independently of the main

summing comparator output whenever the voltage

across the sense resistor exceeds 154mV. For a 7.5mΩ

resistor this corresponds to a nominal 20A current limit.

Since output current is continuously monitored, cycleby-cycle current limiting results. A second comparator

senses inductor current reverse flow. The low side drive

signal is terminated when the sense resistor voltage is

less than -5mV, corresponding to a nominal reverse cur-

rent of -0.67A, for a 7.5mΩ sense resistor. Additionally,

under fault conditions, with the regulator output over-

7

Loading...

Loading...