ELANT EL7562CU Datasheet

(3.3V,

EL7562C - Preliminary

Monolithic 2 Amp DC:DC Step-down Regulator

EL7562C - Preliminary

Features

• Integrated synchronous MOSFETs

and current mode controller

• 2A continuous output current

• Up to 95% efficiency

• 4.5V to 5.5V input voltage

• Adjustable output from 1V to 3.8V

• Cycle-by-cycle current limit

• Precision reference

• ±0.5% load and line regulation

• Adjustable switching frequency to

1MHz

• Oscillator synchronization

possible

• Internal soft start

• Over temperature protection

• Under voltage lockout

• 16-pin QSOP package

Applications

• DSP, CPU Core and IO Supplies

• Logic/Bus Supplies

• Portable Equipment

• DC:DC Converter Modules

• GTL + Bus Power Supply

Ordering Information

Part No Package Tape & Reel Outline #

EL7562CU 16-Pin QSOP - MDP0040

General Description

The EL7562C is an integrated, synchronous step-down regulator with

output voltage adjustable from 1.0V to 3.8V. It is capable of delivering

2A continuous current at up to 95% efficiency. The EL7562C operates

at a constant frequency pulse width modulation (PWM) mode, making

external synchronization possible. Patented on-chip resistorless current sensing enables current mode control, which provides cycle-bycycle current limiting, over-current protection, and excellent step load

response. The EL7562C is available in a fused-lead 16-pin QSOP

package. With proper external components, the whole converter fits

into a less than 0.5 in2 area. The minimal external components and

small size make this EL7562C ideal for desktop and portable

applications.

The EL7562C is specified for operation over the -40°C to +85°C temperature range.

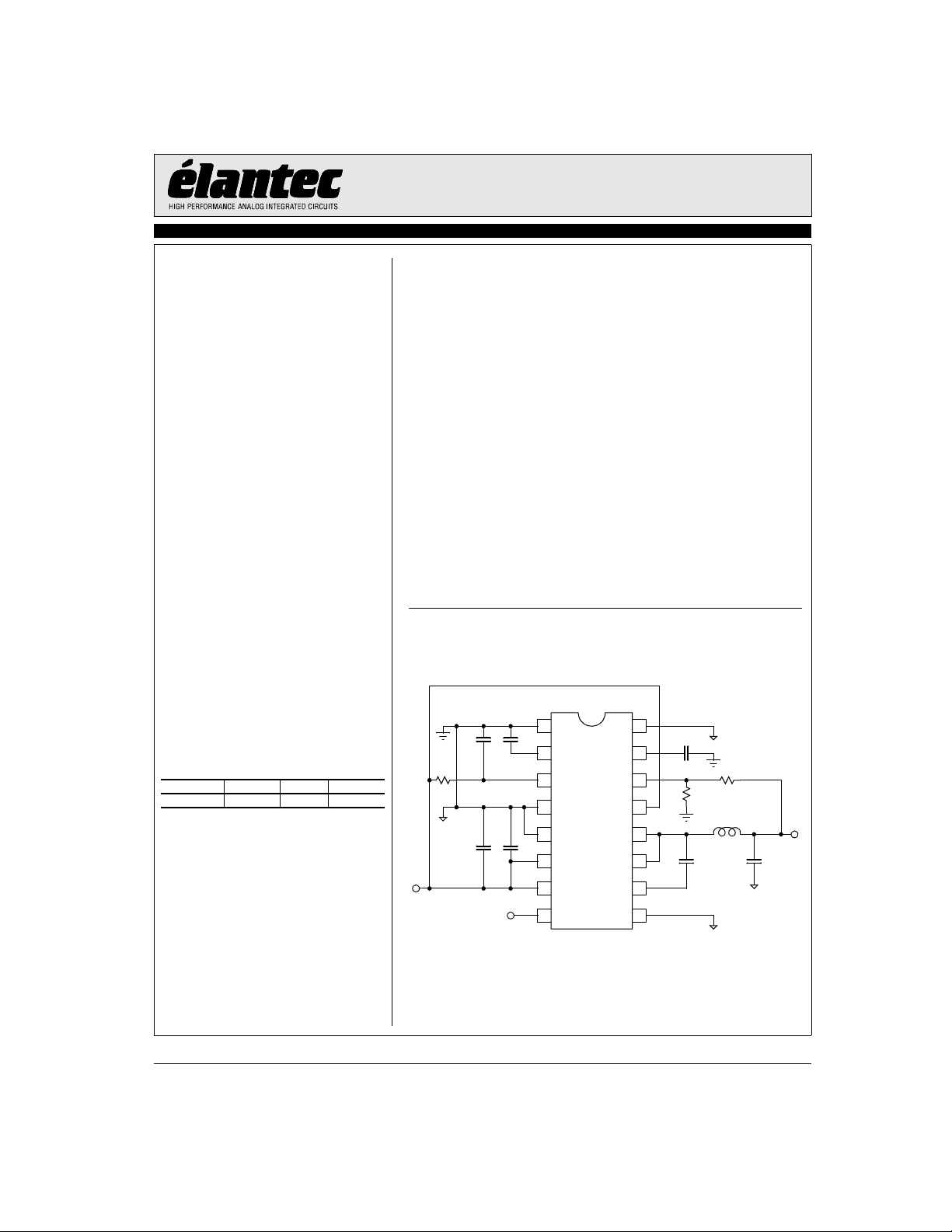

Typical Application Diagram

V

5.5V)

1

C3C

4

0.1µF 270pF

R

3

39Ω

C1C

2

100µF 0.1µF

IN

SGND

2

COSC

3

VDD

4

PGND

5

PGND

6

VIN

7

VIN

8 9

EN

PGND

VREF

VDRV

VHI

PGND

16

15

14

FB

13

12

LX

11

LX

10

C

0.1µF

5

R

1

1kΩ

C

6

0.1µF

R

2.37k

L

4.7µF

2

1

C

7

100µF

2A)

V

O

October 25, 2001

Manufactured under U.S. Patent No. 57,323,974

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a “controlled document”. Current revisions, if any, to these

specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

© 2001 Elantec Semiconductor, Inc.

EL7562C - Preliminary

Monolithic 2 Amp DC:DC Step-down Regulator

Absolute Maximum Ratings (T

Supply Voltage between VIN or VDD and GND +6.5V

VLX Voltage VIN +0.3V

Input Voltage GND -0.3V, VDD +0.3V

VHI Voltage GND -0.3V, V

EL7562C - Preliminary

= 25°C)

A

LX

Storage Temperature -65°C to +150°C

Operating Ambient Temperature -40°C to +85°C

Operating Junction Temperature +135°C

+6V

Important Note:

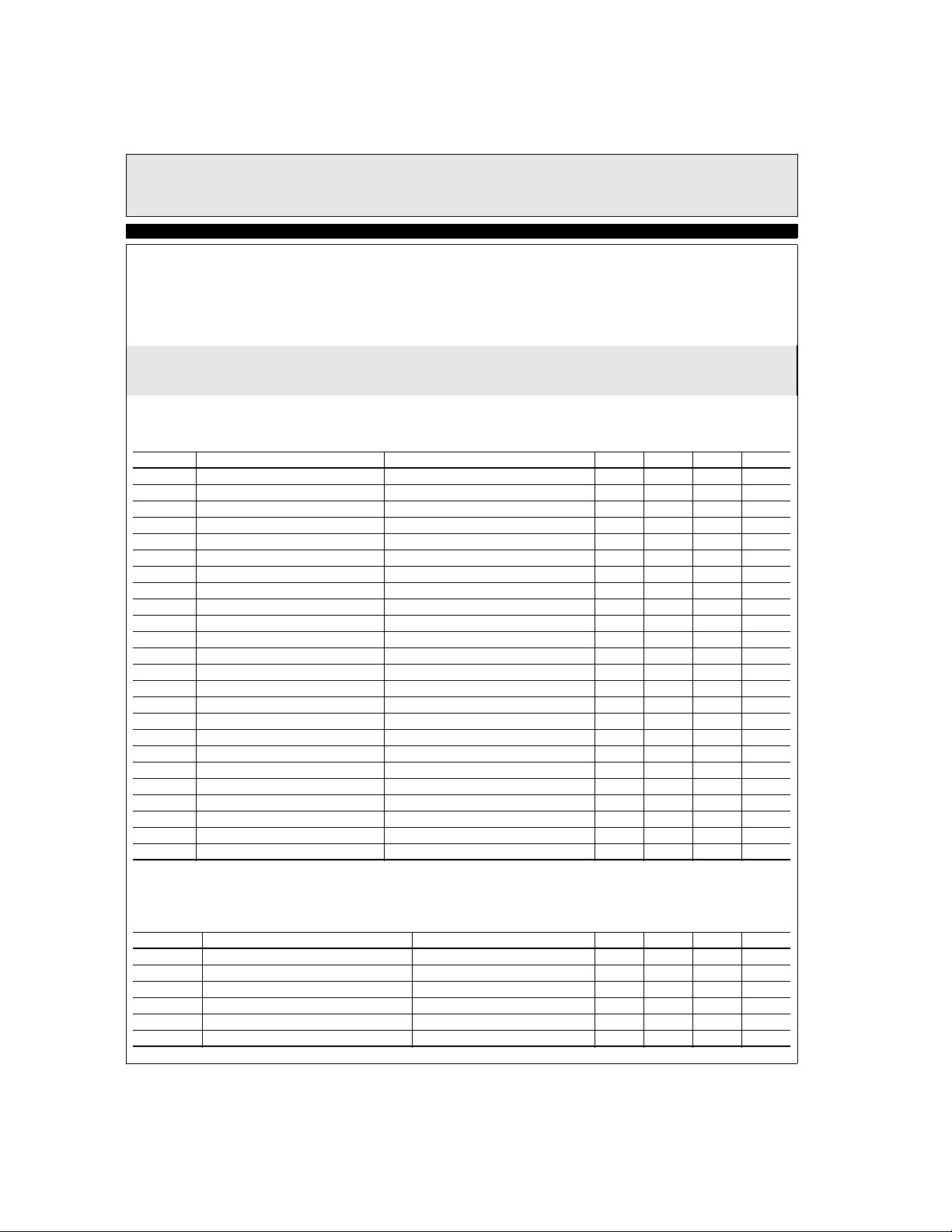

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the

specified temperature and are pulsed tests, therefore: TJ = TC = TA.

DC Characteristics

V

= V

= 5V, TA = TJ = 25°C, C

DD

IN

Parameter Description Conditions Min Typ Max Unit

V

REF

V

REFTC

V

REFLOAD

V

RAMP

I

OSC_CHG

I

OSC_DIS

I

VDD+VDRVVDD+VDRV

I

VDD_OFF

V

DD_OFF

V

DD_ON

T

OT

T

HYS

I

LEAK

I

LMAX

R

DSON

R

DSONTC

V

FB

V

FB_LINE

V

FB_LOAD

V

FB_TC

I

FB

V

EN_HI

V

EN_LO

I

EN

Reference Accuracy 1.24 1.26 1.28 V

Reference Temperature Coefficient 50 ppm/°C

Reference Load Regulation 0 < I

Oscillator Ramp Amplitude 1.15 V

Oscillator Charge Current 0.1V < V

Oscillator Discharge Current 0.1V < V

Supply Current VEN = 4V, F

V

Standby Current EN = 0 1 1.5 mA

DD

VDD for Shutdown 3.5 3.9 V

VDD for Startup 3.95 4.35 V

Over Temperature Threshold 135 °C

Over Temperature Hysteresis 20 °C

Internal FET Leakage Current EN = 0, LX = 5V (low FET), LX = 0V (high FET) 10 µA

Peak Current Limit 3 A

FET On Resistance Wafer level test only 60 120 mΩ

R

Tempco 0.2 mΩ/°C

DSON

Output Initial Accuracy I

Output Line Regulation V

Output Load Regulation 0.1A < I

Output Temperature Stability -40°C < TA < 85°C, I

Feedback Input Pull Up Current V

EN Input High Level 3.2 4 V

EN Input Low Level 1 V

Enable Pull Up Current VEN = 0 -4 -2.5 µA

= 1.2nF, unless otherwise specified.

OSC

LOAD

IN

FB

< 50µA -1 %

REF

< 1.25V 200 µA

OSC

< 1.25V 8 mA

OSC

= 120kHz 2 3.5 5 mA

OSC

= 0A 0.960 0.975 0.99 V

= 5V, ∆V

= 10%, I

IN

< 1A 0.5 %

LOAD

= 0A 0.5 %

LOAD

= 0.5A ±1 %

LOAD

= 0V 100 200 nA

Closed Loop AC Electrical Characteristics

VS = V

= 5V, TA = TJ = 25°C, C

IN

Parameter Description Conditions Min Typ Max Unit

F

OSC

t

SYNC

M

t

BRM

t

LEB

D

SS

MAX

Oscillator Initial Accuracy 105 117 130 kHz

Minimum Oscillator Sync Width 25 ns

Soft Start Slope 0.5 V/ms

FET Break Before Make Delay 15 ns

High Side FET Minimum On Time 150 ns

Maximum Duty Cycle 95 %

= 1.2nF, unless otherwise specified.

OSC

2

EL7562C - Preliminary

Monolithic 2 Amp DC:DC Step-down Regulator

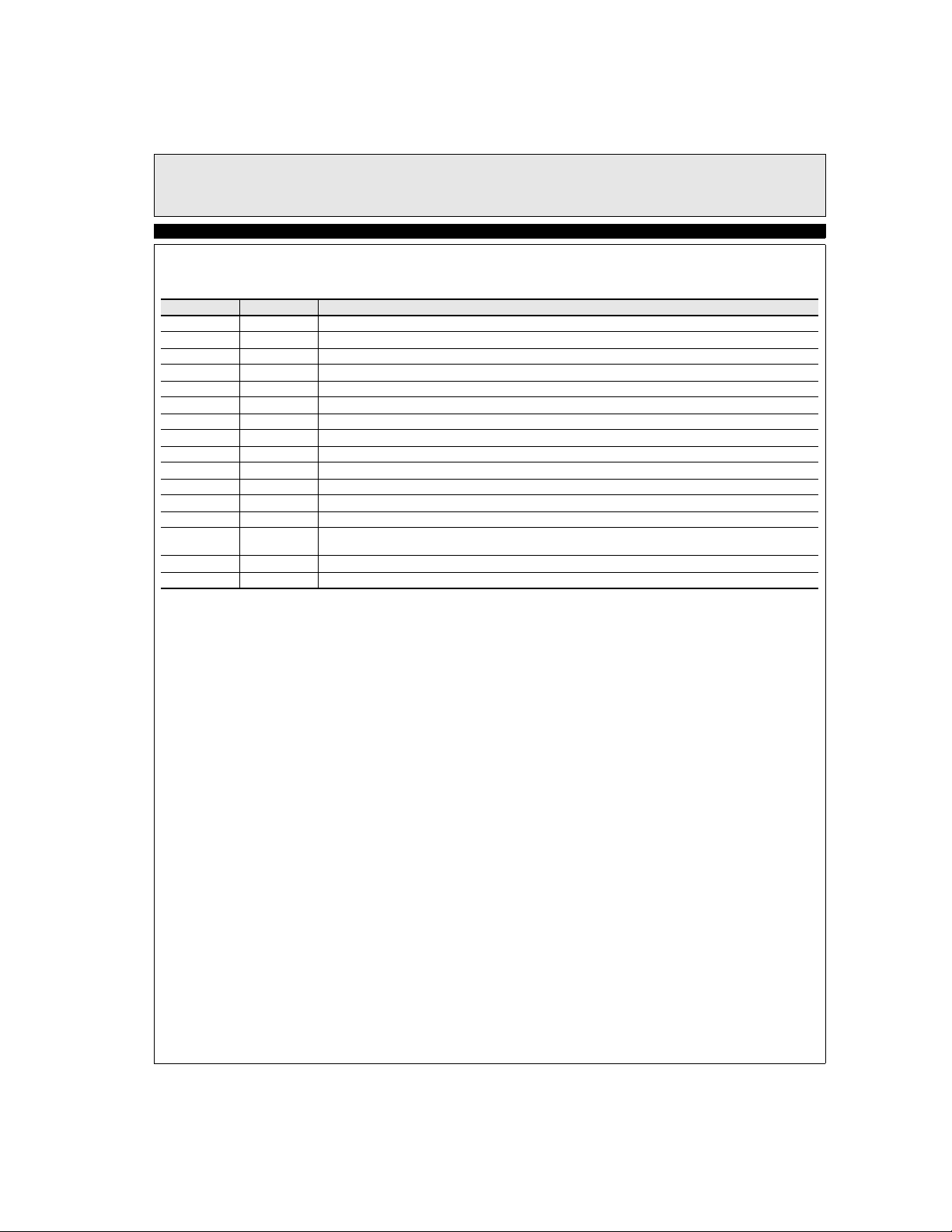

Pin Descriptions

Pin Number Pin Name Pin Function

1 SGND Control circuit negative supply.

2 COSC Oscillator timing capacitor. FOSC can be approximated by: FOSC (kHz) = 0.1843/COSC, COSC in µF.

3 VDD Control circuit positive supply.

4 PGND Ground return of the regulator. Connected to the source of the low-side synchronous NMOS power FET.

5 PGND Ground return of the regulator. Connected to the source of the low-side synchronous NMOS power FET.

6 VIN Power supply input of the regulator. Connected to the drain of the high-side NMOS power FET.

7 VIN Power supply input of the regulator. Connected to the drain of the high-side NMOS power FET.

8 EN Chip Enable, active high. A 2µA internal pull-up current enables the device if the pin is left open.

9 PGND Ground return of the regulator.

10 VHI Positive supply of the high-side driver.

11 LX Inductor drive pin. High current digital output whose average voltage equals the regulator output voltage.

12 LX Inductor drive pin. High current digital output whose average voltage equals the regulator output voltage.

13 VDRV Positive supply of the low-side driver and input voltage for the high-side boot strap.

14 FB Voltage feedback input. Connected to an external resistor divider between VOUT and GND. A 125nA pull-up current

15 VREF Bandgap reference bypass capacitor. Typically 0.1µF to GND.

16 PGND Ground return of the regulator.

forces VOUT to VS in the event that FB is floating.

EL7562C - Preliminary

3

Loading...

Loading...