ELANT EL5825CU, EL5825CR Datasheet

C

EL5825C - Preliminary

8-Channel TFT-LCD Reference Voltage Generator

EL5825C - Preliminary

Features

• 8-channel refere n ce ou tputs

• Accuracy of ±0.1%

• Supply voltage of 5V to 16V

• Digital supply 3.3V to 5V

• Low supply current of 10mA

• Rail-to-rail capability

Applications

• TFT-LCD drive circuits

• Reference voltage generators

Ordering Information

Part No Package Tape & Reel Outline #

EL5825CU 24-Pin LPP - MDP0046 EL5825CR 24-Pin TSSOP - MDP0044

General Description

The EL5825C is designed to produce the reference voltages required

in TFT-LCD applications. Each output is programmed to the required

voltage with 10 bits of resolution. Reference pins determine the high

and low voltages of the output range, which are capable of swinging to

either supply rail. Pr og ramm in g of each ou tp ut is per fo rmed usin g the

serial interface. A serial out pin enables daisy chaining of multiple

devices.

A number of the EL5825C can be stacked for applications requiring

more than 8 outputs. The reference inputs can be tied to th e rails,

enabling each part to output the full voltage range, or alternatively,

they can be connected to external resistors to split the output range and

enable finer resolutions of the outputs.

The EL5825C has 8 ou tputs and is avail able in both the 24-pin TSSO P

and the 24-pin LPP packages. It is specified for operation over the full

-40°C to +85°C temperature range.

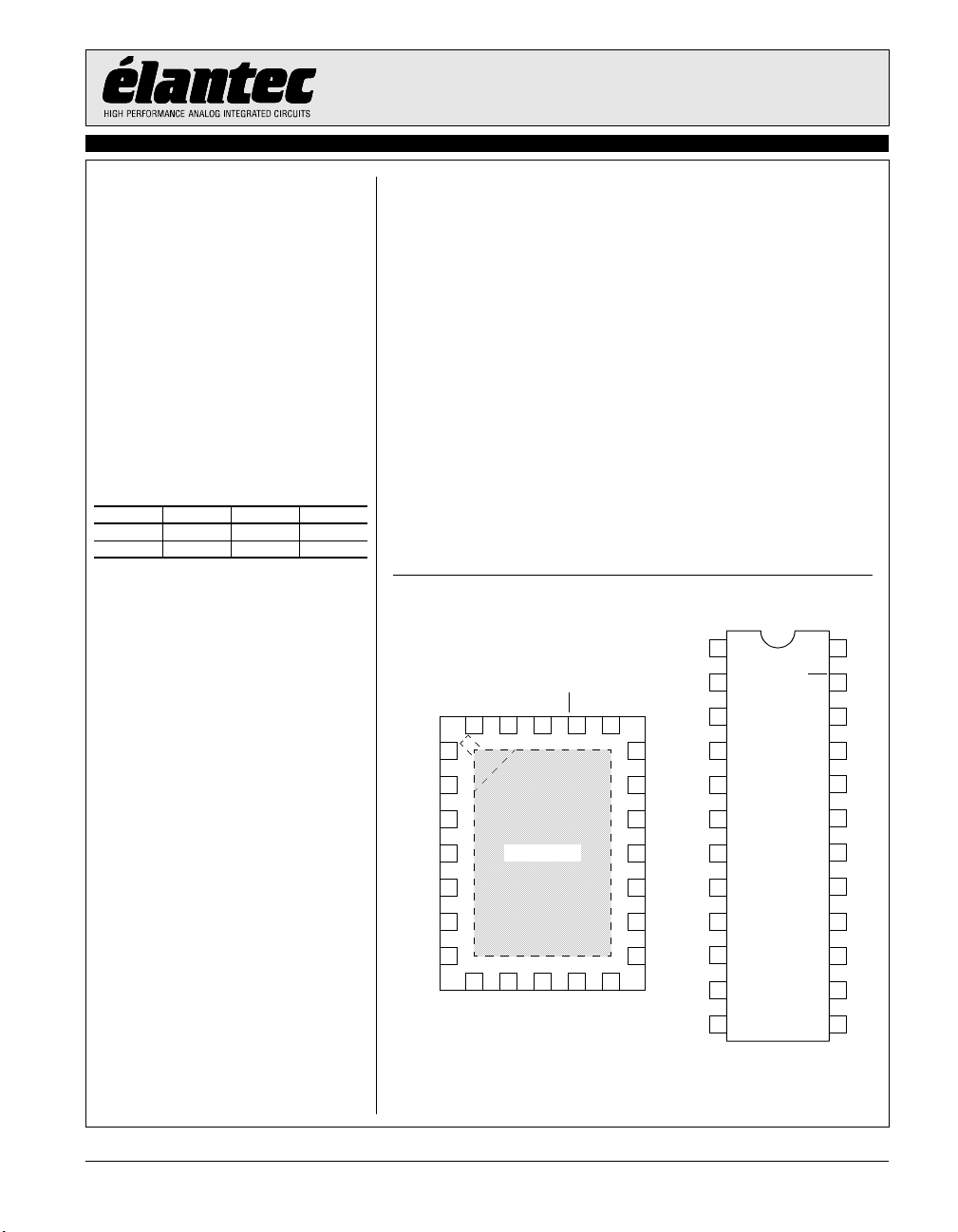

onnection Diagram

SCLK SD1

OSC

1

SDO ENA

2

SDO

SCLK

SDI

ENA

24

23

22

1

OUTA

21

20

OUTB

19

OSC OUT A

3

VSD OUT B

4

24

23

22

21

VSD

2

3

4

VS

5

REFH

6

REFL

7

GND

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a “controlled document”. Current revisions, if any, to these

specifications are maintained at the factory and are available upon your request . W e recommend checking the revision level befo re finalization of your design documentation.

© 2001 Elantec Semiconductor, Inc.

Thermal Pad

8

9

10

BCHOLD

24-Pin LPP Top View

11

OUTC

18

17

OUTD

16

GND

15

OUTE

14

OUTF

13

OUTG

12

OUTH

NC OUT C

5

VS OUT D

6

REFH GND

7

REFL OUT E

8

GND OUT F

9

NC OUT G

10

BG HOLD OUT H

11

NC NC

12

24-Pin TSSOP

20

19

18

17

16

15

14

13

October 4, 2001

EL5825C - Preliminary

8-Channel TFT-LCD Reference Voltage Generator

Absolute Maximum Ratings (T

Values beyond absolute maximum ratings can cause the device to be prematurely damaged. Absolute maximum ratings are stress ratings only and

functional device operation is not implied.

Supply Voltage between V

EL5825C - Preliminary

Supply Voltage between V

Maximum Continuous Output Current 30mA

and GND +18V

S

and GND VS and +7V (min)

SD

= 25°C)

A

Maximum Die Temperature +125°C

Storage Temperature -65°C to +150°C

Operating Temperature -40°C to +85°C

Lead Temperature 260°C

Power Dissipation See Curves

ESD Voltage 2kV

Important Note:

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the

specified temperature and are pulsed tests, therefore: T

= TC = TA.

J

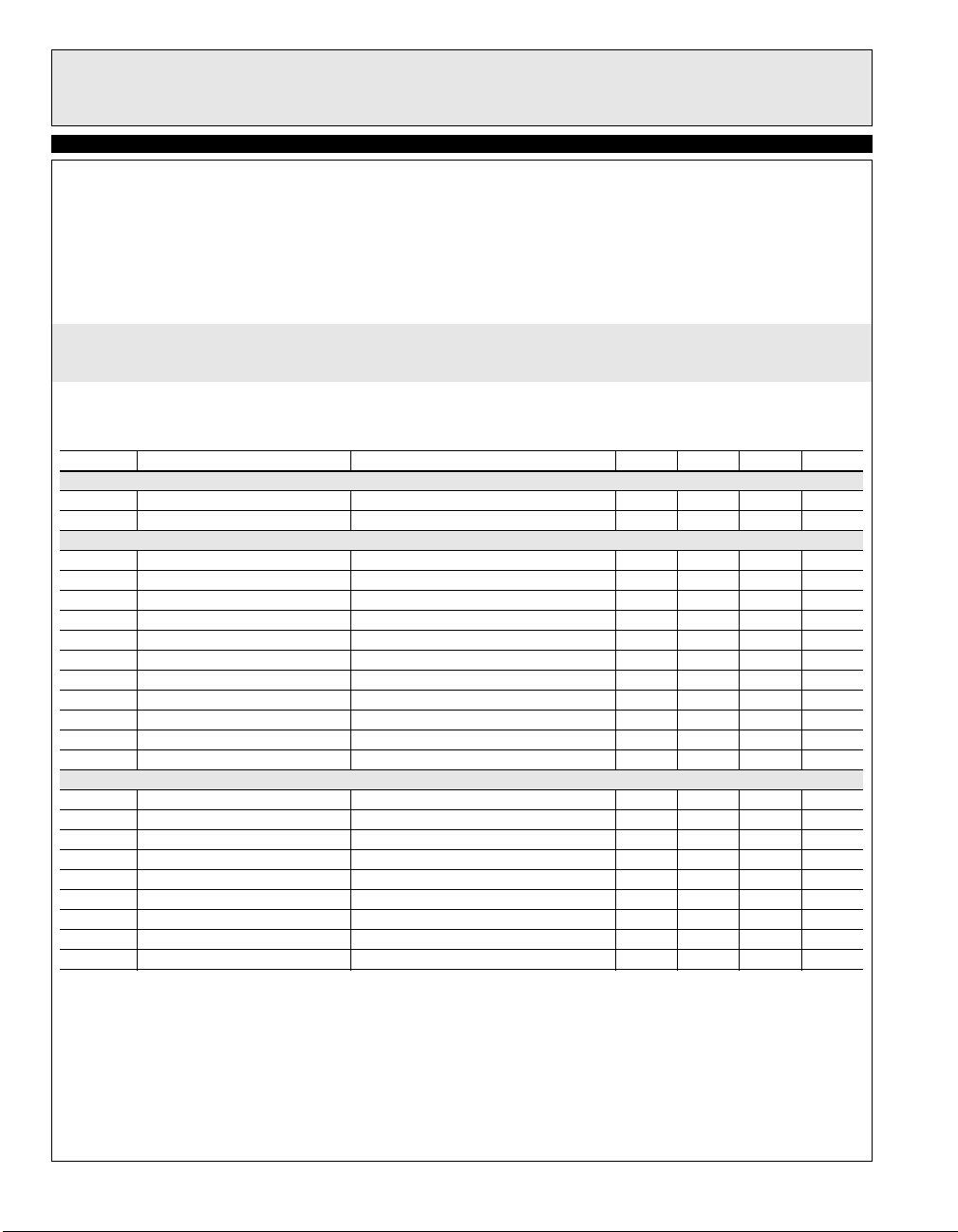

Electrical Characteristics

VS = 15V, VSD = 5V, V

Parameter Description Condition Min Typ Max Unit

Supply

I

S

I

SD

Supply Current No load 10 TBD mA

Digital Supply Current 1mA

Analog

V

OL

V

OH

I

SC

Output Swing Low RL = 1.5kΩ to 7.5V, after 1mS 100 200 mV Output Swing High RL = 1.5kΩ to 7.5V, after 1mS 14.75 14.9 V

Short Circuit Current RL = 10Ω 100 mA

PSRR Power Supply Rejection Ratio V

V

OS

t

D

V

AC

V

DROOP

R

INH

R

INL

Offset Voltage V

Program to Out Delay TBD mS

Accuracy TBD 12 mV

Droop Voltage TBD 15 mV/mS

Input Resistance @ VREFH V

Input Resistance @ VREFL V

REG Load Regulation I

Digital

V

V

F

t

t

t

t

t

R

IH

IL

CLK

S

H

LC

CE

DCO

SDIN

Logic 1 Input Voltage VSD-20% V Logic 0 Input Voltage 20%*V Clock Frequency 5MHz Setup Time 10 ns Hold Time 10 ns Load to Clock Time 10 ns Clock to Load Line 10 ns Clock to Out Delay Time ns S

= 13V, V

REFH

Input Resistance 1GΩ

DIN

= 2V, RL = 1.5kΩ and CL = 200pF to 0V, TA = 25°C unless otherwise specified.

REFL

+ is moved from 14V to 16V TBD TBD dB

S

= VS / 2 2 5 mV

OUT

= 15V 32 kΩ

REFH

= 0V 32 kW

REFL

= 5mA step 2 mV

OUT

SD

V

2

Loading...

Loading...