ELANT EL4584CS, EL4584CN Datasheet

EL4584C

Horizontal Genlock, 4 F

EL4584C February 1995 Rev B

SC

Features

# 36 MHz, general purpose PLL

# 4F

based timing (use the

SC

EL4585 for 8 F

SC

)

# Compatible w/EL4583 Sync

Separator

# VCXO, Xtal, or LC tank

oscillator

k

#

2 ns jitter (VCXO)

# User controlled PLL capture and

lock

# Compatible with NTSC and PAL

TV formats

# 8 pre-programmed TV scan rate

clock divisors

# Selectable external divide for

custom ratios

# Single 5V, low current operation

Applications

# Pixel Clock regeneration

# Video compression engine

(MPEG) clock generator

# Video capture or digitization

# PIP (Picture in Picture) timing

generator

# Text or graphics overlay timing

Ordering Information

Part No. Temp. Range Package Outline

EL4584CN -40§Ctoa85§C 16-Pin DIP MDP0031

EL4584CS -40

For 6Fsc and 8Fsc clock frequencies, see

EL4585 datasheet.

Ctoa85§C 16-Lead SO MDP0027

§

Demo Board

A demo PCB is available for this

product. Request ‘‘EL4584/5 Demo

Board’’.

General Description

The EL4584C is a PLL (Phase Lock Loop) sub system, designed

for video applications but also suitable for general purpose use

up to 36 MHz. In a video application this device generates a

TTL/CMOS compatible Pixel Clock (Clk Out) which is a multiple of the TV Horizontal scan rate, and phase locked to it.

The reference signal is a horizontal sync signal, TTL/CMOS

format, which can be easily derived from an analog composite

video signal with the EL4583 Sync Separator. An input signal

to ‘‘coast’’ is provided for applications were periodic disturbances are present in the reference video timing such as VTR

head switching. The Lock detector output indicates correct lock.

The divider ratio is four ratios for NTSC and four similar ratios

for the PAL video timing standards, by external selection of

three control pins. These four ratios have been selected for common video applications including 4 F

,3FSC, 13.5 MHz

SC

(CCIR 601 format) and square picture elements used in some

workstation graphics. To generate 8 F

,6FSC, 27 MHz (CCIR

SC

601 format) etc. use the EL4585, which includes an additional

divide by 2 stage.

For applications where these frequencies are inappropriate or

for general purpose PLL applications the internal divider can be

bypassed and an external divider chain used.

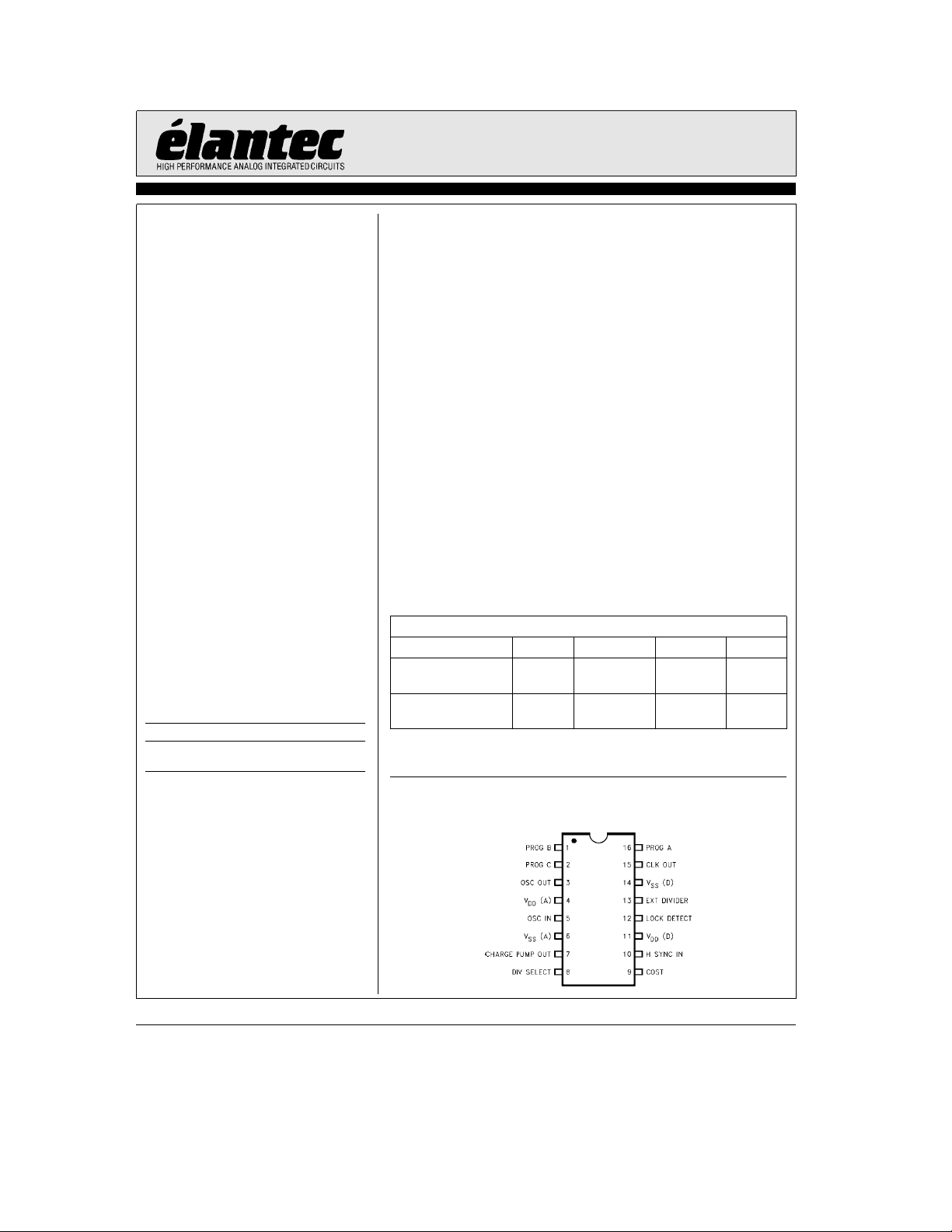

FREQUENCIES and DIVISORS

Function 3Fsc CCIR 601 Square 4Fsc

Divisor 851 864 944 1135

PAL Fosc (MHz) 13.301 13.5 14.75 17.734

Divisor 682 858 780 910

Ý

NTSC Fosc (MHz) 10.738 13.5 12.273 14.318

CCIR 601 Divisors yield 720 pixels in the portion of each line for NTSC and PAL.

Square pixels format gives 640 pixels for NTSC and 768 pixels for PAL in the active portion.

3Fsc numbers do not yield integer divisors.

Connection Diagram

EL4584 SO, P-DIP Packages

4584– 17

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a ‘‘controlled document’’. Current revisions, if any, to these

specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

©

1994 Elantec, Inc.

Ý

4584C

EL4584C

Horizontal Genlock, 4 F

SC

Absolute Maximum Ratings

V

Supply 7V Operating Junction Temp 125§C

CC

Storage Temperature

Lead Temperature 260

Pin Voltages

Operating Ambient Temperature

Range

Important Note:

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually

performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test

equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore T

Test Level Test Procedure

I 100% production tested and QA sample tested per QA test plan QCX0002.

II 100% production tested at T

III QA sample tested per QA test plan QCX0002.

IV Parameter is guaranteed (but not tested) by Design and Characterization Data.

V Parameter is typical value at T

T

MAX

and T

MIN

A

per QA test plan QCX0002.

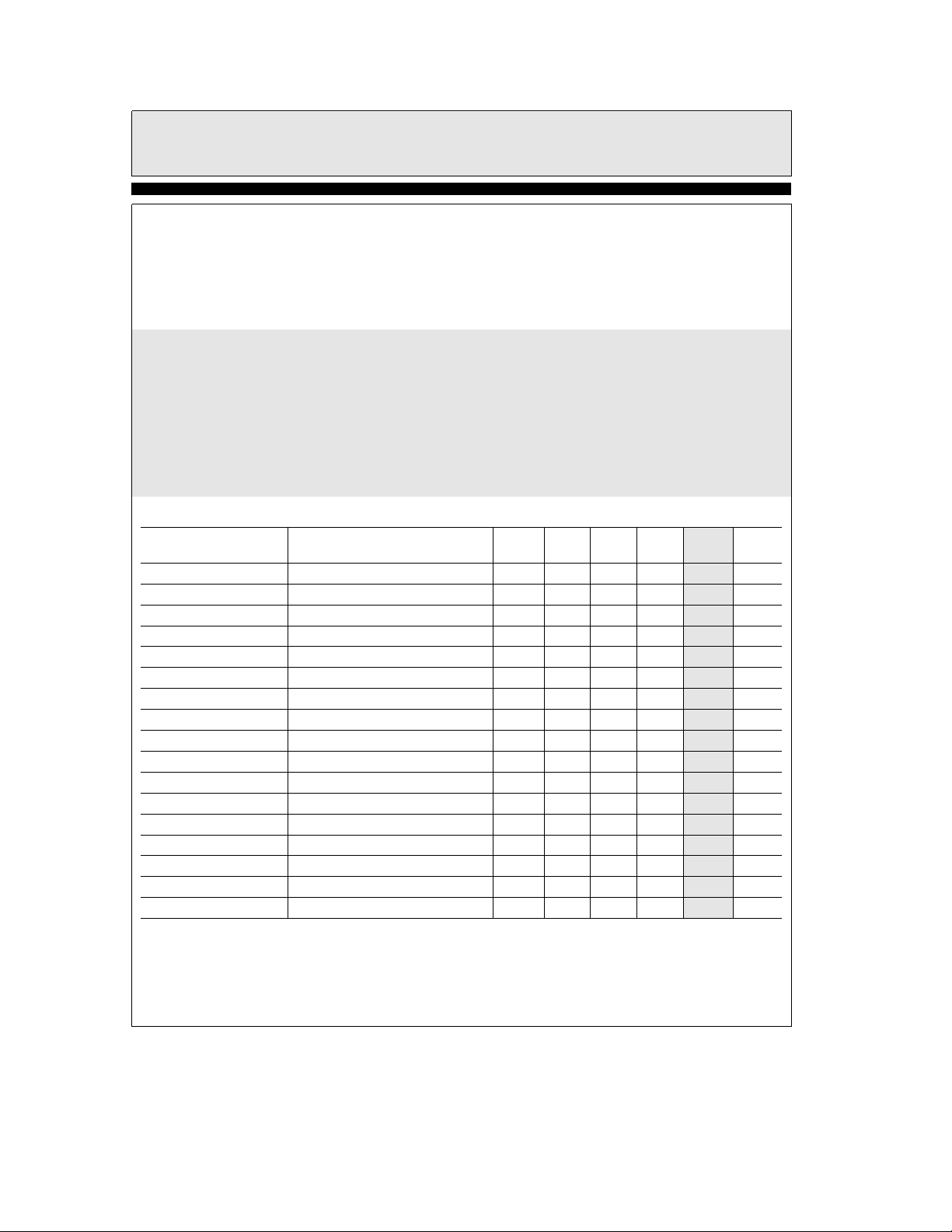

DC Electrical Characteristics

Parameter Conditions Temp Min Typ Max

I

DD

V

Input Low Voltage 25§C 1.5 I V

IL

e

V

5V (Note 1) 25§C24ImA

DD

e

(T

25§C)

A

b

65§Ctoa150§C Power Dissipation 400 mW

b

0.5V to V

b

40§Ctoa85§C

e

25§C and QA sample tested at T

e

25§C for information purposes only.

A

(V

DD

C Oscillator Frequency 36 MHz

§

a

0.5V

CC

e

25§C,

A

e

5V, T

e

25§C unless otherwise noted)

A

e

J

e

T

C

Test

Level

TA.

Units

VIHInput High Voltage 25§C 3.5 I V

IILInput Low Current All inputs except COAST, V

IIHInput High Current All inputs except COAST, V

IILInput Low Current COAST pin, V

IIHInput High Current COAST pin, V

VOLOutput Low Voltage Lock Det, I

VOHOutput High Voltage Lock Det, I

VOLOutput Low Voltage CLK, I

VOHOutput High Voltage CLK, I

OL

OH

VOLOutput Low Voltage OSC Out, I

VOHOutput High Voltage OSC Out, I

IOLOutput Low Current Filter Out, V

IOHOutput High Current Filter Out, V

IOL/IOHCurrent Ratio Filter Out, V

I

Filter Out Coast Mode, V

LEAK

e

1.5V 25§C

IN

e

3.5V 25§C 60 100 I mA

IN

e

1.6mA 25§C 0.4 I V

OL

eb

1.6mA 25§C 2.4 I V

OH

e

3.2mA 25§C 0.4 I V

eb

3.2mA 25§C 2.4 I V

e

200mA25

OL

eb

200mA25

OH

e

2.5V 25§C 200 300 I mA

OUT

e

2.5V 25§C

OUT

e

2.5V 25§C 1.05 1.0 0.95 I

OUT

l

V

DD

OUT

e

1.5V 25§C

IN

e

3.5V 25§C 100 I nA

IN

l

0V 25§C

b

100 I nA

b

C 0.4 I V

§

C 2.4 I V

§

b

b

100

100

60 I mA

b

300b200 I mA

g

1 100 I nA

Note 1: All inputs to 0V, COAST floating.

TDis 3.5in

2

EL4584C

Horizontal Genlock, 4 F

TDis 3.5in

SC

AC Electrical Characteristics

Parameter Conditions Temp Min Typ Max

VCO Gain@20 MHz Test Circuit 1 25§C 15.5 V dB

H-sync S/N Ratio V

Jitter VCXO Oscillator 25§C1 Vns

Jitter LC Oscillator (Typ) 25§C10 Vns

Note 2: Noisy video signal input to EL4583C, H-sync input to EL4584C. Test for positive signal lock.

e

5V (Note 2) 25§C35 V dB

DD

e

(V

DD

5V, T

e

25§C unless otherwise noted)

A

Test

Level

Units

Pin Description

Pin No. Pin Name Function

16,1,2 Prog A,B,C Digital inputs to selectdN value for internal counter. See table below for values.

3 Osc/VCO Out Output of internal inverter/oscillator. Connect to external crystal or LC tank VCO circuit.

4VDD(A) Analog positive supply for oscillator, PLL circuits.

5 Osc/VCO In Input from external VCO.

6VSS(A) Analog ground for oscillator, PLL circuits.

7 Charge Pump Out Connect to loop filter. If the H-sync phase is leading or H-sync frequencylCLKdN, current is pumped

8 Div Select Divide select input. When high, the internal divider is enabled and EXT DIV becomes a test pin,

9 Coast Tri-state logic input. Low(k(/3*VCC)enormal mode, Hi Z(or (/3 to )/3*VCC)efast lock mode,

10 H-sync In Horizontal sync pulse (CMOS level) input.

11 VDD(D) Positive supply for digital, I/O circuits.

12 Lock Det Lock Detect output. Low level when PLL is locked. Pulses high when out of lock.

13 Ext Div External Divide input when DIV SEL is low, internaldN output when DIV SEL is high.

14 VSS(D) Ground for digital, I/O circuits.

15 CLK Out Buffered output of the VCO.

into the filter capacitor to increase VCO frequency. If H-sync phase is lagging or frequency

current is pumped out of the filter capacitor to decrease VCO frequency. During coast mode or when

locked, charge pump goes to a high impedance state.

outputting CLK

externaldN.

l

High(

d

N. When low, the internal divider is disabled and EXT DIV is an input from an

)/3*VCC)ecoast mode.

VCO Divisors Table 1

Prog A Prog B Prog C Div Value

Pin 16 Pin 1 Pin 2 N

0 0 0 851

0 0 1 864

0 1 0 944

0 1 1 1135

1 0 0 682

1 0 1 858

1 1 0 780

1 1 1 910

k

CLKdN,

TABWIDE

TDis 3.5in

3

EL4584C

Horizontal Genlock, 4 F

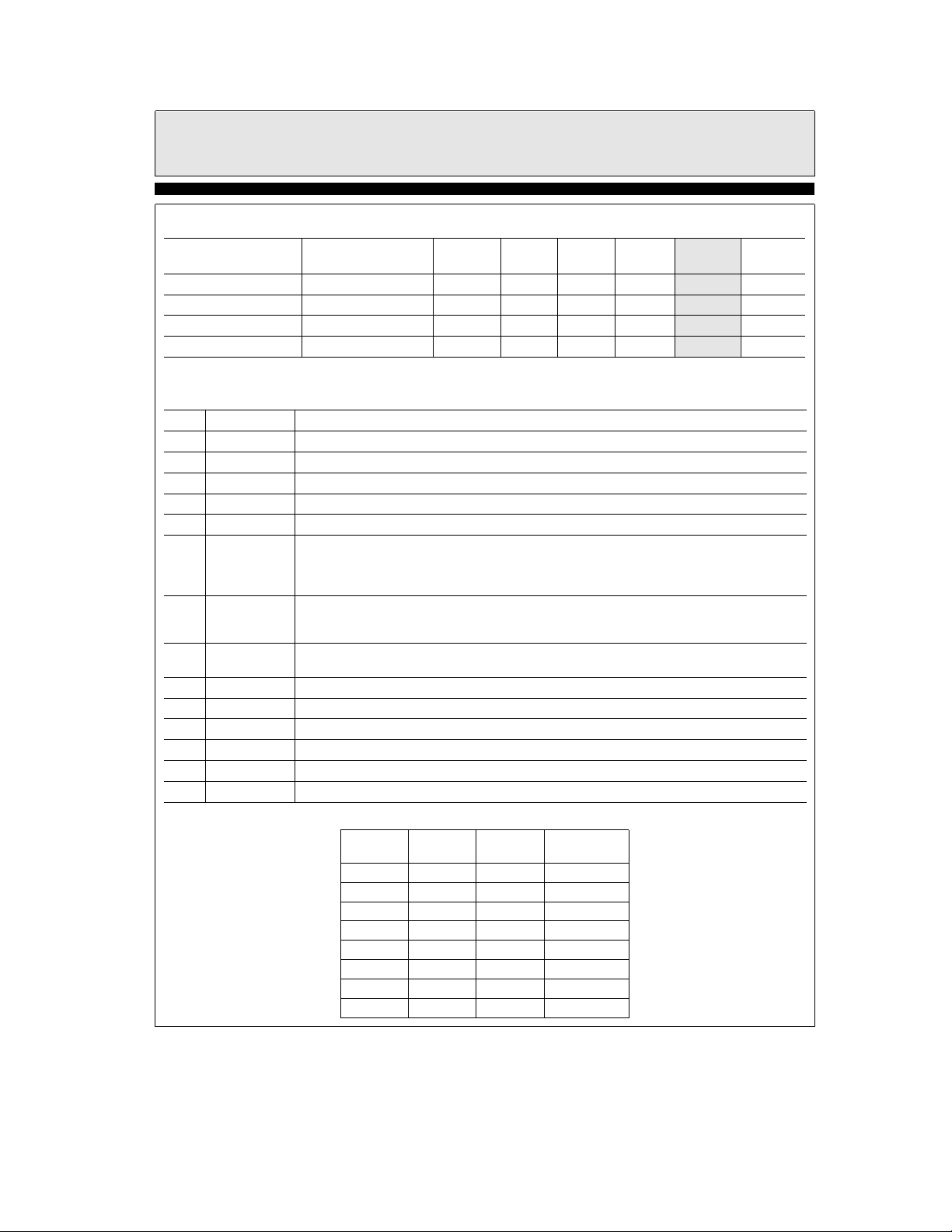

Timing Diagrams

PLL Locked Condition (Phase Errore0)

SC

Falling edge of H-synca110 ns locks to rising edge of Ext Div signal.

Out of Lock Condition

Test Circuit 1

4584– 2

T

i

e

i

E

T

H

e

T

H-sync period

H

e

phase error period

T

i

c

360

§

4584– 3

4584– 5

4

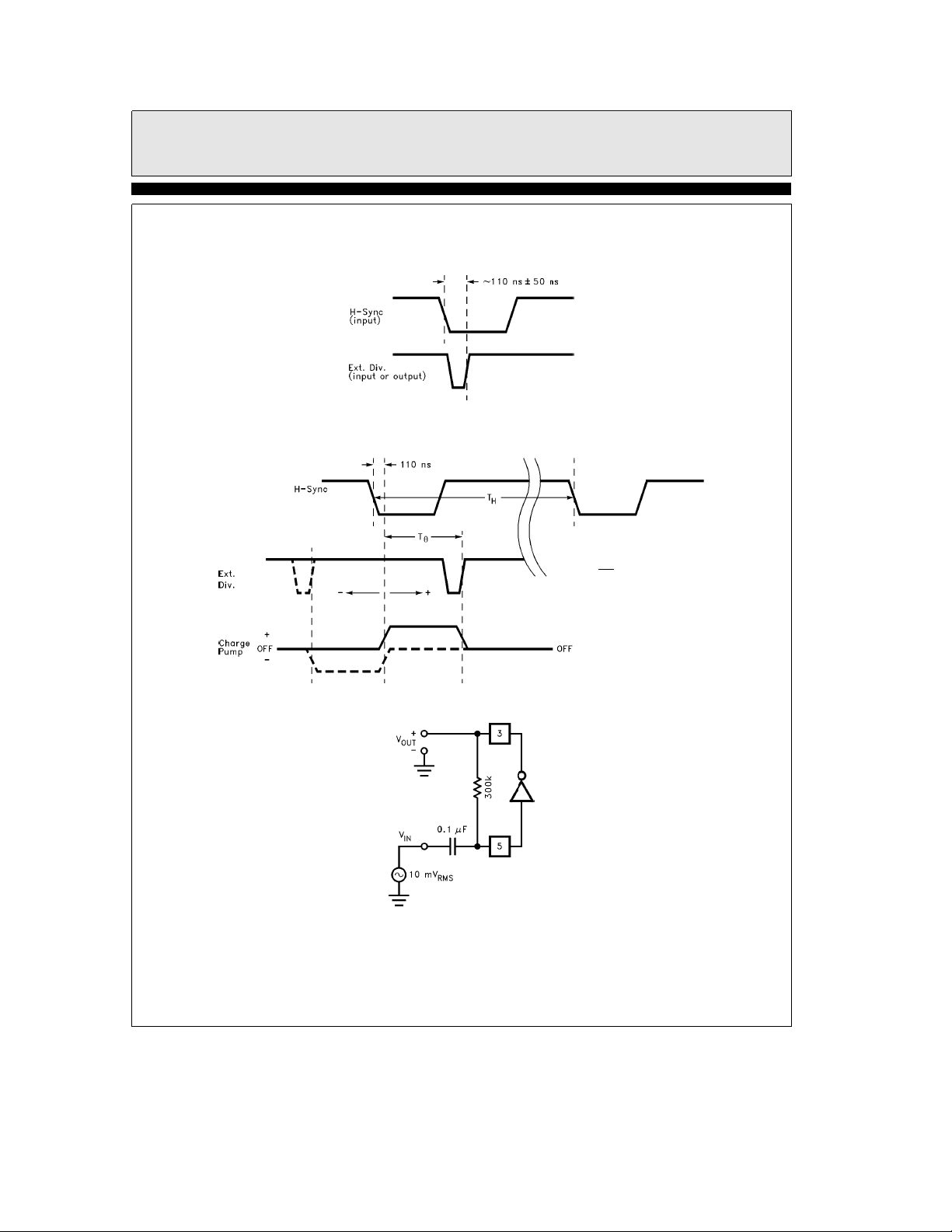

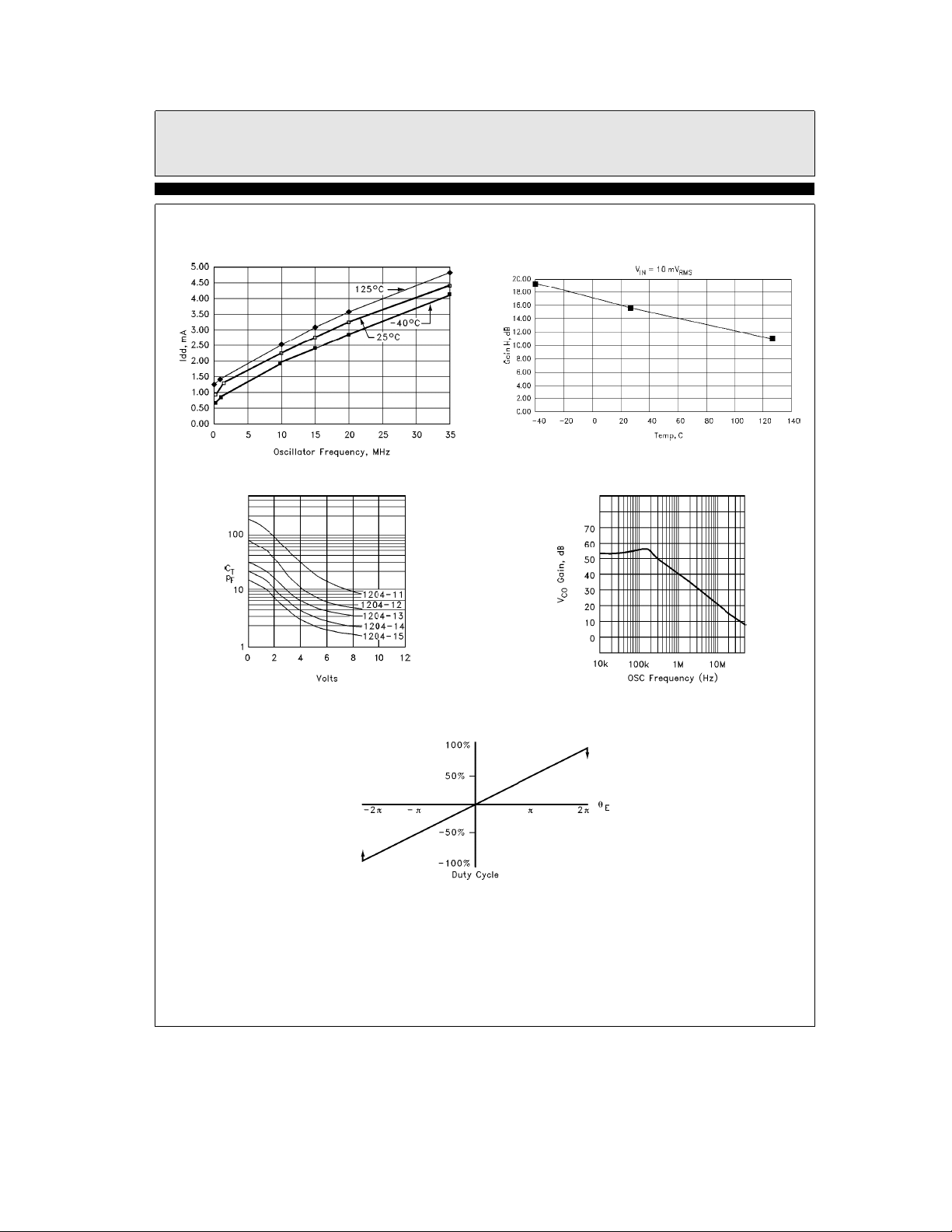

Typical Performance Curves

EL4584C

Horizontal Genlock, 4 F

SC

Idd vs Fosc

Typical Varactor

4584– 4

4584– 7

4584 OSC Gain@20 MHz vs Temp

4584– 6

OSC Gain vs Fosc

4584– 8

Charge Pump Duty Cycle vs i

5

E

4584– 9

Loading...

Loading...