EL2006/EL2006A November 1993 Rev F

EL2006/EL2006A

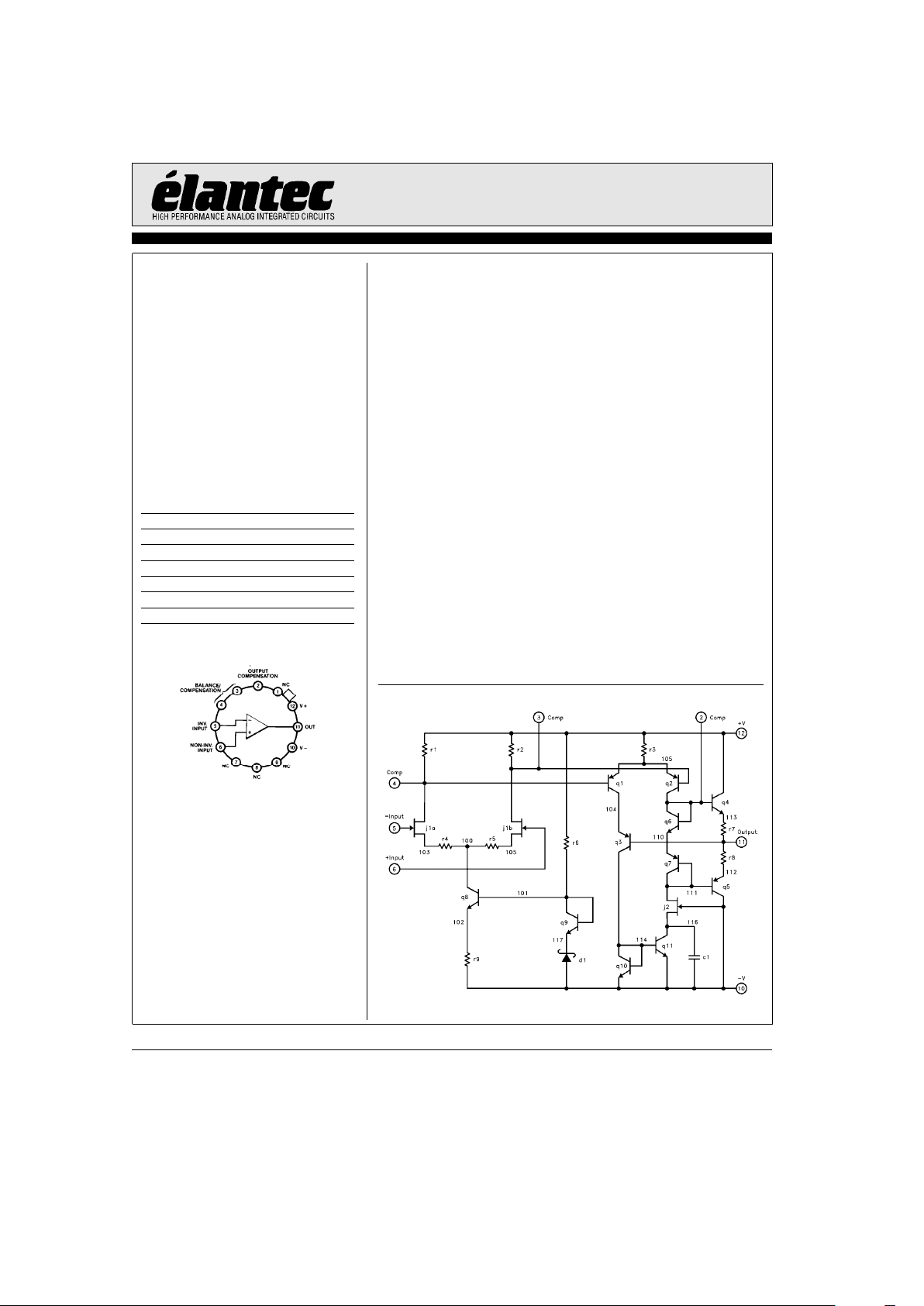

High Gain Fast FET Input Op Amp

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a ‘‘controlled document’’. Current revisions, if any, to these

specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

©

1989 Elantec, Inc.

Features

# 90 dB open loop gain

# 450 V/ms slew rate

# 40 MHz bandwidth

# No thermal tail

# 3 mV max input offset voltage

# Offset nulls with single pot

# No compensation required for

gains above 50

# Peak output current to 200 mA

# Pin compatible with LH0032

# 80 dB common mode rejection

Ordering Information

Part No. Temp. Range Pkg. Outline

Ý

EL2006CG

b

25§Ctoa85§C TO-8 MDP0002

EL2006G

b

55§Ctoa125§C TO-8 MDP0002

EL2006G/883Bb55§Ctoa125§C TO-8 MDP0002

EL2006ACG

b

25§Ctoa85§C TO-8 MDP0002

EL2006AG

b

55§Ctoa125§C TO-8 MDP0002

EL2006AG/883Gb55§Ctoa125§C TO-8 MDP0002

Connection Diagrams

2006– 1

Top View

General Description

The EL2006/EL2006A are high slew rate, wide bandwidth, high

input impedance, high gain and fully differential input operational amplifiers. They exhibit excellent open loop gain characteristics making them suitable for a broad range of high speed

signal processing applications. These patented devices have

open loop gains in excess of 86 dB making the EL2006/

EL2006A ideal choices for current mode video bandwidth digital to analog converters of 10 bits or higher resolution. The

EL2006’s FET input structure, high slew rate, and high output

drive capability allow use in applications such as buffers for

flash converter inputs. In general, the EL2006/EL2006A allow

the user to take relatively high closed loop gains without compromising gain accuracy or bandwidth.

The EL2006/EL2006A are pin compatible with the popular industry standard ELH0032/ELH0032A offering comparable

bandwidth and slew rate, while offering significant improvements in open loop gain, common mode rejection and power

supply rejection.

Elantec facilities comply with MIL-I-45208A and are

MIL-STD-1772 certified. Elantec’s Military devices comply

with MIL-STD-883 Class B Revision C and are manufactured

in our rigidly controlled, ultra-clean facilities in Milpitas, California. For additional information on Elantec’s Quality and Reliability Assurance Policy and procedures request brochure

QRA-1.

Simplified Schematic

2006– 3

Manufactured under U.S. Patent No. 4,746,877

EL2006/EL2006A

High Gain Fast FET Input Op Amp

Absolute Maximum Ratings

(T

A

e

25§C)

V

S

Supply Voltage

g

18V

V

IN

Input Voltage

g

15V

Differential Input Voltage 30V

I

OUT

Peak Output Current (Note 1)

g

200 mA

P

D

Power Dissipation

T

A

e

25§C 1.5W, derate 100§C/W toa125§C

T

C

e

25§C 2.2W, derate 70§C/W toa125§C

T

A

Operating Temperature Range

EL2006, EL2006A

b

55§Ctoa125§C

EL2006C, EL2006AC

b

25§Ctoa85§C

T

J

Operating Junction Temperature 175§C

T

ST

Storage Temperature

b

65§Ctoa150§C

Lead Temperature

(Soldering 10 seconds) 300

§

C

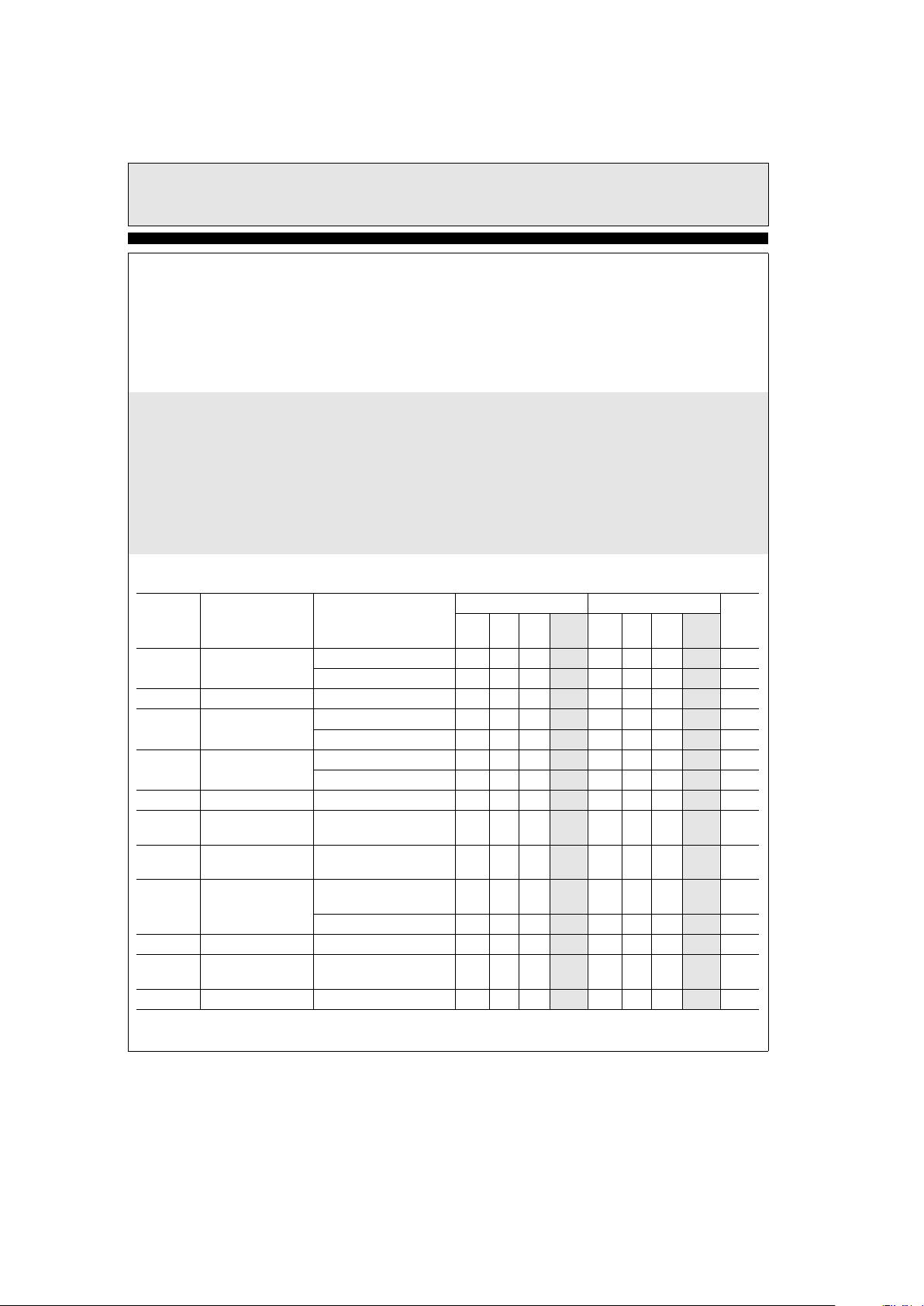

Important Note:

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually

performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test

equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore T

J

e

T

C

e

TA.

Test Level Test Procedure

I 100% production tested and QA sample tested per QA test plan QCX0002.

II 100% production tested at T

A

e

25§C and QA sample tested at T

A

e

25§C,

T

MAX

and T

MIN

per QA test plan QCX0002.

III QA sample tested per QA test plan QCX0002.

IV Parameter is guaranteed (but not tested) by Design and Characterization Data.

V Parameter is typical value at T

A

e

25§C for information purposes only.

DC Electrical Characteristics

V

S

e

g

15V, T

MIN

k

T

A

k

T

MAX

EL2006 EL2006C

Parameter Description Test Conditions

Min Typ Max

Test

Min Typ Max

Test Units

Level Level

V

OS

Offset Voltage T

J

e

25§C5I5ImV

10 I 10 III mV

DVOS/DT Offset Voltage Drift 15 V 15 V mV/§C

I

B

Bias Current T

J

e

25§C 100 I 500 I pA

1 10 I 1 10 III nA

I

OS

Offset Current T

J

e

25§C 25 I 50 I pA

0.2 2.5 I 0.2 2.5 III nA

V

CM

Common Mode Range

g

10 I

g

10 II V

CMRR Common Mode DV

IN

e

g

10V

70 80 I 70 80 II dB

Rejection Ratio

PSRR Power Supply

g

5VsV

S

s

g

15V

70 88 I 70 88 II dB

Rejection Ratio

A

VOL

Large Signal R

L

e

1kX,V

OUT

e

g

10V,

74 90 I 74 90 I dB

Voltage Gain T

J

e

25§C

R

L

e

1kX,V

OUT

e

g

10V 80 I 74 III dB

V

O

Output Voltage Swing R

L

e

1kX

g

12 I

g

12 II V

I

OUT

Output Current V

OUT

e

g

10V,

g

100 Ig100 I mA

T

J

e

25§C, (Note 1)

I

CC

Supply Current 20 23 I 20 23 II mA

2

TDis 0.9inTDis 3.9in

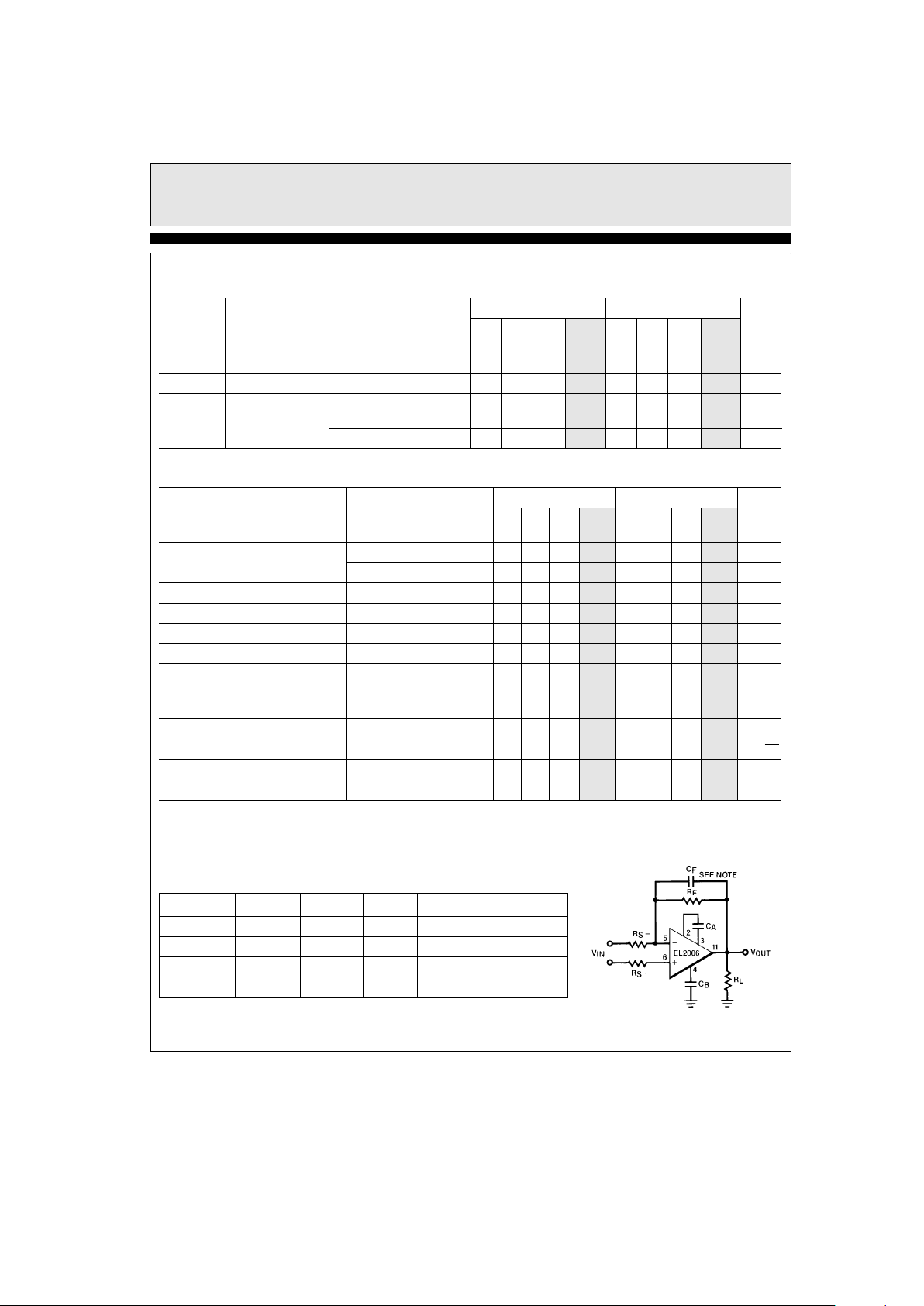

EL2006/EL2006A

High Gain Fast FET Input Op Amp

DC Electrical Characteristics

Ð Contd.

V

S

e

g

15V, T

MIN

k

T

A

k

T

MAX

(Note: These tests are in addition to those listed above.)

EL2006A EL2006AC

Parameter Description Test Conditions

Min Typ Max

Test

Min Typ Max

Test Units

Level Level

V

OS

Offset Voltage T

J

e

25§C3I3ImV

DV

OS

/DT Offset Voltage Drift 15 25 I 15 25 I mV/§C

A

VOL

Large Signal T

J

e

25§C, R

L

e

1kX,

74 90 I 74 90 II dB

Voltage Gain V

OUT

e

g

10V

R

L

e

1kX,V

OUT

e

g

10V 74 I 74 III dB

AC Electrical Characteristics

V

S

e

g

15V, R

L

e

1kX,T

J

e

25§C (See AC Test Circuits)

EL2006, EL2006A EL2006C, EL2006AC

Parameter Description Test Conditions

Min Typ Max

Test

Min Typ Max

Test Units

Level Level

t

r

Rise Time A

V

e

10V, V

OUT

e

1V

P-P

18 V 18 V ns

A

V

e

1V, V

OUT

e

1V

P-P

12 15 I 12 15 I ns

SR Slew Rate (Note 2) A

V

e

1V, V

OUT

e

20 V

P-P

350 450 I 350 450 I V/ms

t

s

Settling Time to 1.0% A

V

eb

1V, V

OUT

e

10 V

P-P

90 V 90 V ns

t

s

Settling Time to 0.1% A

V

eb

1V, V

OUT

e

10 V

P-P

160 V 160 V ns

t

s

Settling Time to 0.01% A

V

eb

1V, V

OUT

e

10 V

P-P

250 V 250 V ns

GBW Gain Bandwidth Product A

V

t

20V 500 V 500 V MHz

Pull Power V

OUT

e

g

10V

5.5 7 I 5.5 7 I MHz

Bandwidth (Note 3)

Unity Gain Bandwidth C

A

e

8 pF, C

B

e

100 pF 40 V 40 V MHz

e

N

Noise Voltage 1 kHz to 1 MHz 20 V 20 V nV/0Hz

t

D

Small Signal Delay A

V

e

1V 13 15 I 13 15 I ns

C

IN

Input Capacitance 2 V 2 V pF

Note 1: T

J

e

25§C, duty cyclek1%, pulse widthk10 ms.

Note 2: Slew rate is measured at the 25% and 75% points.

Note 3: The Full Power bandwidth is guaranteed by testing slew rate.

EL2006 Recommended Compensation

(See Figure 1)

A

VOL

C

A

C

B

R

S

a

R

S

b

R

F

a

1 5–8 pF 100 pF 2k Open Circuit 100

b

1toa5 5 pF 68 pF 0

k

1k 1k

g

10 5pF 10pF

k

1k 1k

l

10k

l

g

20 3pF 10pF

k

1k 1k

l

20k

Note: Use a small capacitor of about 1 pF in parallel with RFto compensate for stray

input capacitance.

2006– 4

Figure 1

3

TDis 1.4inTDis 2.9in

EL2006/EL2006A

High Gain Fast FET Input Op Amp

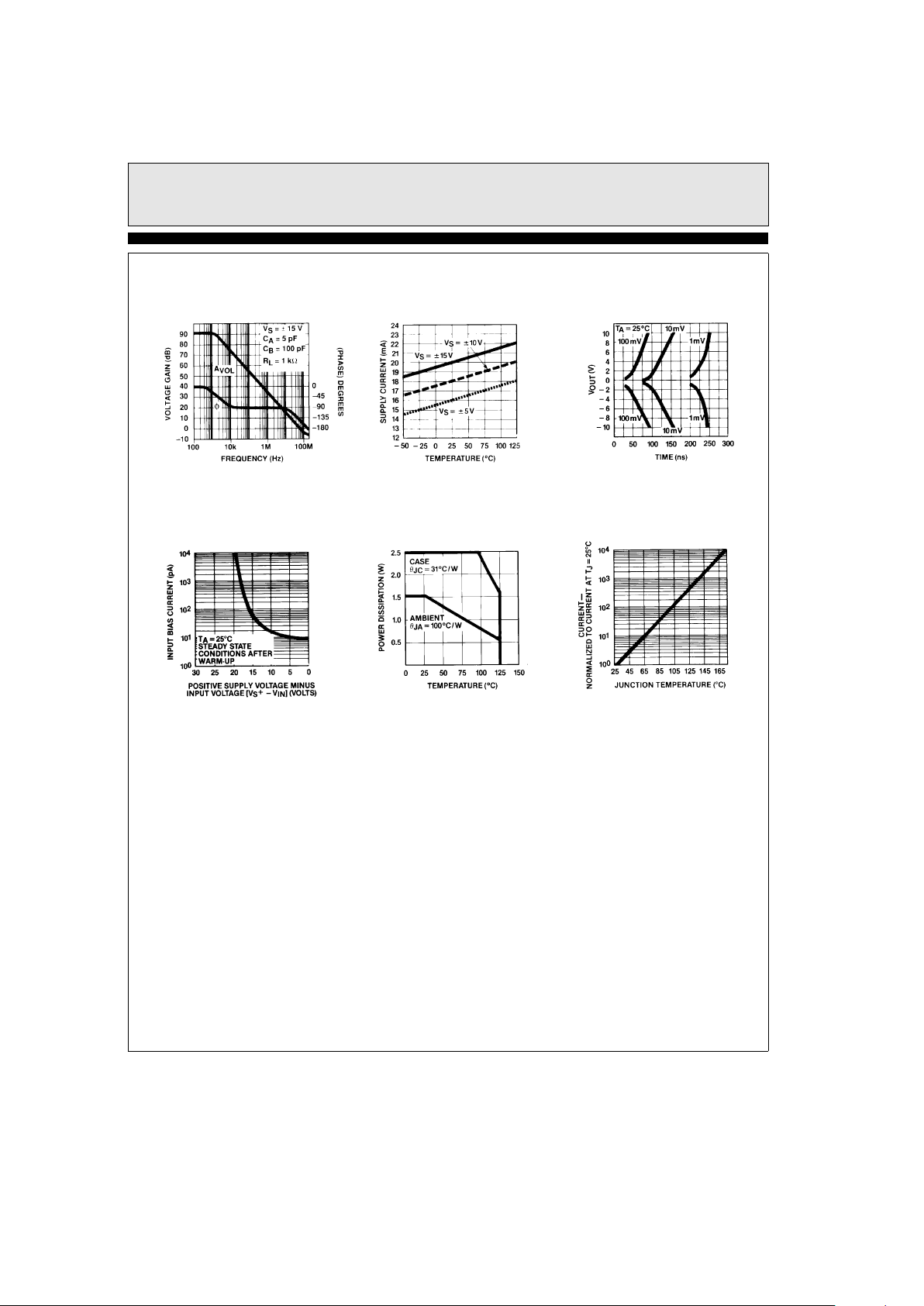

Typical Performance Curves

Bode Plot, Unity Gain

Compensation

Supply Current vs

Temperature

Inverting Gain ofb1

Settling Time

Voltage

Function of Input

Input Bias Currents as a

Dissipation

Maximum Power

TO-8

Junction Temperature

and Offset Current vs

Normalized Input Bias

2006– 5

Applications Information

General

The EL2006 was designed to overcome the gain

and stability limitations of prior high speed FET

input operational amplifiers like the LH0032.

Open loop gain is typically 90 dB allowing gain

setting to 12-bit accuracy. This new design also

eliminates ‘‘thermal tail’’, which is the tendency

for the gain to diminish at very low frequencies

to DC due to thermal feedback. The EL2006 is

also easier to stabilize than earlier designs,

thanks to an Elantec proprietary internal compensation technique which eliminates the ‘‘second stage bump.’’ The EL2006 open loop gain

4

Loading...

Loading...