EL2004/EL2004C

350 MHz FET Buffer

EL2004/EL2004C November 1993 Rev G

Features

# Slew rateÐ2500 V/ms

# Rise timeÐ1 ns

# BandwidthÐ350 MHz

# ELH0033Ðpin compatible

g

#

5tog15V operation

# 100 mA output current

# MIL-STD-883B Rev. C devices

manufactured in U.S.A.

Applications

# Coaxial cable driver

# Fast op amp booster

# Flash converter driver

# Video line driver

# High-speed sample and hold

# Pulse transformer driver

# A.T.E. pin driver

Ordering Information

Part No. Temp. Range Package Outline

EL2004CGb25§Ctoa85§C TO-8 MDP0002

EL2004G

EL2004L

EL2004L/MILb55§Ctoa125§C 52-Pad LCC MDP0013

5962-89659 is the SMD version of this device.

b

55§Ctoa125§C TO-8 MDP0002

b

55§Ctoa125§C 52-Pad LCC MDP0013

General Description

The EL2004 is a very high-speed, FET input buffer/line driver

designed for unity gain applications at both high current (up to

100 mA) and at frequencies up to 350 MHz. The 2500 V/ms slew

rate and wide bandwidth ensures the stability of the circuit

when the EL2004 is used inside op amp feedback loops.

Applications for the EL2004 include line drivers, video buffers,

wideband instrumentation, and high-speed drivers for inductive

and capacitive loads. The performance of the EL2004 makes it

an ideal buffer for video applications including input buffers for

flash A/D converters, and output buffers for video DACs. Its

excellent phase linearity is particularly advantageous in digital

signal processing applications.

Elantec facilities comply with MIL-I-45208A and are MILSTD-1772 certified. Elantec’s Military devices comply with

MIL-STD-883B Revision C and are manufactured in our rigidly

controlled, ultra-clean facilities in Milpitas, California. For additional information on Elantec’s Quality and Reliability Assurance Policy and procedures request brochure QRA-1.

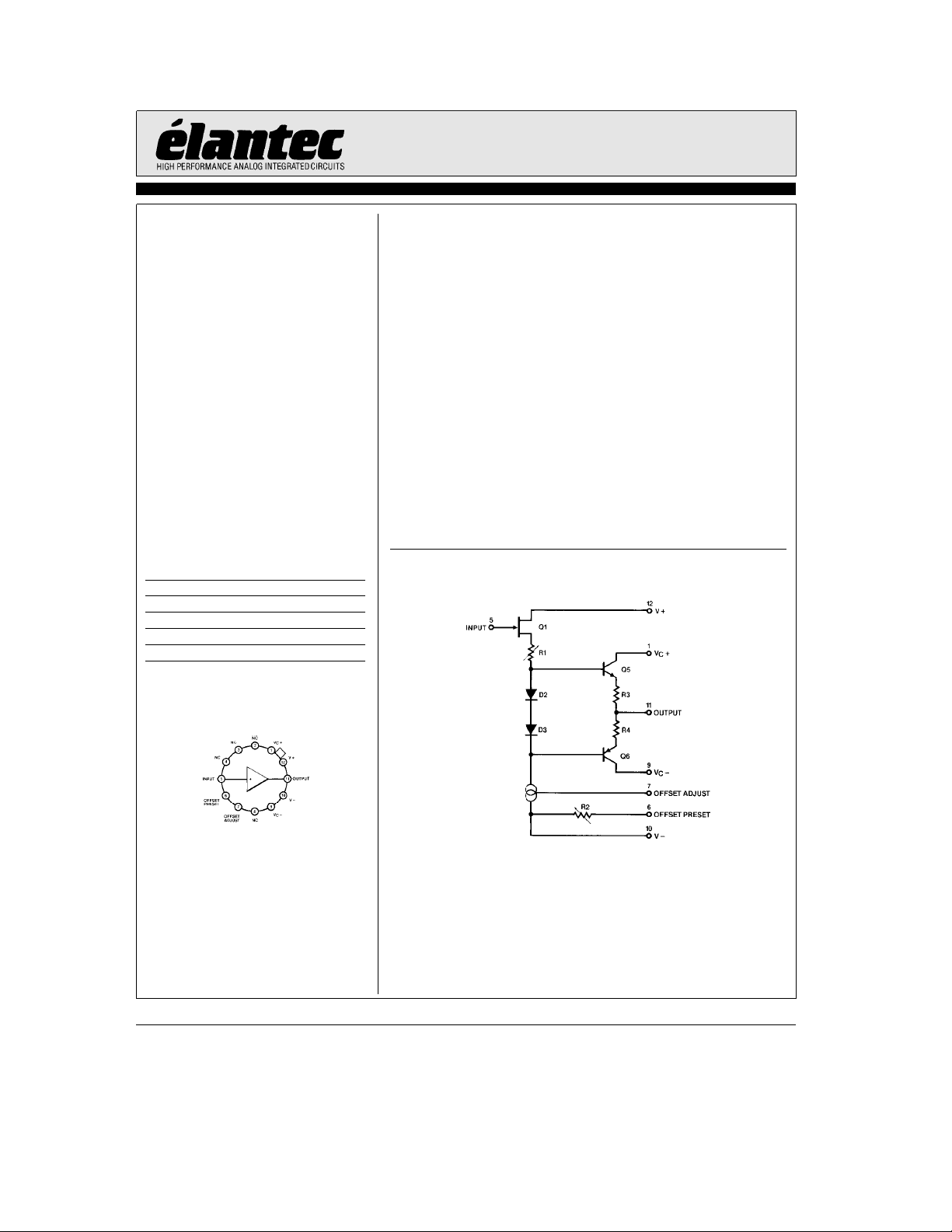

Simplified Schematic

Ý

Connection Diagram

Case is Electrically Isolated

Top View

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a ‘‘controlled document’’. Current revisions, if any, to these

specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation. Patent pending.

©

1989 Elantec, Inc.

2004– 1

2004– 3

EL2004/EL2004C

350 MHz FET Buffer

Absolute Maximum Ratings

V

S

V

IN

P

D

I

OC

I

OP

Important Note:

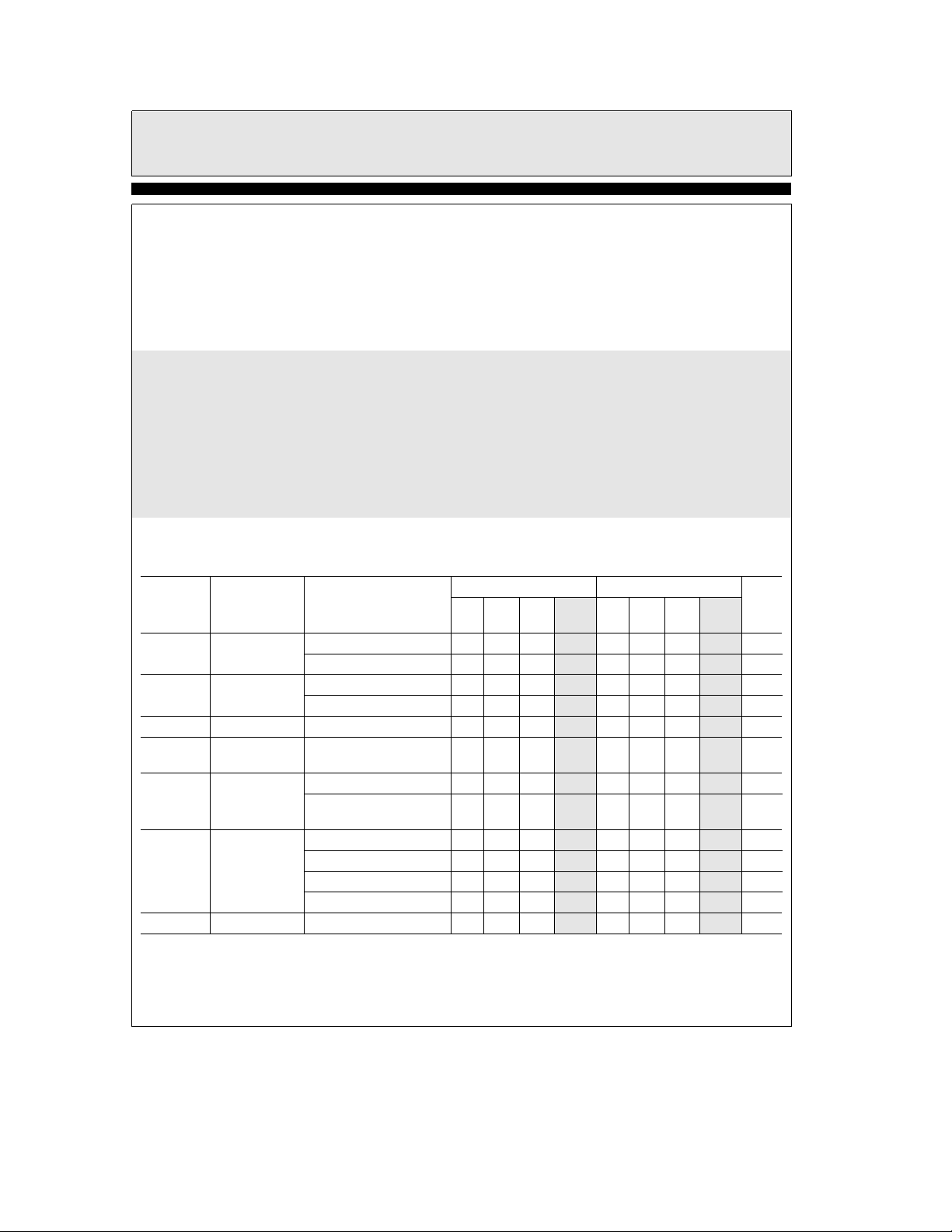

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually

performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test

equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore T

Test Level Test Procedure

g

15V DC Electrical Characteristics

e

V

S

Supply Voltage (VabVb) 40V

Input Voltage 40V

Power Dissipation (See curves) 1.5W

Continuous Output Current

Peak Output Current

I 100% production tested and QA sample tested per QA test plan QCX0002.

II 100% production tested at T

III QA sample tested per QA test plan QCX0002.

IV Parameter is guaranteed (but not tested) by Design and Characterization Data.

V Parameter is typical value at T

g

15V, T

MIN

T

and T

MAX

k

T

A

k

T

MIN

MAX,VIN

A

per QA test plan QCX0002.

e

0V, R

e

(T

25§C)

A

T

Operating Temperature Range

A

EL2004

EL2004C

g

100 mA

g

250 mA

T

Operating Junction Temperature 175§C

J

T

Storage Temperature

ST

Lead Temperature

(Soldering, 10 seconds) 300

e

25§C and QA sample tested at T

e

25§C for information purposes only.

A

e

1kXunless otherwise specified (Note 1)

L

A

e

25§C,

b

55§Ctoa125§C

b

25§Ctoa85§C

b

65§Ctoa150§C

e

e

T

J

C

§

TA.

EL2004 EL2004C

Parameter Description Test Conditions

V

A

R

R

V

I

I

OS

V

IN

OUT

O

IN

S

Output Offset R

Voltage

Voltage Gain V

Input Impedance T

Output V

Impedance DR

Output Voltage V

Swing

Input Current T

s

100 kX,T

S

s

R

100 kX 15 I 25 III mV

S

e

g

IN

e

R

100X,V

L

e

25§C, V

J

e

g

IN

e

L

e

g

IN

e

g

V

IN

e

T

25§C

A

e

25§C (Note 2) 0.25 I 2.0 I nA

J

e

T

25§C (Note 3) 2.5 IV 20 IV nA

A

e

T

T

J

A

eb

V

IN

Supply Current 20 24 I 20 24 II mA

e

25§C 5 10 I 12 20 I mV

J

10V 0.97 0.98 1.0 I 0.96 0.98 1.0 II V/V

e

IN

e

g

IN

1VDC,

100X to Infinity

14V

T

MAX

e

L

10.5V, R

e

10V 20 V 20 V nA

Min Typ Max

g

10V 0.92 0.95 0.98 I 0.90 0.95 0.98 II V/V

1V 10810

11

Test

Min Typ Max

Level Level

I10810

11

4 8 I 4 10 II X

100X

g12g

g9g

13 I

9.8 I

g12g

13 II V

g9g

9.8 I V

10 I 50 III nA

Test

I X

Units

C

TDis 3.2in

2

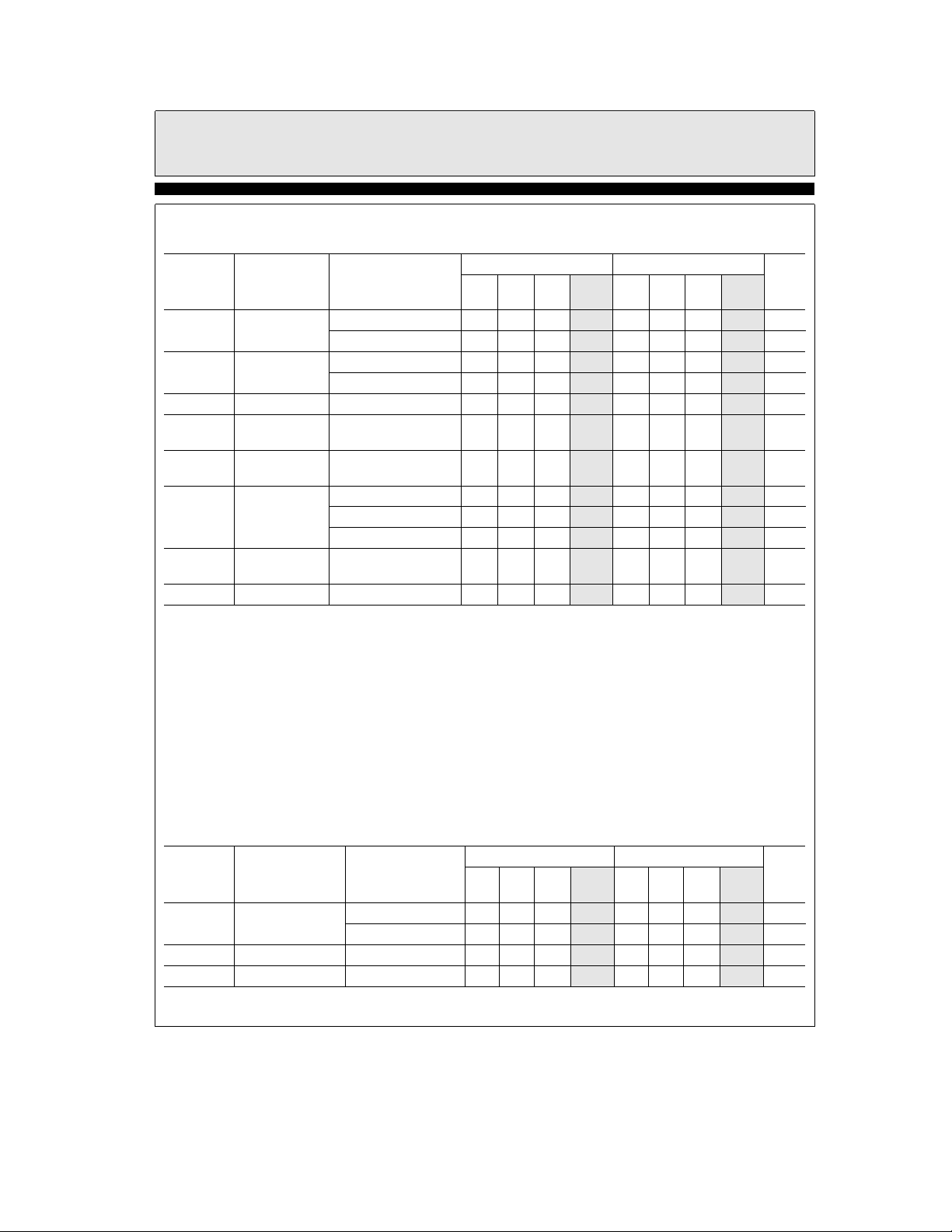

EL2004/EL2004C

350 MHz FET Buffer

g

5V DC Electrical Characteristics

e

g

V

5V, T

S

Parameter Description Test Conditions

V

OS

A

V

R

IN

R

OUT

V

O

I

IN

PSRR Power Supply V

I

S

Note 1: When operating at elevated temperatures the power dissipation of the EL2004 must be limited to the values shown in the

typical performance curve ‘‘Maximum Power Dissipation vs Temperature’’. Junction to case thermal resistance is 31

when dissipation is spread among the transistors in a normal AC steady-state condition. In special conditions where heat is

concentrated in one output device, junction temperature should be calculated using a thermal resistance of 70

Note 2: Specification is at 25

temperatures will exceed the value at T

may rise 40

I

IN

Note 3: Measured in still air seven minutes after application of power. See graph of Input Current During Warm-up for further

information.

Note 4: Bandwidth is calculated from the rise time. The EL2004 has a single pole gain and phase response up to the

frequency.

Note 5: Slew rate is measured between V

Note 6: Slew rate is measured between V

k

MIN

k

T

T

A

MAX,VIN

e

0V, R

e

50X unless otherwise specified

L

EL2004 EL2004C

Min Typ Max

Output Offset R

Voltage

Voltage Gain V

Input Impedance T

Output V

Impedance DR

Output Voltage V

Swing

Input Current T

Rejection Ratio R

Supply Current R

C junction temperature due to requirements of high-speed automatic testing. Actual values at operating

§

Cto60§C above ambient and more under load conditions. Accordingly, VOSmay change one to several mV, and

§

will change significantly during warm-up. Refer to IINvs Temperature graph for expected values.

s

100 kX,T

S

s

R

100 kX 35 I 35 III mV

S

e

g

IN

e

g

V

IN

e

25§C, V

J

e

g

IN

e

L

e

g

IN

e

25§C (Note 2) 250 I 500 I pA

J

e

T

25§C (Note 3) 2.5 IV 5 IV nA

A

e

T

T

J

A

e

g

S

e

1kX

L

e

1kX 17.5 20 I 17.5 20 II mA

L

OUT

OUT

e

25§C 10 30 I 10 30 I mV

J

e

1V, R

1kX 0.90 0.95 1.0 I 0.90 0.95 1.0 II V/V

L

1V 0.80 0.88 0.95 I 0.80 0.88 0.95 II V/V

e

g

1V 10810

IN

1VDC,

50X to Infinity

4V

e

T

MAX

g

5V tog15V

e

25§C. When supply voltages areg15V, no-load operating junction temperatures

J

ea

2.5V andb2.5V for this test.

ea

1V andb1V for this test. Pulse repetition rate isk50 MHz.

11

4 8 I 4 10 II X

2.0g2.9 I

60 V 60 V dB

Test

Min Typ Max

Level Level

I101010

g

11

2.0g2.9 III V

10 I 20 III nA

Test

I X

C/W.

§

Units

C/W

§

b

3dB

TDis 3.2inTDis 1.3in

g

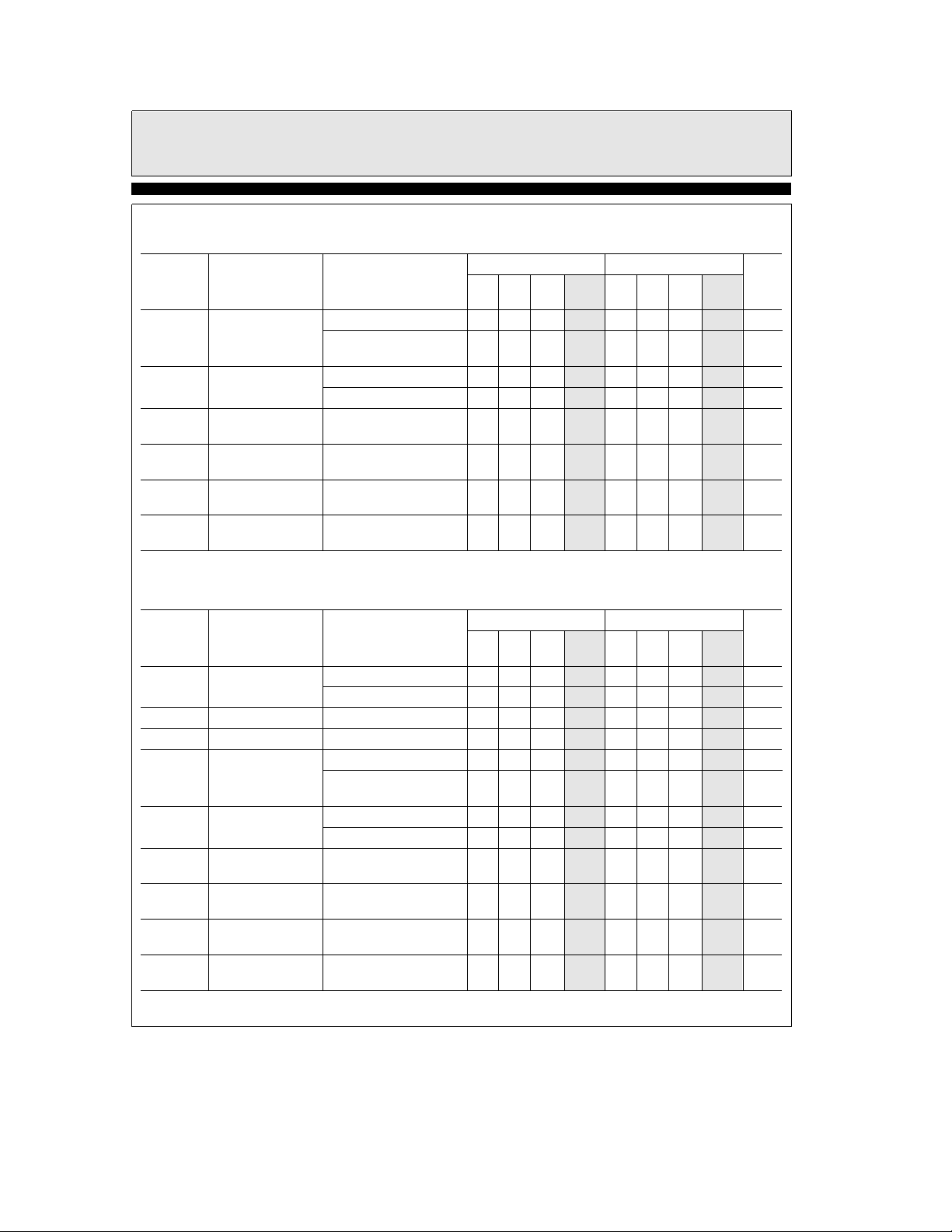

15V AC Electrical Characteristics

e

g

V

S

15V, R

L

e

1kX,R

S

e

50X,T

e

25§C unless otherwise specified

J

EL2004 EL2004C

Parameter Description Test Conditions

Min Typ Max

Test

Min Typ Max

Level Level

Test

Units

BW Bandwidth (Note 4) 200 350 I 200 350 I MHz

e

R

50X 140 200 I 140 200 I MHz

L

e

t

s

C

in

Settling Time to 1% DV

IN

Input Capacitance 3 V 3 V pF

e

1V, t

3ns 6 V 6 V ns

r

3

EL2004/EL2004C

350 MHz FET Buffer

g

15V AC Electrical Characteristics

e

g

V

S

Parameter Description Test Conditions

SR Slew Rate V

t

r

t

p

R

OUT

a

PSRR Power Supply DV

b

PSRR Power Supply DV

g

5V AC Electrical Characteristics

e

g

V

S

Parameter Description Test Conditions

BW Bandwidth R

t

s

C

in

SR Slew Rate V

t

r

t

p

R

OUT

a

PSRR Power Supply DV

b

PSRR Power Supply DV

15V, R

e

L

1kX,R

S

e

50X,T

e

25§C unless otherwise specified Ð Contd.

J

e

g

5V (Note 5) 2000 2500 I 2000 2500 I V/ms

IN

e

C

100 pF, V

L

(Note 5)

IN

Rise Time DVINP 0.6V 1.0 1.7 I 1.0 1.7 I ns

Note: See Test Figure

Propagation Delay

Note: See Test Figure

Output fe1 MHz, V

Impedance DR

Rejection Ratio fe1 kHz

Rejection Ratio f

5V, R

e

L

50X,R

e

50X,T

S

DV

P 0.6V, R

IN

DV

P 0.6V 1.0 2.0 I 1.0 2.0 I ns

IN

e

100X to Infinity

L

ae

S

be

S

e

1 kHz

e

25§C unless otherwise specified

J

e

1kX 175 220 I 175 220 I MHz

L

g

g

IN

1.5 V

1.5 V

L

e

peak

e

peak

(Note 4) 125 150 IV 125 150 IV MHz

e

Settling Time to 1% DV

IN

e

1V, t

3ns 8 V 8 V ns

r

Input Capacitance 3 V 3 V pF

e

g

2V (Note 6) 900 1200 I 900 1200 I V/ms

IN

e

C

100 pF, V

L

e

R

L

Rise Time R

Note: See Test Figure

Propagation Delay R

Note: See Test Figure

e

L

e

R

L

e

L

Output fe1 MHz, V

e

e

L

be

S

ae

S

1 kHz

Impedance DR

Rejection Ratio fe1 kHz

Rejection Ratio f

IN

1kX(Note 6)

1kX,DVINP 0.6V 1.6 2.0 I 1.6 2.0 I ns

50X, DVINP 0.6V 2.3 2.8 IV 2.3 2.8 IV ns

1kX,DVINP 0.6V

e

IN

100X to Infinity

g

0.5 V

peak

g

0.5 V

peak

EL2004 EL2004C

Min Typ Max

e

g

5V

1200 V 1200 V V/ms

Test

Min Typ Max

Level Level

Test

50X 1.7 2.5 I 1.7 2.5 I ns

1V

RMS

4V4VX

40 V 40 V dB

40 V 40 V dB

EL2004 EL2004C

Min Typ Max

e

g

2V

500 V 500 V V/ms

Test

Min Typ Max

Level Level

Test

1.2 2.4 I 1.2 2.4 I ns

1V

RMS

4V4VX

30 V 30 V dB

30 V 30 V dB

Units

TDis 2.7inTDis 3.4in

Units

4

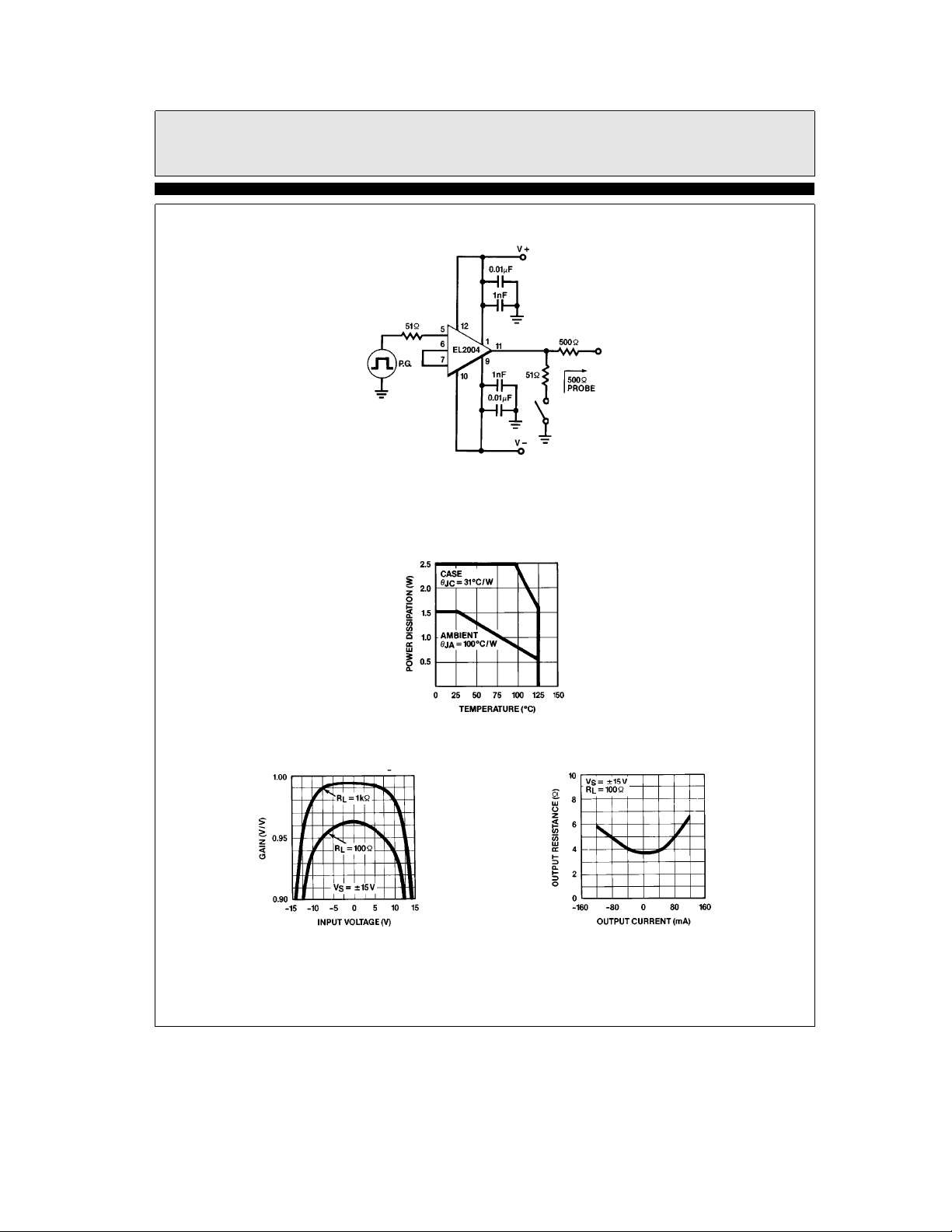

AC Test Circuit

Typical Performance Curves

TO-8

Maximum Power

Dissipation

EL2004/EL2004C

350 MHz FET Buffer

2004– 4

2004– 5

Gain vs Input Voltage Output Current

5

Output Resistance vs

2004– 7

Loading...

Loading...