Page 1

EPH3600

RISC II Series

Microcontroller

Product

Specification

DOC. VERSION 0.1

ELAN

MICROELECTRONICS CORP.

October 2007

Page 2

Trademark Acknowledgments:

IBM is a registered trademark and PS/2 is a trademark of IBM.

Windows is a trademark of Microsoft Corporation.

ELAN and ELAN logo are trademarks of ELAN Microelectronics Corporation.

Copyright © 2007 by ELAN Microelectronics Corporation

All Rights Reserved

Printed in Taiwan

The contents of this specification are subject to change wi t h out f urt her notice. ELAN Microelectronics assumes

no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN

Microelectronics makes no commitment to update, or to keep current the information and material contained in

this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible for any claims attributed to errors, omissions, or

other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall

not be liable for direct, indirect, special incidental, or consequential damages arising from the use of such

information or material.

The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and

may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of

ELAN Microelectronics product in such applications is not supported and is prohib ited.

NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR

BY ANY MEANS WITHOUT THE EXPRESSED WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

ELAN MICROELECTRONICS CORPORATION

Headquarters:

No. 12, Innovation Road 1

Hsinchu Science Park

Hsinchu, TAIWAN 308

Tel: +886 3 563-9977

Fax: +886 3 563-9966

http://www.emc.com.tw

Hong Kong:

Elan (HK) Microelectronics

Corporation, Ltd.

Flat A, 19F., World Tech Centre

95 How Ming Street, Kwun Tong

Kowloon, HONG KONG

Tel: +852 2723-3376

Fax: +852 2723-7780

elanhk@emc.com.hk

Shenzhen:

Elan Microelectronics

Shenzhen, Ltd.

3F, SSMEC Bldg., Gaoxin S. Ave. I

Shenzhen Hi-tech Industrial Park

(South Area), Shenzhen

CHINA 518057

Tel: +86 755 2601-0565

Fax: +86 755 2601-0500

USA:

Elan Information

Technology Group (U.S.A.)

PO Box 601

Cupertino, CA 95015

U.S.A.

Tel: +1 408 366-8225

Fax: +1 408 366-8225

Shanghai:

Elan Microelectronics

Shanghai, Ltd.

#23, Zone 115, Lane 572, Bibo Rd.

Zhangjiang Hi-Tech Park

Shanghai, CHINA 201203

Tel: +86 21 5080-3866

Fax: +86 21 5080-4600

Page 3

Contents

Contents

1 General Description.................................................................................................. 1

1.1 Applications........................................................................................................2

2 Features ..................................................................................................................... 2

2.1 MCU Features....................................................................................................2

2.2 Peripheral...........................................................................................................2

2.3 Internal Specification..........................................................................................3

2.4 Elan Software Support (Option) ......................................................................... 3

3 Block Diagram........................................................................................................... 4

4 Pin Assignment......................................................................................................... 5

5 Pin Description.......................................................................................................... 6

5.1 MCU System Pins (9 Pins)................................................................................. 6

5.2 I/O Ports (32 Pins).............................................................................................. 7

6 Code Options............................................................................................................. 8

7 Function Description ................................................................................................ 9

7.1 Reset Function................................................................................................... 9

7.1.1 Power-up and Reset Timing................................................................................9

7.1.2 Register Initial Values........................................................................................11

7.2 Oscillator System .............................................................................................13

7.2.1 32.768kHz Crystal or 32.8kHz RC....................................................................13

7.2.2 Phase Locked Loop (PLL).................................................................................13

7.3 MCU Operation Mode ...................................................................................... 15

7.4 Wake-up Function............................................................................................ 17

7.5 Interrupt............................................................................................................18

7.5.1 Input Port A Interrupt .........................................................................................18

7.5.2 Capture Input Interrupt......................................................................................19

7.5.3 Speech Timer Interrupt......................................................................................19

7.5.4 Timer 0, Timer 1, and Timer 2 Interrupts...........................................................19

7.5.5 Peripheral Interrupt............................................................................................20

7.6 Program ROM Map .......................................................................................... 20

7.7 Data ROM Map ................................................................................................ 21

7.8 RAM Map Register

(RAM Size: 128 Bytes + 32 Banks × 128 Bytes = 4224 Bytes)........................

7.8.1 Special and Control Register of RAM................................................................21

7.8.2 Other Un-banked Register of RAM:..................................................................25

7.8.3 Banked Register of RAM:(selected by BSR) ....................................................25

7.9 Special Register Description............................................................................ 25

7.9.1 Indirect Addressing Pointer 0............................................................................26

7.9.2 Indirect Addressing Pointer 1............................................................................27

21

Product Specification (V0.1) 10.11.2007 • iii

(This specification is subject to change without further notice)

Page 4

Contents

8 Peripheral................................................................................................................. 32

8.1 Timer 0 (16-bit Timer with Capture and Event Counter Functions).................. 32

8.1.1 Timer 0 Mode: ...................................................................................................32

8.1.2 Capture Mode: CPIN (Port B.5) Pin ..................................................................33

8.1.3 Event Counter Mode: EVIN (Port B.5) Pin ........................................................33

8.2 Timer 1 (8 Bits)................................................................................................. 37

8.3 Timer 2 (8 Bits)................................................................................................. 40

8.4 IR Generator: IROT (Port B.2) Pin.................................................................... 43

8.5 EL Timer (6 Bits)............................................................................................... 44

8.5.1 EL Generator Timing.........................................................................................46

8.6 Watchdog Timer (WDT).................................................................................... 47

8.7 Universal Asynchronous Receiver Transmitter (UART).................................... 48

8.7.1 Data Format in UART........................................................................................49

8.7.2 UART Modes.....................................................................................................49

8.7.3 UART Transmit Data.........................................................................................50

8.7.4 UART Receive Data..........................................................................................50

8.7.5 UART Baud Rate Generator.............................................................................51

8.7.6 UART Applicable Registers...............................................................................51

8.7.7 Transmit Counter Timing...................................................................................54

8.7.8 UART Transmit Operation (8-Bit Data with Parity Bit).......................................54

8.7.9 Receive Counter T iming....................................................................................55

8.8 A/D Converter................................................................................................... 57

8.8.1 A/D Converter Applicable Registers..................................................................58

8.8.2 Timing Diagram of General A/D Converter Application.....................................61

8.8.3 Correlation between A/D Converter and MCU Mode........................................61

8.8.4 A/D Converter Flowchart...................................................................................63

8.9 Serial Peripheral Interface (SPI)....................................................................... 65

8.9.1 Master Mode .....................................................................................................66

8.9.2 Slave Mode .......................................................................................................67

8.9.3 SPI Pin Descriptions..........................................................................................67

8.9.4 SPI Applicable Registers...................................................................................67

8.9.5 SPI Timing Diagrams.........................................................................................70

8.10 Speech Synthesizer.......................................................................................... 72

8.10.1 Speech Function................................................................................................72

8.11 DAC Function................................................................................................... 74

8.11.1 DAC Function Block Diagram ...........................................................................74

8.11.2 DAC Function Registers....................................................................................75

iv • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 5

Contents

9 Electrical Characteristic ......................................................................................... 76

9.1 Absolute Maximum Ratings.............................................................................. 76

9.2 Recommended Operating Conditions.............................................................. 76

9.3 DC Electrical Characteristics............................................................................ 76

9.4 AC Electrical Characteristics............................................................................78

10 Application Circuit ................................................................................................. 79

11 Instruction Set......................................................................................................... 80

12 Pad Diagram ............................................................................................................83

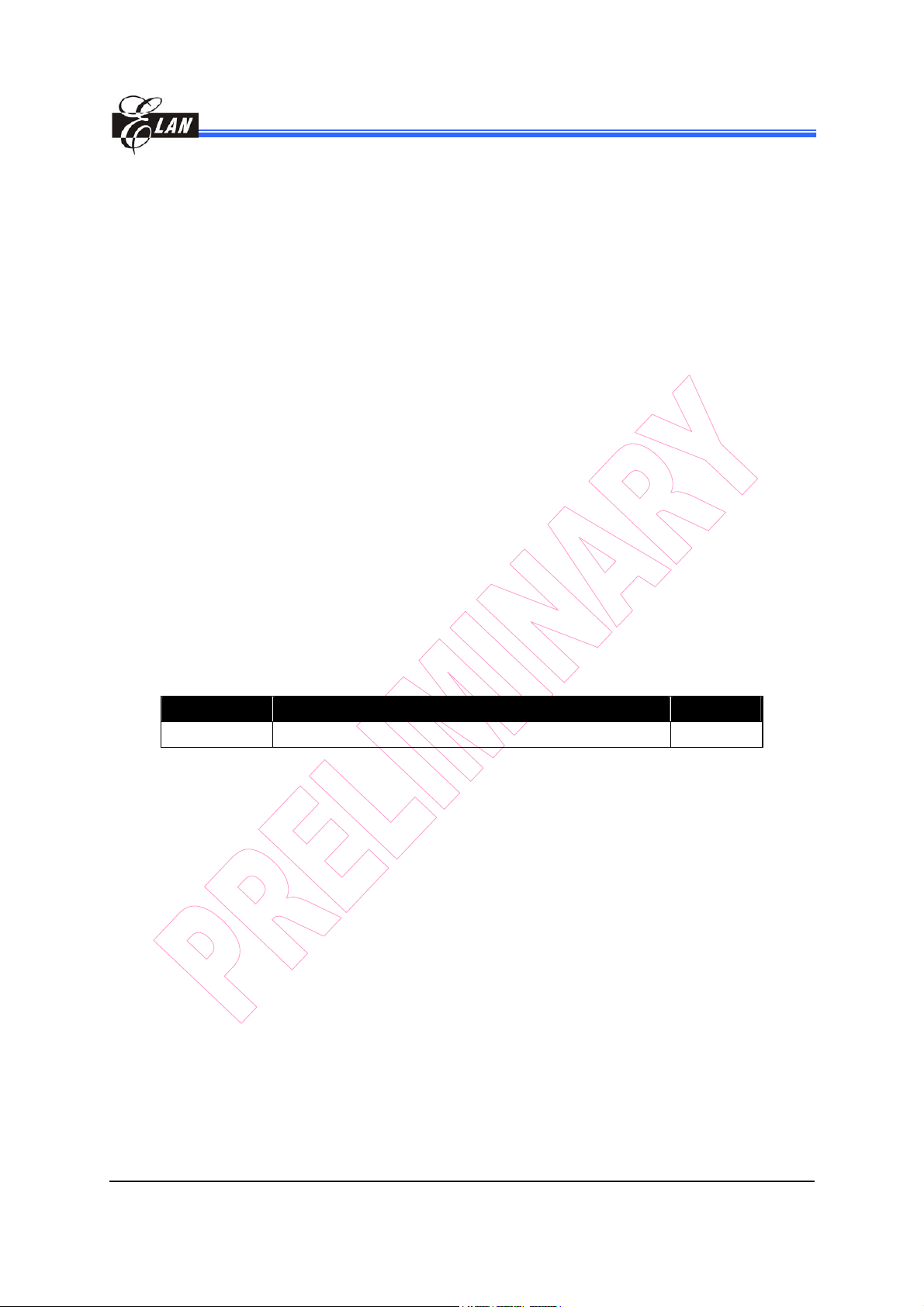

Specification Revision History

Doc. Version Revision Description Date

0.1 Initial Preliminary Version 2007/10/12

Product Specification (V0.1) 10.11.2007 • v

(This specification is subject to change without further notice)

Page 6

Contents

vi • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 7

1 General Description

The EPH3600 is an 8-bit RISC MCU embedded with following:

10 bits SAR A/D converter with touch screen controller

One 16-bit general timer with capture and event counter functions,

Two 8-bit timers IR generator

EL timer Watchdog timer

SPI UART

One current D/A.

Moreover, the EPH3600 is equipped with a large size user RAM and program/data

memory. The MCU is most suitable for products involving handwriting recognition

application that requires high performance with low cost solution; such as SMS,

Stylus Remote Controller, mobile phones, handwriting input device, etc.

The MCU’s core is ELAN’s second generation RISC (RISC II) based IC. The core is

specifically designed to provide a low power consumption portable device. It

supports FAST, SLOW, and Idle mode, as well as Sleep mode for low power

consumption application.

EPH3600

RISC II Series Microcontroller

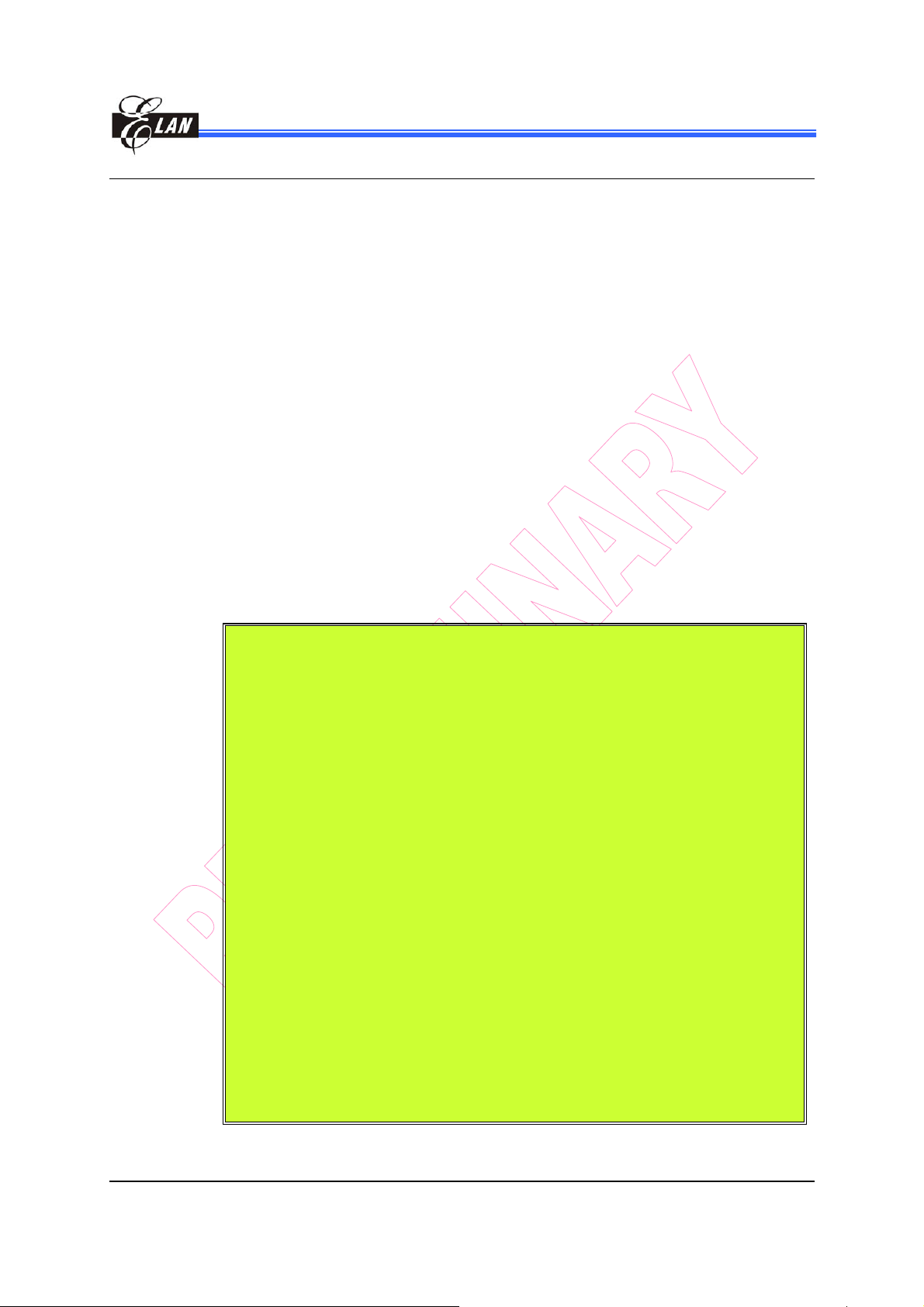

IMPORTANT NOTES

■ Do not use Register BSR (05h) Bit 7 ~ Bit 5

■ Do not use Register BSR1 (07h) Bit 7 ~ Bit 5

■ Do not use Special Register (04h)

■ Do not use Special Register (1Bh)

■ Do not use Special Register (1Ch)

■ Do not use Special Register (1Fh)

■ Do not use Special Register (32h)

■ Do not use Special Register (33h)

■ Do not use Special Register (37h)

■ Do not use Special Register (38h)

■ Do not use Special Register (39h)

■ Do not use Special Register (45h)

■ Do not use Special Register (46h)

■ Do not use Special Register (47h)

■ Do not use Special Register (4Fh)

■ Do not use Special Register (50h)

■ Do not use Special Register (51h)

■ Do not use Special Register (52h)

■ Do not use Special Register (53h)

■ Do not use JDNZ and JINZ at FSR1 (09h) special register

■ Do not use Register TABPTRH (0Dh) Bit 6

Product Specification (V0.1) 10.11.2007 • 1

(This specification is subject to change without further notice)

Page 8

EPH3600

RISC II Series Microcontroller

1.1 Applications

Handwriting Recognition

Dictionary, Data Bank

Stylus Remote Controlller

2 Features

2.1 MCU Features

8-bit RISC MCU

8×8 multiplier with controllable signed or unsigned operation

Operating voltage and speed: 16MHz~11MHz @ 2.9V~3.6V, 10MHz @

2.2V~3.6V, 4MHz @ 1.6V~3.6V

One Instruction cycle time = 2 × System clock time

Program ROM addressing: 16K words maximum

Data ROM addressing: 256K words maximum

128 bytes un-banked RAM including special registers and common registers

32×128 bytes banked RAM

RAM stack has a maximum of 128 levels

Table Look Up function is fast and highly efficient when implemented with Repeat

instruction

Register-to-Register move instruction

Compare and Branch in one instruction (2 cycles)

Single Repeat function (256 repeat times maximum)

Decimal Add & Sub instruction

Full range Call and Jump capability (2 cycles)

2.2 Peripheral

One input port (Port A) and 24 gene ral I/O pins (Port B, Port C, Port D)

1-channel Speech Synthesizer

16-bit timer (Timer 0) with capture and ev ent counter functions

8-bit timer (Timer 1) with wake-up function

8-bit timer (Timer 2)

8-bit IR generator

2 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 9

6-bit EL Timer output

A current D/A for speech application

8-bit Watchdog Timer

10 bits resolution SAR A/D converter with 6 channels general analog input and 2

channels for touch panel application

SPI (Serial Peripheral Interface)

UART (Universal Asynchronous Receiver and Transmitter)

2.3 Internal Specification

Watchdog Timer with on-chip RC oscillator

MCU mode: Sleep Mode, Idle Mode, Slow Mode, and Fast Mode

Supports either RC oscillation or crystal oscillation system clock

EPH3600

RISC II Series Microcontroller

PLL can be turned on at Fast Mode, and controlled by PEN bit when MCU is in

Slow Mode or Idle Mode

MCU Wake-up function includes input wake up, Ti mer 1 wake up, touch panel

wake up, SPI wake up, and A/D wake up

MCU interrupt function includes Input Port interrupt, Touch Panel interrupt,

Capture interrupt, Speech Timer interrupt, Timer Interrupt (Timers 0~2), A/D

interrupt, SPI interrupt, and UART interrupt

MCU reset function includes power-on reset, RSTB pin reset, and Watchdog

timer reset

2.4 Elan Software Support (Option)

Hand writing recognition core

1-channel Speech

ADPCM decoder

ADPCM encoder

Product Specification (V0.1) 10.11.2007 • 3

(This specification is subject to change without further notice)

Page 10

EPH3600

RISC II Series Microcontroller

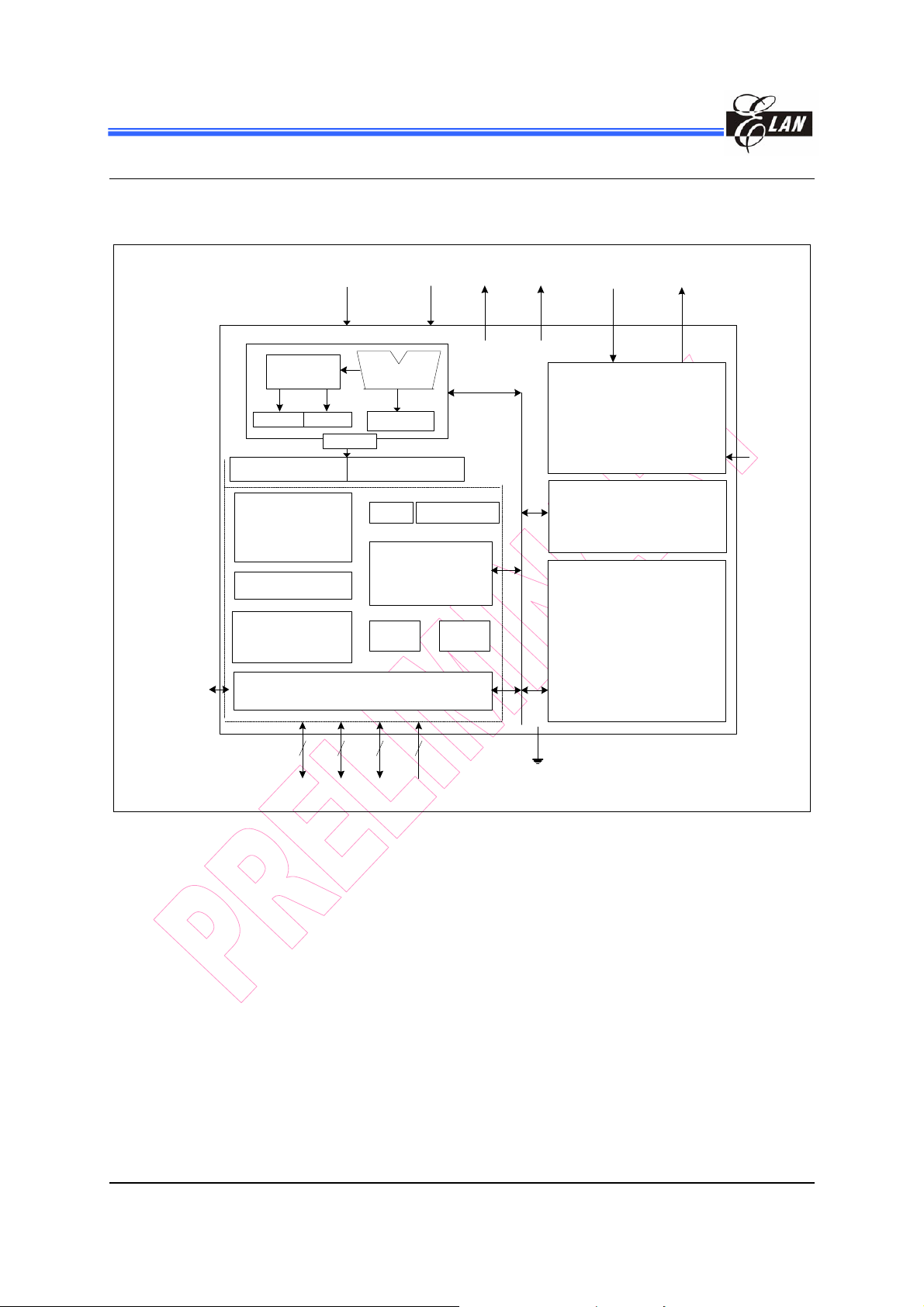

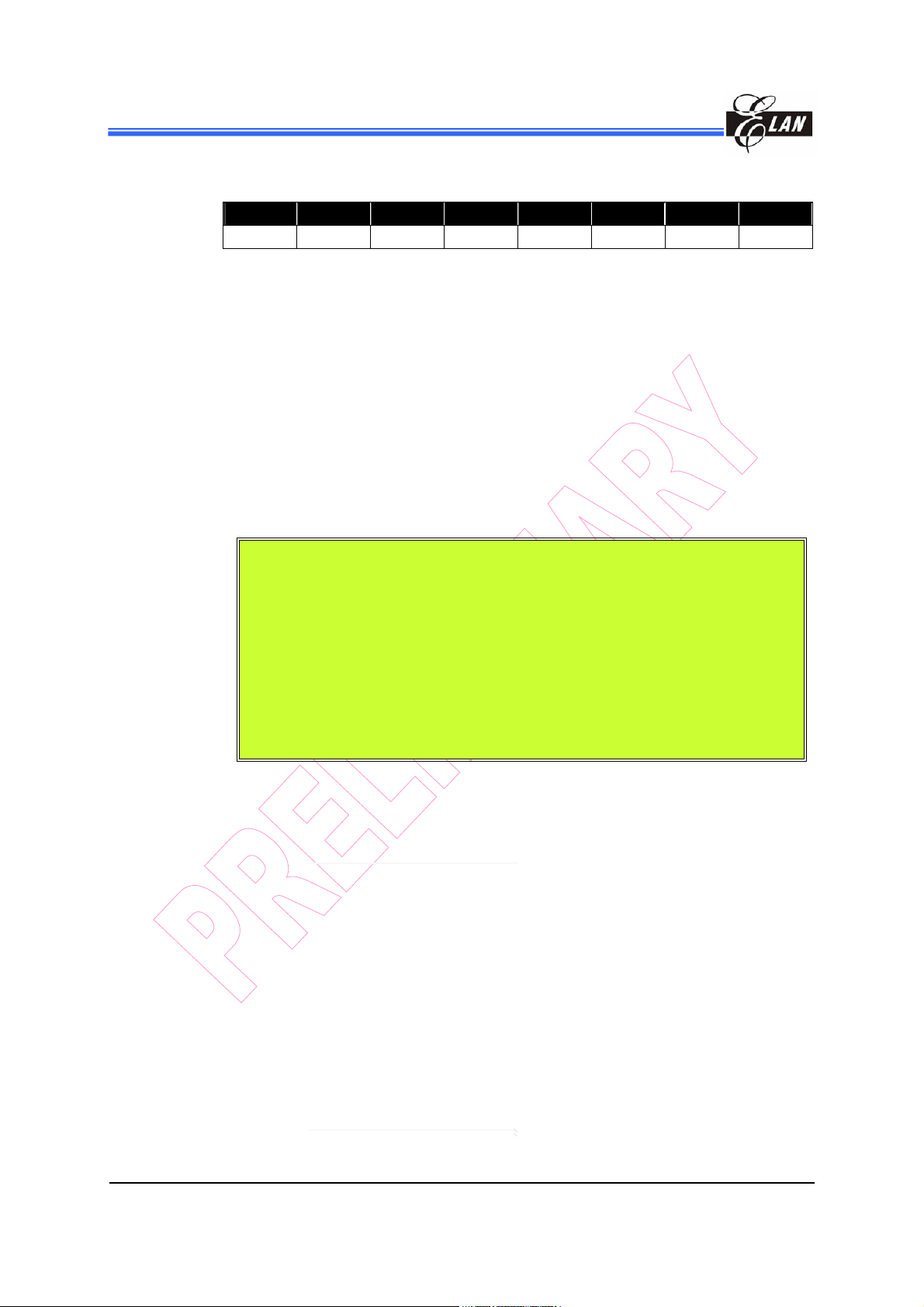

3 Block Diagram

VREX

RSTB TEST VDD OSCI OSCO

8 x 8 Mul

PRODH PRODL

PRODL

Addressing Co n tro l U n it

Speech Synthesizer

D/A

SAR A/D

I/O Control

ALU

Shifter

UART

Timer 0 ~ Timer 2 /

EL / WDT Timer

Key IO

AVDD

IR Generator

SPI

Timing Generator

PLLC

RAM

ROM

88

8

Po rtD PortC PortB P ortA

Figure 1-1 EPH3600 Block Diagram

4 • Product Specification (V0.1) 10.11.2007

8

VSS

(This specification is subject to change without further notice)

Page 11

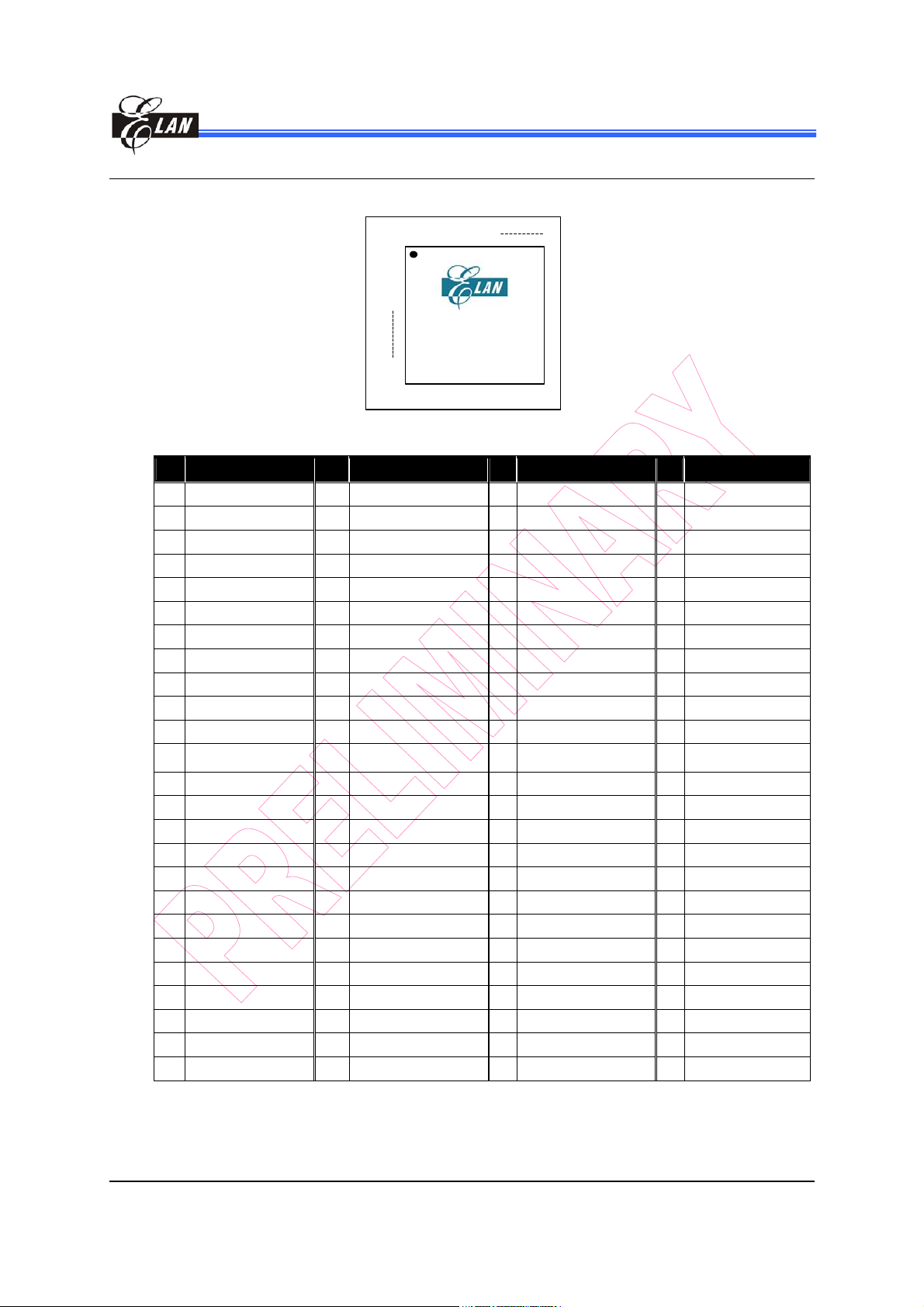

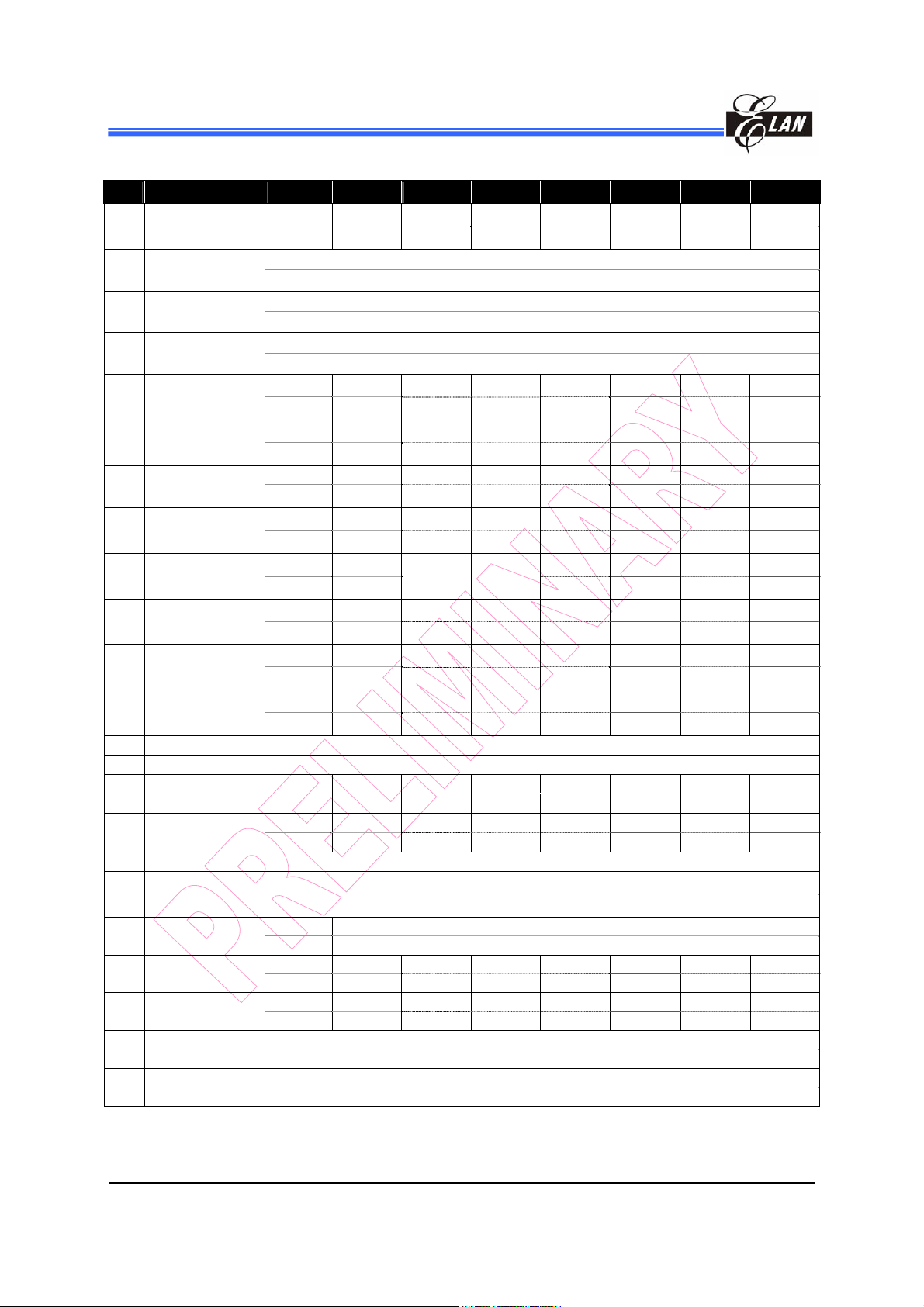

4 Pin Assignment

No. Pin Name No. Pin Name No. Pin Name No. Pin Name

1 N.C. 26 Port C.6 (YN) 51 N.C. 76 N.C.

2 N.C. 27 Port C.5 (ADIN3/XP) 52 N.C. 77 N.C.

3 N.C. 28 Port C.4 (ADIN4/YP) 53 PD.6 (SPISDO) 78 N.C.

4 N.C. 29 N.C. 54 PD.7 (SPISDI) 79 N.C.

5 N.C. 30 N.C. 55 Port A.0 80 N.C.

6 N.C. 31 Port C.3 (ADIN5) 56 Port A.1 81 N.C.

7 N.C. 32 Port C.2 (ADIN6) 57 Port A.2 82 N.C.

8 N.C. 33 Port C.1 (ADIN7) 58 Port A.3 83 N.C.

9 N.C. 34 Port C.0 (ADIN8) 59 Port A.4 84 N.C.

10 N.C. 35 Port B.0 60 Port A.5 85 N.C.

11 N.C. 36 Port B . 1 ( DAO) 61 Port A.6 86 N.C.

12 N.C. 37 Port B.2 (IROT) 62 Port A.7 87 N.C.

13 N.C. 38 Port B.3 (EL CK) 63 N.C. 88 N.C.

14 N.C. 39 Port B.4 (CHOP) 64 N.C. 89 N.C.

15 N.C. 40 Port B.5 (EVIN/CPIN) 65 N.C. 90 N.C.

16 N.C. 41 Port B.6 (UTXD) 66 N.C. 91 N.C.

17 N.C. 42 Port B.7 (URXD) 67 N.C. 92 N.C.

18 TEST 43 VDD 68 N.C. 93 N.C.

19 PLLC 44 VSS 69 N.C. 94 N.C.

20 OSCI 45 Port D.0 70 N.C. 95 N.C.

21 OSCO 46 Port D.1 71 N.C. 96 N.C.

22 RSTB 47 Port D.2 72 N.C. 97 N.C.

23 VREX 48 Port D.3 73 N.C. 98 N.C.

24 AVDD 49 PD.4 (SPISS) 74 N.C. 99 N.C.

25 Port C.7 (XN) 50 PD.5 (SPISCK) 75 N.C. 100 N.C.

EPH3600

RISC II Series Microcontroller

100 99 98 ......

1

2

3

EPH3600

(top view)

Product Specification (V0.1) 10.11.2007 • 5

(This specification is subject to change without further notice)

Page 12

EPH3600

RISC II Series Microcontroller

5 Pin Description

5.1 MCU System Pins (9 Pins)

Name

AVDD

VSS

VDD

VSS

RSTB I

TEST I Normally connected to VSS. Reserved for testing use.

OSCI/RC

OSCO

PLLC I

VREX I/O

I/O/P

Type

P

P

I

O

Description

Analog positive power supply. The range is 2.2V~3.6V. Connect to VSS

through capacitors (0.1µF).

Digital and Analog positive power supply. Range is 2.2V~3.6V. Connect

to VSS through capacitor (0.1µF).

System reset input with built-in pull-up resistor (100KΩ Typical).

Low: RESET asserted

High: RESET released

RC or Crystal selection by Code Option.

32768 Hz oscillator pins. Connect to VSS through capacitor (20pF)

RC oscillator connector pin. Connect to VDD through a resistor (2MΩ).

PLL capacitor connector pin. Connect to VSS through capacitor

(0.047µF).

External or internal reference voltage for A/D converter. Connect to VSS

through capacitor (0.1µF).

6 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 13

5.2 I/O Ports (32 Pins)

EPH3600

RISC II Series Microcontroller

Name

Port A I

Port B

Port C

Port D

I/O/P

Type

I/O

I

O

I

O

O

O

O

O

I/O

O

O

I

I

I

I

I

I

I/O

I

O

I/O

I

I/O

Description

General Input port for special functions, i.e., Wake-up and

Interrupt

Bit 7: ON key input

Bits 6~0: Key matrix input pins

General Input/Output port

Bit 7: UART Rx pin

Bit 6: UART Tx pin

Bit 5: Event Counter/Capture input pin

Bit 4: EL CHOP output pin

Bit 3: EL CK output pin

Bit 2: IR output pin

Bit 1: Current D/A output pin

Bit 0: I/O pin

General Input/Output port

Bit 7: Touch screen X direction negative pin

Bit 6: Touch screen Y direction negative pin

Bit 5: Touch screen X direction positive pin & A/D input Channel 3

Bit 4: Touch screen Y direction positive pin & A/D input Channel 4

Bit 3: A/D input Channel 5

Bit 2: A/D input Channel 6

Bit 1: A/D input Channel 7

Bit 0: A/D input Channel 8

General Input/Output port

Bit 7: Serial data input pin

Bit 6: Serial data output pin

Bit 5: Serial clock Input/Output pin

Bit 4: /Slave Select pin

Bit 3~0: I/O pin

Product Specification (V0.1) 10.11.2007 • 7

(This specification is subject to change without further notice)

Page 14

EPH3600

RISC II Series Microcontroller

6 Code Options

The Code Options are located at Address 0x000C~0x0013 of the Program ROM:

Oscillator (OSCSEL) : “RC” oscillator

“Crystal” oscillator (Default)

Initial mode after reset : “Slow” mode

“Fast” mode (Default)

Port C.7 function selection bit : “XN for touch panel”

“General I/O function” (Default)

Port C.6 function selection bit : “YN for touch panel”

“General I/O function” (Default)

Port C.5 function selection bit : “XP for touch panel/ADIN3”

“General I/O function” (Default)

Port C.4 function selection bit : “YP for touch panel/ADIN4”

“General I/O function” (Default)

Port C.3 function selection bit : “ADIN5”

“General I/O function” (Default)

Port C.2 function selection bit : “ADIN6”

“General I/O function” (Default)

Port C.1 function selection bit : “ADIN7”

“General I/O function” (Default)

Port C.0 function selection bit : “ADIN8”

“General I/O function” (Default)

DAC function selection bits:

DAC Function Selection Port B.0 and Port B.1 Function

DAC is used Port B.1 is DAO for D/A, Port B.0 is General I/O

DAC usage is prohibited General I/O (Default)

Select UART standard baud rate : “PLL frequency is 9.83MHz” (Default)

“PLL frequency is 14.745MHz”

Port A pull-h and DAC control bit: “PAPUR register, DAC bit ineffective” (Default)

“PAPUR register, DAC bit effective”

EL Output TIming : “Output is from carrier gating with 128Hz and CKP” (Default)

“CHOP output is directly from carrier”

8 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 15

7 Function Description

7.1 Reset Function

A Reset can be caused by:

Power-on voltage detector reset and power-on reset

WDT timeout

RSTB pin pull low

VDD

EPH3600

RISC II Series Microcontroller

P o w e r-o n R e se t

RSTB

+

0.1uF

WDT Reset

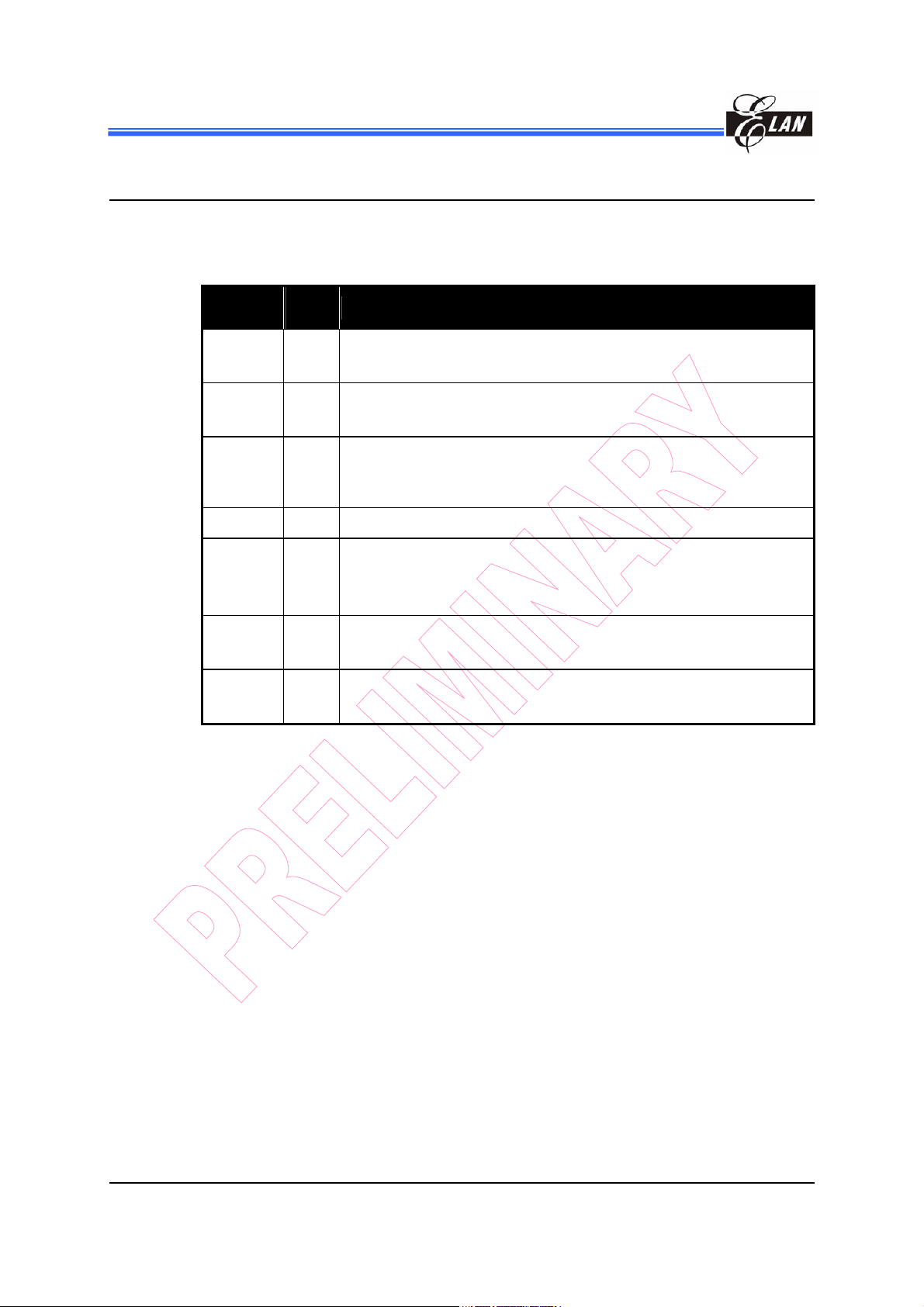

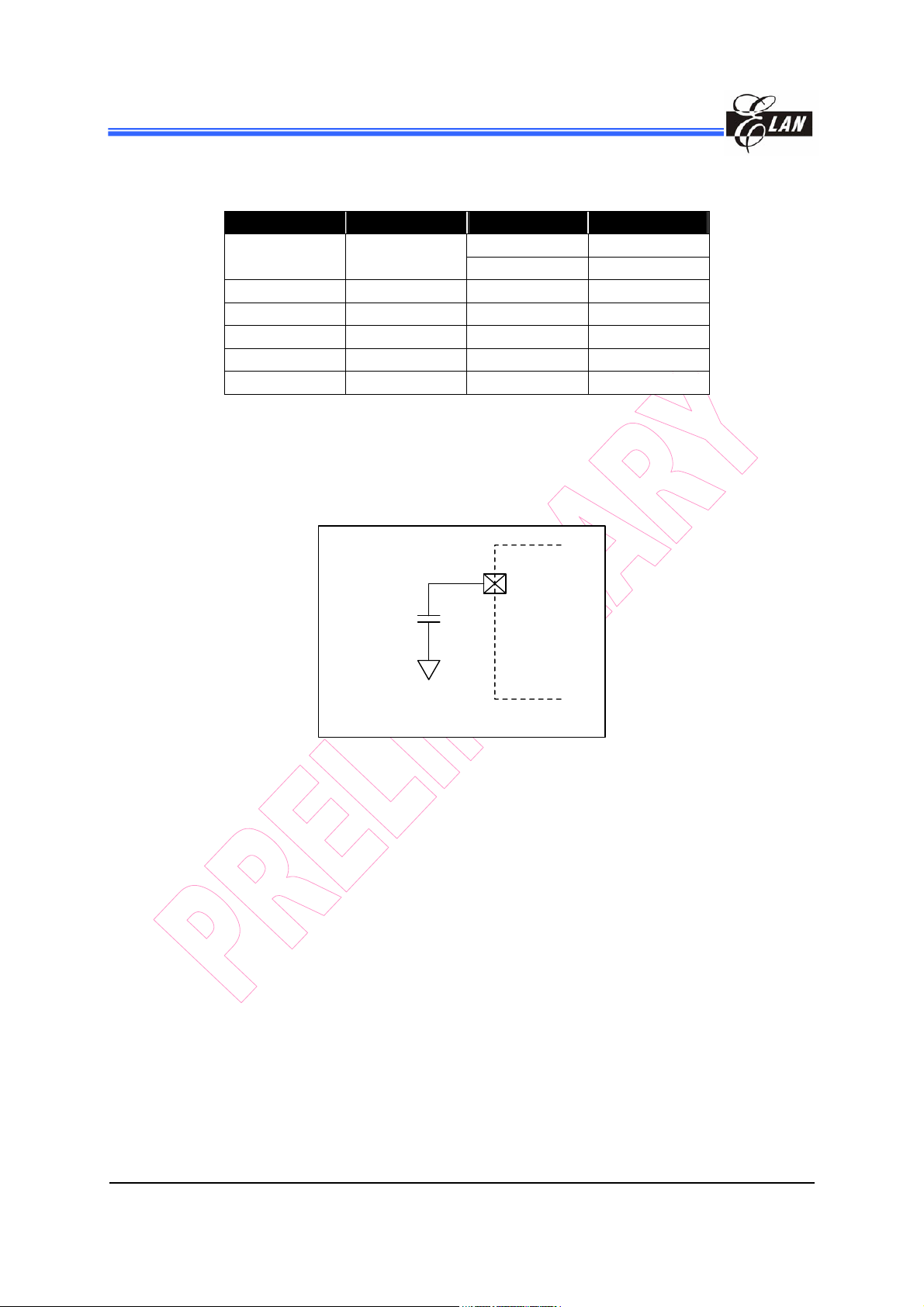

Figure 7-1 On-chip Reset Circuit

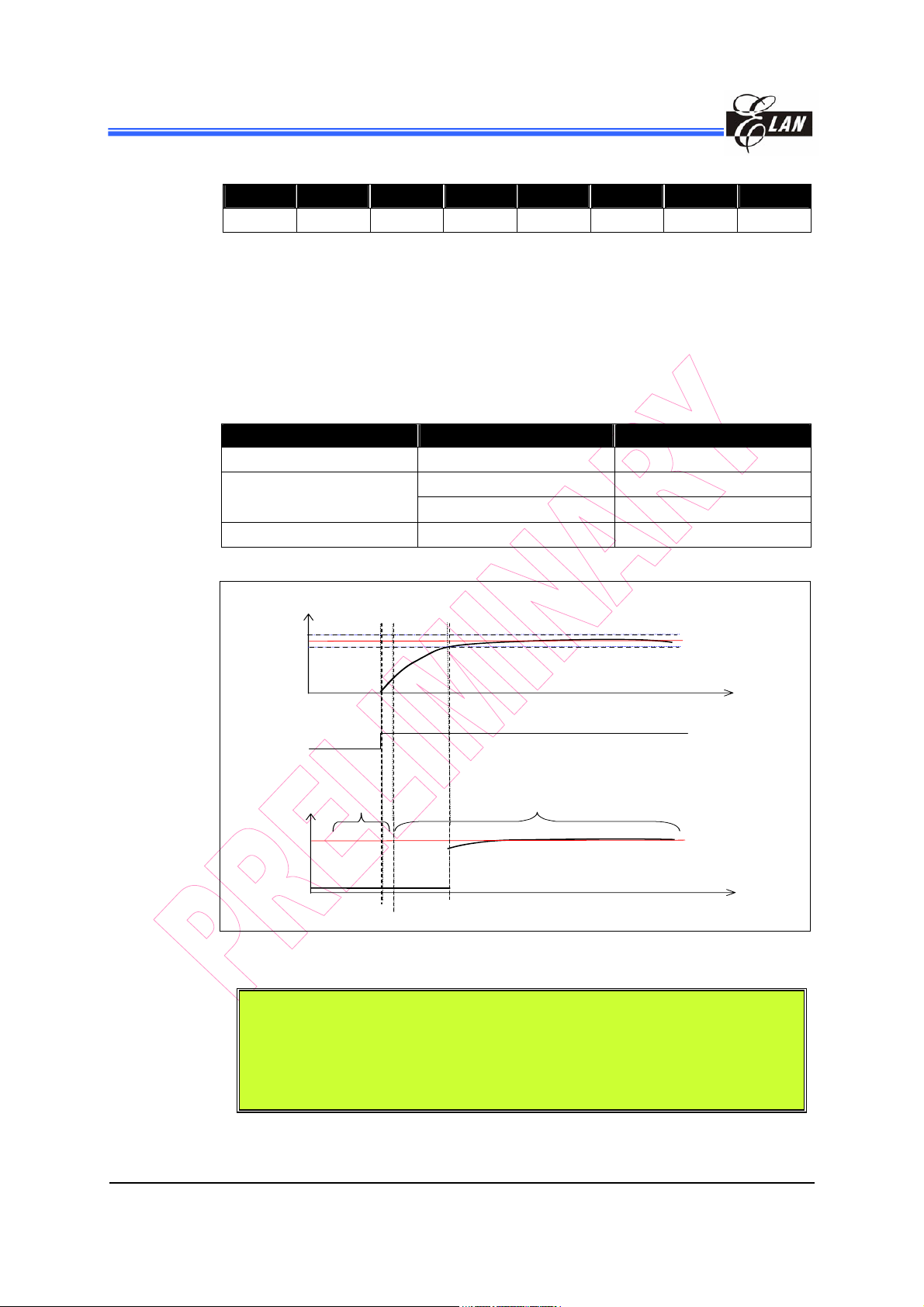

7.1.1 Power-up and Reset Timing

VDD

RSTB

Tpwr

OSC

Twup

CPU Work

/Chip R eset

Twup1

Figure 7-2 Power-up and Reset Timing

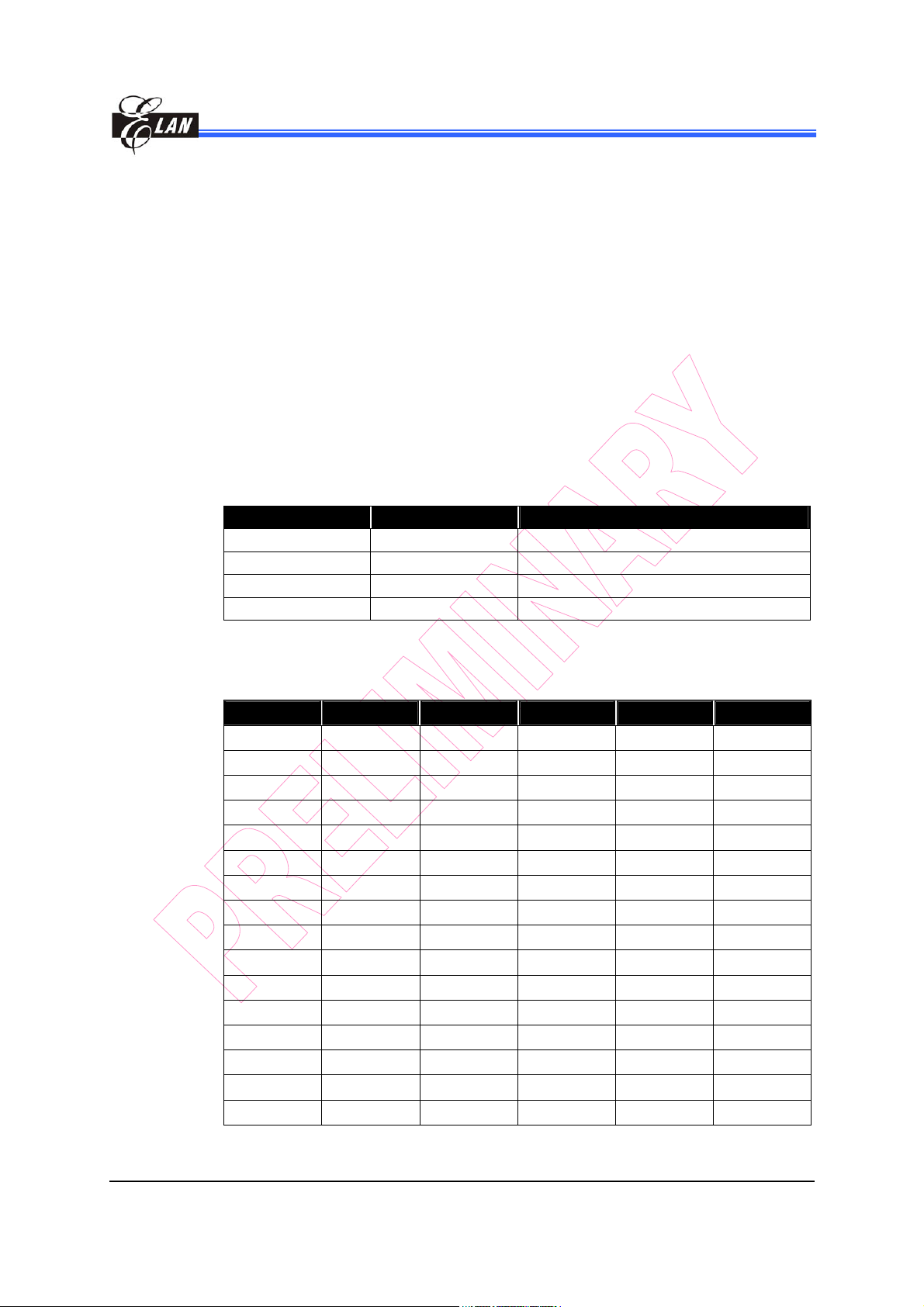

Symbol Characteristics Min. Typical Max. Unit

Tpwr Oscillator start up time 100 226 300 ms

Twup CPU warm up time 260 340 550 ms

Twup1 CPU reset time 18 22 44 ms

Product Specification (V0.1) 10.11.2007 • 9

(This specification is subject to change without further notice)

Page 16

EPH3600

RISC II Series Microcontroller

Status (R0Fh)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

/TO /PD SGE SLE OV Z DC C

Bit 0 (C): Carry flag or inverse of Borrow flag (B)

When in SUB operation, borrow flag is indicated by the inverse of carry

bit (B = /C)

Bit 1 (DC): Auxiliary carry flag

Bit 2 (Z): Zero flag

Bit 3 (OV): Overflow flag. Use in signed operation when Bit 6 carry into or borrow

from a signed bit (Bit 7).

Bit 4 (SLE): Computation result is less than or equal to zero (Negative value) after

a signed arithmetic. It is only affected by a HEX arithmetic instruction.

Bit 5 (SGE): Computation result is greater than or equal to zero (Positive value) after

a signed arithmetic. It is only affected by a HEX arithmetic instruction.

NOTE

1. When OV=1 after a signed arithmetic, user can check the SGE and SLE bits to

determine whether an overflow (carry into a signed bit) or underflow (borrow from

a signed bit) occurs.

OV=1 and SGE=1 → overflow occurs

OV=1 and SLE=1 → underflow occurs

2. When overflow occurs, you should clear the MSB of the Accumulator in order to

get the correct value.

When underflow occurs, you should set the MSB of the Accumulator in order to

get the correct value.

Example 1: ADD a positive value to another positive value, and ACC signed bit will

be affected.

MOV ACC, #60h ; Signed number +60h

ADD ACC, #70h ; +60h ADD WITH +70h

After instruction: ACC = 0D0h

SGE=1, means the result is greater than or equal to 0 (positive value)

OV=1, means the result is carry into a signed bit (Bit 7), overflow occurs.

Correct the signed bit: ACC = 50h (Clear the signed bit)

The actual result = +80h (OV=1) + 50h = +0D0h

Example 2: SUB a positive value from a negative value, and ACC signed bit will be

affected.

MOV ACC, #50h ; Signed number +50h

SUB ACC, #90h ; +50h SUB from –70h (Signed

number of 90h)

10 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 17

EPH3600

RISC II Series Microcontroller

After instruction: ACC = 40h

SLE=1, means the result is less than or equal to 0 (negative value)

OV=1, means the result is borrow from a signed bit (Bit 7), underflow

occurs.

Correct the signed bit: ACC = 0C0h (Set the signed bit)

The actual result = –80h (OV=1) + 0C0h (signed number of 0C0h) = 40h

Bit 6 (/PD): Reset to 0 when entering SLEEP mode. Set to 1 by “WDTC” instruction,

power-on reset, or during a Reset pin low condition.

Bit 7 (/TO): Reset to 0 during WDT time out reset. Set to 1 by “WDTC” instruction,

entering SLEEP MODE, power-on reset, or during a Reset pin low

condition.

When a reset occurs, the special function register will be reset to its initial value

except for the /TO and /PD bits of the STATUS register.

Bit 7 (/TO) Bit 6 (/PD) Event

0 0 WDT time out reset from SLEEP mode

0 1 WDT time out reset (not SLEE P mode)

1 0 Reserved

1 1 Power on or RSTB pin low condition

7.1.2 Register Initial Values

Special Register:

Addr. Name Initial Value Addr. Name Initial Value

00h INDF0 −−−− −−−−

01h FSR0 0000 0000 11h PRODL uuuu uuuu

02h PCL 0000 0000 12h PRODH uuuu uuuu

03h PCM 0000 0000 13h ADOTL 0−0− −0uu

04h (Not Used) −−−− −−−− 14h ADOTH uuuu uuuu

05h BSR −−−0 0000 15h UARTTX ×××× ××××

06h STKPTR 0000 0000 16h UARTRX ×××× ××××

07h BSR1 −−−0 0000 17h Port A ×××× ××××

08h INDF1 −−−− −−−−

09h FSR1 1000 0000 19h Port C ×××× ××xx

0Ah ACC ×××× ×××× 1Ah Port D ×××× xxxx

0Bh TABPTRL 0000 0000 1Bh (Not Used) −−−− −−−−

0Ch TABPTRM 0000 0000 1Ch (Not Used) −−−− −−−−

0Dh TABPTRH 0−00 0000 1Dh R1D ×××x x×××

0Eh CPUCON 0−−0 000c

0Fh STATUS cu×× ××××

1

10h TRL2 uuuu uuuu

1

18h Port B ×××x x×××

2

1Eh R1E ×××x x×××4

3

1Fh (Not Used) −−−− −−−−

4

Product Specification (V0.1) 10.11.2007 • 11

(This specification is subject to change without further notice)

Page 18

EPH3600

RISC II Series Microcontroller

Control Register:

Addr. Name Initial Value Addr. Name Initial Value

20h PFS 0010 0000 3Bh PCCON 0000 0000

21h STBCON 0−−− −−−− 3Ch PLLF ×××× ××××

22h INTCON 0000 0000 3Dh T0CL 0000 0000

23h INTSTA 0000 0000 3Eh T0CH 0000 0000

24h TRL0L uuuu uuuu 3Fh SPICON 0000 0000

25h TRL0H uuuu uuuu 40h SPISTA −−00 0000

26h TRL1 uuuu uuuu 41h SPRL ×××× ××××

27h TR01CON 0000 0000 42h SPRM ×××× ××××

28h TR2CON 0000 0000 43h SPRH ×××× ××××

29h TRLIR uuuu uuuu 44h SFCR 0000 0000

2Ah ELCON 00uu uuuu 45h (Not Used) ×××× ××××

2Bh POST_ID −−11 −−00 46h (Not Used) ×××× ××××

2Ch ADCON 0101 0000 47h (Not Used) ×××× ××××

2Dh PAINTEN 0000 0000 48h SPHDR 0000 0000

2Eh PAINTSTA 0000 0000 49h SPHTCON 0000 0000

2Fh PAWAKE 0000 0000 4Ah SPHTRL 0000 0000

30h UARTCON 0000 0010 4Bh VOCON 0−−−000

31h UARTSTA 0000 0000 4Ch TR1C 1111 1111

32h (Not Used) −−−− −−−− 4Dh TR2C 1111 1111

33h (Not Used) −−−− −−−− 4Eh ADCF uuuu uuuu

34h DCRB 1111 1111 4Fh (Not Used) −−−− −−−−

35h DCRC 1111 1111 50h (Not Used) −−−− −−−−

36h DCRDE −−−− 0011 51h (Not Used) −−−− −−−−

37h (Not Used) −−−− −−−− 52h (Not Used) −−−− −−−−

38h (Not Used) −−−− −−−− 53h (Not Used) −−−− −−−−

39h (Not Used) −−−− −−−− 54h PAPUR 0000 0000

3Ah PBCON 0000 0000 55h PACON −−−− 0110

Legend: “×” = unknown “−” = unimplemented, read as “0”

“u” = unchanged “c” = value depending on the condition

1

Not a physical register.

2

Bit 0 (MS0) of RE (CPUCON) is reloaded from “INIM” bit of code option when the

MCU is reset.

3

If it is a power-on reset or RSTB pin is at low condition, the /TO bit and /PD bit of RF

(STATUS) are set to “1”. If it is a WDT time out reset, the /TO bit is cleared and /PD

bit is unchanged.

4

R1D, R1E are generated register RAM.

5

PAPUR can be used only by the code option setting.

5

12 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 19

××=

××=

7.2 Oscillator System

EPH3600

RISC II Series Microcontroller

OSCI

OSCO

32.8kHz

RC/Crystal

Osc.

OSCSEL

of

Code Option

PLL

PEN

Fosc

A/D Clock

Factor

F

PLL

FSS

0

1

MS0

Fsystem

F

A/D

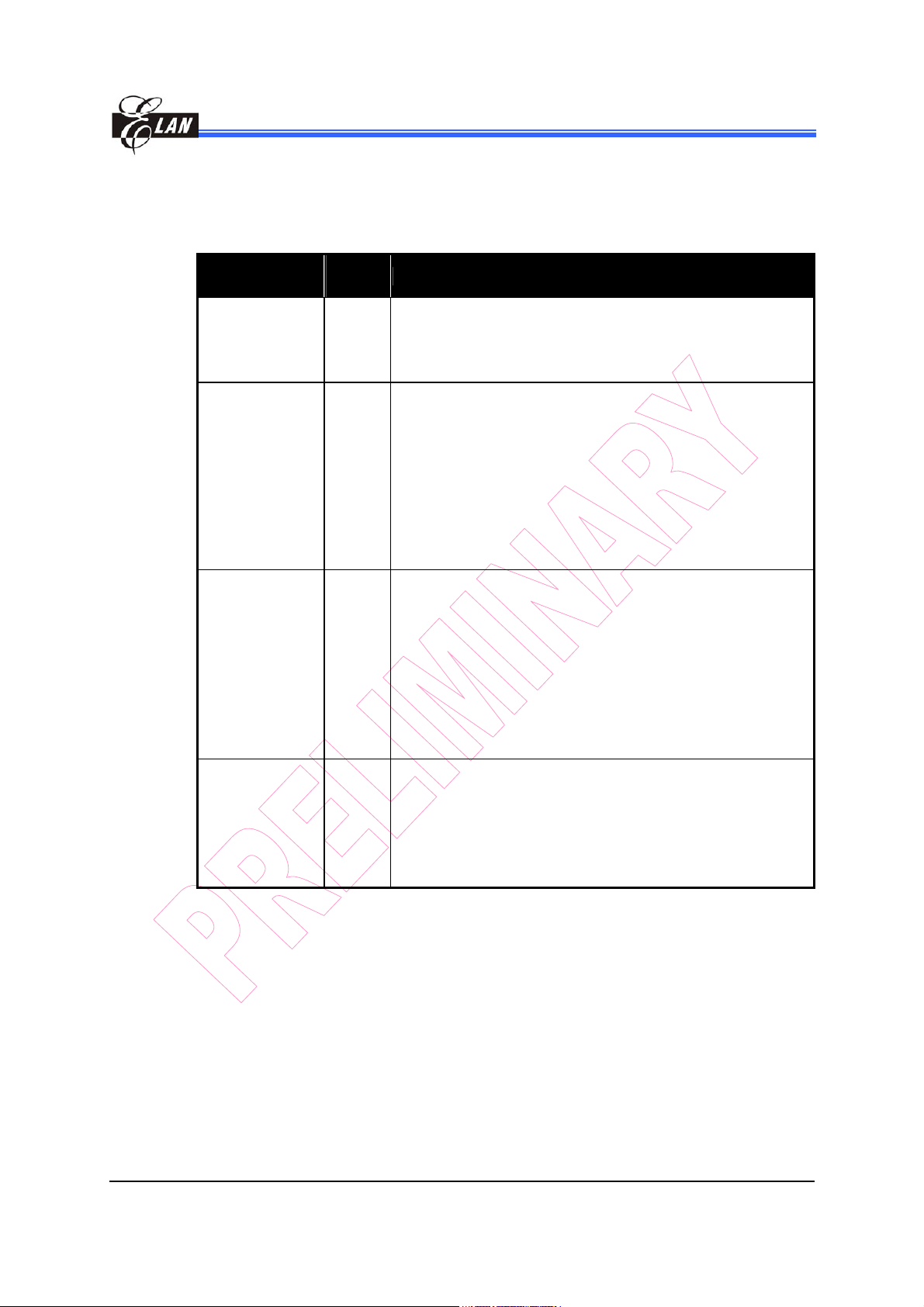

Figure 7-3 Oscillator System Function Block Diagram

7.2.1 32.768kHz Crystal or 32.8kHz RC

For the 32.8kHz RC oscillator, connect a 2MΩ pull-up resistor to OSCI pin and the

OSCO pin should be floating.

For the 32.768kHz Crystal oscillator, connect the crystal between OSCI and OSCO

pins. Then connect the OSCI and OSCO pins to ground through a 20pF capacitor.

VDD

OSCI

2Mohm

OSCO

OSCI

OSCO

32.768kHz Crystal

Oscillator

32.8kHz RC Oscillator

Figure 7-4 Crystal and RC Oscillator Circuit Diagram

7.2.2 Phase Locked Loop (PLL)

PLLF (R3Ch): Store the actual PLL frequency value. It is used to check whether

the PLL frequency is stable or not.

2

PFS (R20h): Target PLL frequency select register. System clock can be fine

tuned from 0.983MHz to 16MHz. The initial value of the PFS

register after a chip reset is set at “20h” (F

2

arg

FPLLFF

OSCactual

=2.097 MHz)

PLL

FPFSF

OSCett

Product Specification (V0.1) 10.11.2007 • 13

(This specification is subject to change without further notice)

Page 20

EPH3600

RISC II Series Microcontroller

PFS Register Ftarget (MHz) PFS Register Ftarget (MHz)

0~14 N.A.1

15 0.983 122 7.995

31 2.032 137 8.978

46 3.015 150 9.83

61 3.998 153 10.027

76 4.981 255 16.712

1

PFS=0~14 is not available.

2

When UART is enabled, the system clock should be 9.83 MHz (PFS=150) or 14.745 MHz

(PFS=225).

The table is based on 32.768kHz oscillator frequency.

The Maximum range of PLL is 983 kHz ~ 16.712 MHz.

92 6.029

107 7.012

2

PLLC

0.047uF

PLL Osc illa t o r

Figure 7-5 PLL Oscillator Circuit Diagram

14 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 21

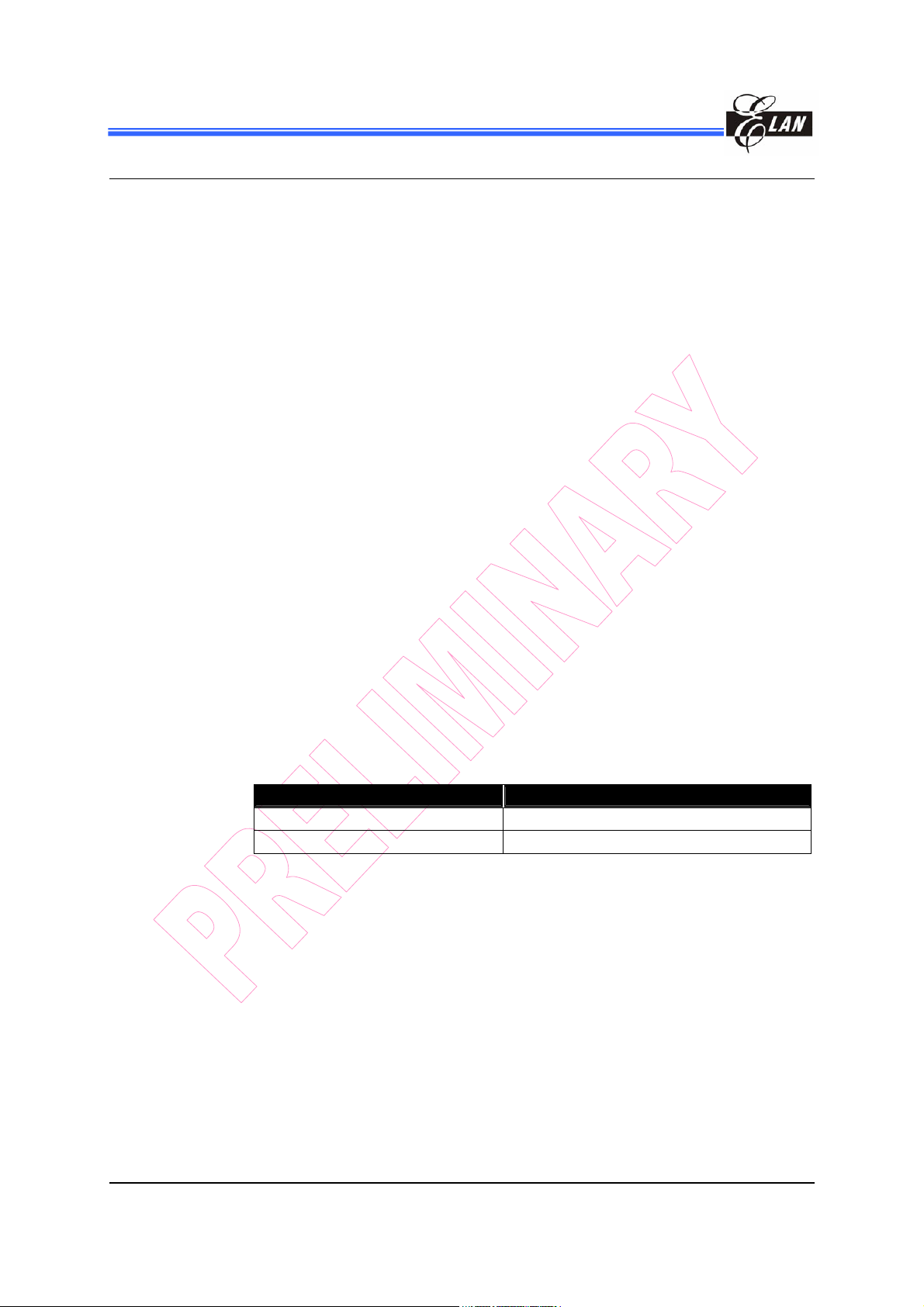

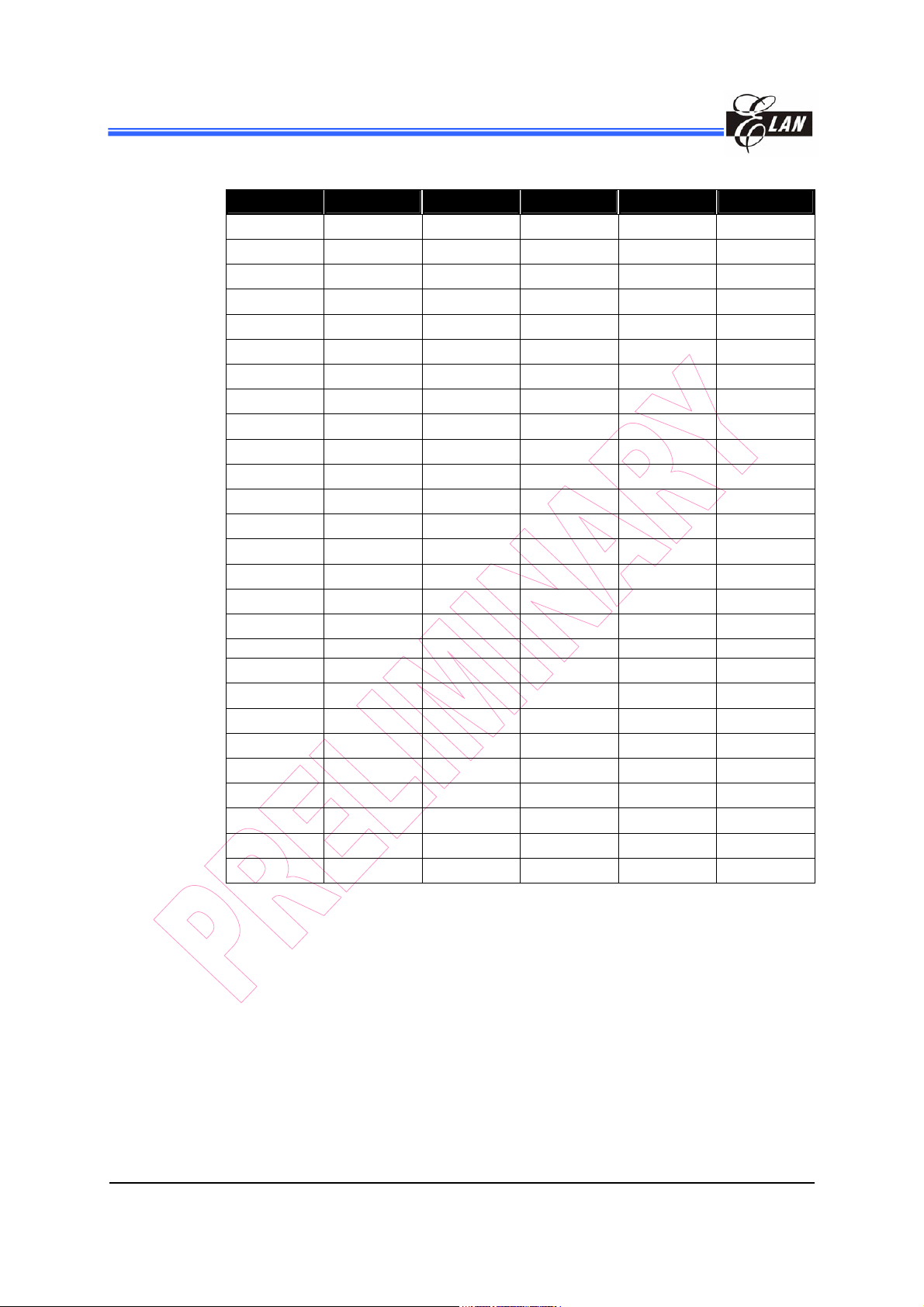

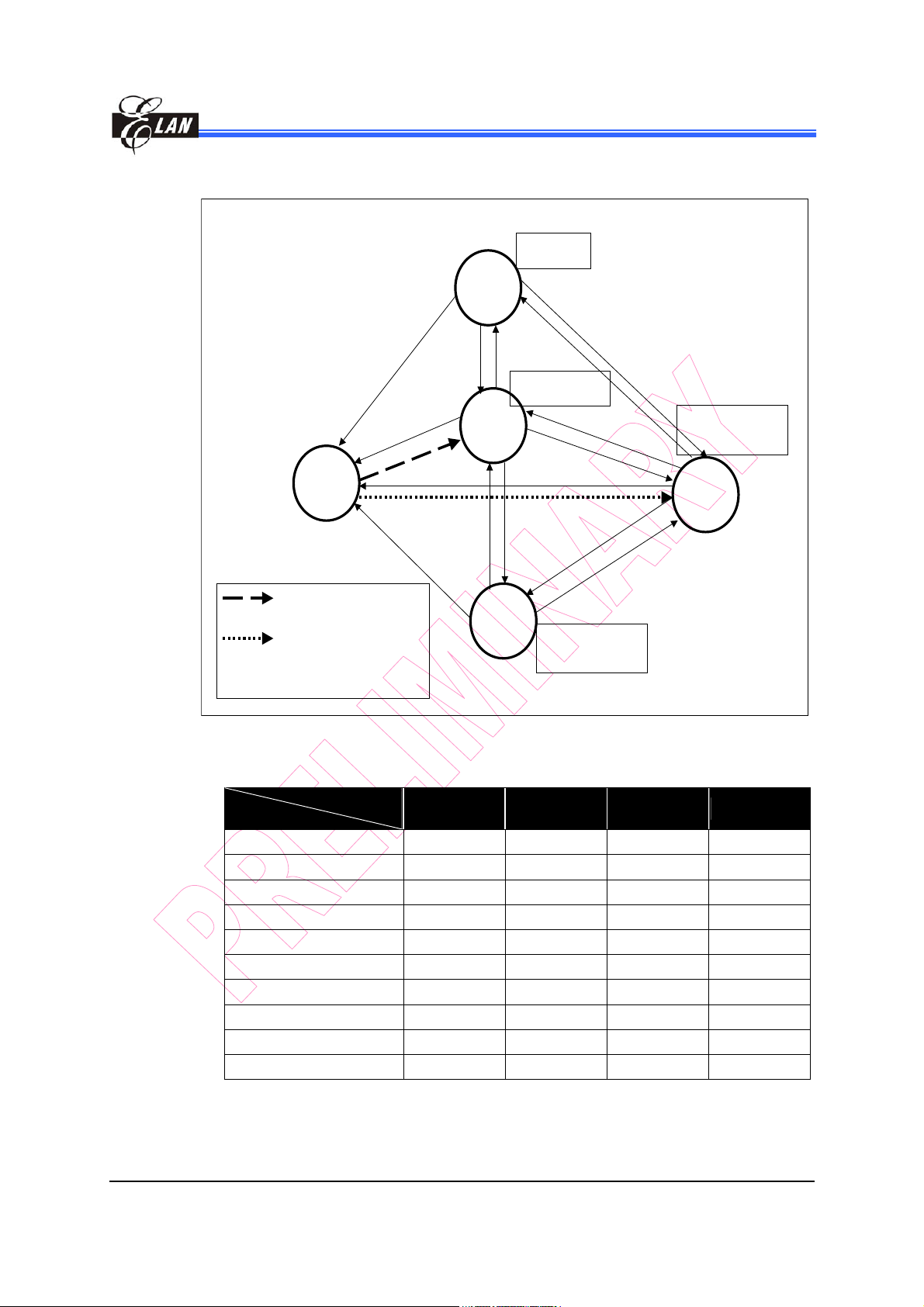

7.3 MCU Operation Mode

RESET

operation

FA S T MODE is th e in itial m o d e

after Reset

SLOW MODE is th e in itia l mode

after Reset

Select by IM bit of Code Option register

Reset

Reset

Reset Release

Wakeup

& MS0=1

Reset Release

Reset

SLEEP

MODE

(CPU stops)

MODE

Reset

wakeup

& MS0=1

MS1= 0 &

“SLEP”

32K OSC.:oscillating

PLL:turned on

FAST

MS1=1 &

“SLEP”

IDL E

MODE

(CPU stops)

32K OSC.:stop

PLL: stopped

Wakeup

& MS0=0

MS0=1

MS0=0

MS1=1 &

“SLEP”

32K O S C.:Oscillating

PEN=0->PLL stopped

PEN=1->PLL turned on

EPH3600

RISC II Series Microcontroller

MS1=0 &

“SLEP”

Wakeup

& MS0=0

32K OSC.:oscil la ti n g

PEN=0->PL L : stopped

PEN=1->PL L turned on

SLOW

MODE

Figure 7-6 Operation Block Diagram

MCU Mode with Function Table:

Mode

Device

OSC (32.768kHz) × √ √ √

Fsystem × × From OSC From PLL

PLL × √ √ √

A/D conversion × √ 2 √ √

Timers 0~2, IR generator × √ √ √

INT × 1 × 1 √ √

SPI √ (slave) √ (slave) √ √

UART × × × √

Speech Synthesizer × × × √

Current D/A × × √ √

Legend: “ √ ” = function is available if enabled “ × ” = function is Not available

1

Interrupt flag will be recorded but not executed until the MCU wakes up.

2

It is recommended to operate the A/D converter in Idle mode to lower the noise couple from

the MCU clock.

SLEEP IDLE SLOW FAST

Product Specification (V0.1) 10.11.2007 • 15

(This specification is subject to change without further notice)

Page 22

EPH3600

RISC II Series Microcontroller

CPUCON (R0Eh):

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PEN - - SMCAND SMIER GLINT MS1 MS0

Sleep Mode: When MS1 bit is set to ‘0’ and “SLEP” instruction is ex ecuted, the

Idle Mode: When MS1 bit is set to ‘1’ and “SLEP” instruction is executed, the

Slow Mode: When MS0 bit is set to ‘0’, the MCU will enter into Slow mode.

Fast Mode: When MS0 bit is set to ‘1’, the MCU will enter into Fast mode.

PLL enable: It is only effective when the MCU is in Idle mode or SLOW mode.

MCU Mode PEN Bit PLL On/Off

SLEEP × Off

IDLE/SLOW

FAST × On

MCU will enter into Sleep mode.

MCU will enter into Idle mode.

0 Off

1 On

F

PLL

Target+5%

Target

T arget-5 %

Ts

FAS T M O D E

Ts

MS0

System

clock

Target

32.768K

0m s

SLOW

MODE

0m s

0.244ms

Figure 7-7 MCU Operation Timing Diagram

NOTE

1. Switch from Slow mode to Fast mode at Time = 0ms

2. The System clock will switch to FPLL after 8 oscillation clocks, and the system

clock will then increase to about hundreds of kHz.

3. The PLL frequency will be stable (±5%) at Time = Ts (2ms ~ 5ms).

Time

Tim e

16 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 23

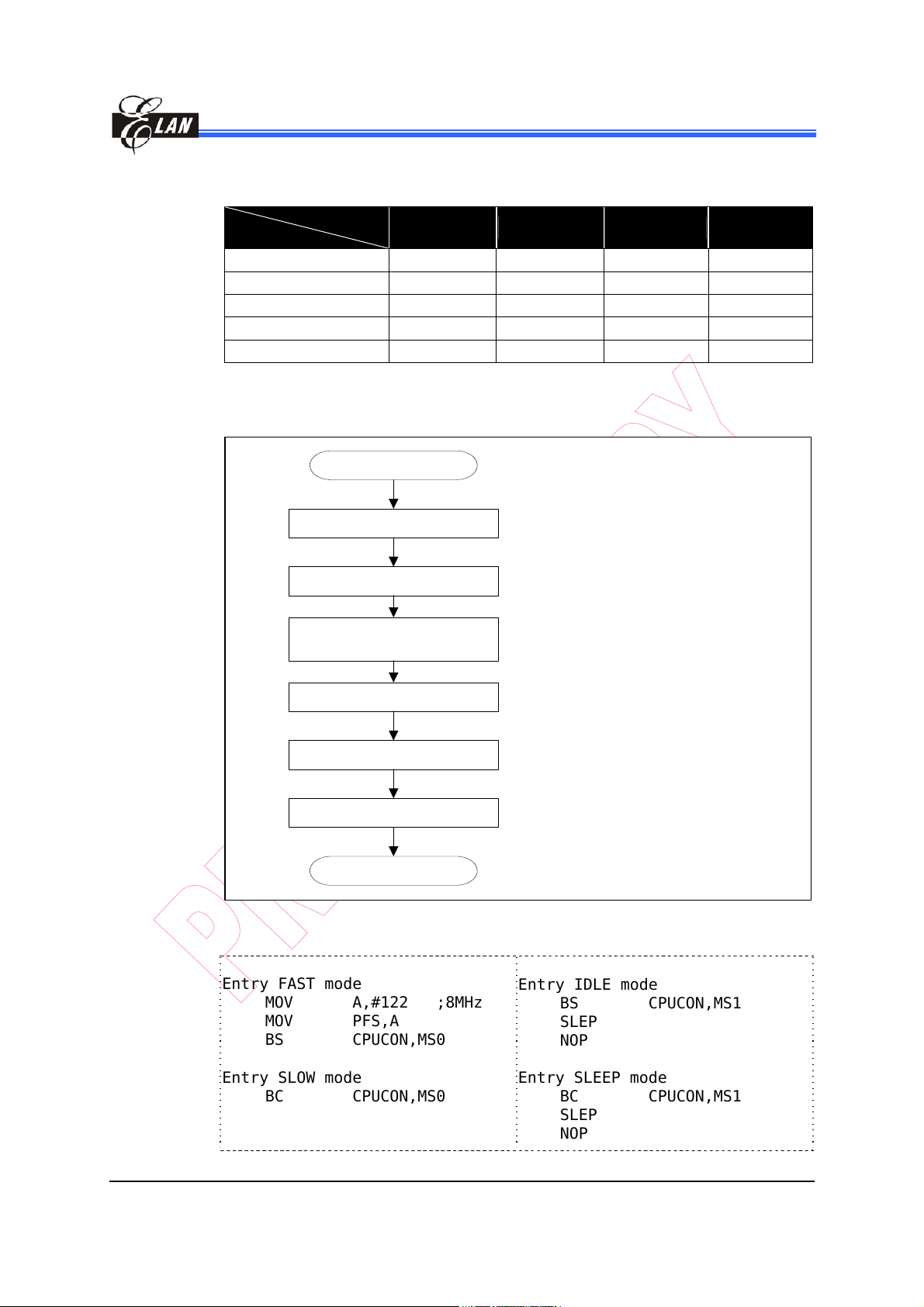

7.4 Wake-up Function

EPH3600

RISC II Series Microcontroller

Mode

Device

I/O wake up √ √ × ×

Touch panel wake up √ √ × ×

Timer1 wake up × √ × ×

A/D wake up × √ × ×

SPI wake up √ (Slave) √ (Slave) × ×

Legend: √ = Function is available if en abled × = Function is NOT available

Sleep Idle Slow Fast

Flowchart:

Change PLL F requency

BS CPUCO N, PEN Turn on the PLL

BC CPUCON, MS0 Change CPU to Slow mode

M O V A ,# 1 2 2

M O V P F S ,A

Chan ge PLL fre quency to

8MHz

SCALL DLY5m s

BS CPUCO N, M S0

BC CPUCON, PEN

G o to M a in R o u tin e

Code Example:

Entry FAST mode

MOV A,#122 ;8MHz

MOV PFS,A

BS CPUCON,MS0

Entry SLOW mode

BC CPUCON,MS0

D e la y fo r 5 m s to w a it fo r

PLL to be stable

Change CPU to Fast m ode

T u rn o ff th e P L L

Entry IDLE mode

BS CPUCON,MS1

SLEP

NOP

Entry SLEEP mode

BC CPUCON,MS1

SLEP

NOP

Product Specification (V0.1) 10.11.2007 • 17

(This specification is subject to change without further notice)

Page 24

EPH3600

RISC II Series Microcontroller

7.5 Interrupt

When an interrupt occurs, the GLINT bit of the CPUCON register is reset to 0, which

disables all interrupts, including Level 1 ~ Level 5. Setting this bit to 1 will enable all

un-mask interrupts.

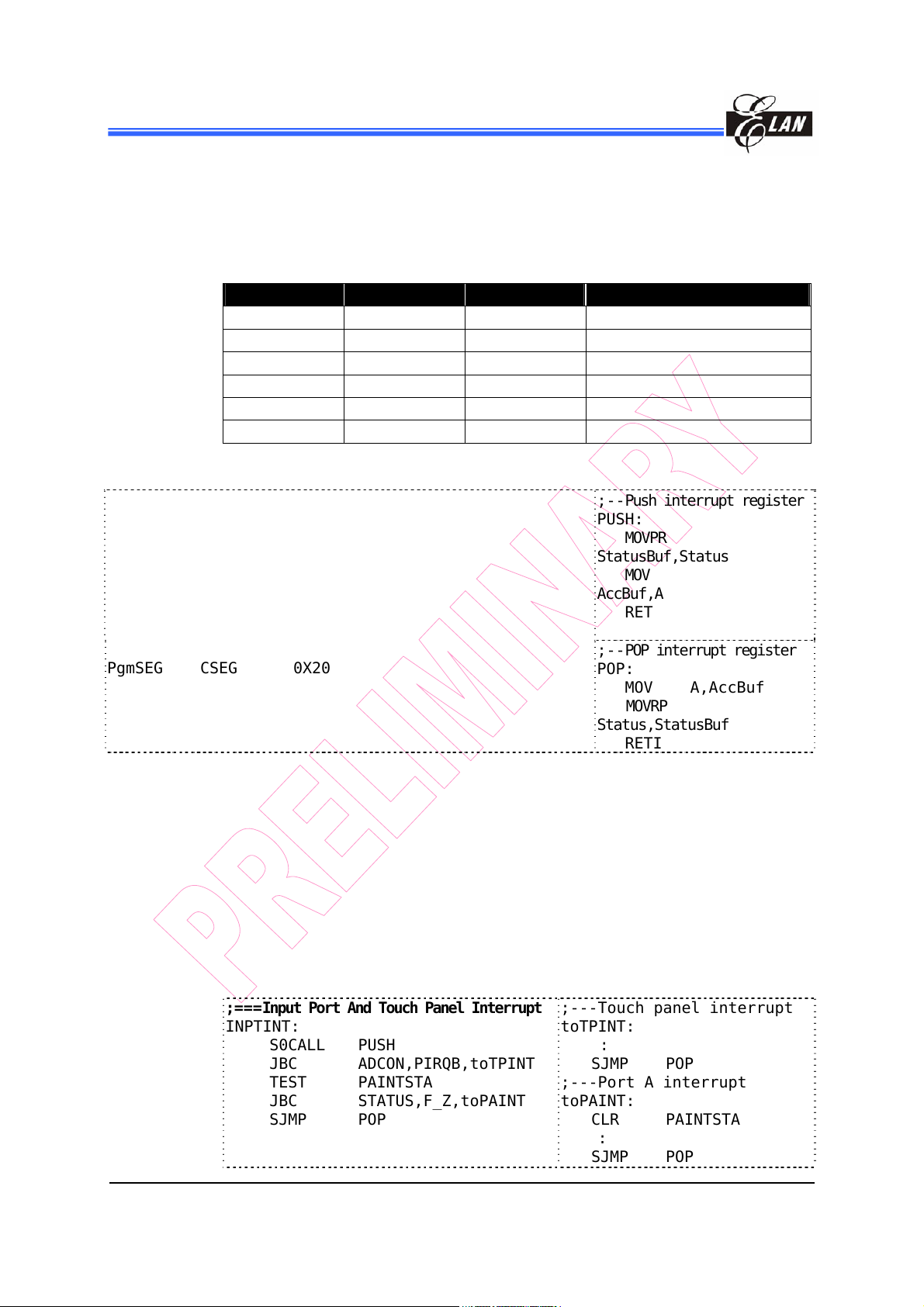

Interrupt Level Interrupt Source Start Address Remarks

RESET 0x00000

Level 1 Input Port 0x00002 PAINT, PIRQB

Level 2 Capture 0x00004 CPIF

Level 3 Speech T imer 0x00006 SPHTI

Level 4 Timers 0~2 0x00008 TMR0I, TMR1I, TMR2I

Level 5 Peripheral 0x0000A UERRI, UTXI, URXI, ADIF, SRBFI

Code Example:

; ***** Reset program

ResetSEG CSEG 0X00

LJMP MSTART ;(0X00) Initialize

LJMP INPTINT ;(0X02) Input Port and Touch Panel INT

LJMP CAPINT ;(0X04) Capture Input INT

LJMP SPHINT ;(0X06) Speech Timer INT

LJMP TIMERINT ;(0X08) Timer-0,1,2 INT

LJMP PERIPH ;(0X0A) Peripheral INT

PgmSEG CSEG 0X20

;--Push interrupt register

PUSH:

MOVPR

StatusBuf,Status

MOV

AccBuf,A

RET

;--POP interrupt register

POP:

MOV A,AccBuf

MOVRP

Status,StatusBuf

RETI

7.5.1 Input Port A Interrupt

1. Port A Interrupt (Falling edge trigger): Port A is used as external interrupt/wake-up

input.

2. Touch Panel Interrupt (Level trigger): When Port C.7 ~ Port C.4 (X+, X-, Y+ and Y-)

are connected to touch panel input pins and

touch panel is touched, PIRQB interrupt

occurs.

Code Example:

;===Input Port And Touch Panel Interrupt

INPTINT:

S0CALL PUSH

JBC ADCON,PIRQB,toTPINT

TEST PAINTSTA

JBC STATUS,F_Z,toPAINT

SJMP POP

18 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

;---Touch panel interrupt

toTPINT:

:

SJMP POP

;---Port A interrupt

toPAINT:

CLR PAINTSTA

:

SJMP POP

Page 25

EPH3600

RISC II Series Microcontroller

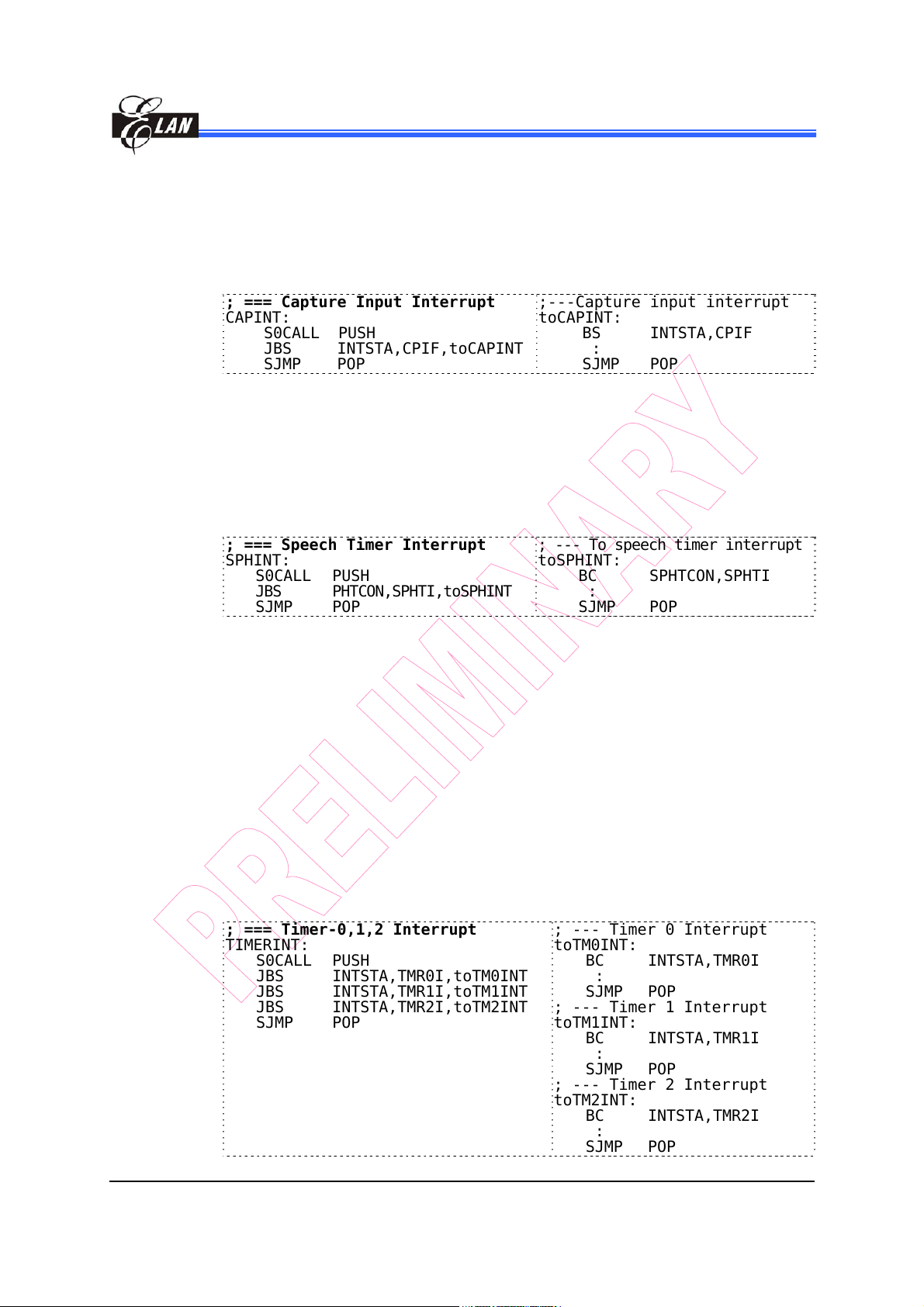

7.5.2 Capture Input Interrupt

The Capture function is used to capture an input event at rising to falling edge, falling

to rising edge, rising to rising edge, or falling to falling edge. When every event input

edge is detected, a Capture interrupt occurs.

Code Example:

; === Capture Input Interrupt

CAPINT:

S0CALL PUSH

JBS INTSTA,CPIF,toCAPINT

SJMP POP

;---Capture input interrupt

toCAPINT:

BS INTSTA,CPIF

:

SJMP POP

7.5.3 Speech Timer Interrupt

Speech Timer is an 11-bit timer for time counting. When the counting value of the

Speech Timer underflows, an interrupt occurs and the SPHTRL value will be reloaded

to counting value.

Code Example:

; === Speech Timer Interrupt

SPHINT:

S0CALL PUSH

JBS PHTCON,SPHTI,toSPHINT

SJMP POP

; --- To speech timer interrupt

toSPHINT:

BC SPHTCON,SPHTI

:

SJMP POP

7.5.4 Timer 0, Timer 1, and Timer 2 Interrupts

1. Timer 0 Interrupt: Timer 0 is a 16-bit timer for general time counting. When the

counting value is larger than TRL0H : TRL0L value, a Timer 0

interrupt occurs.

2. Timer 1 Interrupt: Timer 1 is an 8 bit-timer for time counting and wake-up function.

When the counting value of Timer 1 underflows, an interrupt

occurs and the TRL1 value will be reloaded to counting value.

3. Timer 2 Interrupt: Timer 2 is an 8-bit timer for time counting. When the counting

value of Timer 2 underflows, an interrupt occurs and the TRL2

value will be reloaded to counting value.

Code Example:

; === Timer-0,1,2 Interrupt

TIMERINT:

S0CALL PUSH

JBS INTSTA,TMR0I,toTM0INT

JBS INTSTA,TMR1I,toTM1INT

JBS INTSTA,TMR2I,toTM2INT

SJMP POP

; --- Timer 0 Interrupt

toTM0INT:

BC INTSTA,TMR0I

:

SJMP POP

; --- Timer 1 Interrupt

toTM1INT:

BC INTSTA,TMR1I

:

SJMP POP

; --- Timer 2 Interrupt

toTM2INT:

BC INTSTA,TMR2I

:

SJMP POP

Product Specification (V0.1) 10.11.2007 • 19

(This specification is subject to change without further notice)

Page 26

EPH3600

RISC II Series Microcontroller

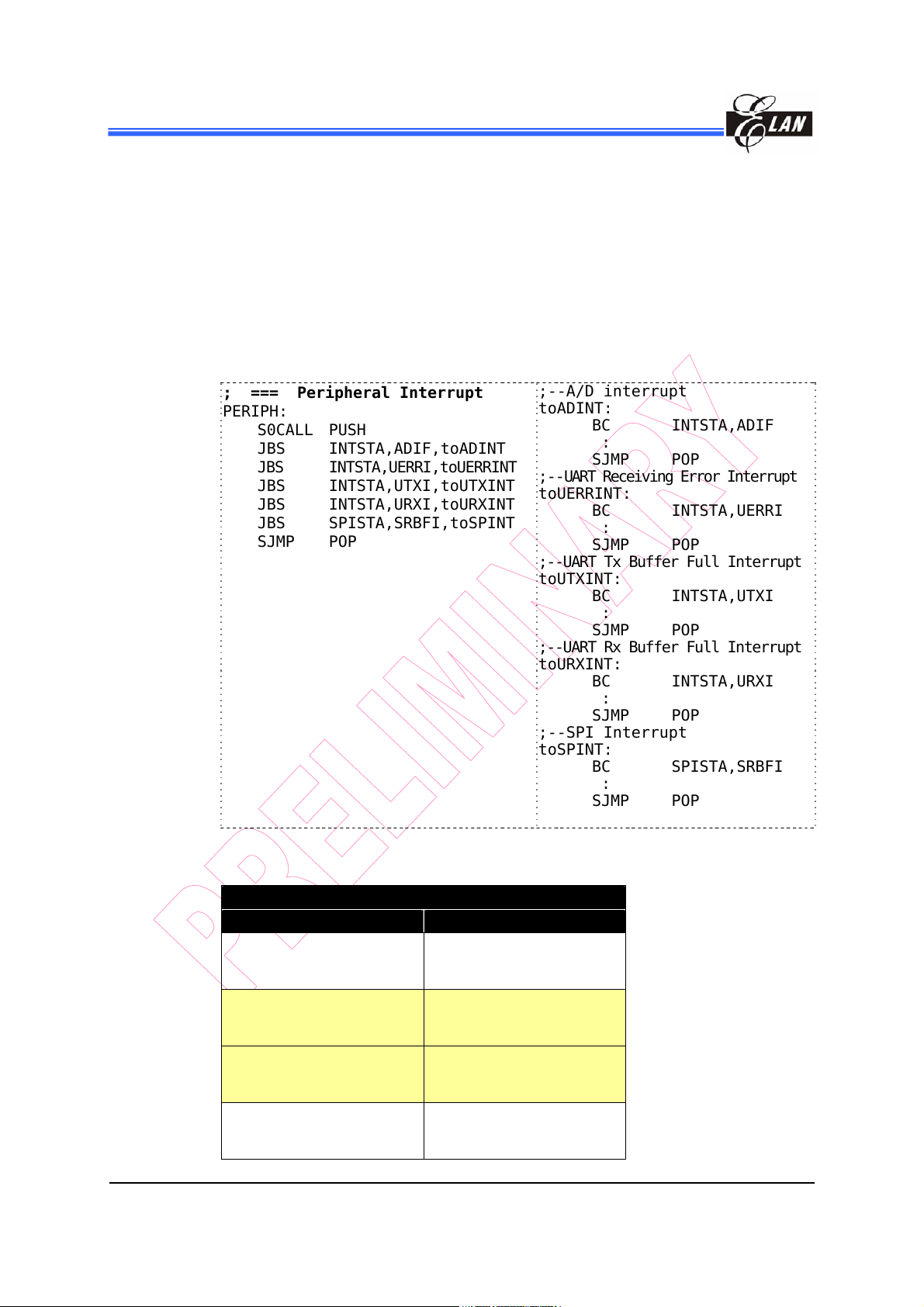

7.5.5 Peripheral Interrupt

1. A/D (Analog to Digital converter) Interrupt: A/D is used to convert analog input

2. UERRI Interrupt: UART receiving error interrupt

3. UTXI Interrupt: UART transfer buffer empty interrupt

4. URXI Interrupt: UART receiver buffer full interrupt

5. SRBFI Interrupt: SPI read buffer full interrupt

Code Example:

; === Peripheral Interrupt

PERIPH:

S0CALL PUSH

JBS INTSTA,ADIF,toADINT

JBS INTSTA,UERRI,toUERRINT

JBS INTSTA,UTXI,toUTXINT

JBS INTSTA,URXI,toURXINT

JBS SPISTA,SRBFI,toSPINT

SJMP POP

7.6 Progra m ROM Map

signal to digital output bits. When the conversion is completed,

an A/D interrupt occurs.

;--A/D interrupt

toADINT:

BC INTSTA,ADIF

:

SJMP POP

;--UART Receiving Error Interrupt

toUERRINT:

BC INTSTA,UERRI

:

SJMP POP

;--UART Tx Buffer Full Interrupt

toUTXINT:

BC INTSTA,UTXI

:

SJMP POP

;--UART Rx Buffer Full Interrupt

toURXINT:

BC INTSTA,URXI

:

SJMP POP

;--SPI Interrupt

toSPINT:

BC SPISTA,SRBFI

:

SJMP POP

8K Words × 2 Segments = 16K Words

Address Segment

0000h

|

000Bh

000Ch

|

0013h

0014h

|

001Fh

0020h

|

3FFFh

20 • Product Specification (V0.1) 10.11.2007

Interrupt Vector

(12 words)

Code Option

(8 words)

Test Program

(12 words)

Segment 0

|

Segment 1

(This specification is subject to change without further notice)

Page 27

EPH3600

RISC II Series Microcontroller

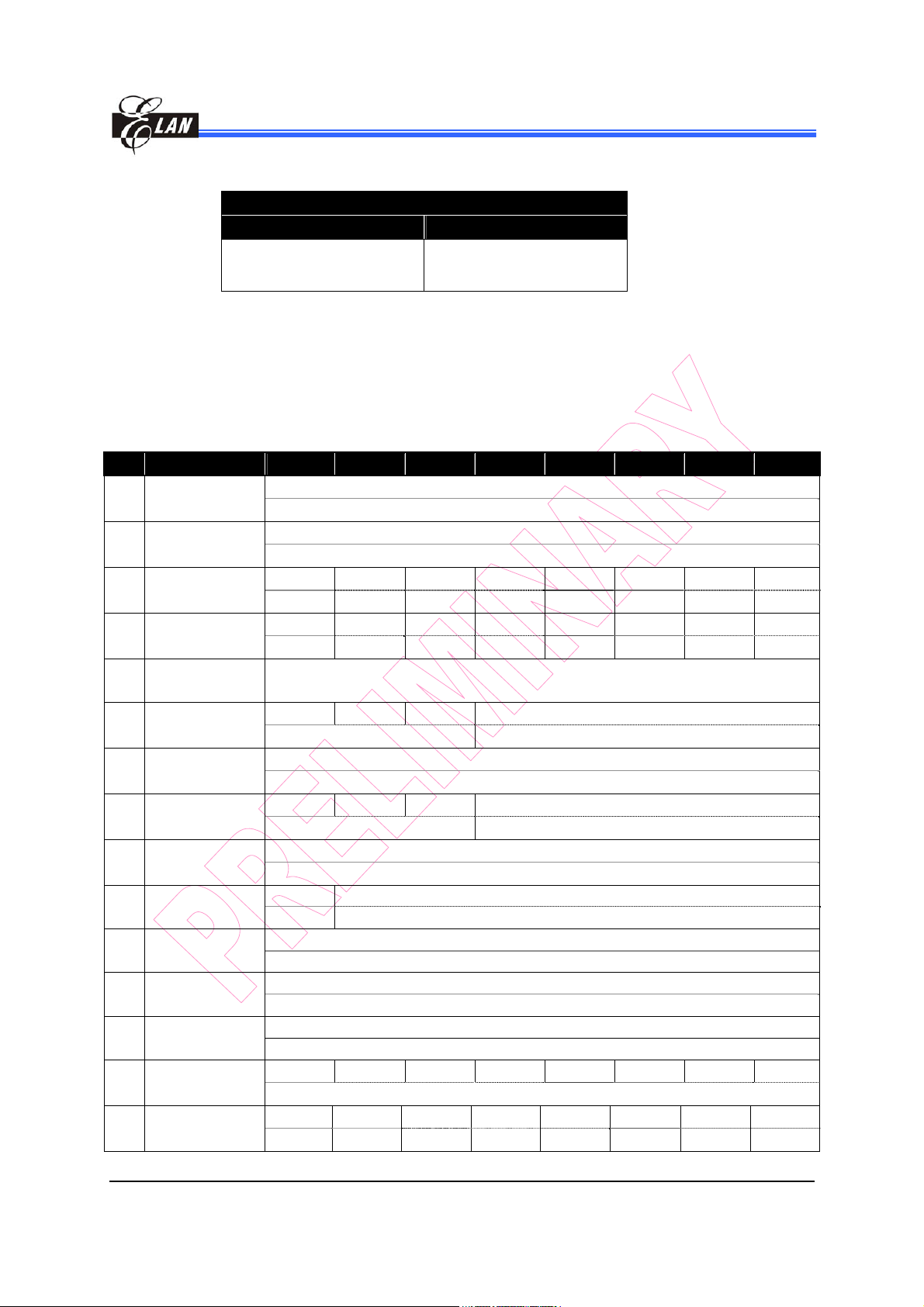

7.7 Data ROM Map

Maximum Size is 256K Words

Address

100000h

|

13FFFFh

Data ROM (4M bits)

7.8 RAM Map Register

(RAM Size: 128 Bytes + 32 Banks × 128 Bytes = 4224 Bytes)

7.8.1 Special and Control Register of RAM

Legend: R = Readable bit W = Writable bit – = unimplemented, read as “0”

Addr. Register Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0 INDF0

1 FSR0

2 PCL

3 PCM

Indirect Addressing Pointer 0

File Select Register 0 for INDF0

R/W R/W R/W R/W R/W R/W R/W R/W

PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

R/W R/W R/W R/W R/W R/W R/W R/W

PC15 PC14 PC13 PC12 PC11 PC10 PC9 PC8

R/W

R/W

4 (Not Used) −

5 BSR

6 STKPTR

7 BSR1

8 INDF1

9 FSR1

A ACC

B TABPTRL

C TABPTRM

D TABPTRH

E CPUCON

R/W

− Bank Select Register for INDF0 & General RAM

R/W

Stack Pointer

R/W

− Bank Select Register 1 for INDF1

R/W

Indirect Addressing Pointer 1

R R/W

1 File Select Register 1 for INDF1

R/W

Accumulator

R/W

Table Pointer Low

R/W

Table Pointer Middle

R/W − R/W R/W R/W R/W R/W R/W

Table Pointer High

R/W R/W R/W R/W R/W R/W

PEN − − SMCAND SMIER GLINT MS1 MS0

Product Specification (V0.1) 10.11.2007 • 21

(This specification is subject to change without further notice)

Page 28

EPH3600

RISC II Series Microcontroller

(Continued)

Addr. Register Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

F STATUS

10 TRL2

11 PRODL

12 PRODH

13 ADOTL

14 ADOTH

15 UARTTX

16 UARTRX

17 Port A

18 Port B

19 Port C

1A Port D

1B (Not Used) −

1C (Not Used) −

1D R1D

1E R1E

1

1

1F (Not Used) −

20 PFS

21 STBCON

22 INTCON

23 INTSTA

24 TRL0L

25 TRL0H

R R R/W R/W R/W R/W R/W R/W

/TO /PD SGE SLE OV Z DC C

R/W

Timer 2 Reload Register

R/W

Multiplier Product Low

R/W

Multiplier Product High

R/W R/W R/W R R

WDTEN − ADWKEN − − FSS ADOT1 ADOT0

R R R R R R R R

ADOT9 ADOT8 ADOT7 ADOT6 ADOT5 ADOT4 ADOT3 ADOT2

W W W W W W W W

TB7 TB6 TB5 TB4 TB3 TB2 TB1 TB0

R R R R R R R R

RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0

R R R R R R R R

A.7 A.6 A.5 A.4 A.3 A.2 A.1 A.0

R/W R/W R/W R/W R/W R/W R/W R/W

B.7 B.6 B.5 B.4 B.3 B.2 B.1 B.0

R/W R/W R/W R/W R/W R/W R/W R/W

C.7 C.6 C.5 C.4 C.3 C.2 C.1 C.0

R/W R/W R/W R/W R/W R/W R/W R/W

D.7 D.6 D.5 D.4 D.3 D.2 D.1 D.0

R/W R/W R/W R/W R/W R/W R/W R/W

R1D.7 R1D.6 R1D.5 R1D.4 R1D.3 R1D.2 R1D.1 R1D.0

R/W R/W R/W R/W R/W R/W R/W R/W

R1E.7 R1E.6 R1E.5 R1E.4 R1E.3 R1E.2 R1E.1 R1E.0

R/W

Target PLL Frequency Selection Register

R/W

UINVEN −

R/W R/W R/W R/W R/W R/W R/W R/W

CPIE ADIE URXIE UTXIE UERRIE TMR2IE TMR1IE TMR0IE

R/W R/W R/W R/W R/W R/W R/W R/W

CPIF ADIF URXI UTXI UERRI TMR2I TMR1I TMR0I

R/W

Timer 0 Reload Low Byte Register

R/W

Timer 0 Reload High Byte Register

22 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 29

EPH3600

RISC II Series Microcontroller

(Continued)

Addr. Register Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

26 TRL1

27 TR01CON

28 TR2CON

29 TRLIR

2A ELCON

2B POST_ID

2C ADCON

2D PAINTEN

2E PAINTSTA

2F PAWAKE

30 UARTCON

31 UARTSTA

32 (Not Used) −

33 (Not Used) −

34 DCRB

35 DCRC

36 DCRDE

37 (Not Used) −

38 (Not Used) −

39 (Not Used) −

3A PBCON

3B PCCON

3C PLLF

3D TOCL

3E TOCH

3F SPICON

R/W R/W R/W R/W R/W R/W R/W R/W

T1WKEN T1EN T1PSR1 T1PSR0 IREN T0CS T0PSR1 T0PSR0

R/W R/W R/W R/W R/W R/W R/W R/W

IRPSR1 IRPSR0 T0FNEN1 T0FNEN0 T2EN T2CS T2PSR1 T2PSR0

R/W R/W R/W

ELTEN CKP ELTRL5~ELTRL0

R/W R/W R/W R/W

− − FSR1_ID FSR0_ID − − FSR1PE FSR0PE

R/W R/W R/W R R/W R/W R/W

DET VRS ADEN PIROB − CHS2 CHS1 CHS0

R/W R/W R/W R/W R/W R/W R/W R/W

PA7IE PA6IE PA5IE PA4IE PA3IE PA2IE PA1IE PA0IE

R/W R/W R/W R/W R/W R/W R/W R/W

PA7I PA6I PA5I PA4I PA3I PA2I PA1I PA0I

R/W R/W R/W R/W R/W R/W R/W R/W

WKEN7 WKEN6 WKEN5 WKEN4 WKEN3 WKEN2 WKEN1 WKEN0

W R/W R/W R/W R/W R/W R R/W

TB8 UMODE1 UMODE0 BRATE2 BRATE1 BRATE0 UTBE TXE

R R/W R/W R/W R/W R/W R R/W

RB8 EVEN PRE PRERR OVERR FMERR URBF RXE

R/W R/W R/W R/W R/W R/W R/W R/W

Bit7DC Bit6DC Bit5DC Bit4DC Bit3DC Bit2DC Bit1DC Bit0DC

R/W R/W R/W R/W R/W R/W R/W R/W

Bit7DC Bit6DC Bit5DC Bit4DC Bit3DC Bit2DC Bit1DC Bit0DC

R/W R/W R/W R/W

− DHNPU DLNPU DHNDC DLNDC

R/W R/W R/W R/W R/W R/W R/W R/W

Bit7PU Bit6PU Bit5PU Bit4PU Bit3PU Bit2PU Bit1PU Bit0PU

R/W R/W R/W R/W R/W R/W R/W R/W

Bit7PU Bit6PU Bit5PU Bit4PU Bit3PU Bit2PU Bit1PU Bit0PU

Timer 0 Counting Value Low Byte Register

Timer 0 Counting Value High Byte Register

R/W R/W R/W R/W R/W R/W R/W R/W

TLS1 TLS0 BRS2 BRS1 BRS0 EDS DORD SE

Timer 1 Reload Register

Actual PLL Frequency Value Register

R/W

R/W

IR Reload Register

R

R

R

Product Specification (V0.1) 10.11.2007 • 23

(This specification is subject to change without further notice)

Page 30

EPH3600

RISC II Series Microcontroller

(Continued)

Addr. Reg ister Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

40 SPISTA

41 SPRL

42 SPRM

43 SPRH

44 SFCR

45 (Not Used) −

46 (Not Used) −

47 (Not Used) −

48 SPHDR

49 SPHTCON

4A SPHTRL

4B VOCON 2

4C TR1C

4D TR2C

4E ADCF

4F (Not Used) −

50 (Not Used) −

51 (Not Used) −

52 (Not Used) −

53 (Not Used) −

54 PAPUR 2

55 PACON 2

1

R1D, R1E are generated register RAM.

2

When the PAPUR register & DAC bit are enabled and effective, the following conditons occur:

a) Code option setting can use PAPUR register, SPHTPSR1~0, and DAC bit.

b) The KE, /R2EN, and Bit7PU bit of PACON can NOT be used.

Note that the code option setting is available only from the real chip but can NOT be simulated

with the PM board.

R/W R/W R/W R/W R/W R

− − SRBFIE SRBFI SPWKEN SMP DCOL RBF

R/W

Shift Register Low Byte of SPI

R/W

Shift Register Middle Byte of SPI

R/W

Shift Register High Byte of SPI

R/W R/W R/W R/W R/W R/W R/W R/W

AGMD2 AGMD1 AGMD0

WDTPRS1 WDTPRS0 SPHSB CSB1 CSB0

R/W

Speech Data Register

R/W R/W R/W R/W R/W R/W R/W R/W

SPHTPSR1 SPHTPSR

0

SPHTI SPHTIE SPHTEN

SPHTRLH2 SPHTRLH1 SPHTRLH

0

R/W

Speech Reload Register

R/W R/W R/W R/W R/W

VOEN DAC − − − VOL2 VOL1 VOL0

R

Timer 1 Counting Value Register

R

Timer 2 Counting Value Register

R/W

A/D Clock Factor Register

R/W R/W R/W R/W R/W R/W R/W R/W

Bit7PU0 Bit6PU0 Bit5PU0 Bit4PU0 Bit3PU0 Bit2PU0 Bit1PU0 Bit0PU0

R/W R/W R/W R/W

− Bit7PU /R2EN /R1EN KE

24 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 31

EPH3600

RISC II Series Microcontroller

7.8.2 Other Un-banked Register of RAM:

Address Un-banked

56h

|

7Fh

General Purpose RAM

7.8.3 Banked Register of RAM:(selected by BSR)

Address Bank 0 Bank 1 Bank 2 Bank 3 …….. Bank 31

80h

|

FFh

General

Purpose

RAM

General

Purpose

RAM

7.9 Special Register Description

STKPTR (R06h)

The stack level starts from the bottom going up (in a decreasing order), starting from

0FFh of Bank 31.

Stack is located at Bank 30 and 31 from Address FFh~80h. Initial top position of

stack pointer is located at 00h.

Bits 0~6 of STKPTR are used as address pointer from 80h ~ FFh

Bit 7=1 is used to select Bank 31

Bit 7=0 is used to select Bank 30

Each INT/CALL will stack two bytes address, total capacity is 128 levels.

PCL, PCM (R02h, R03h): Program Counter Register

Bit 15 … Bit 8 Bit 7 … Bit 0

PCM PCL

General

Purpose

RAM

General

Purpose

RAM

……..

General

Purpose

RAM

Generates up to 64K×16 on-chip ROM addresses at the relative programming

instruction codes.

“S0CALL” loads the low 12 bits of the PC (4K×16 ROM).

“SCALL” or ”SJUMP” loads the low 13 bits of the PC (8K×16 ROM).

“LCALL” or ”LJUMP” loads the full 16 bits of the PC (64K×16 ROM)

“ADD R2, A” or “ADC R2, A” allows a relative address to be added to the current PC.

The carry bit of R2 will automatically carry into PCM.

Product Specification (V0.1) 10.11.2007 • 25

(This specification is subject to change without further notice)

Page 32

EPH3600

RISC II Series Microcontroller

Code Example:

START: MOV A,entry

MOV number,a ;number <-- entry

LCALL Indirect_JUMP

AAA: ........

.......

Indirect_JUMP:

MOV A,number

ADD A,ACC ; A<-- 2*A

ADD PCL,A ; PCL<-- PCL+A

function_table:

LJMP function_address_1 ; number=0

LJMP function_address_2 ; number=1

LJMP function_address_3 ; number=2

LJMP function_address_4 ; number=3

LJMP function_address_5 ; number=4

LJMP function_address_6 ; number=5

LJMP function_address_7 ; number=6

.........

function_address_1:

........; Function 1 operation

........

RET ; PC will return to AAA label

ACC (R0Ah): Accumulator. Internal data transfer, or instruction operand holding

POST_ID (R2Bh): Post increase / decrease the control register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

- - FSR1_ID FSR0_ID - - FSR1PE FSR0PE

Bit 0 (FSR0PE): Enable FSR0 post increase/decrease function. FSR0 will Not carry

into or borrow from BSR.

Bit 1 (FSR1PE): Enable FSR1 post increase/decrease function. FSR1 will carry into

or borrow from BSR1.

Bit 4 (FSR0_ID): Setting to 1 means auto increase, resetting to 0 means auto

decrease of FSR0.

Bit 5 (FSR1_ID): Setting to 1 means auto increase, resetting to 0 means auto

decrease of FSR1.

7.9.1 Indirect Addressing Pointer 0

BSR (R05h) determines which b ank is active (working bank) among the 32 banks

(Bank 0 ~ Bank 31).

FSR0 (R01h) is an address register for INDF0. You can select up to 256 bytes

(Address: 00 ~ 0FFh).

INDF0 (R00h) is not a physically implemented register.

26 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 33

EPH3600

RISC II Series Microcontroller

7.9.2 Indirect Addressing Pointer 1

BSR1 (R07h) is a bank register for INDF1. It cannot determines the working bank

for the general register.

FSR1 (R09h) is an address register for INDF1. You can select up to 128 bytes

(Address: 80 ~ 0FFh). Bit 7 of FSR1 is fixed to 1.

INDF1 (R08h) is not a physically implemented register.

Code Example:

Data transform Bank 0 to Bank 1:

MOV A,#00110011B ; Enable FSR0 & FSR1 post increase

MOV POST_ID,A

BANK #0 ; BSR = 0 working bank

MOV A,#1

MOV BSR1,A ; BSR1 = 1 is Bank 1

MOV A,#80H

MOV FSR0,A ; FSR0 = 80H

CLR FSR1 ; FSR1 = 80H

MOV A,#80H

RPT ACC

MOVRP INDF1,INDF0 ; Move 80H ~ 0FFH data to Bank 1

:

Linear addressing capability of INDF1 is shown below:

Auto Increase on FSR1

(Set FSR1PE=1,FSR1 ID=1)

FDh

FEh

FFh

File Register

BANK 3

:

:

88

99

AA

80h

81h

82h

BANK 4

BB

CC

DD

:

:

Instruction BSR1 FS R1 INDF1

MOV A,INDF1

MOV A,INDF1

MOV A,INDF1

:

(* FSR1 will carry into BSR1)

(*Bit 7 of FSR1is fixed to 1)

Auto Decrease on FSR1

(Set FSR1PE=1,FSR1 ID=0)

Instruction BSR1 FSR 1 INDF1

MOV A,INDF1

MOV A,INDF1

MOV A,INDF1

:

(* FSR1 will borrow from BSR1)

(*Bit 7 of FSR 1is fix ed to 1)

AAFF03

BB8004

CC8104

DD8204

ACC

00

AA

BB

CC

ACC

BB8004

AAFF03

99FE03

88FD03

00

BB

AA

99

Product Specification (V0.1) 10.11.2007 • 27

(This specification is subject to change without further notice)

Page 34

EPH3600

RISC II Series Microcontroller

Code Example:

;*******************************************

;* Const => Working bank setting

;* REG => Save or Recall register

;*******************************************

; ***** RAM stack macro

; *** Initial RAM stack

IniRAMsk MACRO #Const

MOV A,#Const

MOV BSR1,A

CLR FSR1

BS POST_ID,FSR1PE

ENDM

; *** Push RAM stack

PushRAM MACRO REG

BS POST_ID,FSR1_ID

MOVRP INDF1,REG

ENDM

; *** Pop RAM stack

PopRAM MACRO REG

BC POST_ID,FSR1_ID

MOVPR REG,INDF1

ENDM

; *** Main start program

Mstart:

:

:

IniRAMsk #29

:

:

MnLoop:

:

:

LJMP MnLoop

; *** Interrupt routine

IntSR:

PushRAM ACC

PushRAM Status

:

:

:

PopRAM Status

PopRAM ACC

RETI

TABPTRL, TABPTRM, TABPTRH (R0Bh, R0Ch, R0Dh): Table Pointer Re gister

Bit 23 Bit 22 … Bit 16 Bit15 … Bit 8 Bit 7 … Bit 0

- TABPTRH TABPTRM TABPTRL

Program ROM or Internal ROM address register:

Bit 23 is used to select the internal/external memory.

Bit 20 ~ Bit 1 are used to point the memory address.

Bit 0 is used to select the low byte or high byte of the pointed word (see

TBRD instruction).

Code Example:

; *** Program ROM

:

:

TBPTH #(PROMTabB*2)/10000H

TBPTM #(PROMTabB*2)/100H

TBPTL # PROMTabB*2

:

:

TBRD 0,ACC ; no change

TBRD 1,ACC ; auto-increase

TBRD 2,ACC ; auto-decrease

:

:

; *** Program ROM data

PROMTabB:

DB 0x00,0x01,0x02,0x03,0x04,0x05

DB 0x10,0x11,0x12,0x13,0x14,0x15

DB 0x20,0x21,0x22,0x23,0x24,0x25

; *** Internal data ROM

INCLUDE "DROM_I.hdr";to ROMConverter

:

:

TBPTL #_Data_l

TBPTM #_Data_m

TBPTH #_Data_h

:

:

TBRD 0,ACC ; no change

TBRD 1,ACC ; auto-increase

TBRD 2,ACC ; auto-decrease

:

28 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 35

PRODL, PRODH (R11h, R12h): An unsigned or signed 8 × 8 hardware multiplier

is included in the microcontroller. The result is stored into the

16 bits product register.

CPUCON (R0Eh): MCU Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PEN - - SMCAND SMIER GLINT MS1 MS0

Bit 3 (SMIER): Signed or unsigned selection bit of the Multiplier. (ACC)

“0” : Multiplier is unsigned

“1” : Multiplier is signed

Bit 4 (SMCAND): Signed or unsigned selection bit of the Multiplicand.

(Constant or Register)

“0” : Multiplier is unsigned

“1” : Multiplier is signed

Code Example:

; *** Signed multiplier operation

; === PRODH:PRODL = A x REG

BS CPUCON,SMIER

BS CPUCON,SMCAND

MUL A,REG

EPH3600

RISC II Series Microcontroller

; *** Unsigned multiplier operation

; === PRODH:PRODL = A x #k

BC CPUCON,SMIER

BC CPUCON,SMCAND

MUL A,# 88

Port A (R17h): is a general input register

PAPUR (R54h): Pull-up Resistor Control of Port A

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bit7PU0 Bit6PU0 Bit5PU0 Bit4PU0 Bit3PU0 Bit2PU0 Bit1PU0 Bit0PU0

Bit 7 ~ Bit 0 (Bit 7PU7 ~ Bit 0PU0): Enable Port A R2 pull-up resistor.

“0” : Disable pull-up resistor

“1” : Enable pull up resistor

NOTE

1. When the PAPUR register & DAC bit are enabled and effective, the

following conditons occur:

a) Code option setting can use PAPUR register and DAC bit.

b) The KE, /R2EN, and Bit7PU bit of PACON can NOT be used.

2. The code option setting is available only from the real chip but

cannot be simulated with the PM board.

PACON (R55h): Port A Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

- - - - Bit7PU /R2EN /R1EN KE

Bit 0 (KE): Key input enable/disable control bit.

“0” : Disable Key input function

“1” : Enable Key input function.

Product Specification (V0.1) 10.11.2007 • 29

(This specification is subject to change without further notice)

Page 36

EPH3600

RISC II Series Microcontroller

Bit 1 (/R1EN): R1 pull-up resistor (small resistor) control bit.

“0” : Enable R1 pull-up resistor

“1” : Disable R1 pull-up resistor

Bit 2 (/R2EN): R2 pull-up resistor (large resistor) control bit.

Bit 3 (Bit 7PU): Enable Port A.7 pull-up resistor.

“0” : Disable pull-up resistor

“1” : Enable pull up resistor

PAINTEN (R2Dh): is Port A interrupt control register

“0” : Disable interrupt function

PAINTSTA (R2Eh): is Port A interrupt status register

Set to “1” when pin falling edge is detected

“0” : Enable R2 pull-up resisto r

“1” : Disable R2 pull-up resistor

“1” : Enable interrupt function

Clear to “0” by software

PAWAKE (R2Fh): is Port A wake-up control register

“0” : Disable wake-up function

“1” : Enable wake-up function

Port B (R18h) are general I/O registers

DCRB (R34h): Port B Direction Control

“0” : Output pin setting

“1” : Input pin setting

PBCON (R3Ah): Pull-up Resistor Control of Port B

“0” : Disable pull-up resistor

“1” : Enable pull-up resistor

Port C (R19h): are General I/O Registers

DCRC (R35h): Port C Direction Control

“0” : Output pin setting

“1” : Input pin setting

PCCON (R3Bh): Pull-up Resistor Control of Port C.

“0” : Disable pull-up resistor

“1” : Enable pull-up resistor

30 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 37

Port D (R1Ah): is a General I/O Register

DCRDE (R36h): Direction Control & Pull-up Resistor Control of Port D

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

- - - - DHNPU DLNPU DHNDC DLNDC

Bit 1 (DHNDC) & Bit 0 (DLNDC): Port D high nibble direction control

“0” : Output pin setting

Bit 3 (DHNPU) & Bit 2 (DLNPU): Enable Port D high nibble pull-up resistor

“0” : Disable pull up resistor

Code Example:

; *** Port A function

; --- Port A interrupt

INPTINT:

PUSH

MOV A,PAINTSTA

BC PACON,KE

; --- Port A interrupt

JBS STATUS,F_Z,Q_PAINT

MOV PORTD,A

Q_PAINT:

POP

RETI

; --- Port A R2 pull-up enable

MOV A,#00001010B

MOV PACON,A

; --- Port A interrupt

MOV A,#11111111B

MOV PAINTEN,A

CLR PAINTSTA

; --- Port A wakeup

MOV PAWAKE,A

BS CPUCON,GLINT

; --- Sleep mode

BC CPUCON,MS1

KeyLoop:

BS PACON,KE

SLEP

NOP

:

SJMP KeyLoop

EPH3600

RISC II Series Microcontroller

“1” : Input pin setting

“1” : Enable pull-up resistor

; *** Output function => 0XAAh to all port

CLR DCRC

CLR DCRB

CLR DCRDE

MOV A,#0XAA

MOV PORTC,A

MOV PORTB,A

MOV PORTD,A

;

; *** Input function => Input port to RAM 80 ~ 83h

BS POST_ID,FSR1_ID

BS POST_ID,FSR1PE

CLR BSR1

CLR FSR1

MOV A,#00001011B

MOV PACON,A

MOV A,#0XFF

MOV DCRB,A

MOV PBCON,A

MOV DCRC,A

MOV PCCON,A

MOV DCRDE,A

MOVRP INDF1,PORTA

BC PACON,KE

MOVRP INDF1,PORTB

MOVRP INDF1,PORTC

MOVRP INDF1,PORTD

Product Specification (V0.1) 10.11.2007 • 31

(This specification is subject to change without further notice)

Page 38

EPH3600

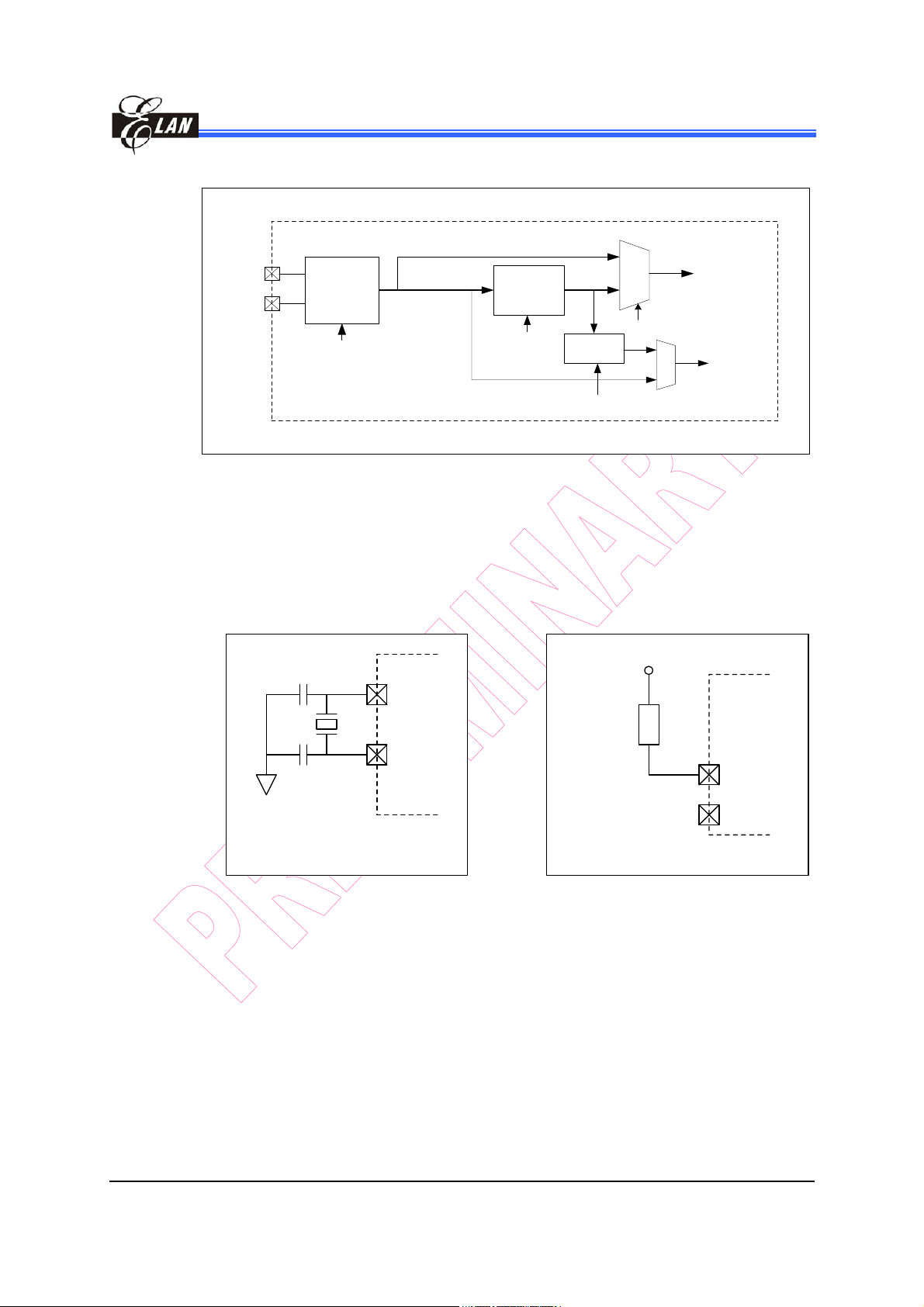

RISC II Series Microcontroller

8 Peripheral

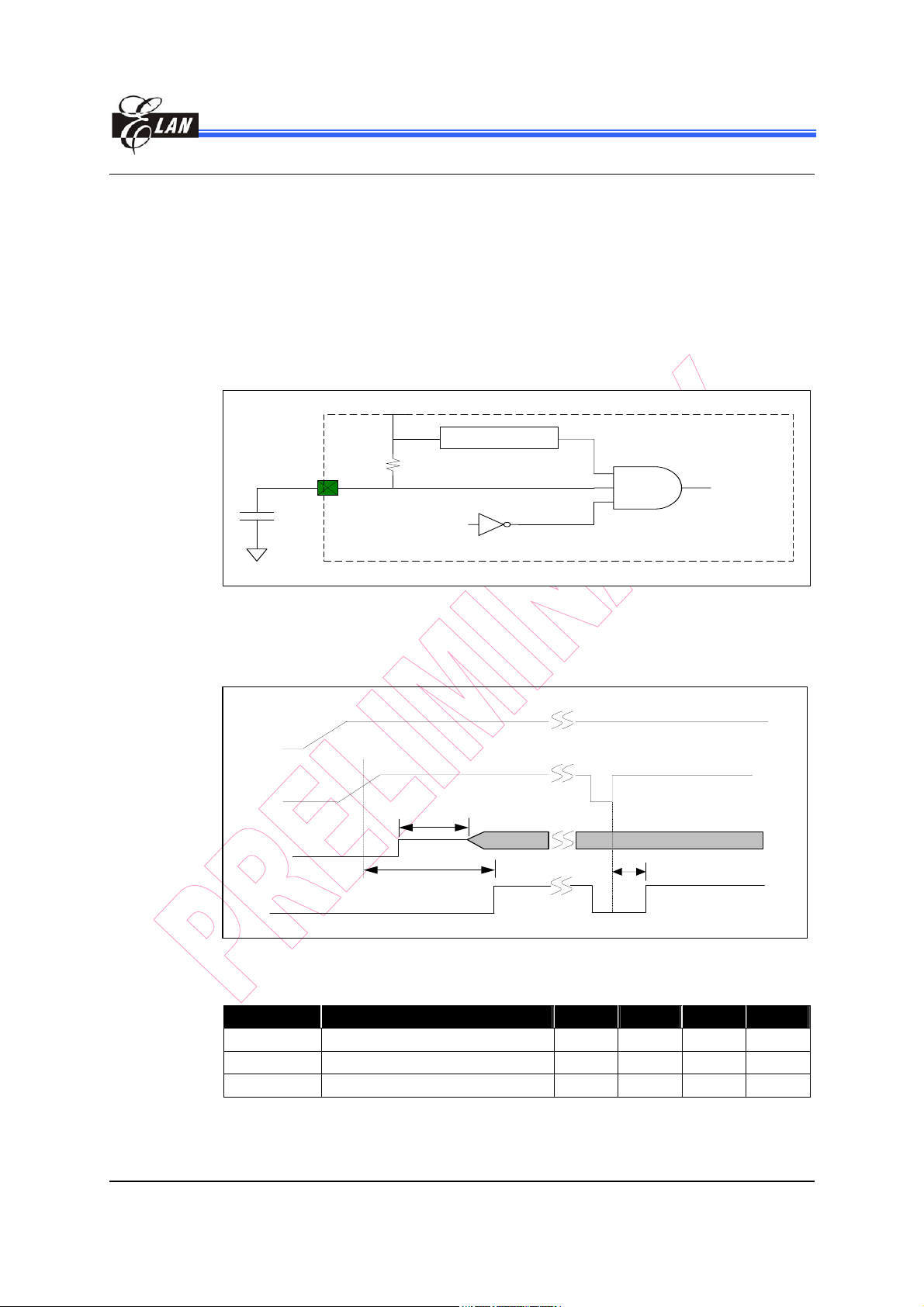

8.1 Timer 0 (16-bit Timer with Capture and Event Counter Functions)

TRL0H:TRL0L

Timer 0

(16-bit Counter)

AGMD2~0

Edge Detector

Comparator

Reset

Counting

Value

Selector

T0FNEN1~0

Timer 0 INT

T0CH:T0CL

CPIF

Fosc

FPLL/2

T0CS

T0PSR1~0

Fcs

Prescaler

EVIN/CPIN

T0FNEN1~0

Function

Enable

Selector

Schmit

Trigger

Figure 8-1 Timer 0 Function Block Diagram

8.1.1 Timer 0 Mode:

Under this mode, Timer 0 is used as a general-purpose 16-bit up counter. An

interrupt is available for user’s application.

A prescaler for the timer is also available. The T0PSR2~T0PSR0 bits of the

TR01CON register determine the prescaler ratio and generate different clock rates for

the timer clock source. Counter value will be incremented by one (counting up)

according to the timer clock source and stored into the T0CH: T0CL register. The

clock source (Fcs) is selected from Fosc or F

T0PSR1~0. When the counting value is larger than TRL0H: TRL0L value, Timer 0

interrupt will occur, and the counter value will be reset to zero automatically.

/2 by T0CS and pre-scaled by

PLL

1

T

()

10:0Pr

+××= LTRLHTRLescaler

Fcs

Timer 0 Frequency:

Clock Source Fper / 2 TRL0H:TRL0L Prescaler Timer 0 Freq.

Fosc (32.768kHz) - FFFFh 1:64 128Hz

Fpll (8MHz) 4MHz 00FFh 1:1 15.6kHz

Fpll (16MHz) 8MHz 00FFh 1:1 31.2kHz

32 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 39

EPH3600

RISC II Series Microcontroller

8.1.2 Capture Mode: CPIN (Port B.5) Pin

Capture is a function that captures a Timer 0 value when an event occurs on CPIN pin.

The counter value is captured at: 1st rising edge, 2nd falling edge, etc.; 1st falling

edge, 2nd rising edge, etc.; every rising edge or every falling edge selected by

AGMD2~0 bit of the SFCR register. When an event edge is detected from CPIN

input pin, the interrupt flag CPIF is set. If a new event edge is detected before the old

value in T0CH: T0CL register is read, the old captured value will be lost.

The CPIN pin should be configured in capture function input by setting T0FNEN1~0

bits of TR2CON register.

1

T 0:00:0Pr

Fcs

()()

[]

−××=

CLTCHTCLTCHTescaler

OLDNEW

Capture Mode Example:

T0FNEN1~0

AGMD2~0

T0CH:T0CL

00

000

CPIN

Timer0

P1 P2 P3 P4 P5P6P7 P8 P9

CPIF

P2 P6

001 010

P10 P11

P7 P9P3

10

011

P12 P13P14

P15

P11 P13 P15

P16 P17

100

P18 P19 P20

P17 P21

101

P21

P22 P23 P24 P25 P26 P27 P28 P29 P30

P22

P31 P32

P33

8.1.3 Event Counter Mode: EVIN (Port B.5) Pin

Event counter is a function wherein the 16-bit counter value increments by one when

an event occurs on EVIN pin at: every rising edge or every falling edge selected by

AGMD2~0 bit of the SFCR register. In other words, the Timer 0 clock source is from

an external event (EVIN pin).

The EVIN pin should be configured in event counting function input by setting the

T0FNEN1~0 bits of the TR2CON register. The counting value of Timer 0 will be

stored in T0CH: T0CL registers.

Event Counter Mode Example:

T0FNEN1~0

AGMD2~0

Timer 0

T0CH:T0CL

00 11

010 011

EVIN

P0 P1 P2 P3 P4 P5

P0 P1 P2 P3 P4 P5

Product Specification (V0.1) 10.11.2007 • 33

(This specification is subject to change without further notice)

Page 40

EPH3600

RISC II Series Microcontroller

TRL0H, TRL0L (R25h, R24h): is used to store the values that are compared with

T0CH, T0CL (R3Eh, R3Dh): is used to store the Timer 0 counting value in Timer

TR01CON (R27h): Timer 0 and Timer 1 Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

T1WKEN T1EN T1PSR1 T1PSR0 IREN T0CS T0PSR1 T0PSR0

Bit 1 ~ Bit 0 (T0PSR1~T0PSR0): Timer 0 Prescaler select bit

T0PSR1: T0PSR0 Prescaler Value

Bit 2 (T0CS): Timer 0 clock source select bit

Timer 0 register.

0 mode and Event counter mode. But in Capture

mode, it is used to store the captured value.

00 1:1

01 1:4

10 1:16

11 1:64

“0” : Clock source is from Fosc

“1” : Clock source is from F

PLL/2

TR2CON (R28h): Timer 2 Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

IRPSR1 IRPSR0 T0FNEN1 T0FNEN0 T2EN T2CS T2PSR1 T2PSR0

Bit 5 ~ Bit 4 (T0FNEN1 ~ T0FNEN0): Timer 0 and Capture, event counter mode

selection bits.

SFCR (R44h): Special Function Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

AGMD2 AGMD1 AGMD0 WDTPSR1 WDTPSR0 SPHSB CSB1 CSB0

Bit 7 ~ Bit 5 (AGMD2 ~ AGMD0): Capture and Event Counter function e dg e

detector selection bits.

T0FNEN 1 ~ 0 Mode AGMD 2~0 Edge Mode

00 Disable - 01 Timer 0 - -

000 1st Rising edge, 2nd falling edge, etc.

001 1st Falling edge, 2nd rising edge, etc.

10 Capture

11 Event Counter

010 Every rising edge

011 Every falling edge

100 Every 4th rising edge

101 Every 16th rising edge

010 Every rising edge

011 Every falling edge

Note: 1. When changing from one mode to another, the Timer 0 must be initially disabled.

2. To avoid error, setup T0FNEN1 and T0FNEN0 simultaneously.

34 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 41

EPH3600

RISC II Series Microcontroller

CPUCON (R0Eh): MCU Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PEN - - SMCAND SMIER GLINT MS1 MS0

Bit 2 (GLINT): Global Interrupt Control Bit

“0” : Disable all interrupts

“1” : Enable all un-masked interrupt

INTCON (R22h): Interrupt Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

CPIE ADIE URXIE UTXIE UERRIE TMR2IE TMR1IE TMR0IE

Bit 0 (TMR0IE): Timer 0 Interrupt Control Bit

“0” : Disable Timer 0 interrupt

“1” : Enable Timer 0 interrupt

Bit 7 (CPIE): Capture Interrupt Control bit

“0” : Disable Capture interrupt

“1” : Enable Capture interrupt

INTSTA (R23h): Interrupt Status Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

CPIF ADIF URXI UTXI UERRI TMR2I TMR1I TMR0I

Bit 0 (TMR0I): Set to 1 when Timer 0 is larger than TRL0H ~ TRL0L value

Clear to 0 by software or Timer 0

Bit 7 (CPIF): Set to 1 when Capture input edge is detected

Clear to 0 by software or disable Capture

Code Example:

;===Timer 0 interrupt

TIMERINT:

PUSH

JBC INTSTA,TMR0I,Q_Time

BC INTSTA,TMR0I

BTG PORTC,3

Q_Time:

POP

RETI

;===Timer 0 = (8M/2) / [4 x 3FFF + 1]

Timer0SR:

:

System setting 8MHz

PC.2 Port C & D setting output port

:

; --- Fpll & Prescaler 1:4

;===Capture Input Interrupt

CAPINT:

PUSH

JBS INTSTA,CPIF,Q_ICAP

BC INTSTA,CPIF

BTG PORTC,3

BS INTFLAG,F_ICAP

Q_ICAP:

POP

RETI

;

;===1st falling edge,2nd rising edge, etc.

CAP_SR:

System setting 8MHz

PC.2 Port C & D setting output port

User setting F_ICAP flag.

Product Specification (V0.1) 10.11.2007 • 35

(This specification is subject to change without further notice)

Page 42

EPH3600

RISC II Series Microcontroller

MOV A,#00000101B

MOV TR01CON,A

; --- 4ms = (4 x 16383 + 1)/(8M/2)

MOV A,#0FFH

MOV TRL0L,A

MOV A,#03FH

MOV TRL0H,A

; --- Timer 0 mode

MOV A,#00010000B

MOV TR2CON,A

; --- Timer 0 interrupt enable

BS INTCON,TMR0IE

; --- Clear Timer 0 interrupt status.

BC INTSTA,TMR0I

; --- Enable global interrupt

BS CPUCON,GLINT

TimeLoop:

; --- Out Timer 0 count to Port C :D

MOVRP PORTC,T0CH

MOVRP PORTD,T0CL

SJMP TimeLoop

:

; --- Count end => 0FFFFH

MOV A,#0XFF

MOV TRL0H,A

MOV TRL0L,A

; --- PLL/2 & Prescaler 1:1

; --- (8MHz/2)/65536=61Hz

MOV A,#00000100B

MOV TR01CON,A

; --- 1st Falling - 2nd Rising

MOV A,#00100000B

MOV SFCR,A

BS INTCON,CPIE

; --- 10->Capture Enable

MOV A,#00100000B

MOV TR2CON,A

BC INTFLAG,F_ICAP

BS CPUCON,GLINT

CAP_LOOP:

JBC INTFLAG,F_ICAP,CAP_LOOP

BC INTFLAG,F_ICAP

; --- Out capture count to Port C :D

MOVRP PORTC,T0CH

MOVRP PORTD,T0CL

SJMP CAP_LOOP

; === Every rising edge

EVcntSR:

:

System setting 8MHz

Port C & D setting output port

:

MOV A,#0XFF ; Switch 256 times reload

MOV TRL0L,A

CLR TRL0H ; Count start 0000H

BS TR01CON,T0CS ; PLL/2

MOV A,#01000000B

MOV SFCR,A ; Rising edge

MOV A,#00110000B

MOV TR2CON,A ; 11->Event count Enable

EV_LOOP:

MOVRP PORTC,T0CH ; Out event count to Port C:D

MOVRP PORTD,T0CL

SJMP EV_LOOP

36 • Product Specification (V0.1) 10.11.2007

(This specification is subject to change without further notice)

Page 43

8.2 Timer 1 (8 Bits)

EPH3600

RISC II Series Microcontroller

TRL1

reload

PrescalerFosc

T1PSR1~0

underflow

Timer 1

Figure 8-2 Timer 1 Function Block Diagram

Timer 1 INT or

Timer 1 wake up

TR1C

Timer 1 is a general-purpose 8-bit down counter for applications requiring time

counting. Interrupt and wake up functions are offered for your application. The clock

source is from the oscillator clock.

A prescaler is also available for the timer. The T1PSR1~T1PSR0 bits of the

TR01CON register determine the prescaler ratio and generate different clock rates for

the timer clock source. Setting T1WKEN bit of the TR01CON register to 1 will enable

the Timer 1 underflow wake-up function in IDLE MODE.

Counting value will be decremented by one (count down) according to the real timer

clock source. When the counter underflows, the timer interrupt will be triggered if the

global interrupt and Timer 1 interrupt are both enabled. At the same time, the TRL1

value is automatically reloaded into the 8 bits counter.

1

T

()

11Pr

+××= TRLescaler

Focs

The Timer 1 frequency range is from 0.5Hz (TRL1 = 0FFh, prescaler = 1:256) to

8.192kHz (TRL1 = 0h, prescaler = 1:4). The clock source is from the oscillator clock

(Fosc).

TRL1 (R26h): Use to store the auto-reload value of Timer 1. When enabling

Timer 1 or an underflow occurs, TRL1 register value will

automatically be reloaded into the 8 bits counter.

TR1C (R4Ch): Use to store the Timer 1 Counting Value

Product Specification (V0.1) 10.11.2007 • 37

(This specification is subject to change without further notice)

Page 44

EPH3600

RISC II Series Microcontroller

TR01CON (R27h): Timer 0 and Timer 1 Control Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

T1WKEN T1EN T1PSR1 T1PSR0 IREN T0CS T0PSR1 T0PSR0

Bit 5 ~ Bit 4 (T1PSR1~T1PSR0): Timer 1 Pre-scale Select Bit.

Bit 6 (T1EN): Timer 1 Enable Control Bit