ELAN EM83040AH, EM83040ABQ, EM83040AAQ Datasheet

1

* This specification are subject to be changed without notice.

PreliminaryPreliminary

PreliminaryPreliminary

Preliminary

EM83040A

LCD CONTROLLER

5.31.2001

GENERAL DESCRIPTION

The EM83040A is a dot matrix LCD driver which is fabricated by low power CMOS technology. This chip

includes 80- bits shift register , 80 bits data latch and 80 bits level driver. A LCD RAM inside can be mapping

to LCD signal. It converts RAM data to parallel data and output lcd waveform to LCD.

FEATURES

(1) Supply power 2.6~6V

(2) Internal RAM : 2.5k x 4 bits

(3) RAM can be controlled by eight signals including four bit data bus.

(4) LCD drive voltage :<13V

(5) Duty: 1/32, 1/48, 1/80

(6) Build in DC converter double and triple

(7) Modularized function: connect to another 83040 to extent LCD matrix

(8) One DC converter enabled and other 83040 can shared with this.

(9) Internal regulator output for DC converter controlled by control register. (2.5V to 4.6V, 8 level)

(10) Chip form (EM83040AH), 128 pin package (14mmx20mm EM83040AAQ), 160 pin package (EM83040ABQ)

(11) Bias : 1/5 for 32 common, 1/7 for 48 common, 1/9 for 80 common. Fixed by internal circuit.

(12) Internal RC clock about 250 KHz.

APPLICATION

(1) Data Bank

(2) LCD toy

(3) Education computer

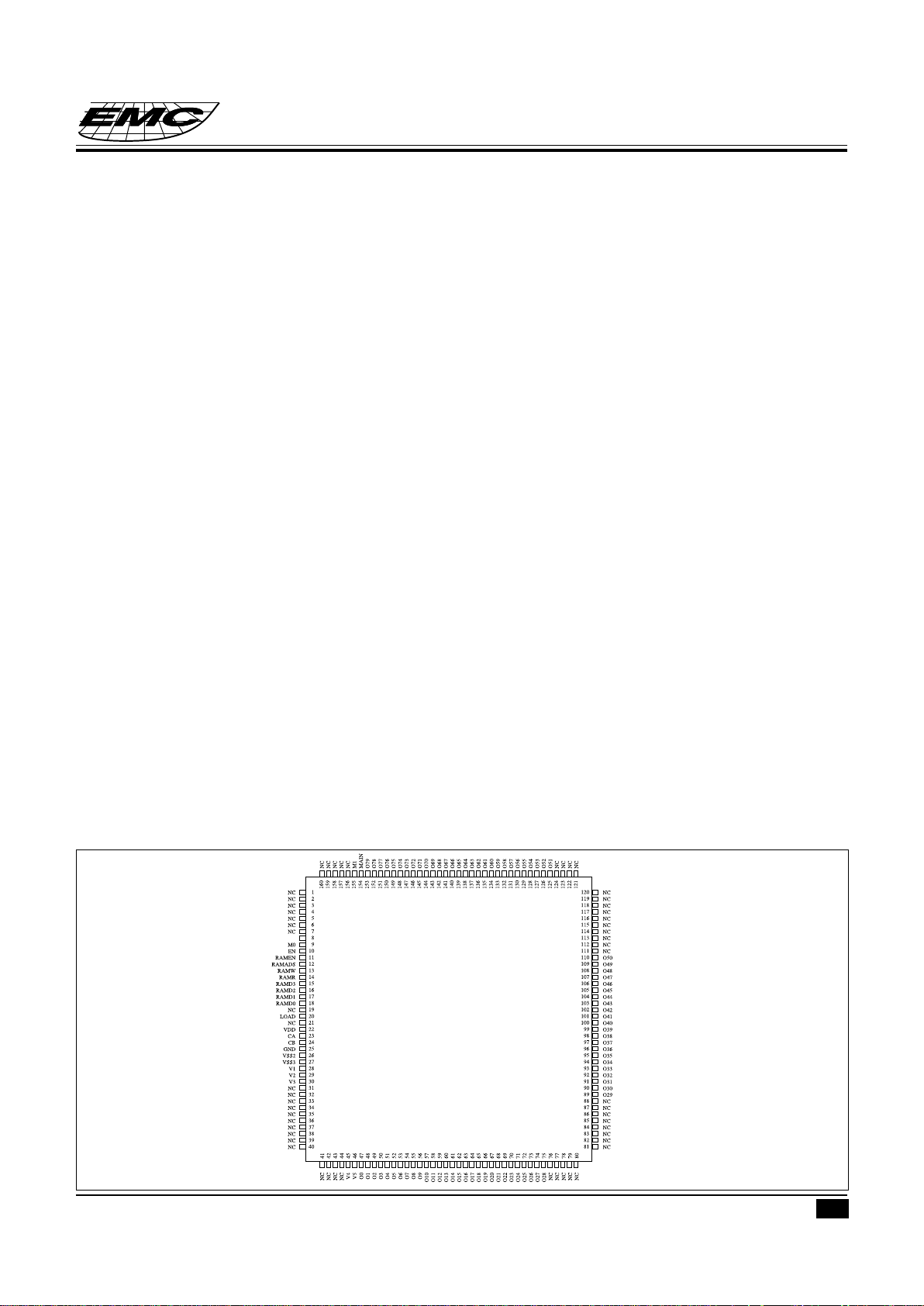

PIN ASSIGNMENTS

VREG

EM83040ABQ

* This specification are subject to be changed without notice.

EM83040A

LCD CONTROLLER

2

5.31.2001

PreliminaryPreliminary

PreliminaryPreliminary

Preliminary

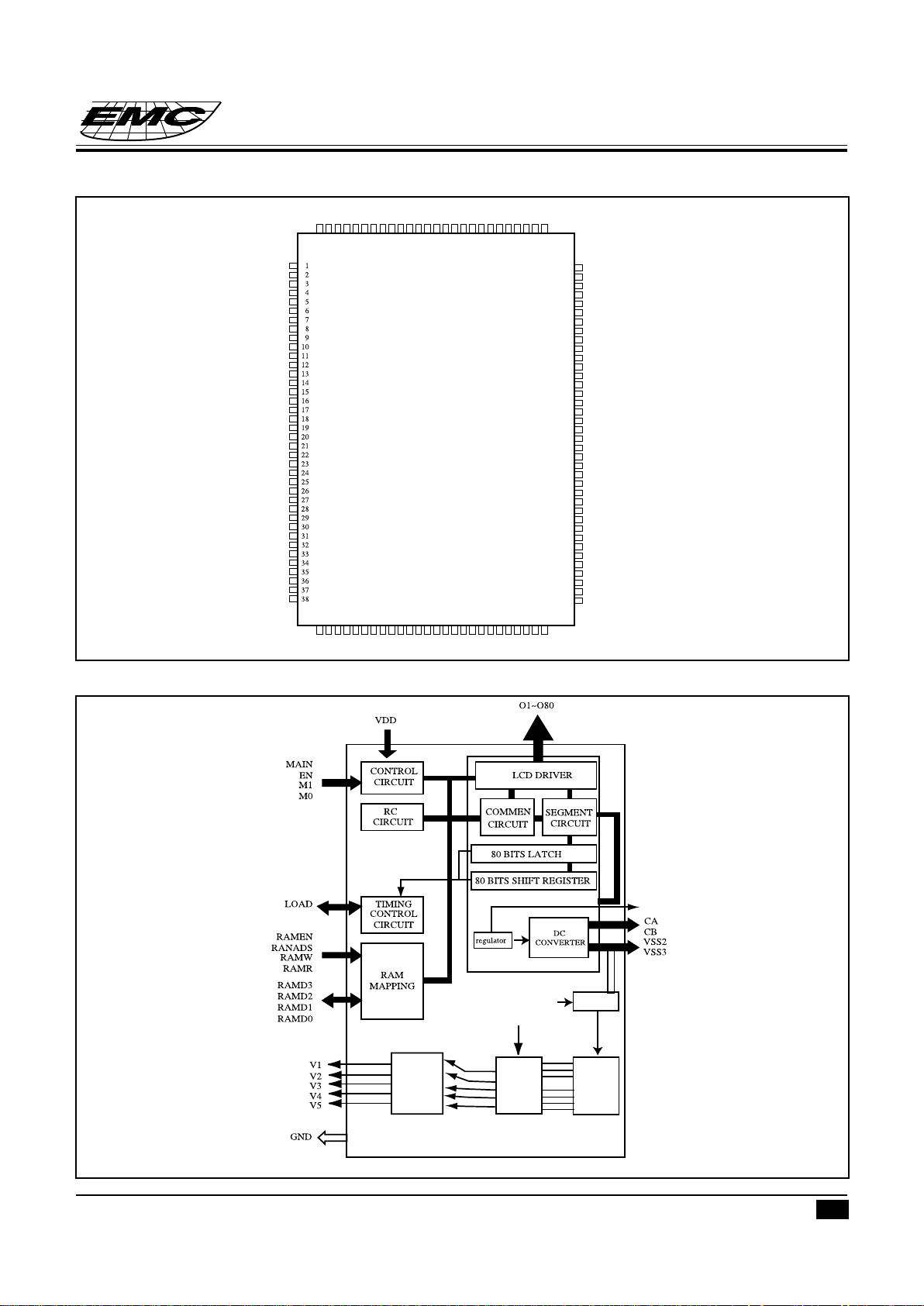

VREG

MUX

VSS2

or

VSS3

V_BIAS

BIAS

MUX

: : : : :

M1,M0

Buffer1

Buffer2

Buffer3

Buffer4

Buffer5

BLOCK DIAGRAM

EM83040AAQ

39404142434445464748495051525354555657585960616263

64

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

O79

MAIN

NC

NC

NC

NC

NC

M1

VREG

M0

EN

RAMEN

RAMADS

RAMW

RAMR

RAMD3

RAMD2

RAMD1

RAMD0

LOAD

VDD

CA

CB

GND

VSS2

VSS3

V1

V2

V3

V4

NC

NC

NC

NC

NC

NC

V5

O0

O1O2O3O4O5O6O7O8O9

O10

O11

O12

O13

O14

O15

O16

O17

O18

O19

O20

O21

O22

O23

O24

O25

O26

O52

O51

NC

NC

NC

NC

NC

NC

O50

O49

O48

O47

O46

O45

O44

O43

O42

O41

O40

O39

O38

O37

O36

O35

O34

O33

O32

O31

O30

P29

NC

NC

NC

NC

NC

NC

O28

O27

O78

O77

O76

O75

O74

O73

O72

O71

O70

O69

O68

O67

O66

O65

O64

O63

O62

O61

O60

O59

O58

O57

O56

O55

O54

O53

3

* This specification are subject to be changed without notice.

PreliminaryPreliminary

PreliminaryPreliminary

Preliminary

EM83040A

LCD CONTROLLER

5.31.2001

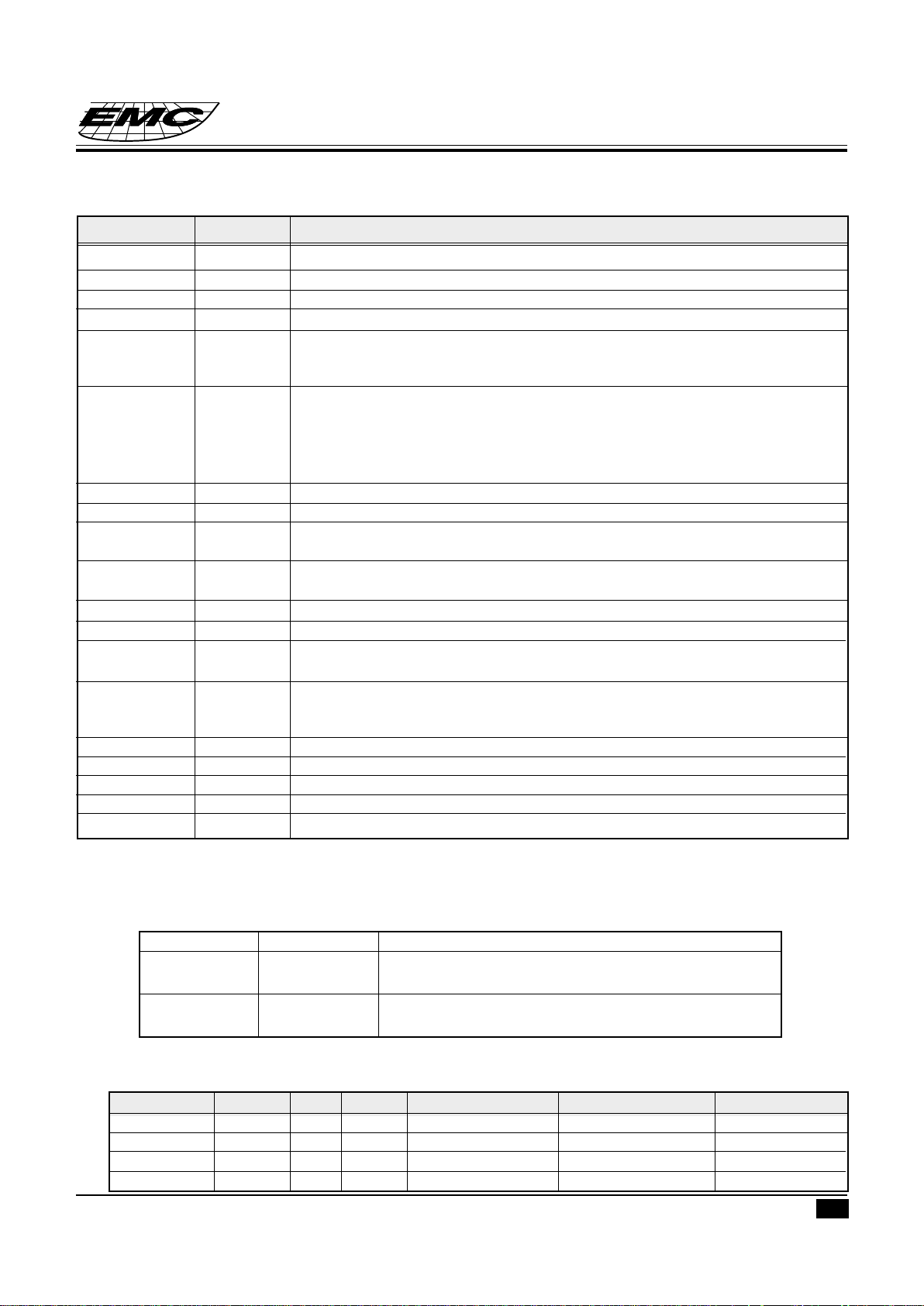

PIN DESCRIPTIONS

Symbol I/O Function

VDD Power

GND power Ground

VSS3 power EN=0 and MAIN=1, 3*regulator output, EN=1 ,VSS3=VDD

VSS2 Power EN=0 and MAIN=1, 2*regulator output, EN=1, VSS2=VDD

MAIN I Master or slave control signal.

MAIN=1 ,master unit

MAIN=0 , slave unit

EN I This pin control whole chip power. This chip will work when this pin is

connectted to ground. And whole chip will disable when connect to VDD voltage.

EN=0 and MAIN=1 the chip will generate VSS2, VSS3, LOAD signal and internal

RC clock.

EN=1, standby mode

M1 I Mode select

M0 I Mode select

RAMEN RAM read and write control signal.

1 => can not read and write. 0=> can read and write.

RAMADS RAM data select signal

1=> RAM Data , 0=>Address

RAMW RAM write signal, low write

RAMR RAM read signal, low read

RAMD3~ RAM data or address bus

RAMD0

LOAD I/O LCD load signal between one COMMON signal to another .

MAIN=1 , the master unit will output LOAD signal.

MAIN=0 , the slave will accept the signal from master unit.

VREG power regulator output, connect a capacitor to ground.

CA I Coupling capacitor

CB I Coupling capacitor

V1~V5 I Reference voltage input ,highest V1..lowest V5

O1~O80 O LCD waveform output

FUNCTION DESCRIPTIONS

(1)User can use MAIN pin to chose master unit or slave unit.

MAIN Unit Function

1 MASTER Generate these signals

Load, VSS2, VSS3, Internal RC clock

0 SLAVE Accept these signals

Load, V1, V2, V3, V4, V5

(2)User can use M1,M2 to chose four modes. As followed

MASTER MAIN M1 M0 Segment Common Bias

Mode1 1 0 0 Reserved for test

Mode2 1 0 1 O(80:1)=C(80:1) 1/9

Mode3 1 1 0 O(32:1)=S(32:1) O(80:33)=C(48:1) 1/7

Mode4 1 1 1 O(48;1)=S(48:1) O(80:49)=C(32:1) 1/5

* This specification are subject to be changed without notice.

EM83040A

LCD CONTROLLER

4

5.31.2001

PreliminaryPreliminary

PreliminaryPreliminary

Preliminary

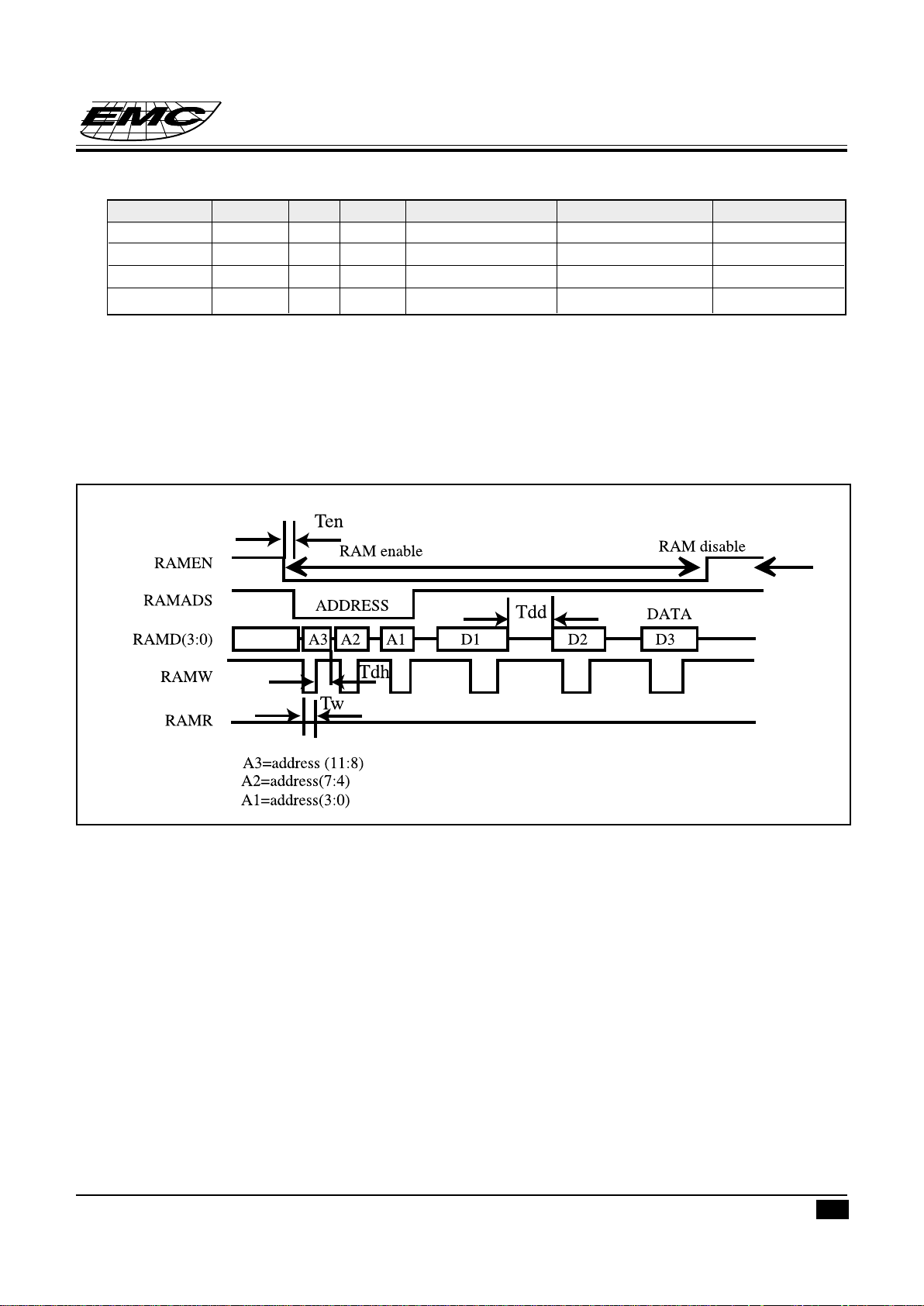

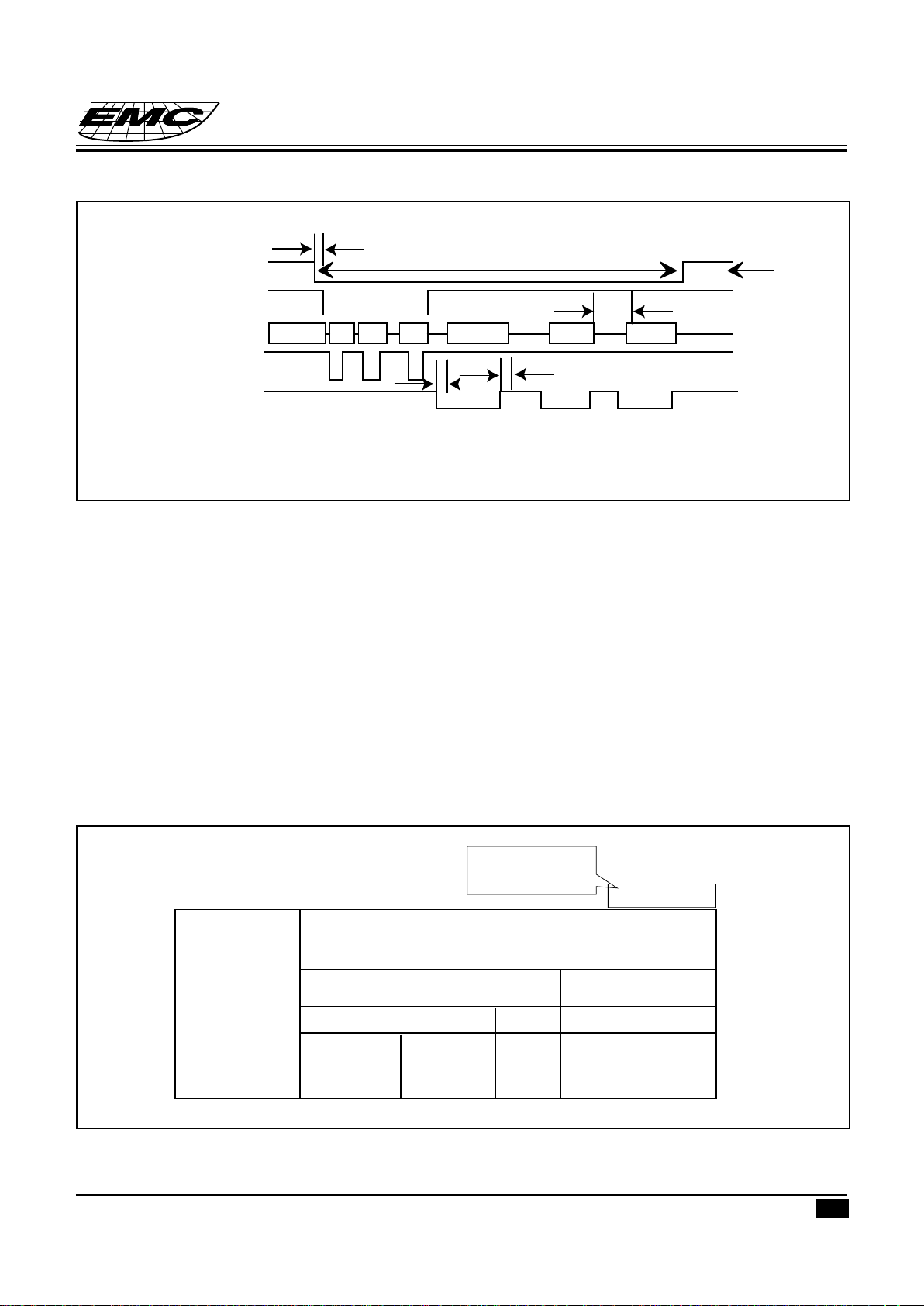

Fig.3

LCD RAM can be written or read with control signal. The RAMEN pin can select a RAM which can be read or

write . The RAMADS pin can select whether RAMD(3:0) are data or address of RAM. At the address mode ,

RAMADS is low and user should sent address three times. From address (11:8) to address (3:0). Then it will go

into data mode when RAMADS is high. In data mode , user can sent one or more nibble data which address can

be increased by internal counter.

Once the RAMEN pin is high, the RAM can not read and write.

SLAVE MAIN M1 M0 Segment Common

Mode1 0 0 0 Reserved for test

Mode2 0 0 1 O(80:1)=S(80:1) 1/9

Mode3 0 1 0 O(80:1)=S(80:1) 1/7

Mode4 0 1 1 O(80:1)=S(80:1) 1/5

* S=Segment, C=common

* (M1, M0) for master must same as slave unit.

(3)RAM control

Writer mode

5

* This specification are subject to be changed without notice.

PreliminaryPreliminary

PreliminaryPreliminary

Preliminary

EM83040A

LCD CONTROLLER

5.31.2001

RAMEN

RAMADS

RAMD(3:0)

RAMW

RAMR

A3 A2 A1 D1 D2 D3

RAM enable

RAM disable

ADDRESS

DATA

A3=address (11:8)

A2=address(7:4)

A1=address(3:0)

Ten

Tdv

Tdh

Tdd

Fig.4

address2559 ...................

address0031 ...................

address0063 ................... address0051 ........................................................

..........................

address1023 ...................

address1535 ...................

address2047 ...................

address2547 ......................................................................................................................... address2528

address2035 ......................................................................................address2019...............address2016

address1523 ............................................................address1511........................................address1504

address1011 .......................address1003 ............................................................................. address0992

LCD RAM

Area 10

Area 11

Area 9

Area 8

Area 5

Area 6

Area 7

Area 4 Area 3

Area 2

Area 1

Address 2560

Control register

Address 2560

Control register

EMPTY AREA

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

................................... address0032

address0019 ...................

s80s79s78s77

s4 s3 s2 s1

s48 s32

s16

address0011................ address7...........

address0003............... address0000

COM80

COM64

COM48

COM32

COM2

COM1

Fig.5

As same as write mode , user has to sent address three times. And read data from RAM one by one which

address can be increased by internal counter. NOTE!! Be sure to make RAMR low pulse 2 µS (Tdv+data)

width and 2 µS (Tdd) high width at least.

(5) RAM mapping

RAM address is from 0 to address 2559

User fill “1” to LCD RAM , LCD driver will generate “light” waveform. Otherwise , it will generate a

“dark” waveform. The LCD RAM area is mapped to segment 1 to segment 80 from address 0 to address

19. And user can refer to fig.5 to get the idea of LCD ram mapping. The other RAM can use as general

RAM for data storage. And the RAM of address 2560 is a control register.

Loading...

Loading...