ELAN EM78911, EM78R911 Datasheet

1

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

EM78911

I.General Description

The EM78911 is an 8-bit CID (Call Identification) RISC type microprocessor with low power , high speed CMOS

technology . Integrated onto a single chip are on_chip watchdog (WDT) , RAM , ROM , programmable real time

clock /counter , internal interrupt , power down mode , LCD driver , FSK decoder ,CALL WAITING decoder, DTMF

generator and tri-state I/O . The EM78911 provides a single chip solution to design a CID of calling message_display .

II.Feature

CPU

•Opera t ing voltage range : 2.5V〜5.5V

•16K× 13 on chip ROM

•2.8K× 8 on chip RAM

•Up to 36 bi-directional tri-state I/O ports

•8 level stack for subroutine nesting

•8-bit real time clock/counter (TCC)

•Two sets of 8 bit counters can be interrupt sources

•Selective signal sources and trigger edges , and with overflow interrupt

•Programmable free running on chip watchdog timer

•99.9% single instruction cycle commands

•Four modes (internal clock 3.579MHz)

1. Sleep mode : CPU and 3.579MHz clock turn off, 32.768KHz clock turn off

2. Idle mode : CPU and 3.579MHz clock turn off, 32.768KHz clock turn on

3. Green mode : 3.579MHz clock turn off, CPU and 32.768KHz clock turn on

4. Normal mode : 3.579MHz clock turn on , CPU and 32.768KHz clock turn on

•Ring on voltage detector and low battery detector

•Input port wake up function

•9 interrupt source , 4 external , 5 internal

•100 pin QFP or chip

•Port key scan function

•Clock frequency 32.768KHz

•Eight R-option pins

CID

•Operation Volltage 3.5 〜6V for FSK

•Operation Volltage 2.5 〜6V for DTMF

•Bell 202 , V.23 FSK demodulator

•DTMF generator

•Ring detector on chip

CALL WAITING

•Operation Volltage 3.6 〜5.5V

•Compatible with Bellcore special report SR-TSV-002476

•Call-Waiting (2130Hz plus 2750Hz) Alert Signal Detector

•Good talkdown and talkoff performance

•Sensitivity compensated by adjusting input OP gain

LCD

•LCD operation voltage chosen by software

•Common driver pins : 16

•Segment driver pins : 60

•1/4 bias

2

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

•1/8,1/16 duty

III.Application

1. adjunct units

2. answering machines

3. feature phones

IV.Pin Configuration

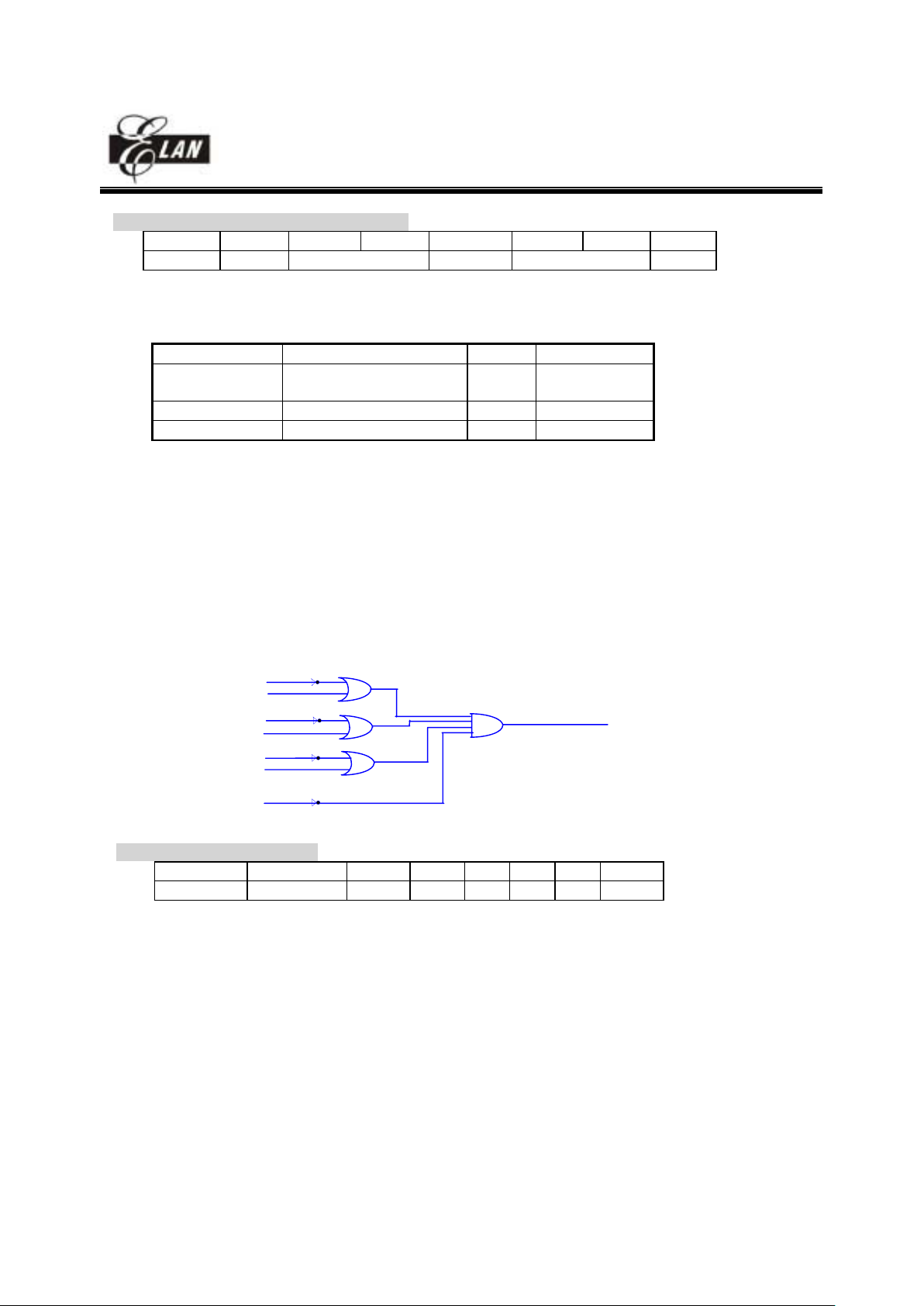

Fig1. Pin Assignment

OTP writer PIN NAME MASK ROM PIN NAME P.S.

1.VDD VDD,AVDD

2.VPP /RESET

3.DINCK P77

4.ACLK P76

5.PGMB P75

6.OEB P74

7.DATA P73

8.GND VSS,AVSS

AVSS

DTMF

PLLC

RINGTIME

RDET1

RING

TIP

GAIN

CWTIP

XIN

XOUT

AVDD

COM7

COM6

COM5

COM4

COM3

COM2

COM1

COM0

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG29

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

SEG22

SEG21

SEG20

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

VSS

TEST

COM8/P60

COM9/P61

COM10/P62

COM11/P63

COM12/P64

COM13/P65

COM14/P66

COM15/P67

SEG40/P54

SEG41/P55

SEG42/P56

SEG43/P57

SEG44/P80

SEG45/P81

SEG46/P82

SEG47/P83

SEG48/P84

SEG49/P85

SEG50/P86

SEG51/P87

SEG52/P90

SEG53/P91

SEG54/P92

SEG55/P93

SEG56/P94

SEG57/P95

SEG58/P96

SEG59/P97

P70/INT0

P71/INT1

P72/INT2

P73/INT3

P74

P75

P76

P77

/RESET

VDD

1234567891011121314151617181920212223242526272829

30

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

3

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

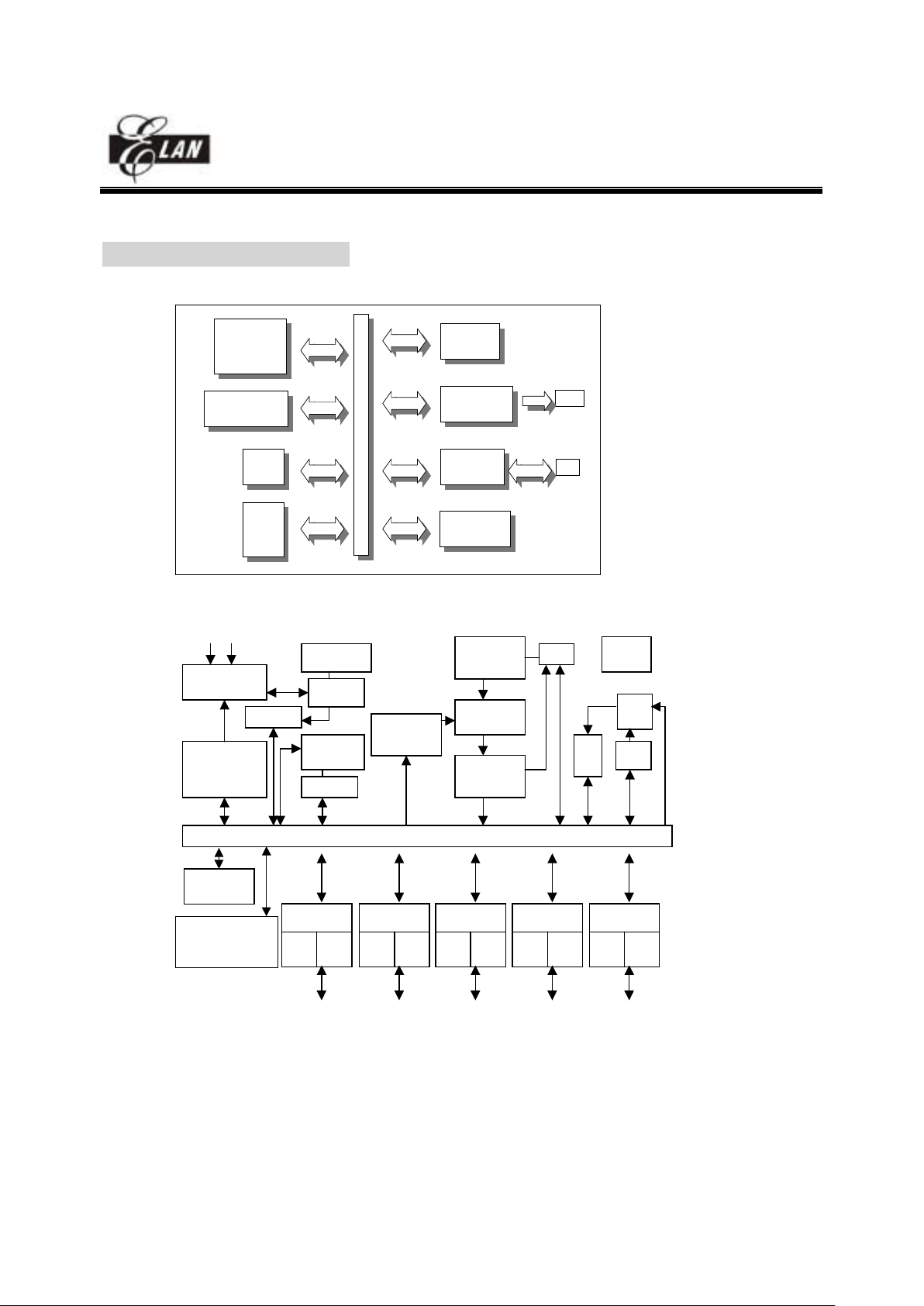

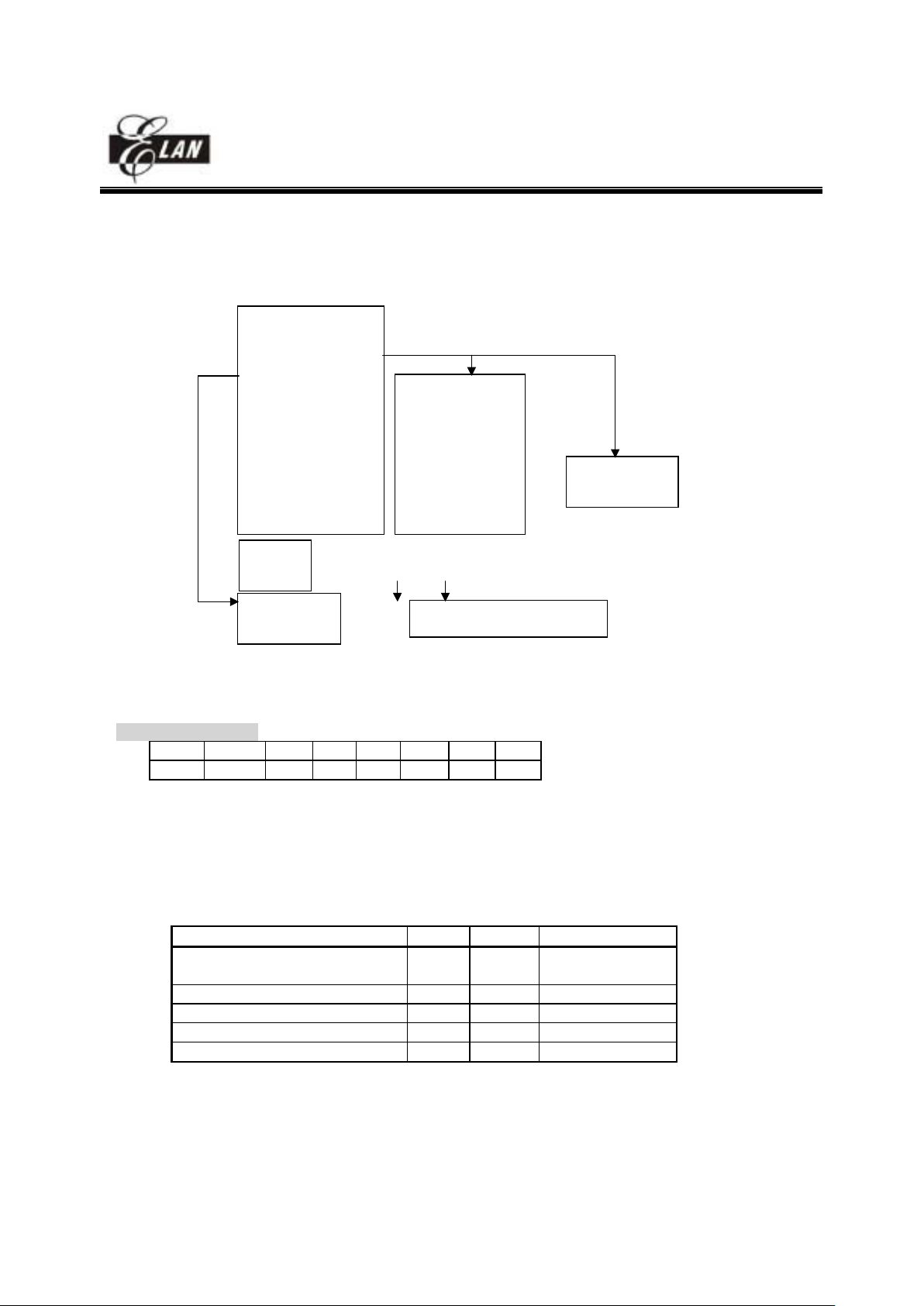

V.Functional Block Diagram

Fig2. Block diagram1

Fig3. Block diagram2

CPU

CPU

TIMING CONTROL

TIMING CONTROL

TIMER

TIMER

ROM

ROM

RAM

RAM

LCD DRIVER

LCD DRIVER

LCD

IO PORT

IO PORT I/O

FSK

DTMF

CALL WAITING

FSK

DTMF

CALL WAITING

Xin Xout

Oscillator

timing control

Control sleep

and wake-up

on I/O port

R1(TCC)

WDT timer

prescalar

GENERAL

RAM

R4

Interruption

control

ROM

Instruction

register

Instruction

decoder

R2

STACK

ALU

ACC

R3

R5

DATA & CONTROL BUS

2.5k RAM

PORT6

IOC6 R6

P60~P67

PORT7

IOC7 R7

P70~P77

PORT8

IOC8 R8

P80~P87

PORT9

IOC9 R9

P90~P97

PORT5

IOC5 R5

P54~P57

FSK

DTMF

CALL WAITING

4

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

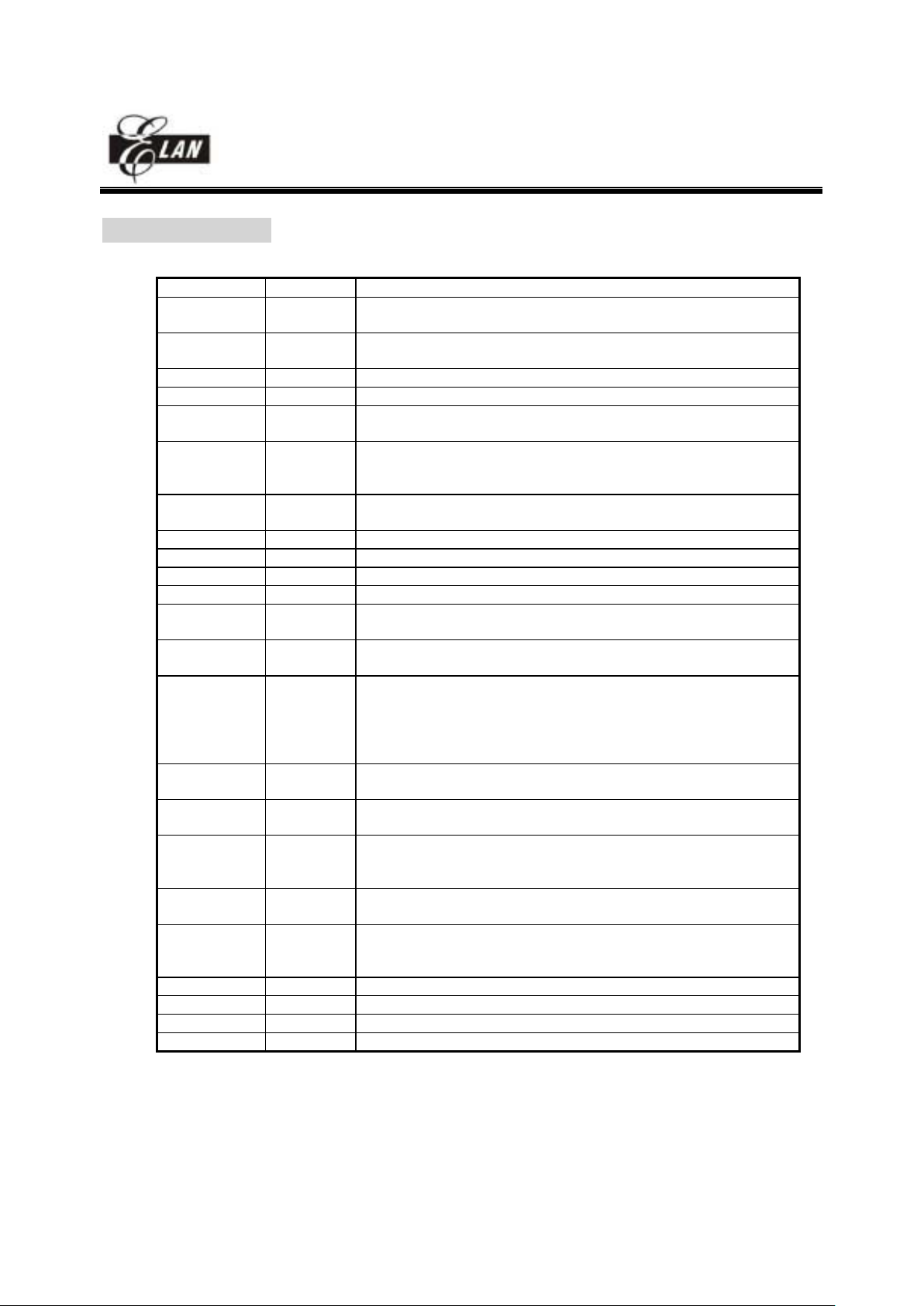

VI.Pin Descriptions

PIN I/O DESCRIPTION

VDD

AVDD

POWER digital power

analog power

GND

AVSS

POWER digital ground

analog ground

Xtin I Input pin for 32.768 kHz oscillator

Xtout O Output pin for 32.768 kHz oscillator

COM0..COM7

COM8..COM15 O O (PORT6)

Common driver pins of LCD drivers

SEG0...SEG43

SEG44..SEG51

SEG52..SEG59

O

O (PORT8)

O (PORT9)

Segment driver pins of LCD drivers

PORT9 AS FUNCTION KEY CAN WAKE UP WATCHDOG.

PLLC I Phase loop lock capacitor, connect a capacitor 0.01u to 0.047u with

AVSS

TIP I Should be connected with TIP side of twisted pair lines for FSK.

RING I Should be connected with RING side of twisted pair lines for FSK.

CWTIP I Should be connected with TIP side of twisted pair lines for CW.

GAIN I OP output pin for gain adjustment.

RDET1 I Detect the energy on the twisted pair lines . These two pins coupled to

the twisted pair lines through an attenuating network.

/RING TIME I Determine if the incoming ring is valid.An RC network may be

connected to the pin.

INT0

INT1

INT2

INT3

PORT7(0)

PORT7(1)

PORT7(2)

PORT7(3)

PORT7(4:7)

PORT7(0)~PORT7(3) signal can be interrupt signals.

Int2 and int3 has the same interrupt flag.

IO port

P5.4 ~P5.7 PORT5 PORT 5 can be INPUT or OUTPUT port each bit.

Shared with LCD segment signals

P6.0 ~P6.7 PORT6 PORT 6 can be INPUT or OUTPUT port each bit.

Shared with LCD common signals

P7.0 ~P7.7 PORT7 PORT 7 can be INPUT or OUTPUT port each bit.

Internal Pul l high function.

Key scan function.

P8.0 ~P8.7 PORT8 PORT 8 can be INPUT or OUTPUT port each bit.

And shared with Segment signal.

P9.0 ~P9.7 PORT9 PORT 9 can be INPUT or OUTPUT port each bit.

And can be set to wake up watch dog timer.

And shared with Segment signal.

TEST I Test pin into test mode , normal low

DTMF O DTMF tone output

RESET I

5

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

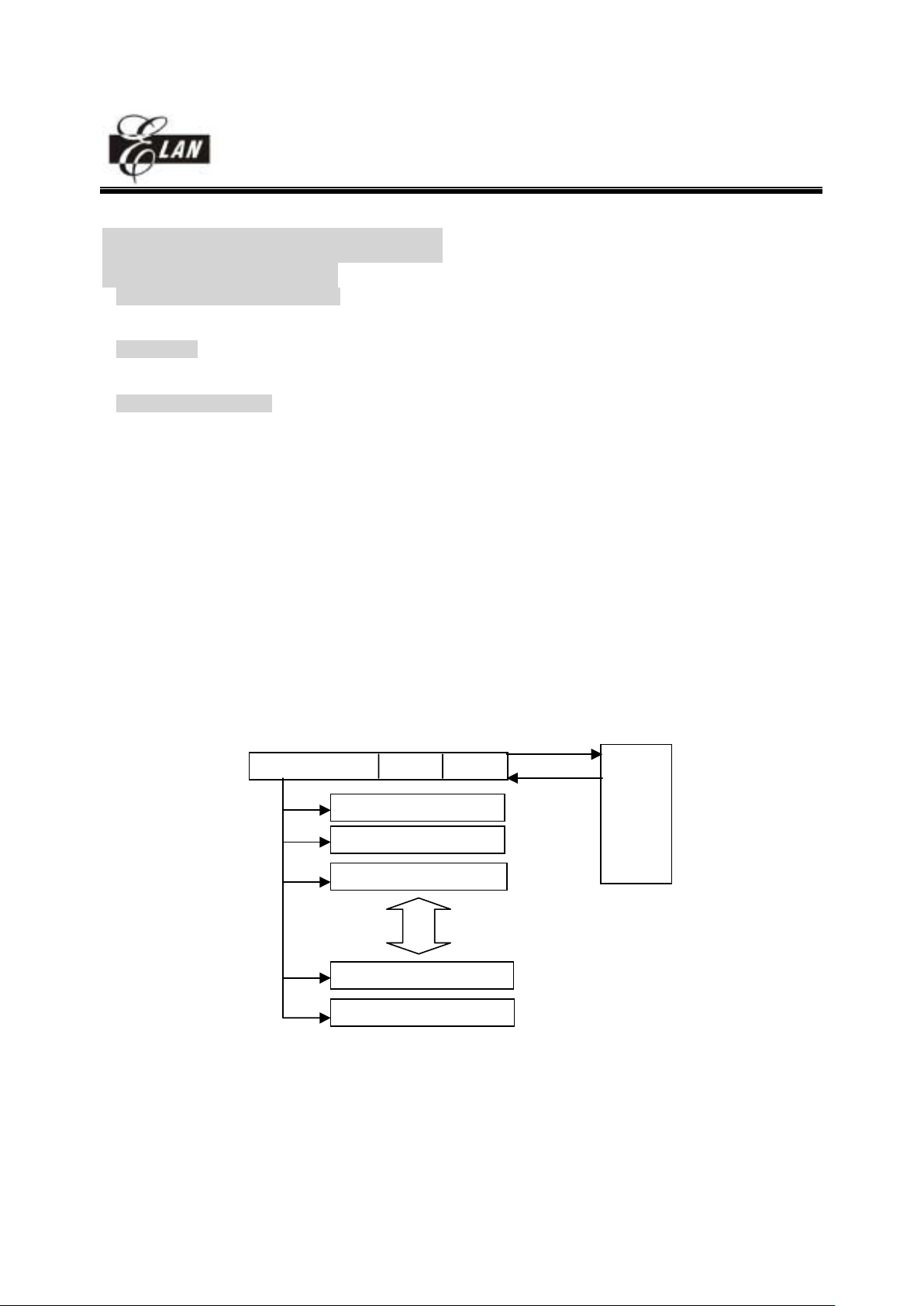

VII.Functional Descriptions

VII.1 Operational Registers

1. R0 (Indirect Addressing Register)

* R0 is not a ph ysically imp lemented register. It is useful as indirect a ddressing p ointer. A ny instructio n using

R0 as register actually accesses data pointed by the RAM Select Register (R4).

2. R1 (TCC)

* Increased by an external signal edge applied to TCC , or by the instruction cycle clock.

Written and read by the program as any other register.

3. R2 (Program Counter)

* The structure is depicted in Fig. 4.

* Generates 16K × 13 on-chip ROM addresses to the relative programming instruction codes.

* "JMP" instruction allows the direct loading of the low 10 program counter bits.

* "CALL" instruction loads the low 10 bits of the PC, PC+1, and then push into the stack.

* "RET'' ("RETL k", "RETI") instruction loads the program counter with the contents at the top of stack.

* "MOV R2,A" allows the loading of an address from the A register to the PC, and the ninth and tenth bits are

cleared to "0''.

* "ADD R2,A" allows a relative address be added to the current PC, and contents of the ninth and tenth bits are

cleared to "0''.

* "TBL" allows a relative address be added to the current PC, and contents of the ninth and tenth bits don't

change. The most significant bit (A10~A13) will be loaded with the content of bit PS0~PS3 in the status register

(R5) upon the execution of a "JMP'', "CALL'', "ADD R2,A'', or "MOV R2,A'' instruction .

Fig.4 Program counter organization

PC

A13 A12 A11 A10 A9 A8 A7~A0

0000 PAGE0 0000~03FF

0001 PAGE1 0400~07FF

1110 PAGE14 3800~3BFF

1111 PAGE15 3C00~3FFF

0010 PAGE3 0800~0BFF

STACK1

STACK2

STACK3

STACK4

STACK5

STACK6

STACK7

STACK8

CALL

RET

RETL

RETI

6

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

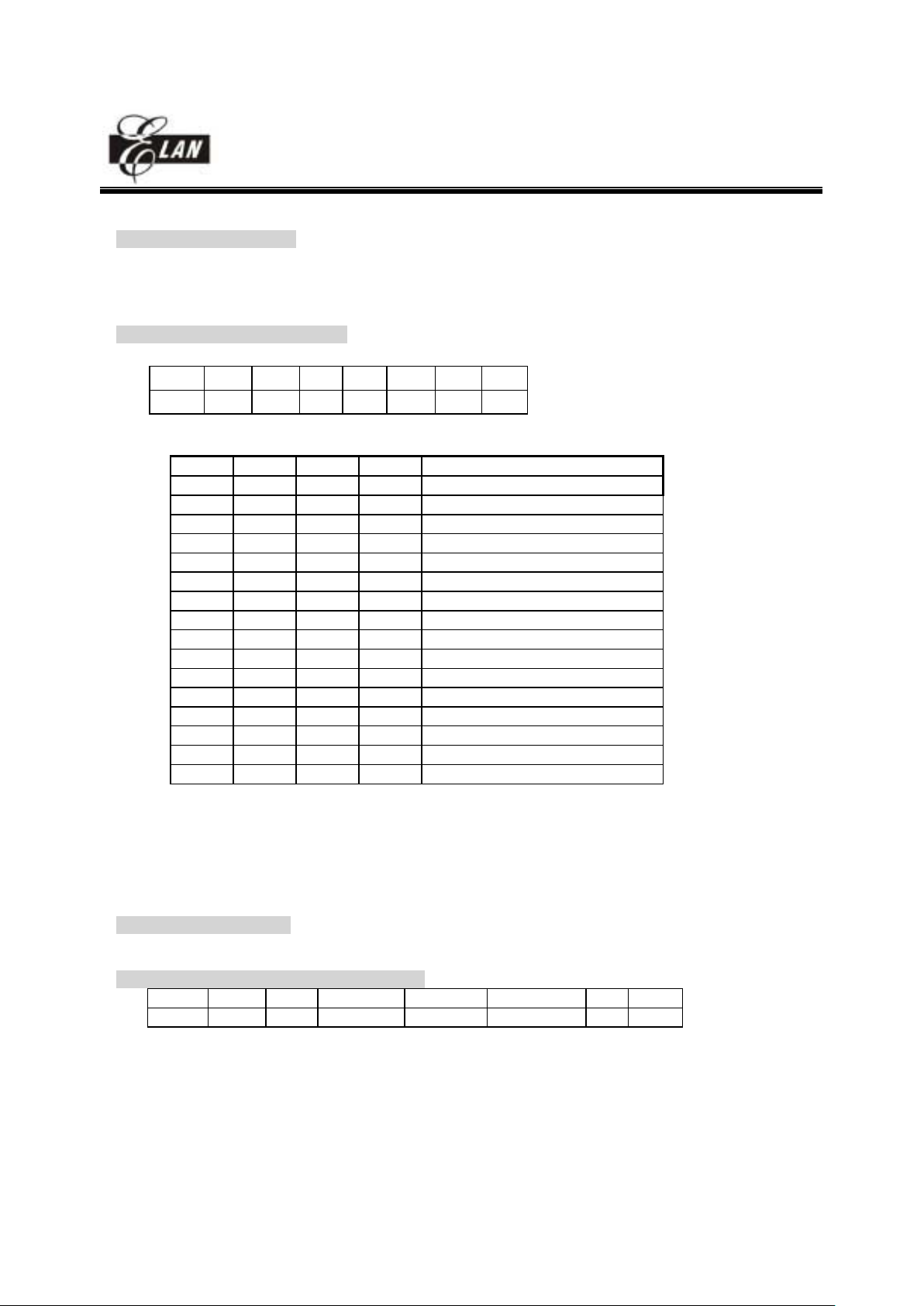

Fig.5 Data memory configuration

4. R3 (Status Register)

7 6 5 4 3 2 1 0

CAS PAGE - T P Z DC C

* Bit 0 (C) Carry flag

* Bit 1 (DC) Auxiliary carry flag

* Bit 2 (Z) Zero flag

* Bit 3 (P) Power down bit. Set to 1 during power on or by a "WDTC" command and reset to 0 by a "SLEP"

command.

* Bit 4 (T) Time-out bit. Set to 1 by the "SLEP" and "WDTC" command, or during power up and reset to 0 by

WDT timeout.

EVENT T P REMARK

WDT wake up from

sleep mode

0 0

WDT time out (not sleep mode) 0 1

/RESET wake up from sleep 1 0

power up 1 1

Low pulse on /RESET x x x .. don't care

* Bit 5 unused

* Bit 6 PAGE : change IOCB ~ IOCE to another page , 0/1 => page0 / page1

* Bit7 (CAS : CALL WAITING Output)

0/1= CW data valid/No data

00

01

02

03

04

05

06

07

08

09

0A

0B

0C

0D

0E

0F

R0

R1(TCC)

R2(PC)

R3(STATUS)

R4(RSR)

R5(ROM PAGE & R5)

R6(PORT6)

R7(PORT7)

R8(PORT8)

R9(PORT9)

RA(CLK,FSK)

RB(DTMF)

RC(2.5K RAM ADDRES S)

RD(2.5K RAM DATA)

RE(WDT)

RF(INT FLAG)

10

:

1F

16X8

COMMON

REGISTER

20

:

3F

BANK0 ~BANK3

32X8 ~32X8

REGISTER

IOC6

IOC7

IOC8

IOC9

IOCA

IOCB(LCD ADDRESS)

IOCC(LCD DATA)

IOCD(PULL HIGH)

IOCE(IO, LCD)

IOCF(INT CONTROL)

IOCB(COUNTER1)

IOCC(COUNTER2)

IOCD(R-OPTION)

page0

page1

BANK1 BANK2 …………..BANK10

256X8 256X8 …………….256X8

RC(ADDRESS) RD(DATA)

0

:

255

ADDRESS REGISTER CONTROL REGISTER

(PAGE0)

CONTROL REGISTER

(PAGE1)

7

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

5. R4 (RAM Select Register)

* Bits 0 ~ 5 are used to select up to 64 registers in the indirect addressing mode.

* Bits 6 ~ 7 determine which bank is activated among the 4 banks.

* See the configuration of the data memory in Fig. 5.

6. R5 (Program Page Select Register)

7 6 5 4 3 2 1 0

R57 R56 R55 R54

PS3 PS2 PS1 PS0

* Bit 0 (PS0) ~ 3 (PS3) Page select bits

Page select bits

PS3 PS2 PS1 PS0 Program memory page (Address)

0 0 0 0 Page 0

0 0 0 1 Page 1

0 0 1 0 Page 2

0 0 1 1 Page 3

0 1 0 0 Page 4

0 1 0 1 Page 5

0 1 1 0 Page 6

0 1 1 1 Page 7

1 0 0 0 Page 8

1 0 0 1 Page 9

1 0 1 0 Page 10

1 0 1 1 Page 11

1 1 0 0 Page 12

1 1 0 1 Page 13

1 1 1 0 Page 14

1 1 1 1 Page 15

*User can use PAGE instruction to change page. To maintain program page by user. Otherwise, user can use

far jump (FJMP) or far call (FCALL) instructions to program user's code. And the program page is

maintained by EMC's complier. It will change user's program by inserting instructions within program.

*Bit4~7 : PORT5 4-bit I/O register

6. R6 ~ R9 (Port 6 ~ Port 9)

* Four 8-bit I/O registers.

7. RA (FSK Status Register)(bit 0,1,2,4 read only)

7 6 5 4 3 2 1 0

IDLE

/358E /LPD /LOW_BAT /FSKPWR DATA /CD /RD

* Bit0 (Read Only) (Ring detect signal) 0/1 : Ring Valid/Ring Invalid

* Bit1(Read Only)(Carrier detect signal) 0/1 : Carrier Valid/Carrier Invalid

* Bit2(Read Only)(FSK demodulator output signal)

Fsk data transmitted in a baud rate 1200 Hz.

* Bit3(read/write)(FSK block power up signal)

1/0 : FSK demodulator block power up/FSK demodulator power down

8

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

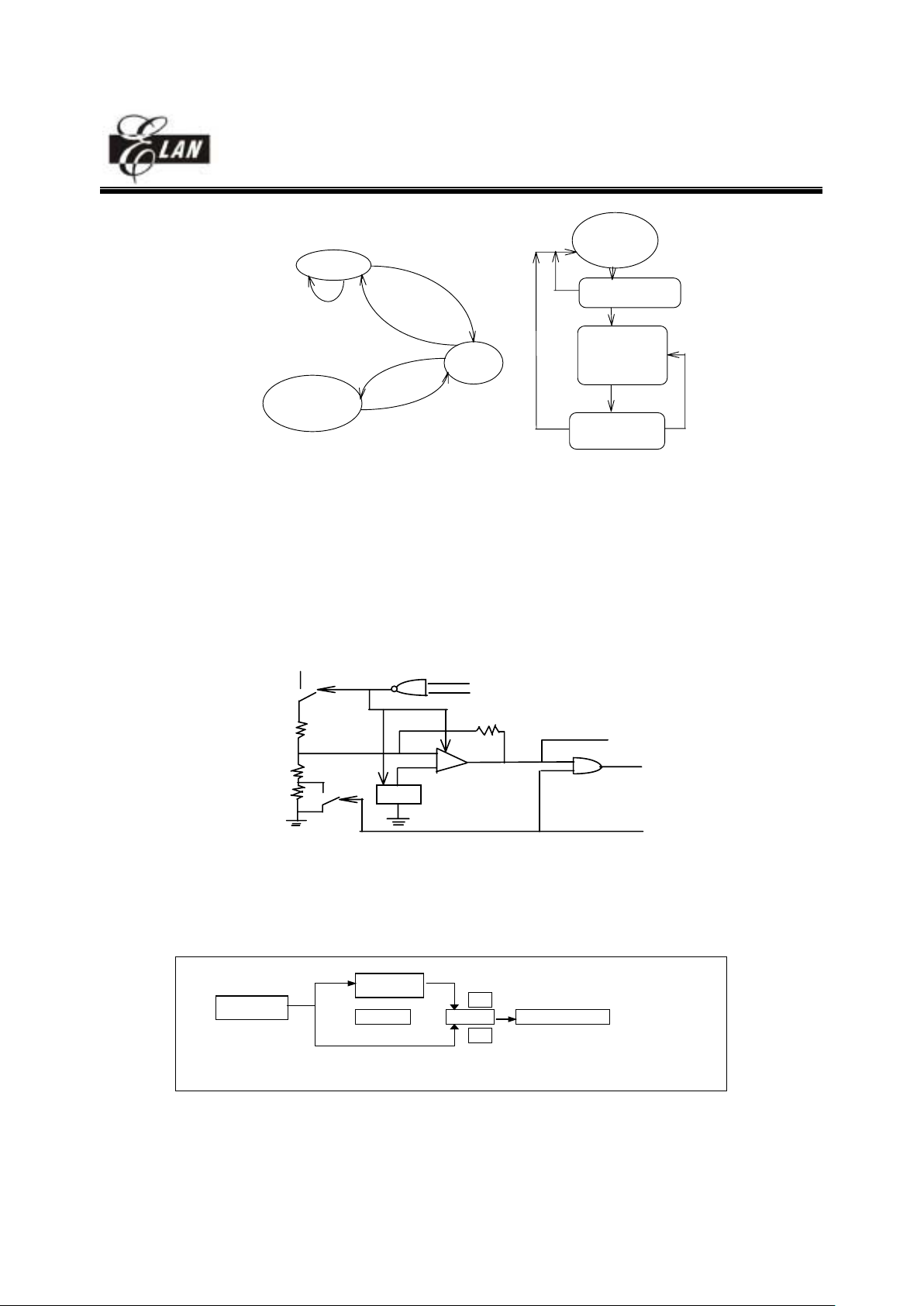

* The relation between Bit0 to Bit3 is shown in Fig.6.

sleep mode

sleep modesleep mode

sleep mode

wake up

wake up wake up

wake up

mode

modemode

mode

/RINGTIME ='0'

/RINGTIME ='0'/RINGTIME ='0'

/RINGTIME ='0'

FSK decoder

FSK decoderFSK decoder

FSK decoder

begin its work

begin its workbegin its work

begin its work

/FSKPWR='1'

/FSKPWR='1'/FSKPWR='1'

/FSKPWR='1'

DATA transfer

DATA transfer DATA transfer

DATA transfer

to Micro

to Microto Micro

to Micro

/RD and /CD ='1' and

/RD and /CD ='1' and/RD and /CD ='1' and

/RD and /CD ='1' and

nothing to do for 30

nothing to do for 30 nothing to do for 30

nothing to do for 30

sec , /FSKPWR='0'

sec , /FSKPWR='0'sec , /FSKPWR='0'

sec , /FSKPWR='0'

or external keys

or external keysor external keys

or external keys

pressed

pressedpressed

pressed

/RD and /CD ='1'

/RD and /CD ='1'/RD and /CD ='1'

/RD and /CD ='1'

SLEEP MODE

SLEEP MODESLEEP MODE

SLEEP MODE

Begin

Begin Begin

Begin

set /FSKPWR='0'

set /FSKPWR='0'set /FSKPWR='0'

set /FSKPWR='0'

/RINGTIME ='0'

/RINGTIME ='0'/RINGTIME ='0'

/RINGTIME ='0'

or external keys

or external keysor external keys

or external keys

pressed

pressedpressed

pressed

WAKE UP MODE

WAKE UP MODEWAKE UP MODE

WAKE UP MODE

8-bit wake up and

8-bit wake up and 8-bit wake up and

8-bit wake up and

set /FSKPWR='1'

set /FSKPWR='1'set /FSKPWR='1'

set /FSKPWR='1'

accept data from

accept data fromaccept data from

accept data from

FSK decoder

FSK decoderFSK decoder

FSK decoder

/RD and /CD ='1'

/RD and /CD ='1'/RD and /CD ='1'

/RD and /CD ='1'

data end and 30

data end and 30data end and 30

data end and 30

sec nothing to do.

sec nothing to do.sec nothing to do.

sec nothing to do.

Yes

YesYes

Yes

No

NoNo

No

No

NoNo

No

Yes

YesYes

Yes

STATE Diagram between 8-bit

STATE Diagram between 8-bit STATE Diagram between 8-bit

STATE Diagram between 8-bit

and FSK decoder

and FSK decoderand FSK decoder

and FSK decoder

Flow Diagram between 8-bit

Flow Diagram between 8-bit Flow Diagram between 8-bit

Flow Diagram between 8-bit

and FSK decoder

and FSK decoderand FSK decoder

and FSK decoder

Fig6. The relation between Bit0 to Bit3.

* Bit4(Read Only)(Low battery signal) 0/1 = Battery voltage is low/Normal .

If the VDD voltage is under low power range (controlled by IOCA bit0) then sends a '0' signal to

/LOW_BAT bit or a '1' signal to this Bit.

* Bit5(read/Write)(Low battery detect enable)

0/1 = low battery detect DISABLE/ENABLE.

The relation between /LPD,/POVD and /LOW_BAT can see Fig7.

Vdd

VddVdd

Vdd

Vref

VrefVref

Vref

s2

s2s2

s2

1 on

1 on1 on

1 on

0 off

0 off0 off

0 off

s2

s2s2

s2

1 on

1 on1 on

1 on

0 off

0 off0 off

0 off

1 on

1 on1 on

1 on

to Low bat

to Low batto Low bat

to Low bat

To reset

To resetTo reset

To reset

/POVD

/POVD/POVD

/POVD

/LPD

/LPD/LPD

/LPD

/LPD

/LPD/LPD

/LPD

++++

----

1 on

1 on1 on

1 on

Fig7. The relation between /LPD,/POVD

* Bit6(read/write)(PLL enable signal)

0/1=DISABLE/ENABLE

The relation between 32.768K and 3.579M can see Fig8.

Fig8. The relation between 32.768K and 3.579K .

Sub-clock

32.768KH z

PLL

3.579M Hz

RA bit6 sw itch To system clock

1

0

9

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

* Bit7 IDLE: sleep mode selection bit

0/1=sleep mode/IDLE mode. This bit will decide SLEP instruction which mode to go.

These two modes can be waken up by TCC clock or Watch Dog or PORT9 and run from “SLEP” next

instruction.

Wakeup signal SLEEP mode IDLE mode GREEN mode NORMAL mode

RA(7,6)=(0,0)

+ SLEP

RA(7,6)=(1,0)

+ SLEP

RA(7,6)=(x,0)

no SLEP

RA(7,6)=(x,1)

no SLEP

TCC time out X Wake-up

+ Interrupt

+ Next instruction

Interrupt

Interrupt

WDT time out RESET Wake-up

+ Next instruction

RESET RESET

Port9

/RINGTIME pin

RESET Wake-up

+ Next instruction

X X

PORT70~73 X Wake-up

+ Interrupt

+ Next instruction

Interrupt

Interrupt

*P70 ~ P73 's wakeup function is co ntrolled by IOCF(1,2,3) and ENI instruction.

*P70 's wakeup signal is a rising or falling signal defined by CONT REGISTER bit7.

*/RINGTIME pin , Port9 ,Port71,Port72 and Port73 's wakeup signal is a falling edge signal.

8. RB(DTMF tone row and column register) (read/write)

7 6 5 4 3 2 1 0

c7 c6 c5 c4 r3 r2 r1 r0

* Bit 0 - Bit 3 are row-frequency tone.

* Bit 4 - Bit 7 are column-frequency tone.

* Initial RB is equal to high. Bit 7 ~ 0 are all " 1" , turn off DTMF power .

bit 3~0 Row freq

1110 699.2Hz 1 2 3 A

1101 771.6Hz 4 5 6 B

1011 854Hz 7 8 9 C

0111 940.1Hz * 0 # D

Column freq 1203Hz 1331.8Hz 1472Hz 1645.2Hz

bit 7~4 1110 1101 1011 0111

9. RC(CALLER ID address)(read/write)

7 6 5 4 3 2 1 0

CIDA7 CIDA6 CIDA5 CIDA4 CIDA3 CIDA2 CIDA1 CIDA0

* Bit 0 ~ Bit 7 select CALLER ID RAM address up to 256.

10. RD(CALLER ID RAM data)(read/write)

* Bit 0 ~ Bit 8 are CALLER ID RAM data transfer register.

User can see IOCA register how to select CID RAM banks.

10

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

11. RE(LCD Driver,WDT Control)(read/write)

7 6 5 4 3 2 1 0

CWPWR /WDTE /WUP9H /WUP9L /WURING LCD_C2 LCD_C1 LCD_M

* Bit0 (LCD_M):LCD_M decides the methods, including duty, bias, and frame frequency.

* Bit1~Bit2 (LCD_C#):LCD_C# decides the LCD display enable or blanking. change the display duty must set

the "LCD_C2,LCD_C1" to "00".

LCD_C2,LCD_C1 LCD Display Control LCD_M duty bias

0 0 change duty

Disable(turn off LCD)

0

1

1/16 1/4

1/8 1/4

0 1 Blanking : :

1 1 LCD display enable : :

* Bit3 (/WURING, RING Wake Up Enable): used to enable the wake-up function of /RINGTIME input pin.

(1/0=enable/disable)

* Bit4 (/WUP9L, PORT9 low nibble Wake Up Enable): used to enable the wake-up function of low nibble in

PORT9.(1/0=enable/disable)

* Bit5 (/WUP9H, PORT9 high nibble Wake Up Enable): used to enable the wake-up function of high nibble in

PORT9.(1/0=enable/disable)

* Bit6 (/WDTE,Watch Dog Timer Enable)

Control bit used to enable Watchdog timer.(1/0=enable/disable)

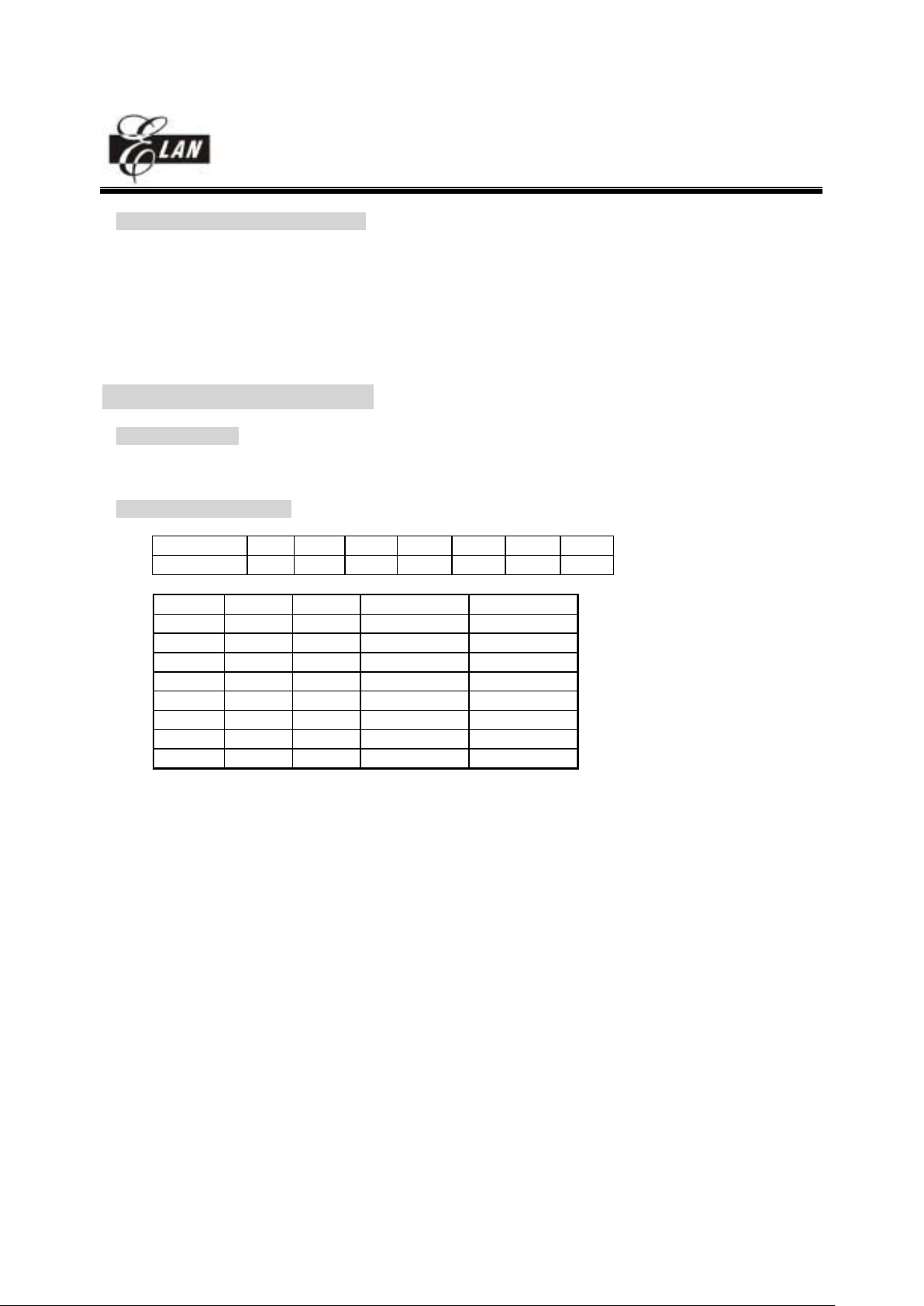

The relation between Bit3 to Bit6 can see the diagram 9.

* Bit7(Power control of Call Waiting circuit)

.(1/0=enable circuit /disable circuit) Please enable PLL before enable Call Waiting circuit.

/WURING

/WURING/WURING

/WURING

/RINGTIME

/RINGTIME/RINGTIME

/RINGTIME

/WUP9L

/WUP9L/WUP9L

/WUP9L

PORT9(3:0)

PORT9(3:0)PORT9(3:0)

PORT9(3:0)

/WUP9H

/WUP9H/WUP9H

/WUP9H

PORT9(7:4)

PORT9(7:4)PORT9(7:4)

PORT9(7:4)

/WDTE

/WDTE/WDTE

/WDTE

/WDTEN 0/1=enable/disable

/WDTEN 0/1=enable/disable/WDTEN 0/1=enable/disable

/WDTEN 0/1=enable/disable

fig.9 Wake up function and control signal

12. RF (Interrupt Status Register)

7 6 5 4 3 2 1 0

INT3 FSK/CW C8_2 C8_1 INT2 INT1 INT0 TCIF

* "1" means interrupt request, "0" means non-interrupt

* Bit 0 (TCIF) TCC timer overflow interrupt flag. Set when TCC timer overflows .

* Bit 1 (INT0) external INT0 pin interrupt flag .

* Bit 2 (INT1) external INT1 pin interrupt flag .

* Bit 3 (INT2) external INT2pin interrupt flag .

* Bit 4 (C8_1) internal 8 bit counter interrupt flag .

* Bit 5 (C8_2) internal 8 bit counter interrupt flag .

* Bit 6 ( FSK/CW ) FSK data or Call waiting data interrupt flag

* Bit 7 (INT3) external INT3 pin interrupt flag.

* High to low edge trigger , Refer to the Interrupt subsection.

* IOCF is the interrupt mask register. User can read and clear.

11

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

13. R10~R3F (General Purpose Register)

* R10~R3F (Banks 0~3) all are general purpose registers.

VII.2 Special Purpose Registers

1. A (Accumulator)

* Internal data transfer, or instruction operand holding

* It's not an addressable register.

2. CONT (Control Register)

7 6 5 4 3 2 1 0

INT_EDGE

INT TS TE PAB PSR2 PSR1 PSR0

* Bit 0 (PSR0) ~ Bit 2 (PSR2) TCC/WDT prescaler bits.

PSR2 PSR1 PSR0 TCC Rate WDT Rate

0 0 0 1:2 1:1

0 0 1 1:4 1:2

0 1 0 1:8 1:4

0 1 1 1:16 1:8

1 0 0 1:32 1:16

1 0 1 1:64 1:32

1 1 0 1:128 1:64

1 1 1 1:256 1:128

* Bit 3 (PAB) Prescaler assignment bit.

0/1 : TCC/WDT

* Bit 4 (TE) TCC signal edge

0: increment from low to high transition on TCC

1: increment from high to low transition on TCC

* Bit 5 (TS) TCC signal source

0: internal instruction cycle clock

1: 16.384KHz

* Bit 6 : (INT)

INT enable flag

0: interrupt masked by DISI or hardware interrupt

1: interrupt enabled by ENI/RETI instructions

* Bit 7 : INT_EDGE

0:P70 's interruption source is a rising edge signal.

1:P7 0 's interruption source is a falling edge signal.

* CONT register is readable and writable.

12

EM78911

EM78911EM78911

EM78911

88--bit micro

bit micro-

-controller

controller

3. IOC5 (I/O Port Control Register)

7 6 5 4 3 2 1 0

IOC57 IOC56 IOC55 IOC54 0 0 0 P5S

* Bit0: P5S is switch register for I/O port or LCD signal switching.

0/1= normal I/O port/SEGMENT output .

* Bit1~3: unused

* Bit 4 to Bit7 are PORT5 I/O direction control registers.

* "1" put the relative I/O pin into high impedance, while "0" put the relative I/O pin as output.

4. IOC6 ~ IOC9 (I/O Port Control Register)

* four I/O direc tion control registers.

* "1" put the relative I/O pin into high impedance, while "0" put the relative I/O pin as output.

* User can see IOCB register how to switch to normal I/O port.

5. IOCA (CALLER ID RAM,IO ,PAGE Control Register)(read/write,initial "00000000")

7 6 5 4 3 2 1 0

P8SH P8SL 0 CALL_4 CALL_3 CALL_2 CALL_1 RANGE

* Bit0 : register to control low power detection range .

0/1=3.2V/3.6V

* Bit4~Bit1:"000" to "1001" are ten blocks of CALLER ID RAM area. User can use 2.5K RAM with RD

ram address.

* Bit 5 unused

* Bit6: port8 low nibble switch, 0/1= normal I/O port/SEGMENT output .

* Bit7: port8 high nibble switch , 0/1= normal I/O port/SEGMENT output

6. IOCB (LCD ADDRESS)

PAGE0 : Bit6 ~ Bit0 = LCDA6 ~ LCDA0

The LCD display data is stored in the data RAM . The relation of data area and COM/SEG pin is as below:

COM15 ~ COM8 COM7 ~ COM0

40H (Bit15 ~ Bit8) 00H (Bit7 ~ Bit0) SEG0

41H 01H SEG1

: : :

: : :

: : :

: : :

7AH 4AH SEG58

7BH 3BH SEG59

7CH 3CH Empty

: : :

7FH 3FH Empty

PAGE1 : 8 bit up-counter (COUNTER1) preset and read out register . ( write = preset ) . After a

interruption , it will count from “00”.

Loading...

Loading...