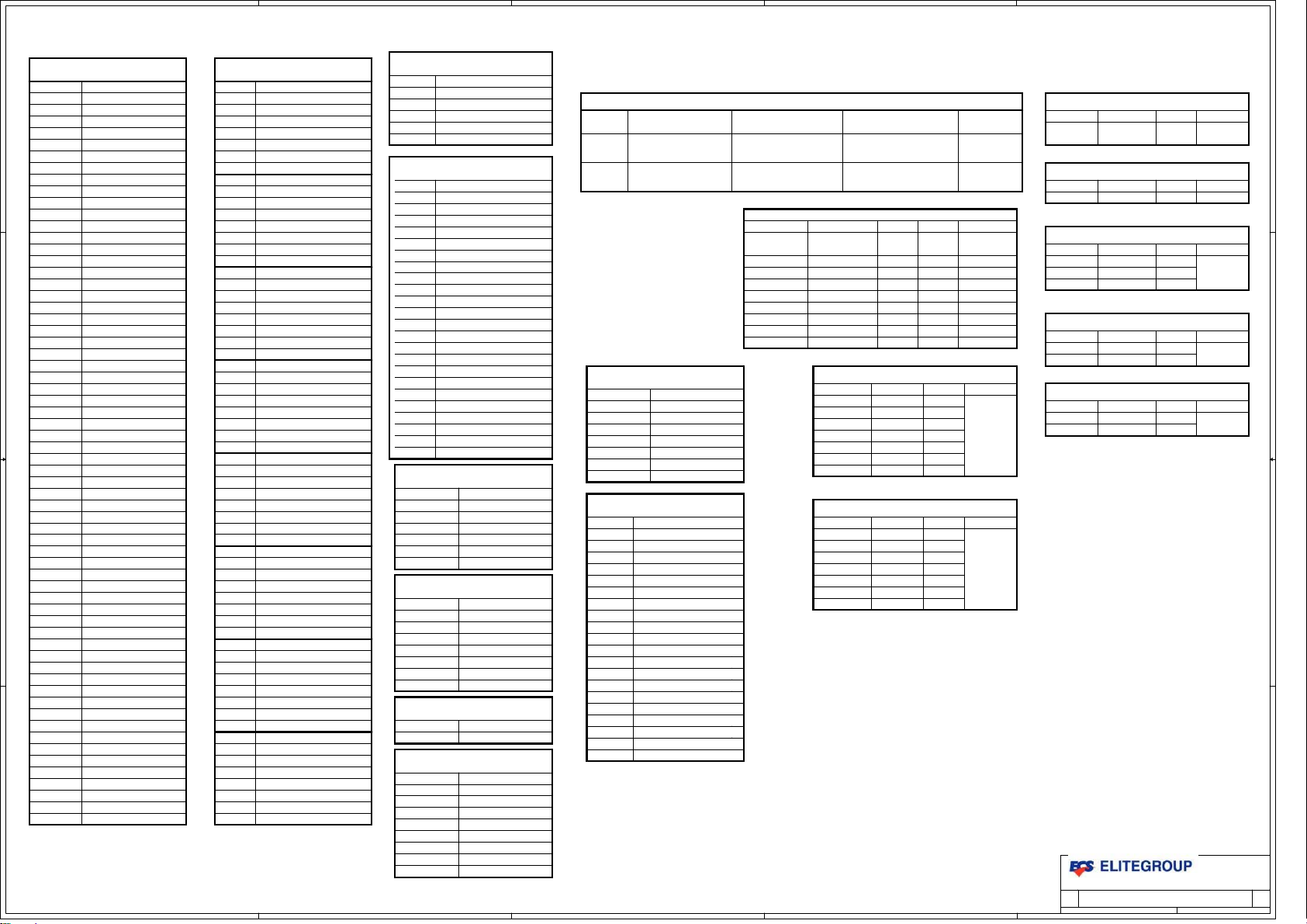

Page 1

5

4

3

2

1

Model : J10IL1

Intel Diamondville CPU +Intel 945GSE+ Intel ICH7-M

D D

PAGE

CONTENT

COVER PAGE1.

2. SYSTEM BLOCK DIAGRAM

POWER DIAGRAM & SEQUENCE3.

4.

5.

6.

7.

8.

C C

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

B B

19.

20.

21.

22.

23.

24.

25.

26.

27.

A A

28.

29.

SEQUENCE DIAGRAM

GPIO & POWER CONSUMPTION

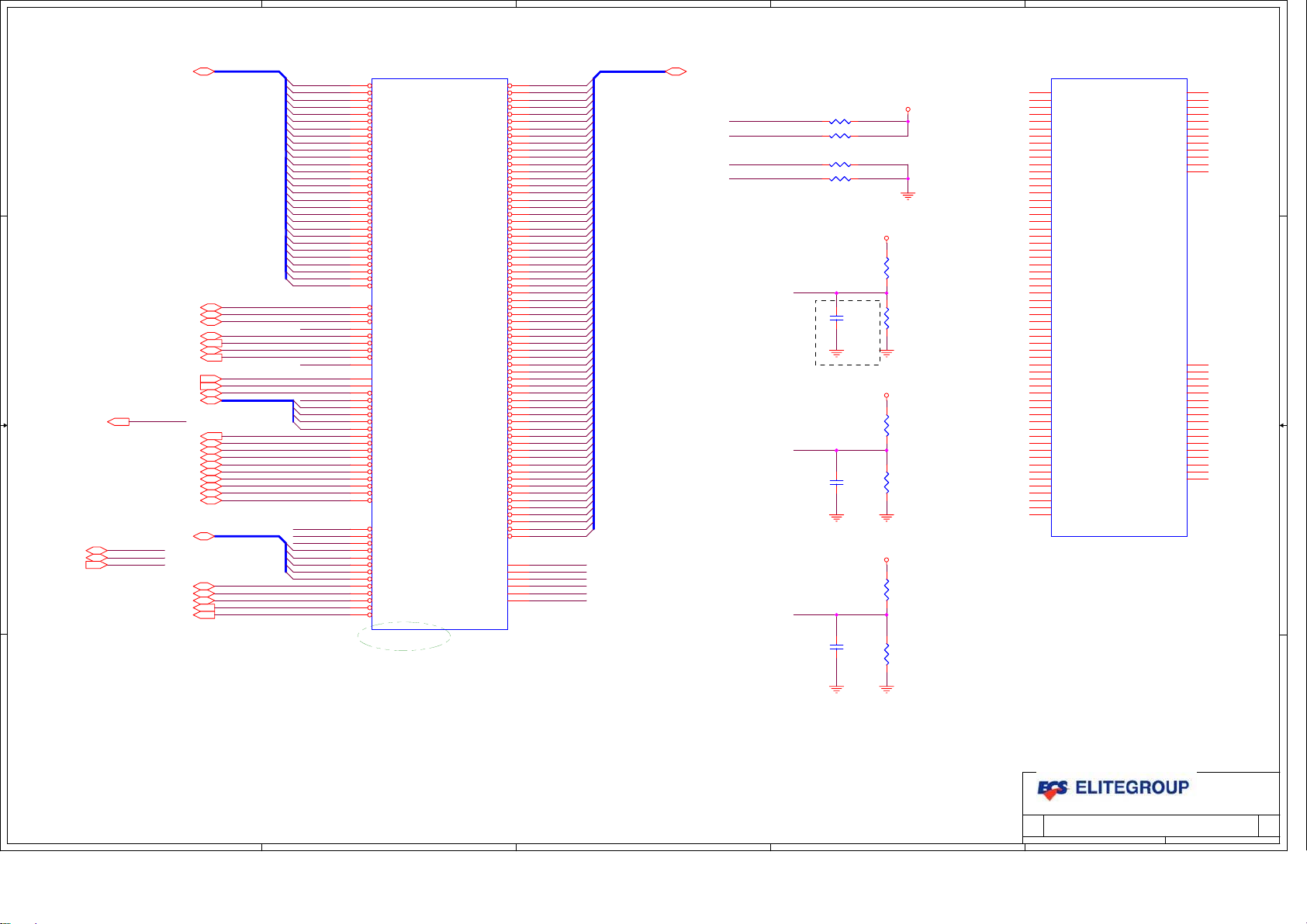

CPU Diamondville-1/2

CPU Diamondville-2/2

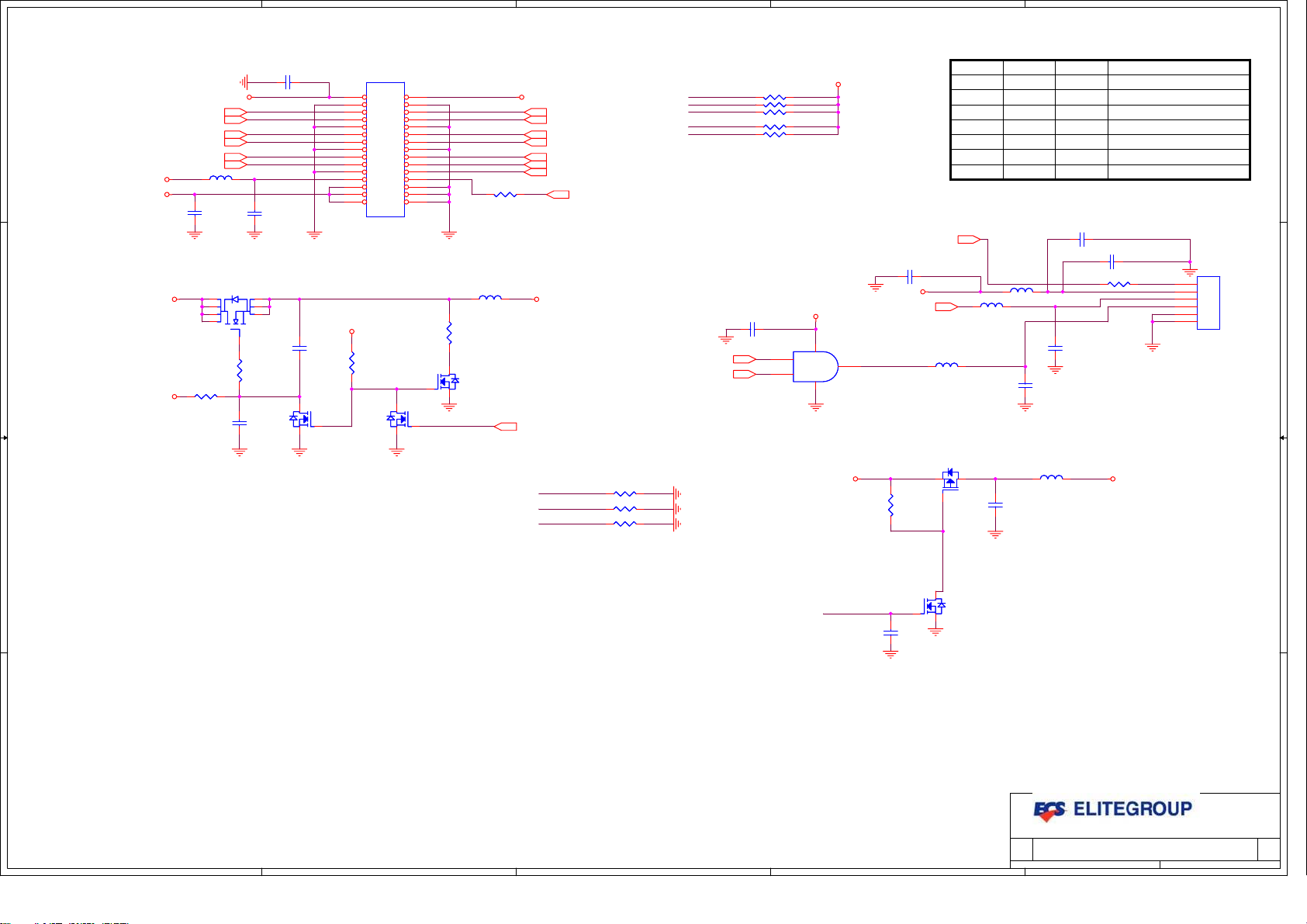

CLOCK GENERATOR

945GSE- Host(1/4)

945GSE- DDR(2/4)

945GSE- DMI & VGA(3/4)

945GSE- POWER & GND(4/4)

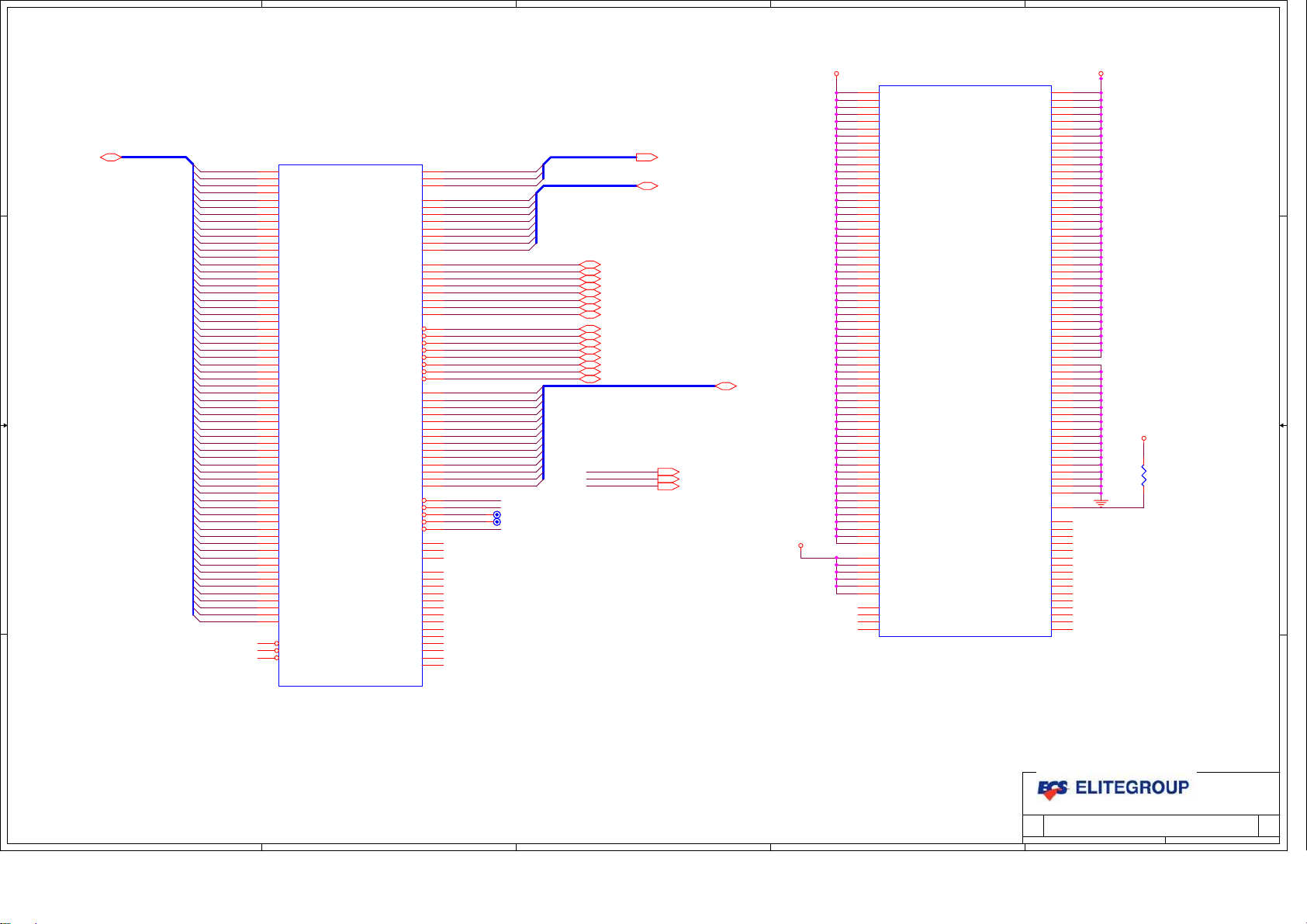

DDR2 SODIMM

LCD

SB ICH7M- HOST(1/4)

SB ICH7M- PCI & GPIO(2/4)

SB ICH7M- PCIE & USB(3/4)

SB ICH7M- POWER & GND(4/4)

MINICARD/BD1/BD2

LAN- RTL8100CL

WEBCAM/TOUCH PAD/FAN/PW

USB CONN

CARD/USB CON

CRT

ITE8512E

POWER SWITCH

DC IN/BATT IN/Charger

+V3.3A/+V5A(OZ815)

CPU_CORE(MAX8796)

J10IL1 REV.C P/N LIST

Initial REV.A

MB BD

Function BD

Release REV.B

MB BD

Function BD

RJ11 BD

Release REV.C

MB BD

Function BD

RJ11 BD

MB

Revision History

Initial REV.A03/31/08A

B 05/23/08 Release REV.B

C ??/??/08 Release REV.C

PCB P/N PCB ASSY P/N

37GJ10000-A0

35GWJ1000-A0 80GWJ1000-A0

37GJ10000-B0

35GWJ1000-B0

35G9J1000-A0 80G9J1000-A0

37GJ10000-C0

35GWJ1000-C0

35G9J1000-B0

82GJ10000-A0

82GJ10000-B0

80GWJ1000-B0

+V1.8S/+V1.05 (OZ8138)30.

+V1.5/+V0.9S/+V2.531

Change Notes32

5

4

3

2

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SCHEMATICS

SCHEMATICS

SCHEMATICS

Date: Sheet of

Date: Sheet of

Date: Sheet

COVER PAGE

COVER PAGE

COVER PAGE

1

132Monday, July 07, 2008

132Monday, July 07, 2008

132Monday, July 07, 2008

of

C

C

C

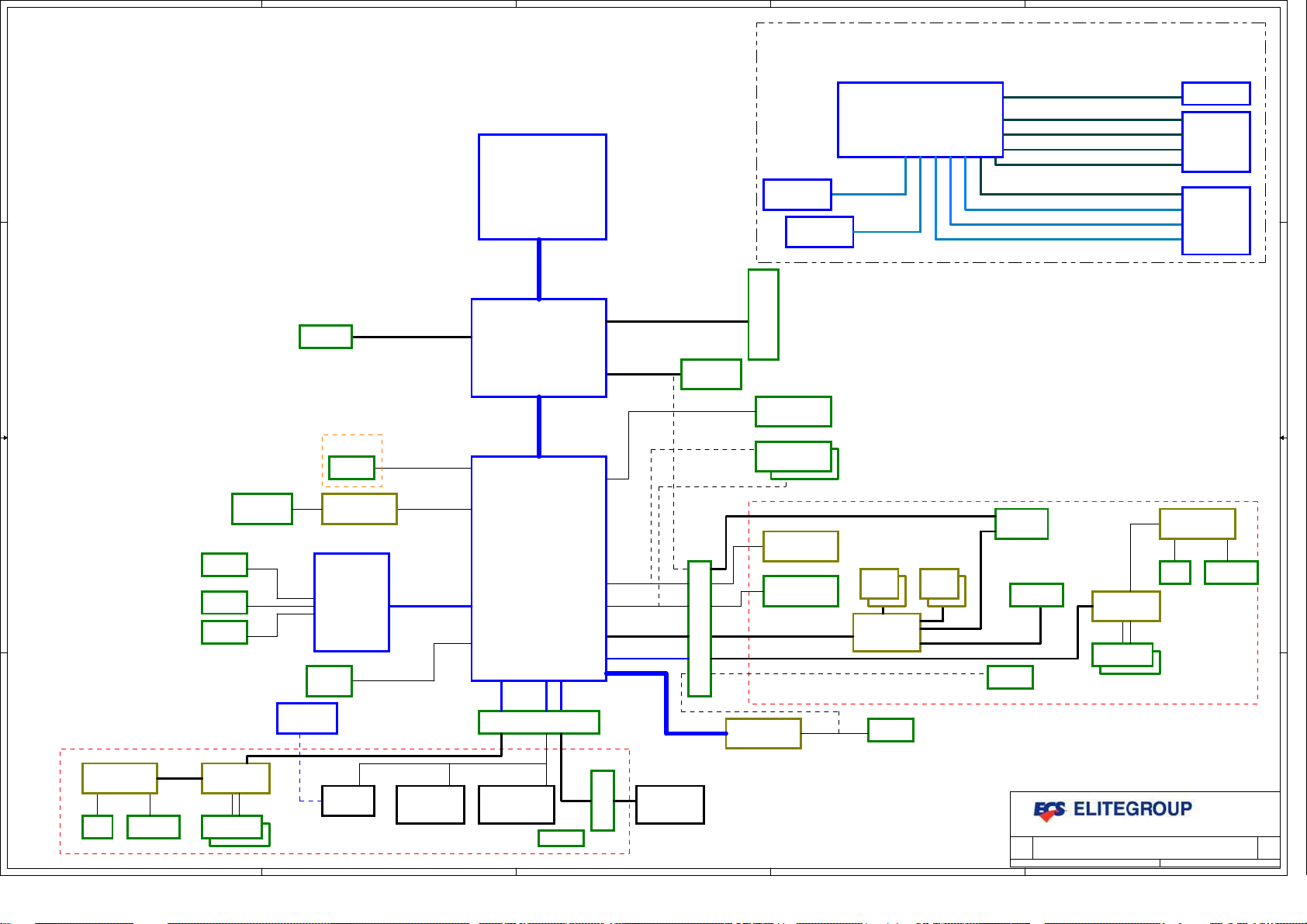

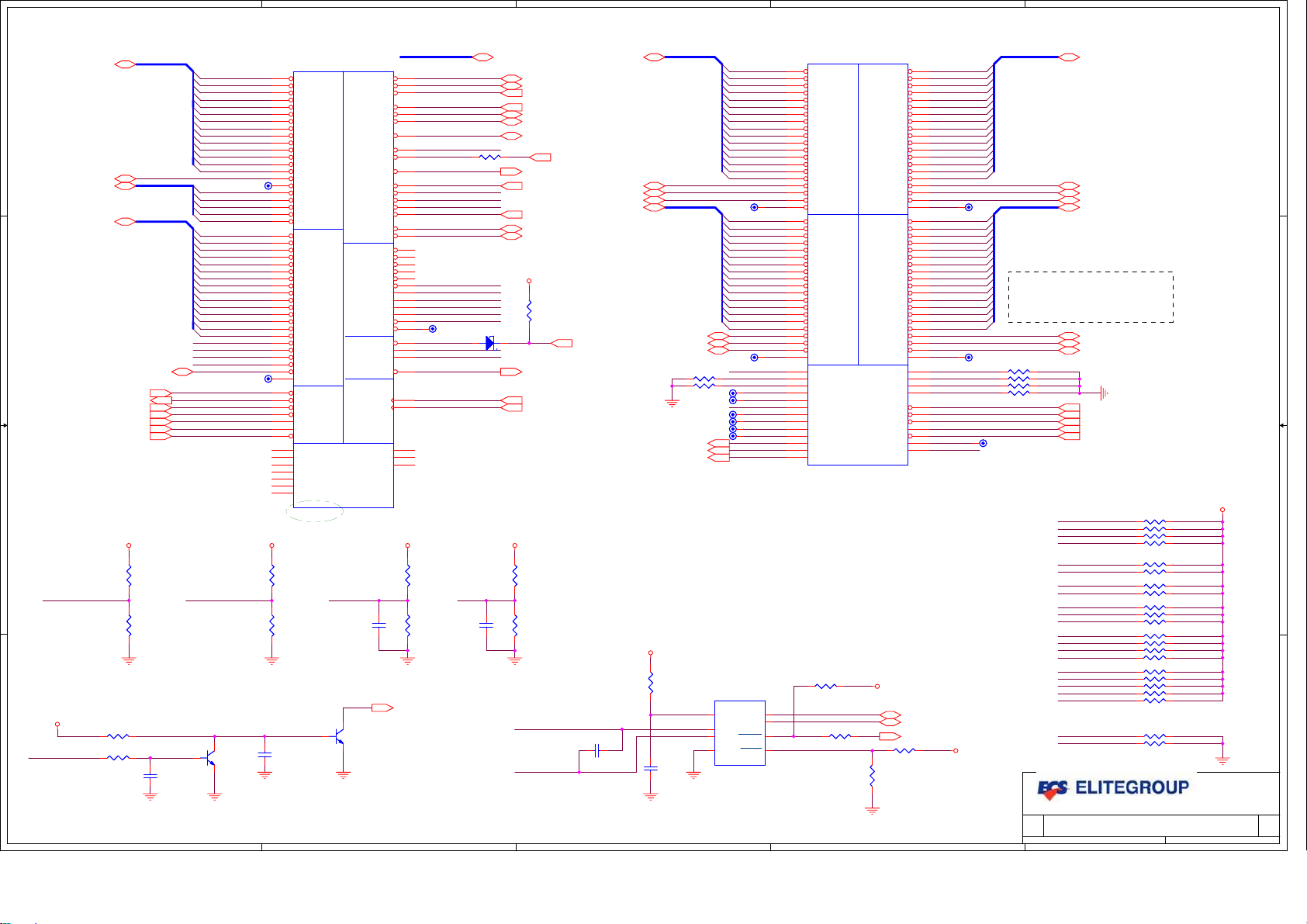

Page 2

5

4

3

2

1

Clock delivery Block

J10IL1/J30

D D

System Block Diagram

Clk Gen

ICS9LPRS365BG

CPU_HOST_CLK+/-

NB_HOST_CLK+/SRC_CLK+/MCH_3GPLL_CLK+/-

CPU

NB

DOT_CLK+/-

Diamondville

DMI_CLK+/-

PCI_CLK

REF_CLK(14.318MHz)

USB_CLK

VCN3

CRT

VCN4

LCD

VCN5

AMP

EUA6027

External

SPK

SB

AUDIO CODEC

ALC662

Head

MIC

phone

EC

PCI_CLK

PCI_CLK

Processor

LAN

FSB 533MHz

CN13

C C

LCD

CN5

Option

WLAN

CON503

B B

FAN

Touch Pad

KB

CN19

CN1

CN2

Web CAM

MDC CN

RCN508

CN18

RT5158E

IT8512

CN6

LVDS

USBX1

USBX1

LPC

USBX1

Azalia

BD to BD Conn.

945GSE

DMIx2

ICH7-M

USBX1

42pins

SATAx1

USBX1

USBX1

USBX1

PCIE 4X

Azalia

PCI

CON501

CRT

Conn.

60pins BD to BD

RT8100CL

DDR II

SODIMM

512MB

CN12

USB Port

CN9, CN10

USB Port

VCN1

USB Port

VCN2

USB Port

Daughter BD1

DDR2

ATI

M82-SE

CN8

J30II1(reserved)

DDR2

RJ45

RJ45

A A

AUDIO CODEC

ALC662

Head

MIC

5

phone

AMP

EUA6027

External

SPK

MDC

NAND

Flash

Daughter BD2

4

3G Card

EDGE Card

LED

SATA

Conn.

SATA HDD

3

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

232Monday, July 07, 2008

232Monday, July 07, 2008

232Monday, July 07, 2008

1

C

C

C

of

of

of

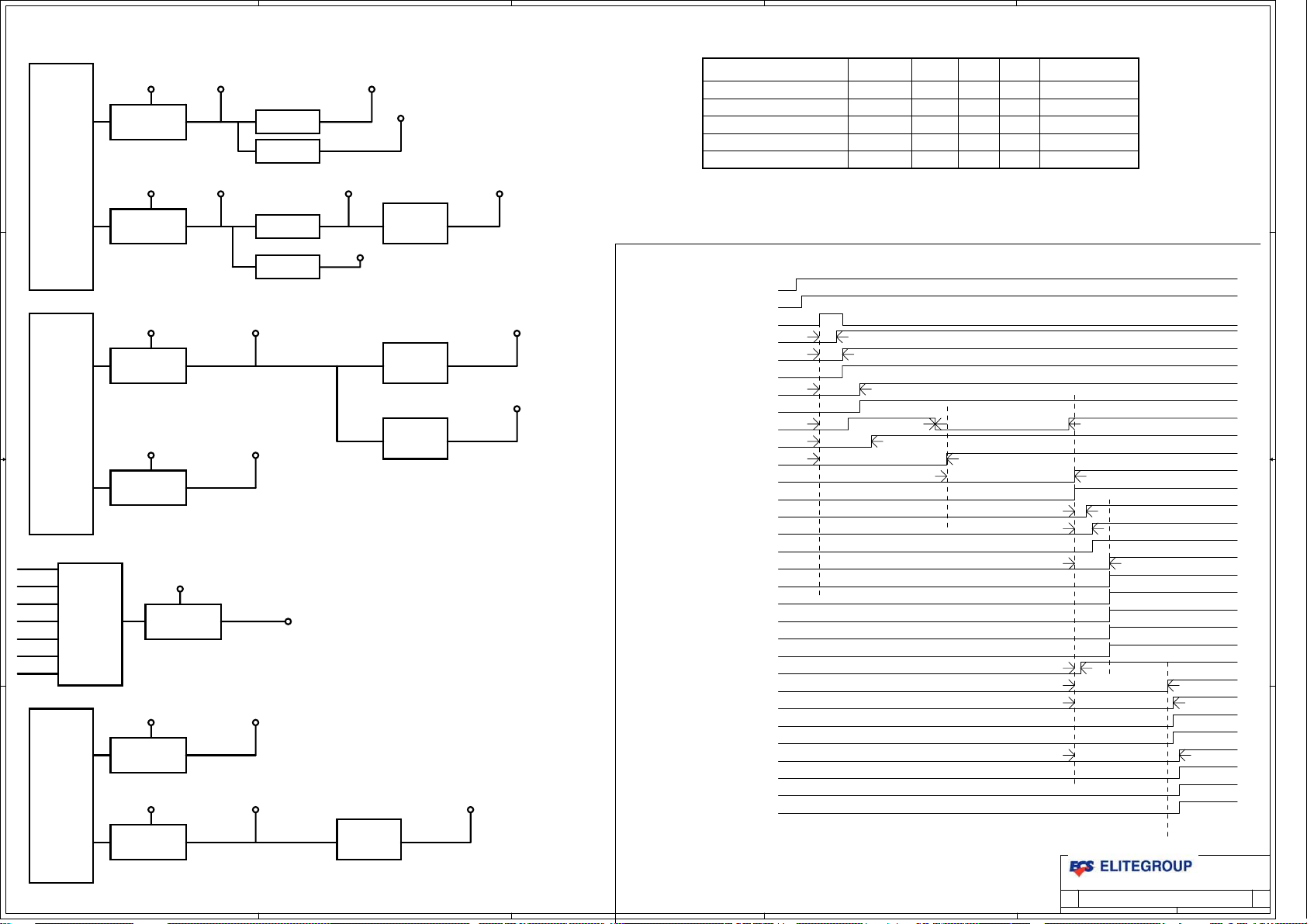

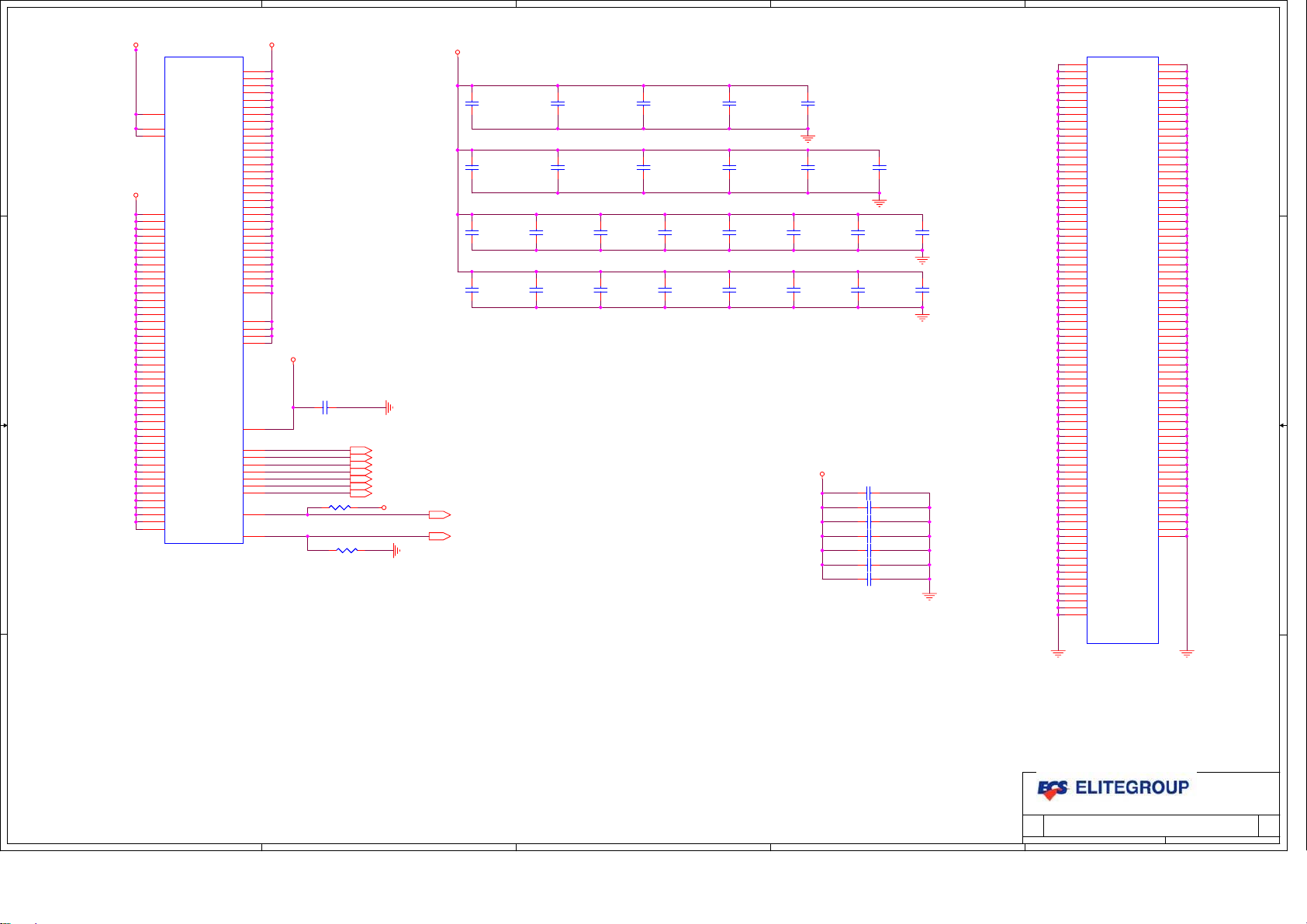

Page 3

5

4

3

2

1

POWER BLOCK DIAGRAM

VIN

D D

AO4468

AO4468

+V5A/6.5A

(EN5) (+V5S_ON)

AO4468

AO4468

OZ815

VIN

AO4468

AO4468

+V3.3A/6.5A

(EN5)

AO4468

AO4468

VIN

C C

AO4468

AO4468

OZ8138

VIN

AO4468

AO4468

+V1.8S/9A

(+V1.8VS_ON)

+V1.05/7.5A

(+V1.05_ON)

VID0

B B

VID1

VIN

VID2

VID3

VID5

MAX8770

AO4468

AO4468VID4

(VCORE_ON)

+VCC_CORE/3A

VID6

VIN

AO4468

AO4468X2

A A

VIN

AO4468

AO4468

+VGA_CORE/15A

(VGA_CORE_ON)

VRAM/9A

(VGA_VRAM_ON)

(+V5_ON)

+V3.3

(+V3.3_ON)

+V3.3S

(+V3.3S_ON)

LDO

APL5912

+V5S

+V5

+V2.5/150mA

LDO

APL5312

+V0.9S/600mA

LDO

FIFT6137B

+V1.5/4A

LDO

APL5912

PCIE_1.2/3AOZ8138

J10IL1 M/B Power Rail State :

+*V_LDO +*VA +*VS +*V CLK

AC/DC S0/Moff (Full On)

AC/DC S3/Moff (STR)

AC/DC S4/Moff (STD)

AC S5/Moff (Soft Off)

DC S5/Moff (Soft Off)

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

Poewr On Sequence

Adaptor

+3.3VA,+5VA

PWR_SW

+5VS_ON

+5VS

+3.3VS

+DDR_ON

+1.8VS

SB-PWRBTN#

PM_RSMRST#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

+5V_ON

+5V

+3.3V

+1.5V_ON

+1.5V

+1.5_PWRGD

+1.05V

+1.05_PWRGD

MPWROK

ALL_SYS_PWRGD

+CPU_CORE_ON

+CPUCORE

VCORE_CLK_EN#

CLK_PWRGD

DELAY_VR_PWRGD

PM_ICH_PWROK

H_PWRGD

PCIRST#/PLTRST#

58ms

110ms

285ms

30ms

36ms

88ms

1S93

ONONON ON

Only MCH BCLK

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

1s95210ms

60ms

62ms

115ms

4ms

455ms

456ms

461ms

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

POWER DIAGRAM & SEQUENCE

POWER DIAGRAM & SEQUENCE

POWER DIAGRAM & SEQUENCE

1

332Monday, July 07, 2008

332Monday, July 07, 2008

332Monday, July 07, 2008

C

C

C

of

of

of

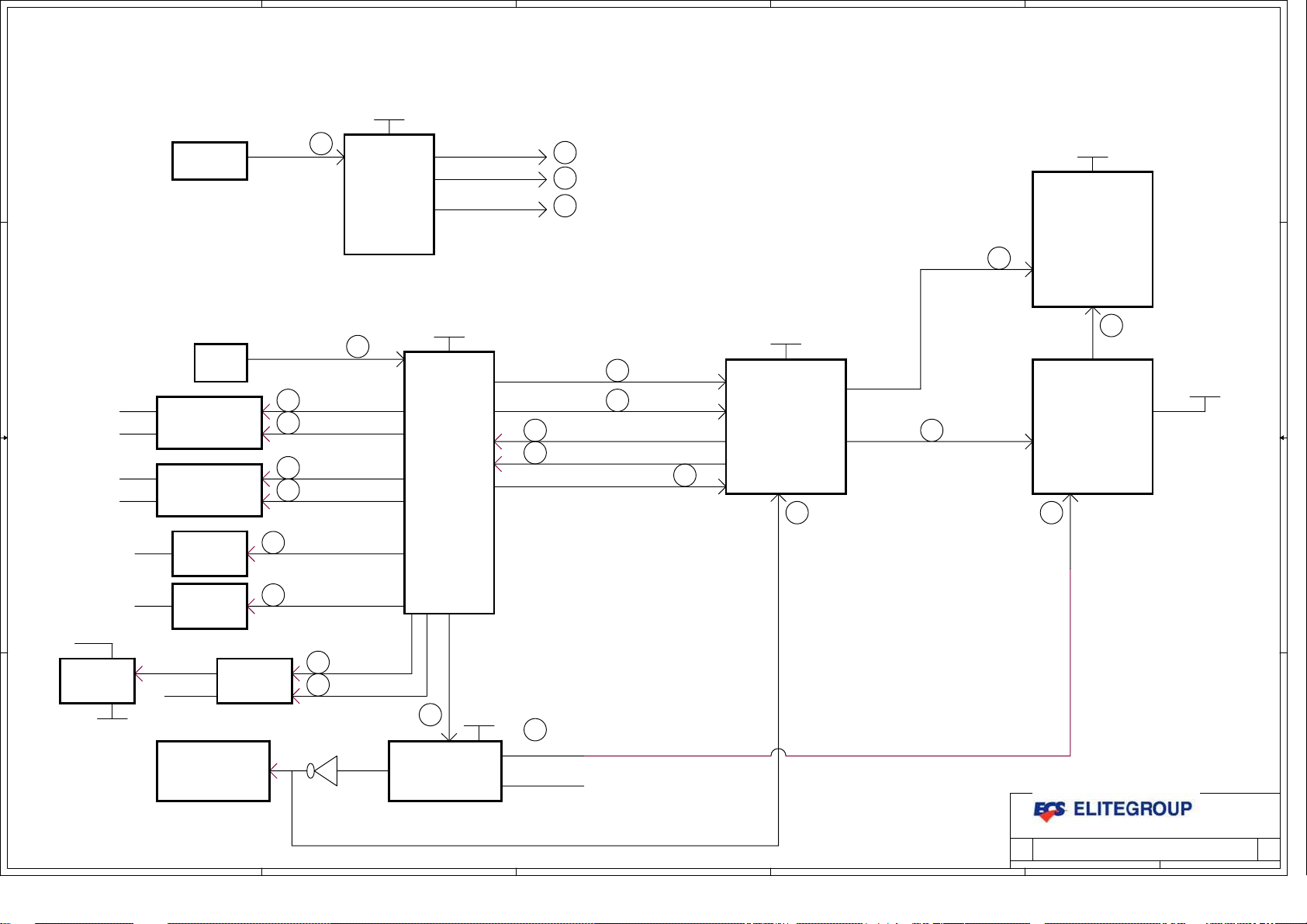

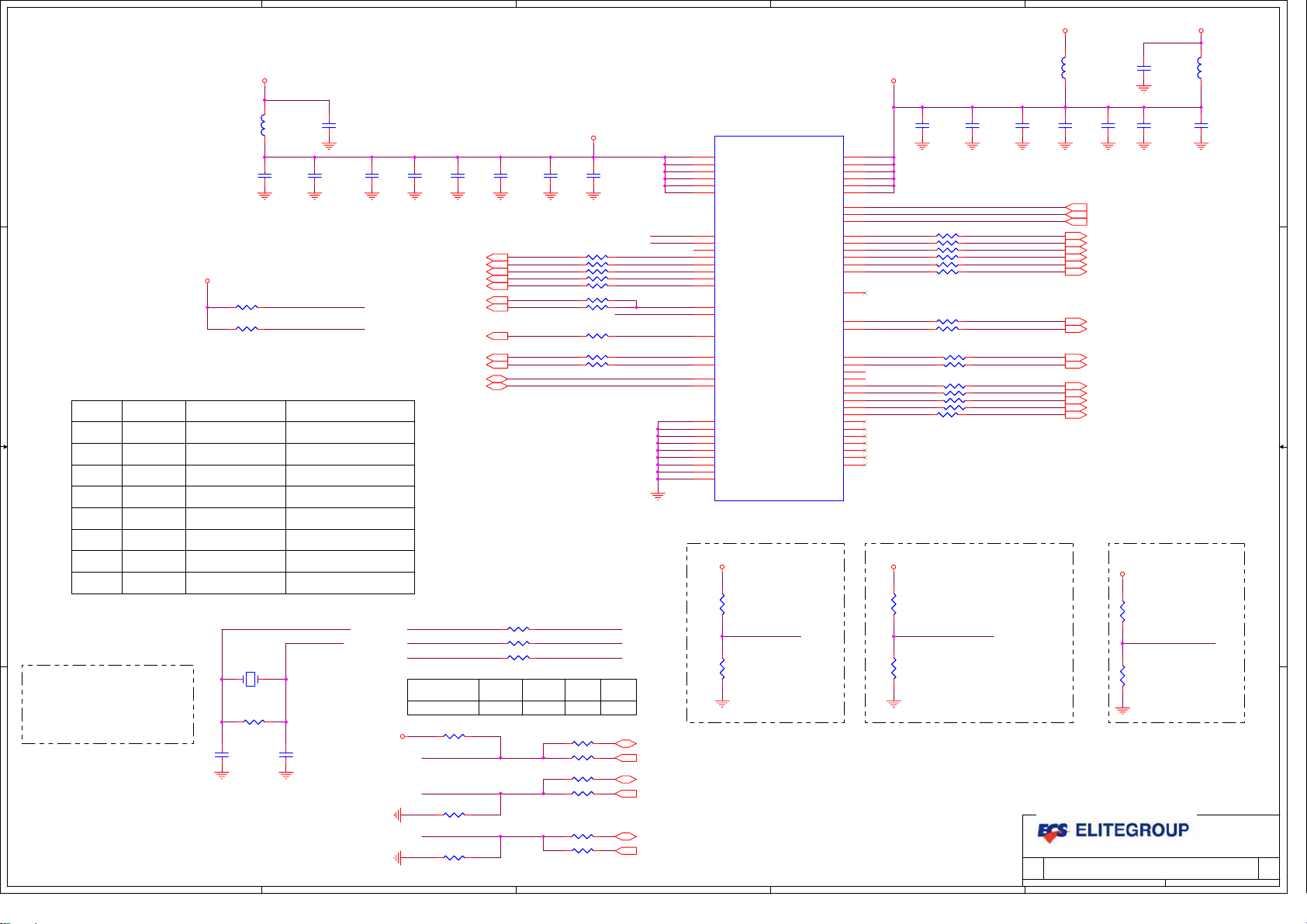

Page 4

5

4

3

2

1

J10IL1 Power on Sequence Diagram

D D

VIN

1

Adpater

VIN

OZ815

3.3v,5v, 12v

Always on

Power Circuit

+V5A

+V12ALWAYS

+V3.3A

+V1.5

+V1.05

2

+VCC_CORE

2

2

CPU

Diamondville

+V5S

H_PWRGD

+V3.3S

+V5

+V3.3

C C

Power

PWR_SW

3

Switch

+V5S

+V3.3S

+V5

+V3.3

VCC MOSFET

page 26

VCC MOSFET

page 26

4

5

10

11

+V5S_ON

+V3.3S_ON

+V5_ON

+V3.3_ON

+V3.3A

IT8512E

Embedded

controller

PM_RSMRST#

PM_PWRBTN#

9

PM_SLP_S4#

9

PM_SLP_S3#

PM_ICH_PWROK

8

7

18

+V1.5

+V1.05

ICH7-M

South Bridge

PLT_RST#

19

16

B B

+V2.5

APL5312

12

+V2.5_ON

page 31

19

17

PM_CPU_PWRGD

20

H_CPURST#

945GSE

North Bridge

+V1.8S

+V0.9S

+V3.3

+V2.5

+V1.5

+V1.05

+V1.5

APL5912

page 31

13

+V1.5_ON

VR_PWRGD_CLKEN

+V0.9S

6

FP6137

page 31

+V1.8S

+V1.05

OZ8138

page 30

+V3.3S

A A

CLK GEN

ICS9LPR365BG

page 8

5

+V1.8S_ON

14

+V1.05_ON

VR_PWRGD_CLKEN

4

+VCORE_ON

15

CPU VCORE

MAX8796

page 29

VIN

17

PM_CPU_PWRGD

+VCC_CORE

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

SEQUENCE DIAGRAM

SEQUENCE DIAGRAM

SEQUENCE DIAGRAM

432Monday, July 07, 2008

432Monday, July 07, 2008

432Monday, July 07, 2008

1

C

C

C

of

of

of

Page 5

5

4

3

2

1

ICH-7M GPIO

GPIO0

GPIO1

D D

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

C C

GPIO22

GPIO23

GPIO24

GPIO25

GPIO26

GPIO27

GPIO28

GPIO29

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

GPIO38

GPIO39

GPIO40

B B

GPIO41

GPIO42

GPIO43

GPIO44

GPIO45

GPIO46

GPIO47 N.C

GPIO48

GPIO49

GPIO50

GPIO51

GPIO52

GPIO53

GPIO54

GPIO55

GPIO56

GPIO57

GPIO59

A A

PM_BMBUSY#

PCI_REQ#5

INT_PIRQE#

INT_PIRQF#

INT_PIRQG#

INT_PIRQH#

N.C

EC_SCI#

EC_EXTSMI#

PNLSW2

PNLSW1

SMB_ALERT#

PNLSW0

SMC_WAKE_SCI#_R

N.C

N.C

PM_DPRSLPVR_R

PCI_GNT#5

PM_STPPCI#

SATA0_R1

PM_STPCPU#

SATA0_R0

ICH_GPIO22

N.C

N.C

N.C

N.C

PM_S3HOT#_R

N.C

USB_OC#5

USB_OC#6

USB_OC#7

PM_CLKRUN#

HDA_DOCK_EN#

N.C

N.C

SATA0_R2

SATA0_R3

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.CGPIO58

N.C

N.CGPIO60

5

ITE8512E GPIO

Pin Definition list

BTL_BEEP

GPA0

GPA1

BRIGHTNESS_R

PWR_LED

GPA2

BUTTON_LED

GPA3

CHG_R_LED

GPA4

CHG_G_LED

GPA5

X

GPA6

GPA7

X

GPB0

VGA_CORE_ON

GPB1

VGA_VRAM_ON

VGA_VDDR3_ON

GPB2

SMB_CLK_GEN

GPB3

GPB4

SMB_DATA_GEN

X

GPB5

X

GPB6

GPB7

PWR_KEEP

GPC0

X

GPC1

SMB_CLK_BAT

SMB_DATA_BAT

GPC2

GPC3

X

X

GPC4

GPC5

+V2.5_ON

X

GPC6

GPC7

+V5S_ON

GPD0

AC_IN

WEBCAM_EN

GPD1

PLT_RST#_EC

GPD2

GPD3

EC_EXTSCI#_R

GPD4

EC_EXTSMI#_R

PM_THROTTING#

GPD5

GPD6

FAN_SPEED#

GPD7

PM_PWRBTN#

GPE0

BKL_EC

GPE1

MUTE_AMP#

GPE2

PM_RSMRST#

GPE3

PM_SYSRST#

PWR_SW

GPE5

PM_SLP_S3#

GPE6

PM_SLP_S4#

GPE7

RF_LED

GPF0

GPF1

RF_OFF#

X

GPF2

GPF3

X

GPF4

PS2_CLK_TP

GPF5

PS2_DATA_TP

SMB_CLK_VGA

GPF6

SMB_DATA_VGA

GPF7

VCC_MCH_VRPWRGD

GPH0

VCORE_ON

GPH1

GPH2

+V5_ON

GPH3

+V3.3_ON

+V3.3S_ON

GPH4

X

GPH5

GPH6

+V1.05_ON

GPG1

ADC0/GPI0

ADC1/GPI1

ADC2/GPI2

ADC3/GPI3

ADC4/GPI4

ADC5/GPI5

ADC6/GPI6

ADC7/GPI7

+V1.8S_ON

BATT_TEMP

ADAPTOR_I

BAT_I

BAT_V

THERM#_VGA

EC_PROCHOT

X

PM_SLP_S5#

ITE8512E GPIO

Pin Definition list

DAC0/GPJ0

EC_BL_PWM

DAC0/GPJ1

CHG_I

DAC0/GPJ2

FAN_CTRL0

DAC0/GPJ3

SENBAT_V

DAC0/GPJ4

CHG_V

DAC0/GPJ5

CHG_ON

ITE8512E

KB Matrlk interface

KSI0/STB#

KB_SIN0

KSI1/AFD#

KB_SIN1

KSI0/STB#

KB_SIN2

KSI3SLIN#

KB_SIN3

KSI4

KB_SIN4

KSI5

KB_SIN5

KSI6

KB_SIN6

KSI7

KB_SIN7

KSO0/PD0

KB_SOUT0

KSO1/PD1

KB_SOUT1

KSO2/PD2

KB_SOUT2

KSO2/PD3

KB_SOUT3

KSO2/PD4

KB_SOUT4

KSO2/PD5

KB_SOUT5

KSO2/PD6

KB_SOUT6

KSO2/PD7

KB_SOUT7

KSO8/ACK#

KB_SOUT8

KSO9/BUSY

KB_SOUT9

KSO10/PE

KB_SOUT10

KSO11/ERR#

KB_SOUT11

KSO12/SLCT

KB_SOUT12

KSO13

KB_SOUT13

KSO14

KB_SOUT14

KSO15

KB_SOUT15

ITE8512E SPI

Flash ROM interface

FLFRAME#/GPG2

FLAD0/SCE#

FLAD1/S1

FLAD2/S2

FLAD3/GPG6

FLCLK/SCK

FLRST#/WU17

/GPG0/TM

System & LPC Bus

LAD0

LAD1

LAD2

LAD3

SERIRQ

LFRAME#

LPCCLK

WRST#

CK32K

CK32KE

VSTBY0

VSTBY1

VSTBY2

VSTBY3

VSTBY4

VSTBY5

VBAT

AVCC

VCC

4

FLFRAME#

SPI_CE#GPE4

SPI_DIN

SPI_DOUT

LID#

SPI_CLK

BKL_EC

ITE8512E

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

INT_SERIRQ

LPC_FRAME#

CLK_PCI_LPC

LRST#

ITE8512E

Clock

EC32KI

EC32KO

ITE8512E

Power

+3.3VA

+3.3VA

+3.3VA

+3.3VA

+3.3VA

+3.3VA

+3.3VA

+3.3VA

+3.3V

945GSE

AVSS

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

CPU Socket P

Diamondville

FSB 533 MHz

ITE8512E

GND

EC-AVSS-75

GND

GND

GND

GND

GND

GND

GND

945GMS

GPIO

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

N.C

N.C

MCH_CFG_5

N.C

MCH_CFG_7

N.C

MCH_CFG_9

MCH_CFG_10

N.C

MCH_CFG_12

MCH_CFG_13

N.C

N.C

MCH_CFG_16

N.C

N.C

MCH_CFG_19

MCH_CFG_20

3

945GSE

GMCH GFX Freq/Core

Volt

533MHZ/+V1.05

Diamondville CPU

1.6

CPU CORE(V)

VID fixed

at 1.1V

Freg.(GHz)

Memory

DDR2 400/533 MHz

ICC(A)

TDP(W)

2.5

2.2

945GSE

VCC

+V1.05

+V1.5

+V3.3

ICC(mA)

3906

3720

3051

2034

528

160

1752+V1.8S 3154

0.02

0.02+V0.9S

355

142+V2.5

ICH7-M

+5V

+5VS

+V3.3 366 1207

+V3.3S

+V1.5 2444

+V1.05 1001 1050

6

10

55

1629

ICC(mA)

VCC

mW

30

50

182

2

mW

TDP

3.5~5.5W

TjMAX( )

90

TEMP( )

105

TEMP( )

70

ITE8512E

990

mW

TEMP( )

70

VCC

+V3.3A

ICC(mA)

300

ICS 9LPR310

VCC

+V3.3

ICC(mA)

450

mW

1485

TEMP( )

70

RTL8100CL

+V3.3S

+V2.5 40 100

80

ICC(mA)

VCC

264

mW

TEMP( )

70

RTS5158E

VCC

+V3.3

ICC(mA)

250

825

mW

TEMP( )

70

ALC662

TEMP( )

VCC ICC(mA)

+V3.3 35 116

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

55+5V

Project : J10IL1

Project : J10IL1

Project : J10IL1

mW

275

70

GPIO & POWER CONSUMPTION

GPIO & POWER CONSUMPTION

GPIO & POWER CONSUMPTION

1

of

of

of

532Monday, July 07, 2008

532Monday, July 07, 2008

532Monday, July 07, 2008

C

C

C

Page 6

5

4

3

2

1

H_D#[63:0]

H_D#[63:0]

TP504TP504

Layout note:

COMP0 ,2 connect with Zo = 27.4R,make

trace length shorter than 0.5"

COMP1 ,3 connect with Zo = 55 Ohm,make

trace length shorter than 0.5"

TP502TP502

R47 27.4-1-04R47 27.4-1-04

R53 54.9-1-04R53 54.9-1-04

R30 27.4-1-04R30 27.4-1-04

R26 54.9-1-04R26 54.9-1-04

TP1TP1

TDO

XDP_BPM#5

TMS

TDI

H_STPCLK#

H_IERR#

H_PROCHOT#

H_PWRGD

H_INIT#

H_A20M#

H_IGNNE#

H_A#32

H_A#33

H_A#34

H_A#35

H_SMI#

H_DPRSTP#

H_DPSLP#

H_INTR

H_NMI

TRST#

TCK

<OrgAddr3>

<OrgAddr3>

<OrgAddr3>

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SCHEMATICS

SCHEMATICS

SCHEMATICS

Date: Sheet

Date: Sheet

Date: Sheet

H_D#[63:0] 9H_D#[63:0]9

H_DSTBN#2 9

H_DSTBP#2 9H_DSTBP#09

H_DINV#2 9

H_DSTBN#3 9

H_DSTBP#3 9

H_DINV#3 9

H_DPRSTP# 15,29

H_DPSLP# 15

H_DPWR# 9

H_PWRGD 15

H_CPUSLP# 9,15

R535 56-04R535 56-04

R533 56-04R533 56-04

R537 56-04R537 56-04

R543 56-04R543 56-04

R552 @56-04R552 @56-04

R523 56-04R523 56-04

R528 68-04R528 68-04

R558 1K-1-04R558 1K-1-04

R563 1K-04R563 1K-04

R554 1K-04R554 1K-04

R532 1K-04R532 1K-04

R522 1K-1-04R522 1K-1-04

R14 1K-1-04R14 1K-1-04

R515 1K-1-04R515 1K-1-04

R15 1K-1-04R15 1K-1-04

R555 @51-04R555 @51-04

R548 1K-1-04R548 1K-1-04

R547 1K-1-04R547 1K-1-04

R559 @51-04R559 @51-04

R544 @51-04R544 @51-04

R534 56-04R534 56-04

R541 56-04R541 56-04

CPU Diamondville-1/2

CPU Diamondville-1/2

CPU Diamondville-1/2

+V1.05

C

C

C

of

of

of

632Monday, July 07, 2008

632Monday, July 07, 2008

1

632Monday, July 07, 2008

+V3.3

3

H_D#[63:0]

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#[63:0]

H_DSTBN#19

H_DSTBP#19

H_DINV#19

R545 @1K-04R545 @1K-04

R550 @1K-04R550 @1K-04

CPU_BSEL08

CPU_BSEL18

CPU_BSEL28

R45

R45

200-1-04

200-1-04

HTHRM_VDD

C73

C73

.1U-10V-04R-K

.1U-10V-04R-K

TP511TP511

TP508TP508

TP505TP505

TP507TP507

TP506TP506

TP509TP509

U6

1

VDD

2

D+

3

DGND5ALERT

ADM1032U6ADM1032

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

TP514TP514

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

TP510TP510

THERM

H_GTLREF

ACLKPH

DCLKPH

H_BINIT#

H_EDM

EXTGBREF

FORCEPR#

H_HFPLL

H_MCERR#

H_RSP

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

SCLK

SDATA

H_DP#0

H_DP#1

8

7

4

6

U4B

U4B

Y11

D[0]#

W10

D[1]#

Y12

D[2]#

AA14

D[3]#

AA11

D[4]#

W12

D[5]#

AA16

D[6]#

Y10

D[7]#

Y9

D[8]#

Y13

D[9]#

W15

D[10]#

AA13

D[11]#

Y16

D[12]#

W13

D[13]#

AA9

D[14]#

W9

D[15]#

Y14

DSTBN[0]#

Y15

DSTBP[0]#

W16

DINV[0]#

V9

DP#0

AA5

D[16]#

Y8

D[17]#

W3

D[18]#

U1

D[19]#

W7

D[20]#

W6

D[21]#

Y7

D[22]#

AA6

D[23]#

Y3

D[24]#

W2

D[25]#

V3

D[26]#

U2

D[27]#

T3

D[28]#

AA8

D[29]#

V2

D[30]#

W4

D[31]#

Y4

DSTBN[1]#

Y5

DSTBP[1]#

Y6

DINV[1]#

R4

DP#1

A7

GTLREF

U5

ACLKPH

V5

DCLKPH

T17

BINIT#

R6

EDM

M6

EXTBGREF

N15

FORCEPR#

N6

HFPLL

P17

MCERR#

T6

RSP#

J6

BSEL[0]

H5

BSEL[1]

G5

BSEL[2]

ATOM-SLB73

ATOM-SLB73

R44 @10K-04R44 @10K-04

SMB_CLK_CPU

SMB_DATA_CPU

R41 @0-04R41 @0-04

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

MISC

MISC

THRM_ALERT#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

DATA GRP 2

DATA GRP 2

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DP#2

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

DATA GRP 3

DATA GRP 3

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

DP#3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

CORE_DET

CMREF[1]

+V3.3

SMB_CLK_CPU 25

SMB_DATA_CPU 25

PM_THRM_CPU# 16

R48 @10K-04R48 @10K-04

R49

R49

@10K-04

@10K-04

2

R3

R2

P1

N1

M2

P2

J3

N3

G3

H2

N2

L2

M3

J2

H1

J1

K2

K3

L1

M4

C2

G2

F1

D3

B4

E1

A5

C3

A6

F2

C6

B6

B3

C4

C7

D2

E2

F3

C5

D4

T1

T2

F20

F21

R18

R17

U4

V17

N18

A13

B7

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DP#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

H_DP#3

COMP0

COMP1

COMP2

COMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGD

H_CPUSLP#

CORE_DET

CPU_CMREF

+V3.3

H_A#[31:3]9

D D

H_ADSTB#09

H_REQ#[4:0]9

H_A#[31:3]9

C C

B B

H_DPWR# H_GTLREF

+VCC_CORE

A A

PM_THRMTRIP# Z0405

H_A#[31:3]

H_ADSTB#0

H_REQ#[4:0]

H_A#[31:3]

H_ADSTB#19

H_A20M#15

H_FERR#15

H_IGNNE#15

H_STPCLK#15

H_INTR15

H_NMI15

H_SMI#15

R567

R567

1K-1-04

1K-1-04

R565

R565

@1K-1-04

@1K-1-04

R542 10K-1-04R542 10K-1-04

R531 1K-1-04R531 1K-1-04

5

U4A

P21

H20

N20

R20

N19

G20

M19

H21

M20

K19

K20

D17

N21

G19

P20

R19

C19

E21

A16

D19

C14

C18

C20

E20

D20

B18

C15

B16

B17

C16

A17

B14

B15

A14

B19

M18

U18

R16

R15

U17

M15

J19

L20

J20

L21

J21

F19

T16

J4

T15

D6

G6

H6

K4

K5

L16

U4A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

AP0

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

AP1

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

NC1

NC2

NC3

NC4

NC5

NC6

NC7

ATOM-SLB73

ATOM-SLB73

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

TP501TP501

TP503TP503

Modify 2.

R539

Layout note: Zo=55 ohm,

0.5" max for EXTGBTEF

EXTGBREF CPU_CMREF

Z0404

Q501

Q501

B

TR-2N3904

TR-2N3904

C542

C542

.1U-10V-04R-K

.1U-10V-04R-K

E C

R539

1K-1-04

1K-1-04

R540

R540

2K-1-04

2K-1-04

C549

C549

1U-6.3-04R-K

1U-6.3-04R-K

ADS#

BNR#

BPRI#

ADDR

GROUP

0

ADDR

GROUP

0

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

ADDR GROUP 1

ADDR GROUP 1

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

BR1#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

PROCHOT#

THRMDA

THRMDC

THERM

THERM

THERMTRIP#

BCLK[0]

BCLK[1]

H CLK

H CLK

RSVD3

RSVD2

NC

NC

RSVD1

Layout note: Zo=55 ohm,

0.5" max for CPU_CMREF.

C526

C526

.1U-10V-04R-K

.1U-10V-04R-K

Q503

Q503

B

TR-2N3904

TR-2N3904

E C

4

H_ADS#

V19

H_BNR#

Y19

H_BPRI#

U21

H_DEFER#

T21

H_DRDY#

T19

H_DBSY#

Y18

H_BREQ#0

T20

H_IERR#

F16

H_INIT#R

V16

H_LOCK#

W20

H_CPURST#

D15

H_RS#0

W18

H_RS#1

Y17

H_RS#2

U20

H_TRDY#

W19

H_HIT#

AA17

H_HITM#

V20

K17

J18

H15

J15

K18

XDP_BPM#5

J16

TCK

M17

TDI

N16

TDO

M16

TMS

L17

TRST#

K16

V15

H_PROCHOT#

G17

H_THERMDA

E4

H_THERMDC

E5

PM_THRMTRIP#

H17

CLK_CPU_BCLK

V11

CLK_CPU_BCLK#

V12

C21

C1

A3

.

.

+V1.05+V1.05 +V1.05+V1.05

R516

R516

1K-1-04

1K-1-04

R517

R517

2K-1-04

2K-1-04

AUX_OFF# 26,28

H_RS#[2:0]

TP513TP513

.1U-10V-04R-K

.1U-10V-04R-K

H_RS#[2:0] 9

R562 0-04R562 0-04

D501

D501

A C

C37

C37

H_ADS# 9

H_BNR# 9

H_BPRI# 9

H_DEFER# 9

H_DRDY# 9

H_DBSY# 9

H_BREQ#0 9

H_LOCK# 9

H_CPURST# 9

H_TRDY# 9

H_HIT# 9

H_HITM# 9

+V3.3

R527

R527

10K-04

10K-04

SCH-BAT54-PH

SCH-BAT54-PH

PM_THRMTRIP# 11,15

CLK_CPU_BCLK 8

CLK_CPU_BCLK# 8

R16

R16

1K-1-04

1K-1-04

R17

R17

2K-1-04

2K-1-04

H_THERMDA

H_THERMDC

H_INIT# 15

EC_PROCHOT# 25

H_DSTBN#09

H_DINV#09

H_D#[63:0]9 H_D#[63:0] 9

C5542200P-50-04X-K C5542200P-50-04X-K

Page 7

5

4

3

2

1

+V1.05+V1.05

U4C

U4C

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

+VCC_CORE

V10

A10

A11

A12

B10

B11

B12

C10

C11

C12

D10

D11

D12

E10

E11

E12

F10

F11

F12

G10

G11

G12

H10

H11

H12

K10

K11

K12

L10

L11

L12

M10

M11

M12

N10

N11

N12

P10

P11

P12

R10

R11

R12

A9

B9

J10

J11

J12

VCCF

VCCQ1

VCCQ2

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

VCCP28

VCCP29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

VCCP35

VCCP36

VCCP37

VCCP38

VCCP39

VCCP40

VCCP41

VCCP42

VCCP43

VCCP44

VCCP45

ATOM-SLB73

ATOM-SLB73

D D

3000mA

C C

B B

C9

D9

E9

F8

F9

G8

G14

H8

H14

J8

J14

K8

K14

L8

L14

M8

M14

N8

N14

P8

P14

R8

R14

T8

T14

U8

U9

U10

U11

U12

U13

U14

F14

F13

E14

E13

130mA

D7

F15

D16

E18

G15

G16

E17

G18

C13

D13

2500mA

+V1.5

C533 .1U-10V-04R-KC533 .1U-10V-04R-K

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

VSSSENSE

R525 100-1-04R525 100-1-04

R524 100-1-04R524 100-1-04

H_VID0 29

H_VID1 29

H_VID2 29

H_VID3 29

H_VID4 29

H_VID5 29

H_VID6 29

+VCC_CORE

+VCC_CORE

VCCSENSE 29

VSSSENSE 29

C519

C519

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C524

C524

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C38

C38

1U-6.3-04R-K

1U-6.3-04R-K

C30

C30

1U-6.3-04R-K

1U-6.3-04R-K

C522

C522

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C528

C528

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C547

C547

1U-6.3-04R-K

1U-6.3-04R-K

C544

C544

1U-6.3-04R-K

1U-6.3-04R-K

C550

C550

1U-6.3-04R-K

1U-6.3-04R-K

C29

C29

1U-6.3-04R-K

1U-6.3-04R-K

C517

C517

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C521

C521

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C535

C535

1U-6.3-04R-K

1U-6.3-04R-K

C546

C546

1U-6.3-04R-K

1U-6.3-04R-K

C520

C520

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C518

C518

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C539

C539

1U-6.3-04R-K

1U-6.3-04R-K

C527

C527

1U-6.3-04R-K

1U-6.3-04R-K

C516

C516

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C514

C514

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C543

C543

1U-6.3-04R-K

1U-6.3-04R-K

C551

C551

1U-6.3-04R-K

1U-6.3-04R-K

+V1.05

C525

C525

4.7U-6.3-06R-K

4.7U-6.3-06R-K

C36

C36

1U-6.3-04R-K

1U-6.3-04R-K

C540

C540

1U-6.3-04R-K

1U-6.3-04R-K

C538 .1U-10V-04R-KC538 .1U-10V-04R-K

C576 1U-6.3-04R-KC576 1U-6.3-04R-K

C563 1U-6.3-04R-KC563 1U-6.3-04R-K

C548 1U-6.3-04R-KC548 1U-6.3-04R-K

C552 1U-6.3-04R-KC552 1U-6.3-04R-K

C570 4.7U-6.3-06R-KC570 4.7U-6.3-06R-K

C575 4.7U-6.3-06R-KC575 4.7U-6.3-06R-K

C534

C534

1U-6.3-04R-K

1U-6.3-04R-K

C559

C559

1U-6.3-04R-K

1U-6.3-04R-K

A15

A18

A19

A20

B13

B20

B21

C17

D14

D18

D21

E15

E16

E19

G13

G21

H13

H16

H18

H19

K13

K15

K21

M13

M21

U4D

U4D

A2

VSS1

A4

VSS2

A8

VSS4

VSS5

VSS6

VSS7

VSS8

B1

VSS9

B2

VSS10

B5

VSS11

B8

VSS12

VSS13

VSS14

VSS15

C8

VSS16

VSS17

D1

VSS18

D5

VSS19

D8

VSS20

VSS21

VSS22

VSS23

E3

VSS24

E6

VSS25

E7

VSS26

E8

VSS27

VSS28

VSS29

VSS30

F4

VSS31

F5

VSS32

F6

VSS33

F7

VSS34

F17

VSS35

F18

VSS36

G1

VSS37

G4

VSS38

G7

VSS39

G9

VSS41

VSS42

VSS45

H3

VSS46

H4

VSS48

H7

VSS49

H9

VSS51

VSS52

VSS53

VSS54

VSS55

J5

VSS56

J7

VSS57

J9

VSS58

J13

VSS59

J17

VSS60

K1

VSS61

K6

VSS62

K7

VSS63

K9

VSS64

VSS65

VSS66

VSS67

L3

VSS68

L4

VSS69

L5

VSS70

L6

VSS71

L7

VSS72

L9

VSS73

L13

VSS74

L15

VSS75

L18

VSS76

L19

VSS77

M1

VSS78

M5

VSS79

M7

VSS80

M9

VSS81

VSS82

VSS83

N4

VSS84

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

N5

N7

N9

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

AA15

AA18

AA19

AA20

ATOM-SLB73

ATOM-SLB73

A A

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SCHEMATICS

SCHEMATICS

SCHEMATICS

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

CPU Diamondville-2/2

CPU Diamondville-2/2

CPU Diamondville-2/2

1

732Monday, July 07, 2008

732Monday, July 07, 2008

732Monday, July 07, 2008

C

C

C

of

of

of

Page 8

5

+V3.3

4

3

2

CLK_VDD_IO

L516

L516

@0-06

@0-06

1

C649

C649

.1U-10V-04R-K

.1U-10V-04R-K

+V1.5+V1.05

L518

L518

0-06

0-06

450mA

C650

C658

C659

C659

4.7U-6.3-06R-K

4.7U-6.3-06R-K

MCH_CLKREQ#

VGA_CLKREQ#

From

X

CLK_MCH_3GPLL

X

X

X

CLK_PCIE_VGA

X

X

XTAL_OUT

XTAL_IN

C123

C123

33P-50-04N-J

33P-50-04N-J

C658

.1U-10V-04R-K

.1U-10V-04R-K

C656

C656

.1U-10V-04R-K

.1U-10V-04R-K

C657

.1U-10V-04R-K

.1U-10V-04R-K

MCH_CLKREQ#11

CLKPCI_EC25

PCI_CLK_LAN20

CLKPCI_DEBUG19

CLK_ICHPCI16

CARD_CLKUSB4823

CLK_USB4816

CLK_ICH1416

DREFCLK11

DREFCLK#11

SMB_CLK_GEN25

SMB_DATA_GEN25

CLKBSEL2

.1U-10V-04R-K

.1U-10V-04R-K

C648

C648

.1U-10V-04R-K

.1U-10V-04R-K

CLKPCI_EC

CARD_CLKUSB48

CLK_USB48 CLKBSEL0

CLK_ICH14

SMB_CLK_GEN

SMB_DATA_GEN

R179 10K-04R179 10K-04

R186 0-04R186 0-04

R605 2.2K-04R605 2.2K-04

C654

C654

C657

BSEL2

FSB533 133

R536 56-04R536 56-04

+V1.05

CLK_BSEL0

CLK_BSEL1

R601 1K-04R601 1K-04

CLK_BSEL2

R597 1K-04R597 1K-04

4

01

0

CLK_VDDA

C647

C647

C645

C645

.1U-10V-04R-K

.1U-10V-04R-K

R158 475-1-04R158 475-1-04

R152 33-04R152 33-04

R610 33-04R610 33-04

R608 33-04R608 33-04

R609 33-04R609 33-04

R141 0-04R141 0-04

R146 100-04R146 100-04

R185 33-04R185 33-04

R150 0-04R150 0-04

R149 0-04R149 0-04

CLK_BSEL2

CLK_BSEL1CLKBSEL1

CLK_BSEL0CLKBSEL0

R538 1K-04R538 1K-04

R599 @0-04R599 @0-04

R595 1K-04R595 1K-04

R181 @0-04R181 @0-04

R594 1K-04R594 1K-04

R172 @0-04R172 @0-04

.1U-10V-04R-K

.1U-10V-04R-K

MHZBSEL1 BSEL0

XTAL_OUT

XTAL_IN

CLKREQ_B#MCH_CLKREQ#

PCI2

PCI3PCI_CLK_LAN

PCI4/LCDCLKCLKPCI_DEBUG

PCIF5/ITP_ENCLK_ICHPCI

CLKBSEL1

CLKBSEL2

DOT_96DREFCLK

DOT_96#DREFCLK#

MCH_BSEL0 11

CPU_BSEL0 6

MCH_BSEL1 11

CPU_BSEL1 6

MCH_BSEL2 11

CPU_BSEL2 6

3

U10

U10

2

VDD_PCI

9

VDD_48

16

VDD_PLL3

39

VDD_SRC

55

VDD_CPU

61

VDD_REF

59

XTAL_OUT

60

XTAL_IN

1

PCI_0/CLKREQ_A#

3

PCI_1/CLKREQ_B#

4

PCI_2/TME

5

PCI_3

6

PCI_4/27_SELECT

7

PCIF_5/ITP_EN

10

USB_48MHz/FS_A

57

FS_B/TEST_MODE

62

REF/FS_C/TEST_SEL

13

SRC_0/DOT_96

14

SRC_0#/DOT_96#

64

SCL

63

SDA

8

VSS_PCI

11

VSS_48

15

VSS_I/O

19

VSS_PLL3

23

VSS_SRC_1

29

VSS_SRC_2

42

VSS_SRC_3

52

VSS_CPU

58

VSS_REF

ICS9LPRS365BG

ICS9LPRS365BG

R142

R142

@10K-04

@10K-04

R153

R153

10K-04

10K-04

12

VDD_I/O

PCI_STOP#

CPU_0

CPU_0#

SRC_4

SRC_4#

SRC_6

SRC_6#

SRC_9

SRC_9#

SRC_10

SRC_10#

20

26

36

45

49

PM_STPCPU#

37

PM_STPPCI#

38

VR_PWRGD_CLKEN

56

CPU0

54

CPU0#

53

CPU1

51

CPU1#

50

SRC8

47

46

48

NC

LCDCK DREFSSCLK

17

LCDCK# DREFSSCLK#

18

SRC2

21

SRC2#

22

24

25

SRC4

27

SRC4#

28

SRC6 CLK_PCIE_ICH

41

SRC6#

40

CLKREQ_F# VGA_CLKREQ#

44

43

30

31

34

35

33

32

VDD_PLL3_I/O

VDD_SRC_I/O_1

VDD_SRC_I/O_2

VDD_SRC_I/O_3

VDD_CPU_I/O

CPU_STOP#

CKPWRGD/PD#

CPU_1_MCH

CPU_1_MCH#

SRC_8/CPU_ITP

SRC_8#/CPU_ITP#

LCDCLK/27M

LCDCLK#/27M_SS

SRC_2/SATAT

SRC_2#/SATAC

SRC_3/CLKREQ_C#

SRC_3#/CLKREQ_D#

SRC_7/CLKREQ_F#

SRC_7#/CLKREQ_E#

SRC_11/CLKREQ_H#

SRC_11#/CLKREQ_G#

0= Pin46/47 SRC output.

1= Pin46/47 ITP output.

PCIF5/ITP_EN PCI4/LCDCLK

L519

Y502

Y502

HUS-8_000-30

HUS-8_000-30

R160

R160

@10M-1-04

@10M-1-04

C118

C118

33P-50-04N-J

33P-50-04N-J

L519

0-06

0-06

C652

C652

4.7U-6.3-06R-K

4.7U-6.3-06R-K

D D

Close to device

+V3.3

R157 10K-04R157 10K-04

C C

Pin number

A

Pin 1

B

Pin 3

C

Pin 24

D

Pin 25

E

Pin 43

F

Pin 44

B B

G

Pin 32

H

Pin 33

R616 10K-04R616 10K-04

SRC BUS(Low/High)CLK REQ

SRC0 or SRC2

SRC1 or SRC4

SRC0 or SRC2

SRC1 or SRC4

SRC7 or SRC6

SRC7 or SRC8

SRC11 or SRC9

SRC11 or SRC10

Ce = 2*CL - ( Cs + Ci )

14.31818M-20-20-KT-D

CL = Crystal Load Cap = 20P

14.31818M-20-20-KT-D

Ci = IC internal Cap = 5P

Cs = 2P

Ce = Crystal external Cap = 33P

A A

5

C655

C655

.1U-10V-04R-K

.1U-10V-04R-K

R184 0-04R184 0-04

R189 0-04R189 0-04

R188 0-04R188 0-04

R183 0-04R183 0-04

R617 0-04R617 0-04

R618 0-04R618 0-04

R148 0-04R148 0-04

R147 0-04R147 0-04

R144 0-04R144 0-04

R155 0-04R155 0-04

R143 0-04R143 0-04

R154 0-04R154 0-04

R170 0-04R170 0-04

R171 0-04R171 0-04

R615 475-1-04R615 475-1-04

0 = Pin17/18 LCDCLK & DOT_96

+V3.3+V3.3

for internal graphic controller support

1 = Pin17/18 27M & 27M_SS & SRC_0

for external graphic controller support

R151

R151

@10K-04

@10K-04

R607

R607

10K-04

10K-04

2

C644

C644

.1U-10V-04R-K

.1U-10V-04R-K

C651

C651

.1U-10V-04R-K

.1U-10V-04R-K

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_PCIE_VGA

CLK_PCIE_VGA#SRC8#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_ICH#

C643

C643

.1U-10V-04R-K

.1U-10V-04R-K

PM_STPCPU# 16

PM_STPPCI# 16

VR_PWRGD_CLKEN 16

CLK_CPU_BCLK 6

CLK_CPU_BCLK# 6

CLK_MCH_BCLK 9

CLK_MCH_BCLK# 9

CLK_PCIE_VGA 19

CLK_PCIE_VGA# 19

DREFSSCLK 11

DREFSSCLK# 11

CLK_PCIE_SATA 15

CLK_PCIE_SATA# 15

CLK_MCH_3GPLL 11

CLK_MCH_3GPLL# 11

CLK_PCIE_ICH 17

CLK_PCIE_ICH# 17

VGA_CLKREQ# 19

Reserved for ICS9LPRS365

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SCHEMATICS

SCHEMATICS

SCHEMATICS

Date: Sheet

Date: Sheet

Date: Sheet

C653

C653

C646

C646

4.7U-6.3-06R-K

4.7U-6.3-06R-K

.1U-10V-04R-K

.1U-10V-04R-K

0 = Overclocking of CPU

and SRC Allowed

+V3.3

1 = Overclocking of CPU

and SRC NOT allowed

R145

R145

@10K-04

@10K-04

R156

R156

10K-04

10K-04

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

1

C650

4.7U-6.3-06R-K

4.7U-6.3-06R-K

PCI2

of

of

of

832Monday, July 07, 2008

832Monday, July 07, 2008

832Monday, July 07, 2008

C

C

C

Page 9

5

4

3

2

1

H_A#[31:3]

D D

H_ADS#6

H_ADSTB#06

H_HIT#

H_HITM#

H_LOCK#

H_CPURST#6

CLK_MCH_BCLK#8

CLK_MCH_BCLK8

H_DINV#[3:0]6

H_DEFER#

H_REQ#[4:0]6

H_CPUSLP#6,15

H_ADSTB#16

H_BNR#6

H_BPRI#6

H_BREQ#06

H_DBSY#6

H_DPWR#6

H_DRDY#6

H_DSTBN#06

H_DSTBN#16

H_DSTBN#26

H_DSTBN#36

H_DSTBP#06

H_DSTBP#16

H_DSTBP#26

H_DSTBP#36

H_RS#06

H_RS#16

H_RS#26

H_TRDY#6

C C

H_DEFER#6

B B

H_HIT#6

H_HITM#6

H_LOCK#6

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DBSY#

H_DINV#[3:0]

H_REQ#[4:0]

H_CPUSLP#

H_TRDY#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_VREF

H_VREF

H_DEFER#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DPWR#

H_DRDY#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

F8

D12

C13

A8

E13

E12

J12

B13

A13

G13

A12

D14

F14

J13

E17

H15

G15

G14

A15

B18

B15

E14

H13

C14

A17

E15

H17

D17

G17

F10

C12

H16

E2

B9

C7

G8

B10

E1

AA6

AA5

C10

C6

H5

J6

T9

U6

G7

E6

F3

M8

T1

AA3

F4

M7

T2

AB3

C8

B4

C5

G9

E9

G12

B8

F12

A5

B6

G10

E8

E10

U5A

U5A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB0#

HADSTB1#

H_AVREF

HBNR#

HBPRI#

HBREQ0#

HCPURST#

HDVREF

HCLKN

HCLKP

HDBSY#

HDEFER#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HHIT#

HHITM#

HLOCK#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

QG92945GSE

QG92945GSE

HOST

HOST

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

H_D#0

C4

H_D#1

F6

H_D#2

H9

H_D#3

H6

H_D#4

F7

H_D#5

E3

H_D#6

C2

H_D#7

C3

H_D#8

K9

H_D#9

F5

H_D#10

J7

H_D#11

K7

H_D#12

H8

H_D#13

E5

H_D#14

K8

H_D#15

J8

H_D#16

J2

H_D#17

J3

H_D#18

N1

H_D#19

M5

H_D#20

K5

H_D#21

J5

H_D#22

H3

H_D#23

J4

H_D#24

N3

H_D#25

M4

H_D#26

M3

H_D#27

N8

H_D#28

N6

H_D#29

K3

H_D#30

N9

H_D#31

M1

H_D#32

V8

H_D#33

V9

H_D#34

R6

H_D#35

T8

H_D#36

R2

H_D#37

N5

H_D#38

N2

H_D#39

R5

H_D#40

U7

H_D#41

R8

H_D#42

T4

H_D#43

T7

H_D#44

R3

H_D#45

T5

H_D#46

V6

H_D#47

V3

H_D#48

W2

H_D#49

W1

H_D#50

V2

H_D#51

W4

H_D#52

W7

H_D#53

W5

H_D#54

V5

H_D#55

AB4

H_D#56

AB8

H_D#57

W8

H_D#58

AA9

H_D#59

AA8

H_D#60

AB1

H_D#61

AB7

H_D#62

AA2

H_D#63

AB5

H_XRCOMP

A10

H_XSCOMP

A6

H_XSWING

C15

H_YRCOMP

J1

H_YSCOMP

K1

H_YSWING

H1

Modify 3.

H_D#[63:0]

H_D#[63:0] 6H_A#[31:3]6

+V1.05

H_XSCOMP

H_YSCOMP

H_XRCOMP

H_YRCOMP

R566 54.9-1-04R566 54.9-1-04

R36 54.9-1-04R36 54.9-1-04

R569 24.9-1-04R569 24.9-1-04

R33 24.9-1-04R33 24.9-1-04

H_VREF

C71

C71

.1U-10V-04R-K

.1U-10V-04R-K

+V1.05

R38

R38

100-1-04

100-1-04

R39

R39

200-1-04

200-1-04

Layout close to H_VREF pin

+V1.05

R108

R108

221-1-04

+V1.05

221-1-04

R103

R103

100-1-04

100-1-04

R34

R34

221-1-04

221-1-04

R37

R37

100-1-04

100-1-04

H_XSWING

H_YSWING

C95

C95

.1U-10V-04R-K

.1U-10V-04R-K

C62

C62

.1U-10V-04R-K

.1U-10V-04R-K

W33

AM33

AL33

AN32

AN31

W28

W29

W32

G24

AN19

AM19

AL19

AK19

AJ19

AH19

AN3

G19

G16

AN2

AM4

AD4

AK4

W31

AH4

AG4

AE4

AM1

C33

B33

A32

V27

J24

H24

F24

E24

D24

K33

A31

E21

C23

J19

H19

F19

E19

D19

C19

B19

A19

F16

E16

D16

C16

B16

A16

AF4

AL4

AJ4

Y9

Y8

Y7

QG92945GSE

QG92945GSE

U5G

U5G

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC26

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC38

NC39

NC40

NC41

NC42

NC43

NC44

NC45

NC46

NC47

NC48

NC49

NC50

NC51

NC52

NC53

NC54

NC55

NC56

NC57

NC58

NC59

NC60

NC

NC

MCH_RSVD26

MCH_RSVD27

MCH_RSVD28

MCH_RSVD29

MCH_RSVD30

MCH_RSVD31

MCH_RSVD32

MCH_RSVD33

MCH_RSVD34

MCH_RSVD35

MCH_RSVD36

MCH_RSVD37

MCH_RSVD38

MCH_RSVD39

MCH_RSVD40

MCH_RSVD41

MCH_RSVD42

NC61

NC62

NC63

NC64

NC65

NC66

NC67

NC68

NC69

NC70

NC71

NC72

W30

Y6

AL1

Y5

Y10

W10

W25

V24

U24

V10

U10

K18

Y25

Y24

AB22

AB21

AB19

AB16

AB14

AA12

W24

AA24

AB24

AB20

AB18

AB15

AB13

AB12

AB17

A A

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SCHEMATICS

SCHEMATICS

SCHEMATICS

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

945GSE- Host(1/4)

945GSE- Host(1/4)

945GSE- Host(1/4)

1

932Monday, July 07, 2008

932Monday, July 07, 2008

932Monday, July 07, 2008

C

C

C

of

of

of

Page 10

5

4

3

2

1

+V1.05

2940mA

U5H

U5H

T25

VCC_NCTF1

R25

VCC_NCTF2

P25

VCC_NCTF3

D D

M_A_DQ[63:0]13

C C

B B

M_A_DQ[63:0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AC31

AB28

AE33

AF32

AC33

AB32

AB31

AE31

AH31

AK31

AL28

AK27

AH30

AL32

AJ28

AJ27

AH32

AF31

AH27

AF28

AJ32

AG31

AG28

AG27

AN27

AM26

AJ26

AJ25

AL27

AN26

AH25

AG26

AM12

AL11

AM11

AK11

AM8

AK8

AG9

AK6

AG11

AH6

AN6

AM6

AK3

AM5

AG2

AE7

AH5

AG3

AG5

AG19

AG21

AG20

AH9

AK9

AF9

AF8

AF7

AJ6

AL2

AL5

AJ3

AJ2

AF3

AF6

AF5

U5C

U5C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SB_CAS#

SB_RAS#

SB_WE#

QG92945GSE

QG92945GSE

SA_BS_0

SA_BS_1

SA_BS_2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

DDR2 SYSTEM MEMORY

DDR2 SYSTEM MEMORY

SA_RCVENINB

SA_RCVENOUTB

SA_WEB

SB_BS_0

SB_BS_1

SB_BS_2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

AH11

AG17

AB30

AL31

AF30

AK26

AL9

AG7

AK5

AH3

AC28

AJ30

AK33

AL25

AN9

AH8

AM2

AE3

AC29

AK30

AJ33

AM25

AN8

AJ8

AM3

AE2

AJ15

AM17

AM15

AH15

AK15

AN15

AJ18

AF19

AN17

AL17

AG16

AL18

AG18

AL14

AJ17

AK18

AN28

AM28

AH17

AH21

AJ20

AE27

AN20

AL21

AK21

AK22

AL22

AH22

AG22

AF21

AM21

AE21

AL20

AE22

AE26

AE20

M_A_BS#1

M_A_BS#2

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_BS#0

AK12

TP3TP3

TP2TP2

M_A_BS#[2:0]

M_A_DM[7:0]

M_A_DQS0 13

M_A_DQS1 13

M_A_DQS2 13

M_A_DQS3 13

M_A_DQS4 13

M_A_DQS5 13

M_A_DQS6 13

M_A_DQS7 13

M_A_DQS#0 13

M_A_DQS#1 13

M_A_DQS#2 13

M_A_DQS#3 13

M_A_DQS#4 13

M_A_DQS#5 13

M_A_DQS#6 13

M_A_DQS#7 13

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_BS#[2:0] 13

M_A_DM[7:0] 13

M_A_A[13:0]

M_A_CAS# 13

M_A_RAS# 13

M_A_WE# 13

M_A_A[13:0] 13

+V1.05

780mA

M25

M24

W22

M22

W21

M21

W20

M20

M19

M18

M17

M16

M15

W14

M14

M10

AB10

AA10

N25

P24

N24

Y22

V22

U22

T22

R22

P22

N22

Y21

V21

U21

T21

R21

P21

N21

Y20

V20

U20

T20

R20

P20

N20

Y19

P19

N19

Y18

P18

N18

Y17

P17

N17

Y16

P16

N16

Y15

P15

N15

Y14

V14

U14

T14

R14

P14

N14

T10

R10

P10

N10

L10

D1

A18

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

MCH_RSVD3

MCH_RSVD4

MCH_RSVD5

MCH_RSVD6

QG92945GSE

QG92945GSE

NCTF

NCTF

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

CFG19

MCH_RSVD10

MCH_RSVD11

MCH_RSVD12

MCH_RSVD13

MCH_RSVD14

MCH_RSVD15

MCH_RSVD16

MCH_RSVD17

MCH_RSVD18

MCH_RSVD19

MCH_RSVD20

MCH_RSVD21

MCH_RSVD22

MCH_RSVD23

MCH_RSVD24

MCH_RSVD25

+V1.5

1250mA

AD25

AC25

AB25

AD24

AC24

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

K14

AD13

Y13

W13

V13

U13

T13

R13

P13

N13

M13

AD12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

AD11

AD10

K10

AN33

AA25

V25

U25

AA22

AA21

AA20

AA19

AA18

AA17

AA16

AA15

AA14

AA13

A4

A33

B2

AN1

C1

K28

K25

K26

R24

T24

K21

K19

K20

K24

K22

J17

K23

K17

K12

K13

K16

K15

+V3.3

CF19 : DMI LANE REVERSAL

Low = Normal (Default)

High = LANES REVERSED

R118

R118

@1K-1-04

@1K-1-04

A A

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SCHEMATICS

SCHEMATICS

SCHEMATICS

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

945GSE- DDR(2/4)

945GSE- DDR(2/4)

945GSE- DDR(2/4)

1

10 32Monday, July 07, 2008

10 32Monday, July 07, 2008

10 32Monday, July 07, 2008

C

C

C

of

of

of

Page 11

5

D D

C C

U5B

U5B

DMI_RXN017

DMI_RXN117

DMI_RXP017

DMI_RXP117

DMI_TXN017

DMI_TXN117

DMI_TXP017

DMI_TXP117

B B

+V1.8S

A A

DMI_RXN0

DMI_RXN1

DMI_RXP0

DMI_RXP1

DMI_TXN0

DMI_TXN1

DMI_TXP0

DMI_TXP1

M_CLK_DDR013

M_CLK_DDR113

M_CLK_DDR#013

M_CLK_DDR#113

M_CKE013

M_CKE113

M_CS#013

M_CS#113

M_ODT013

M_ODT113

R23 80.6-1-04R23 80.6-1-04

R24 80.6-1-04R24 80.6-1-04

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR#0

M_CLK_DDR#1

M_CKE0

M_CKE1

M_CS#0

M_CS#1

M_ODT0

M_ODT1

M_RCOMPN

M_RCOMPP

M_VREF_MCH

AF33

AG1

AM30

AG33

AK1

AN30

AN21

AN22

AF26

AF25

AG14

AF12

AK14

AH12

AJ21

AF11

AE12

AF14

AJ14

AJ12

AN12

AN14

AA33

AE1

Y29

Y32

Y28

Y31

V28

V31

V29

V32

AJ1

AF1

DMI_RXN0

DMI_RXN1

DMI_RXP0

DMI_RXP1

DMI_TXN0

DMI_TXN1

DMI_TXP0

DMI_TXP1

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SMOCDCOMP0

SMOCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

QG92945GSE

QG92945GSE

4

CFG0

CFG1

CFG2

CFG3

CFG5

CFG6

DMI

DMI

MCH_RSVD1

MCH_RSVD2

MCH_RSVD7

MCH_RSVD8

MCH_RSVD9

CFG/RSVD

CFG/RSVD

DDR2 MUXING

DDR2 MUXING

ICHSYNC#

BM_BUSY#

EXT_TS0#

PM

PM

EXT_TS1#/DPRSLPVR

THRMTRIP#

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

CLK

CLK

DREF_SSCLKN

DREF_SSCLKP

CLKREQB

C18

E18

G20

G18

J20

J18

K32

K31

C17

F18

A3

E31

G21

F26

H26

J15

AB29

W27

A27

A26

J33

H33

J22

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

CFG3

CFG5

CFG6

MCH_SYNC#

PM_BMBUSY#

PM_EXTTS#0_R

PM_EXTTS#1_R

PM_THRMTRIP#

PM_CPU_PWRGD

NB_RSTIN#

DREFCLK#

DREFCLK

DREFSSCLK#

DREFSSCLK

MCH_CLKREQ#

TP516TP516

TP515TP515

CFG5

0/1: DMI x2 / DMI x4

R100 0-04R100 0-04

R582 0-04R582 0-04

R592 0-04R592 0-04

R32 100-04R32 100-04

MCH_BSEL0 8

MCH_BSEL1 8

MCH_BSEL2 8

R570 2.2K-04R570 2.2K-04

3

CLK_MCH_3GPLL#8

CLK_MCH_3GPLL8

CRT_DDC_CLK19,24

CRT_DDC_DATA19,24

CRT_BLUE19,24

CRT_GREEN19,24

CRT_RED19,24

VSYNC19,24

HSYNC19,24

L_BKLTEN14,19

L_DDC_CLK14,19

L_DDC_DATA14,19

L_VDDEN14,19

LA_CLKN14,19

LA_CLKP14,19

LA_DATAN014,19

LA_DATAN114,19

LA_DATAN214,19

LA_DATAP014,19

LA_DATAP114,19

LA_DATAP214,19

MCH_ICH_SYNC# 16

PM_BMBUSY# 16

PM_EXTTS#0 13

PM_DPRSLPVR 16,29

PM_THRMTRIP# 6,15

PM_CPU_PWRGD 29

BUF_PLT_RST# 16,19,25

DREFCLK# 8

DREFCLK 8

DREFSSCLK# 8

DREFSSCLK 8

MCH_CLKREQ# 8

TP519TP519

CLK_MCH_3GPLL#

CLK_MCH_3GPLL

VSYNC

HSYNC

R576 255-1-04R576 255-1-04

L_BKLTEN

L_DDC_CLK

L_DDC_DATA

L_VDDEN

LA_CLKN

LA_CLKP

LA_DATAN0

LA_DATAN1

LA_DATAN2

LA_DATAP0

LA_DATAP1

LA_DATAP2

SDVOCTRL_DATA

TP520TP520

CRT_DDC_CLK

CRT_DDC_DATA

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRTIREF

LBKLT_CRTL

LCTLA_CLK

LCTLB_CLK

LIBG

M_VREF_MCH

AA26

G29

G28

G31

G32

H27

Y26

H20

H22

A24

A23

E25

F25

C25

D25

F27

D27

H25

H30

F28

E28

H28

K30

K27

K29

D30

C30

A30

A29

F32

D31

H31

C31

F33

D33

F30

E33

D32

F29

J27

J29

J30

C586

C586

.1U-10V-04R-K

.1U-10V-04R-K

2

U5F

U5F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_CLK

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

QG92945GSE

QG92945GSE

C557

C557

.1U-10V-04R-K

.1U-10V-04R-K

SDV0_TVCLKIN#

SDVO_FLDSTALL#

MISC

MISC

SDVO_FLDSTALL

SDVOB_GREEN#

LVDS VGA

LVDS VGA

0.05A

C562

C562

2.2U-6.3-06R-K

2.2U-6.3-06R-K

EXP_COMPI

EXP_ICOMPO

SDVO_INT#

SDVO_TVCLKIN

SDVO_INT

SDVO

SDVO

SDVOB_RED#

SDVOB_BLUE#

SDVOB_CLKN

SDVOB_RED

SDVOB_GREEN

SDVOB_BLUE

SDVOB_CLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV

TV

TV_IRTNB

TV_IRTNC

TV_DCONSEL0

TV_DCONSEL1

R560

R560

10K-1-04

10K-1-04

R564

R564

10K-1-04

10K-1-04

R28

M28

N30

R30

T29

M30

P30

T30

P28

N32

P32

T32

N28

M32

P33

R32

A21

C20

E20

G23

B21

C21

D21

G26

J26

EXP_COMP

R106 24.9-1-04R106 24.9-1-04

+V1.5

Layout close to NB

PM_EXTTS#0_R

PM_EXTTS#1_R

LCTLA_CLK

LCTLB_CLK

LIBG

R575 1.5K-1-04R575 1.5K-1-04

CRT_RED

CRT_GREEN

CRT_BLUE

1

+V1.5

R583 10K-04R583 10K-04

R631 @10K-04R631 @10K-04

R579 10K-04R579 10K-04

R585 10K-04R585 10K-04

R134 150-1-04R134 150-1-04

R131 150-1-04R131 150-1-04

R125 150-1-04R125 150-1-04

+V3.3+V1.8S

<OrgAddr3>

<OrgAddr3>

<OrgAddr3>

Project : J10IL1

Project : J10IL1

Project : J10IL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SCHEMATICS

SCHEMATICS

SCHEMATICS

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

945GSE- DMI & VGA(3/4)

945GSE- DMI & VGA(3/4)

945GSE- DMI & VGA(3/4)

1

11 32Monday, July 07, 2008

11 32Monday, July 07, 2008

11 32Monday, July 07, 2008

C

C

C

of

of

of

Page 12

5

U5E

U5E

AH33

VSS1

Y33

VSS2

V33

VSS3

R33

VSS4

G33

VSS5

AK32

VSS6

AG32

VSS7

AE32

VSS8

AC32

VSS9

AA32

VSS10

AM31

AJ31

AA31

M31

AL30

AG30

AE30

AC30

AA30

Y30

V30

U30

G30

E30

B30

AA29

U29

R29

P29

N29

M29

H29

E29

B29

AK28

AH28

AE28

AA28

U28

D28

AM27

AF27

AB27

AA27

Y27

U27

R27

P27

N27

M27

G27

E27

C27

B27

AL26

AH26

W26

U26

AN25

AK25

AG25

AE25

G25

A25

H23

B23

AM22

AJ22

AF22

G22

E22

H21

AM20

AK20

AH20

AF20

D20

W19

R19

AM18

AH18

AF18

U18

H18

D18

AK17

V17

B17

AH16

U16

U32

H32

E32

C32

U31

T31

R31

P31

N31

J31

F31

T28

J28

T27

J25

F23

J21

F21

T17

F17

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101