Page 1

5

D D

4

H81H3-MV

3

2

1

Rev :1.0

TABLE OF CONTENTS

Page Index

------- ------------------------

1

COVER PAGE

2

Block Diagram

3

C C

10

11

12

B B

13

14

15

16

17

18

19

GPIO Function Map

4

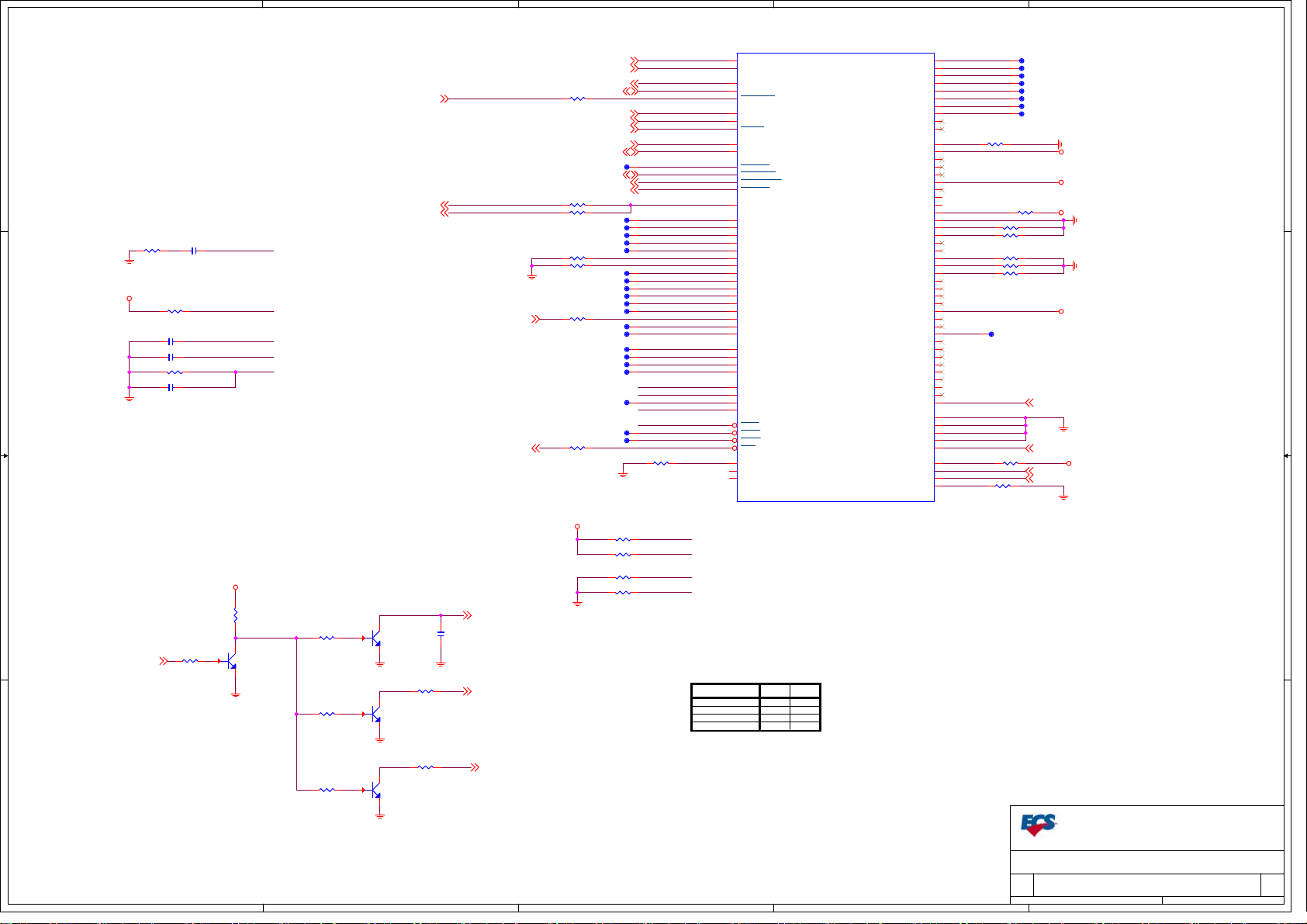

CPU-PEG/DMI/FDI/DDI

5

CPU MISC

6

CPU DDR3

7

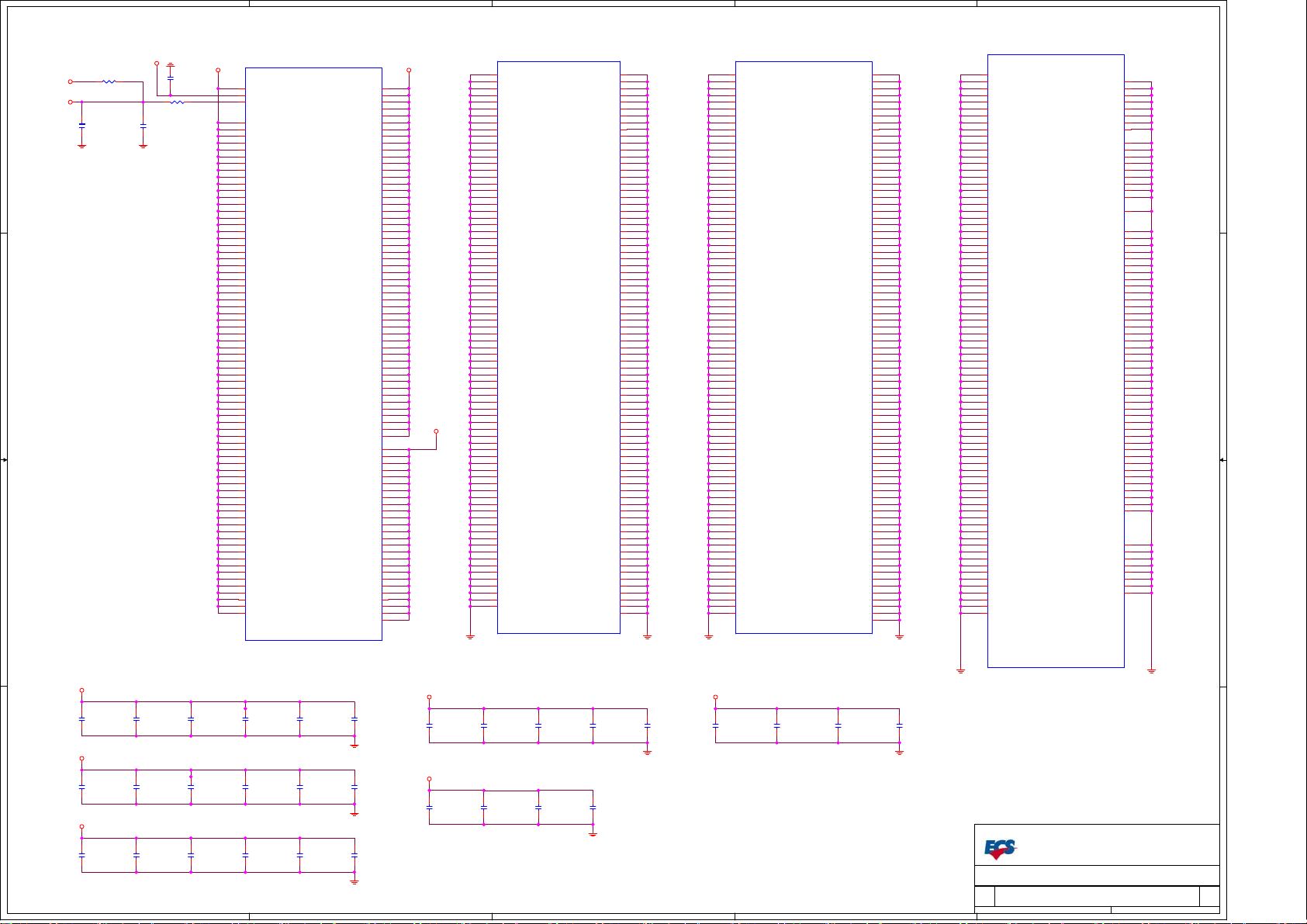

CPU PWR/GND

8

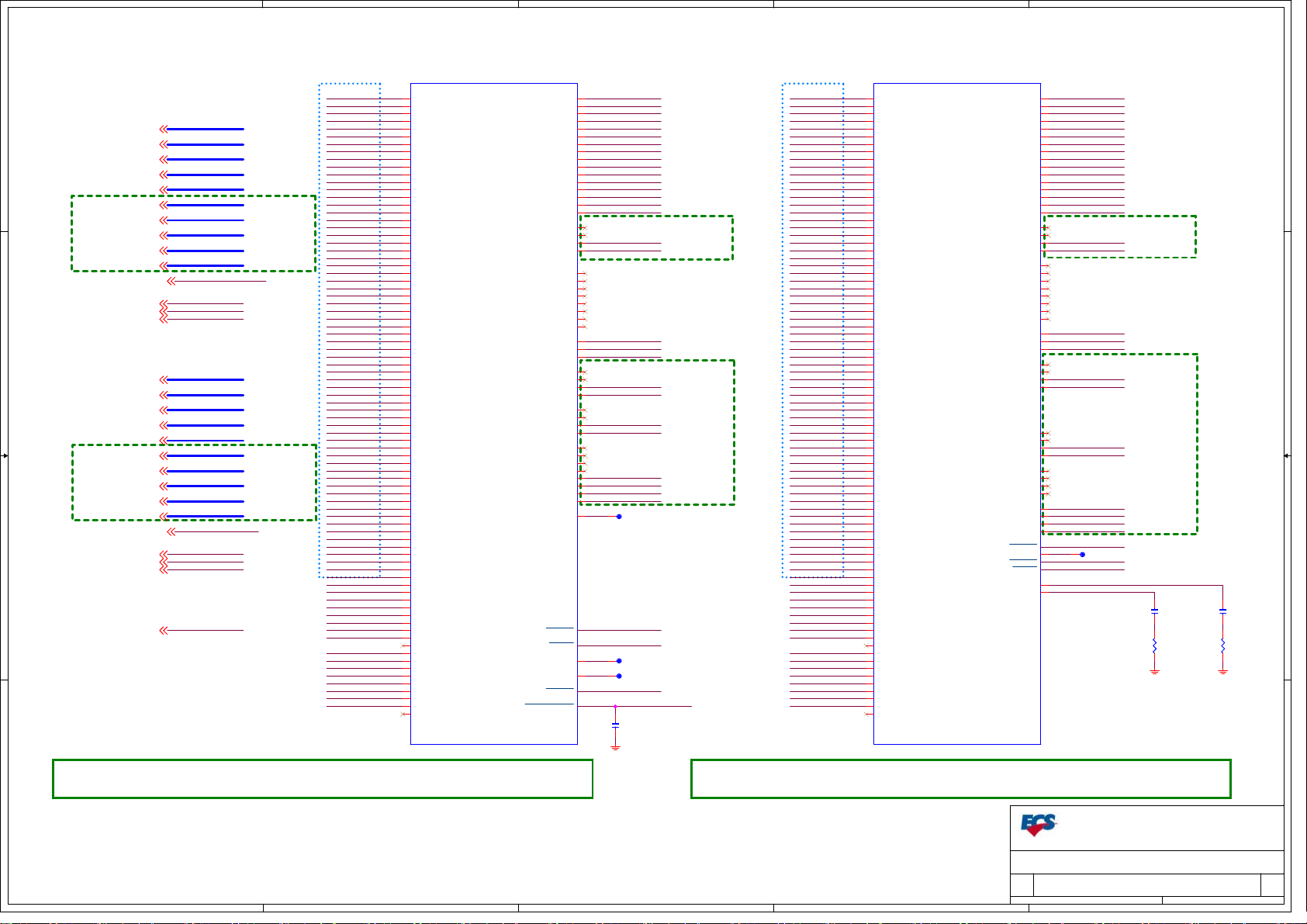

DDR3 CH_A_DIMM1/2

9

DDR3 CH_B_DIMM3/4

DDR3-Vref

RT8884B Vcore

Vcore_Gate Driver

DC/DC PCH / DRAM//PCH-ME

DC/DC PCH_1.5V

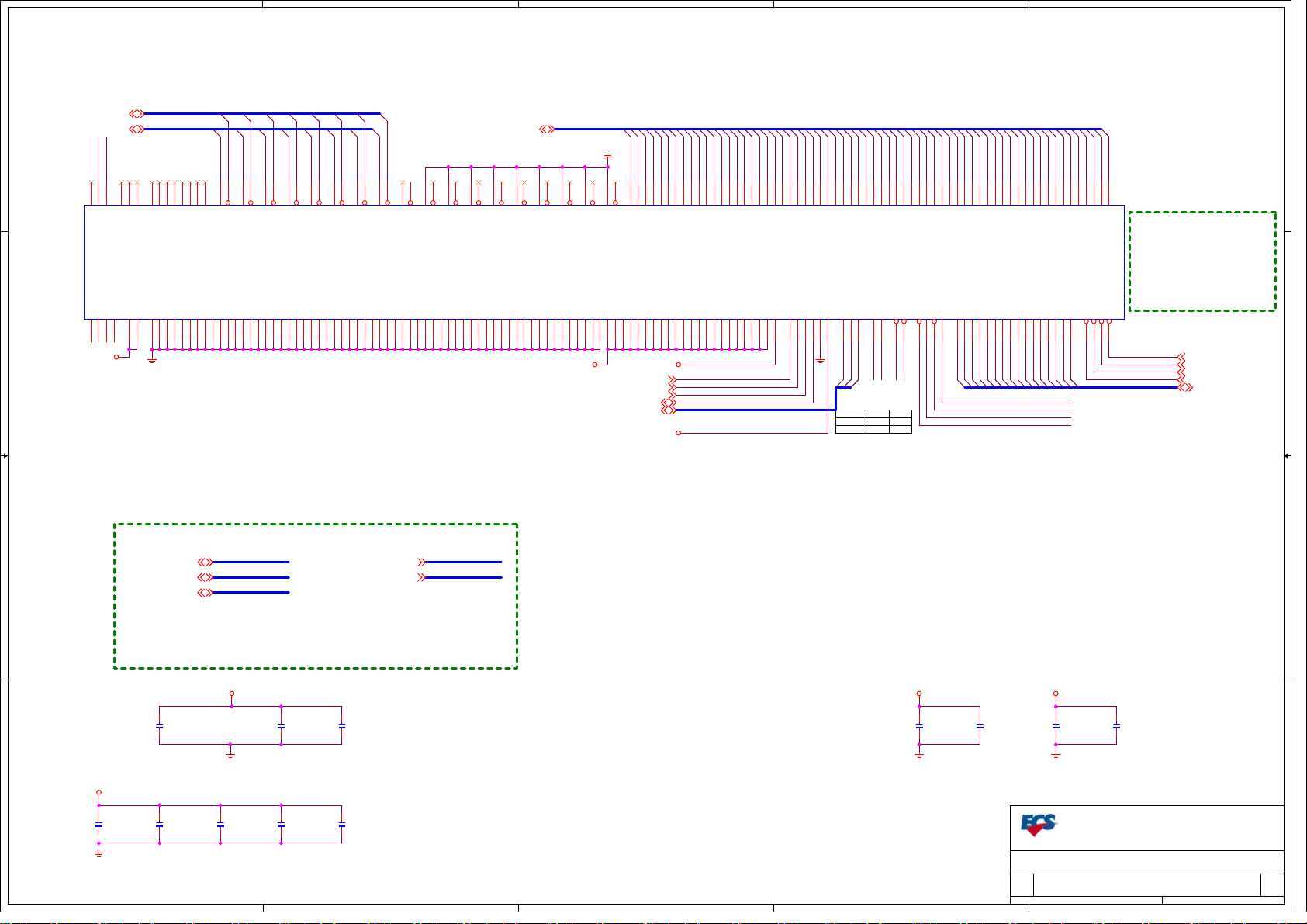

PCH-DMI/PE/USB2.0/USB3.0

PCH-FDI/DDI/CLK/VGA

PCH-SATA/SATA connecter

MISC

PCH PWR

Page Index

------- ------------------------

20

21

22

23

24

25

26

27

28

29

30

31

32

PCH GND

Slot PCI-EX16 /3X PCI-EX1

DVI / HDMI/DP

SPI/USB3F/USB3R/F_USB1

SIO / ITE8772E

LAN RT8111G(S)/8106E

AUDIO CODEC / ALC892

AUDIO PANEL

F_PANNEL / FAN / PWR/ CONN

USB

Power Delivery

Power Sequence, Reset Diagram

Clock Distribution

REVISION HISTORY:

Rev Date Notes

------ -------------- ---------------------------------------------------------------------------------

VA

2013 1224

Initial version

NOTE:

1.

Model Code:

2.

Modified from H81H3-M7 V:1.0

A A

ECS

Elitegroup Computer Systems

Elitegroup Computer Systems

CONFIDENTIAL

5

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

4

3

2

Date:

Elitegroup Computer Systems

Cover Page

Cover Page

Document Number

Document Number

Document Number

Cover Page

H81H3-MV

H81H3-MV

H81H3-MV

Sheet

Sheet

Sheet

1

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

132Monday, March 03, 2014

132Monday, March 03, 2014

132Monday, March 03, 2014

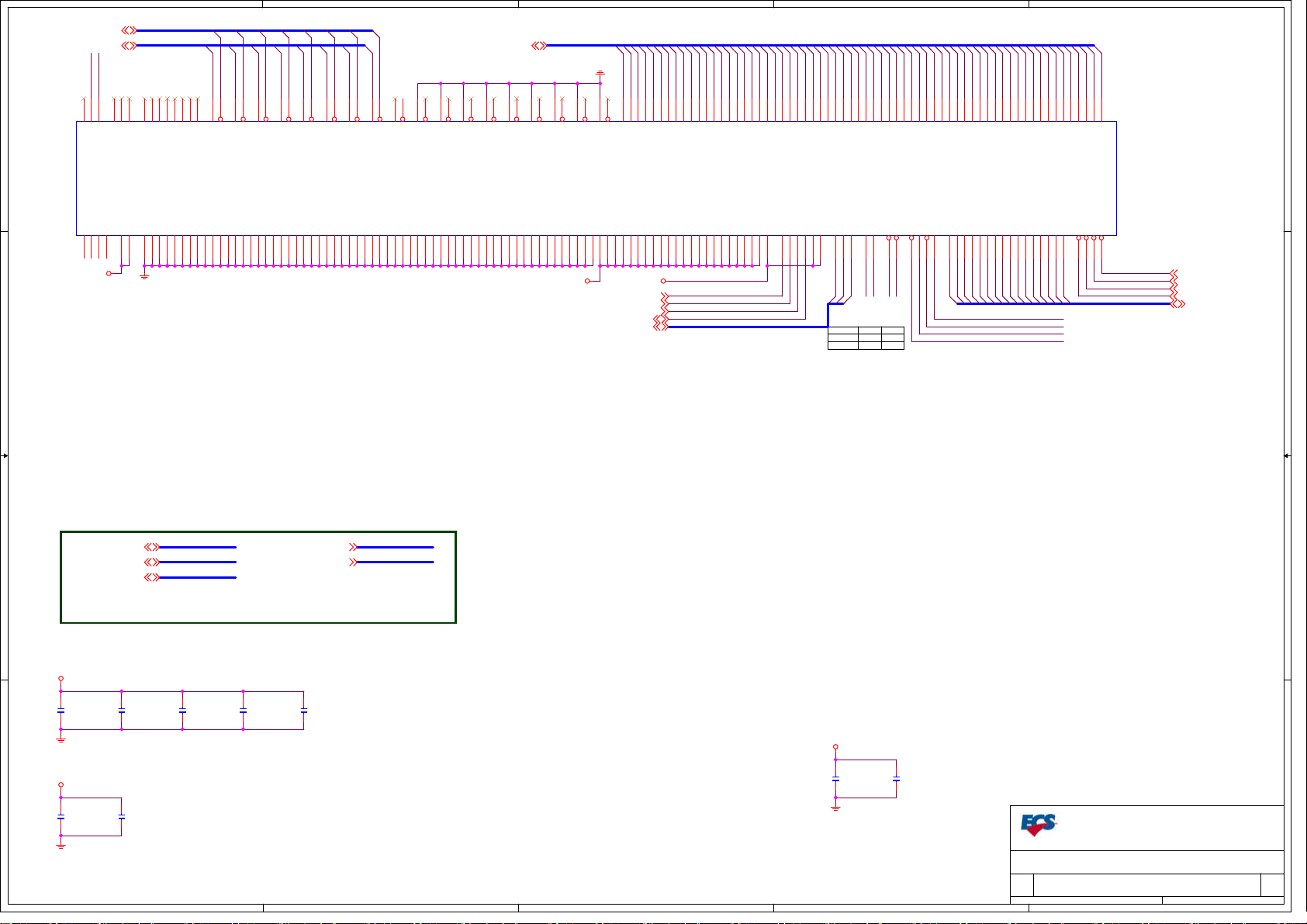

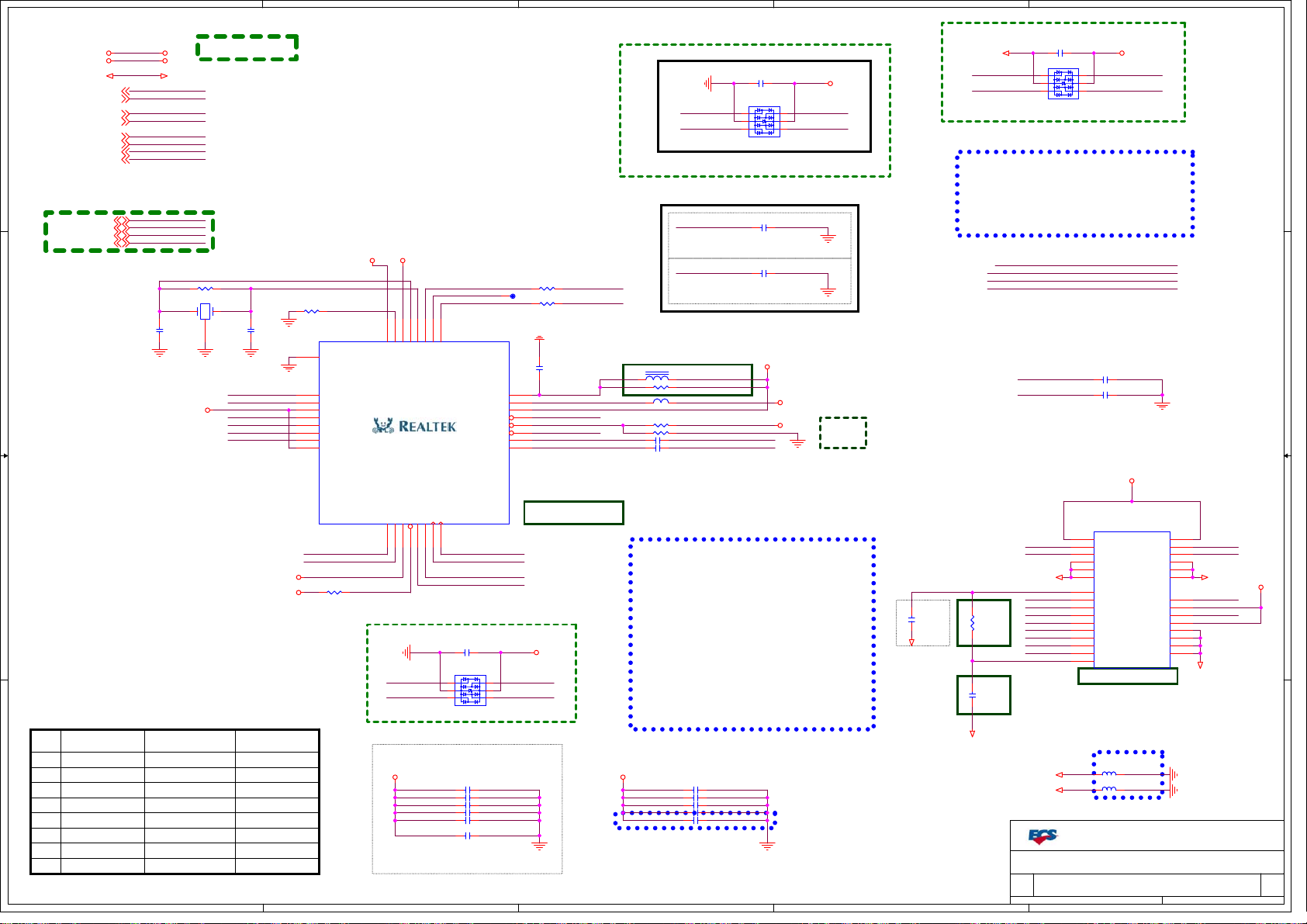

Page 2

5

PCB size:225X170

4

3

2

1

D D

PCI-E X16

HDMI

DVI-D

Gen3 8.0GT/s

DDIC

DDID

Haswell

Desktop Processor

Socket H3

FDI*2

DMI2.0

DDR3 Channel A

DDR3 Channel B

DDR3 1333MHz/1066MHz

1600 ( OC )

Total Max 8GB

VGA

C C

Jack 6 in 1

HDA

PCI-E

USB2.0

LAN:RTL8111G

co-lay

RT8106E

H81

PCI-E X1

SATA 3.0X2

SATA 2.0X2

6Gbps

3Gbps

Lynx

Point

Chipset

USB2.0

B B

USB2.0

USB2.0

F_USB2 2 Header

AUDIO CODEC:

ALC662

RJ-45 & USB2.0*2

USB 2Ports Rear

F_USB1 2 Header

SPDIF OUT

F_AUDIO

USB3.0

RUSB3.0

SIO:

IT8772

A A

PS2 KB & MS

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

5

4

3

2

Date:

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Block Diagram

Block Diagram

Document Number

Document Number

Document Number

Block Diagram

H81H3-MV

H81H3-MV

H81H3-MV

Sheet

Sheet

Sheet

1

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

232Monday, March 03, 2014

232Monday, March 03, 2014

232Monday, March 03, 2014

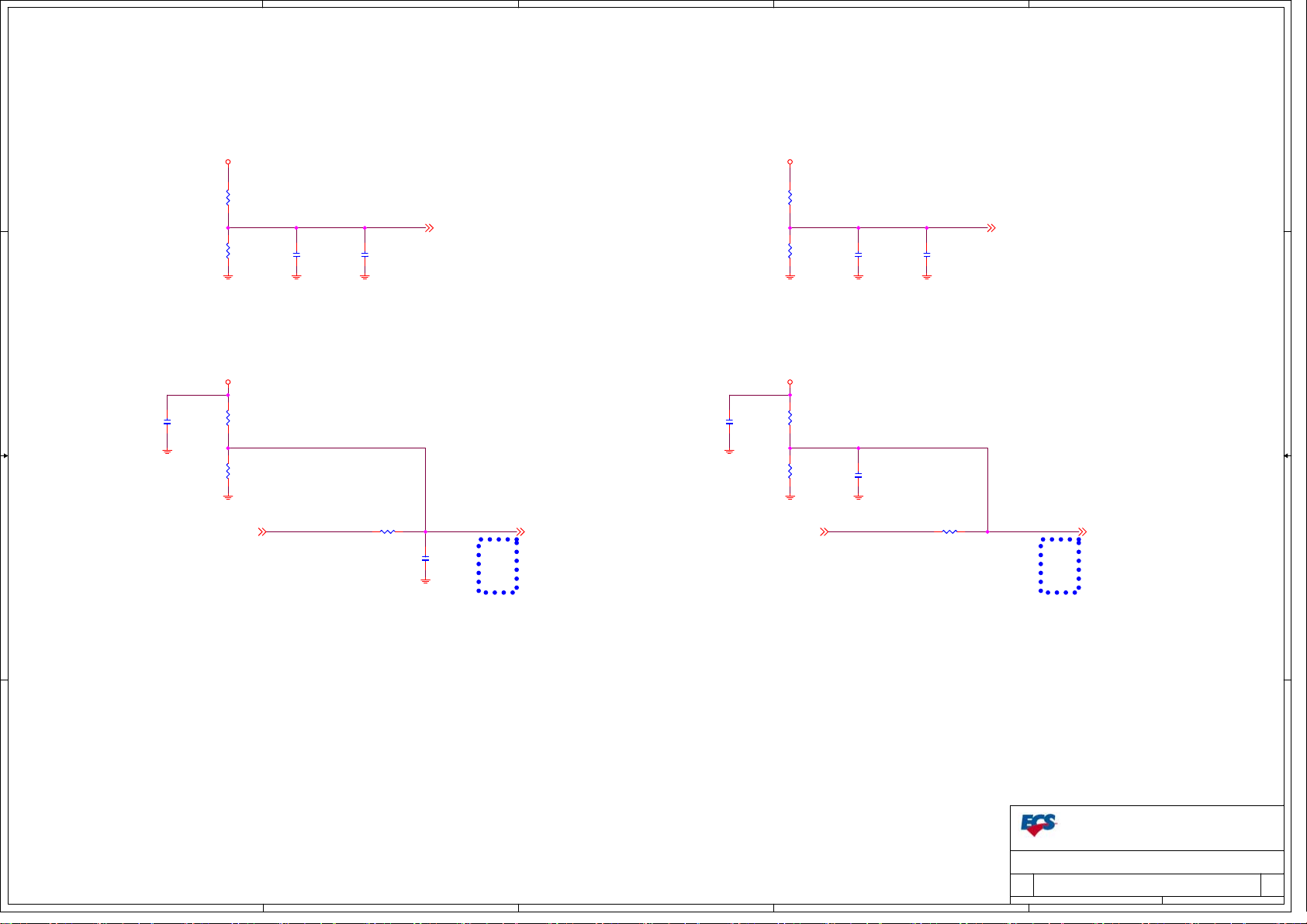

Page 3

5

4

3

2

1

PCH-GPIO function

---------------------------------------------------------------------------------------------

D D

Pin Name

---------------------------------------------------------------------------------------------

GPIO0

GPIO24 USB_5VDUAL control

GPIO45

GPIO57

GPIO46

GPIO61

GPIO27

GPIO1

GPIO68 VCC3

C C

Power Well

VCC3

3VSB

Usage

case open(reserve)

LPC_PMEGPIO13

GPI

GPI

3VSB GPO

3VSB

3VSB

(reserve)

BIOS WP

3VSB

3VSB

3VSB

ATX_3VSB GPI

VCC3

LPCPD_L

LAN_WAKE_L

OBR

NativeGPIO72 USB_5VDUAL control

Native

GPIBIOS WP

NativeWLAN_DIS_L

Native

GPI

GPITP_VGA

SIO-GPIO function

---------------------------------------------------------------------------------------------

Pin Name

---------------------------------------------------------------------------------------------

GP16

GP34

GP55

GP63

GP35

GP37

GP72

GP73

GP74

GP75

GP76

Power Well

VCC3

ATX_3VSB GPIO

ATX_3VSB

3VSB

3VSB

3VSB

3VSB

VCC3

VCC3

VCC3

VCC3

VCC3

UsageDefault Status

Beep(reserve)

SUSACK#GP33

SUSWARN#

DPWROK

RSMRST#GP41

LED0

LED1

BOM detect

BOM detect

BOM detect

BOM detect

BOM detect

Default Status

GPIO

GPIOATX_3VSB

RSMRST#

PWROK2

GPIO3VSBSW_MINI

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

Update 20130520 Amos

Interrupt mapping

---------------------------------------------------------------------------------------------

Function

---------------------------------------------------------------------------------------------

LAN

PCIEX1

PCIEX1

B B

SATA

INT# port PCIe*1 port

INTC# port 7

INTD#

INTA#/B#

INTB#

port 6

port 8

NA

Device

RTL8111G or RTL8106E

LPT integrate

LPT integrate

LPT integrate

A A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

5

4

3

2

Date:

GPIO Function & INT# Mapping

GPIO Function & INT# Mapping

GPIO Function & INT# Mapping

Document Number

Document Number

Document Number

H81H3-MV

H81H3-MV

H81H3-MV

Sheet

Sheet

Sheet

1

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

332Monday, March 03, 2014

332Monday, March 03, 2014

332Monday, March 03, 2014

Page 4

5

4

3

2

1

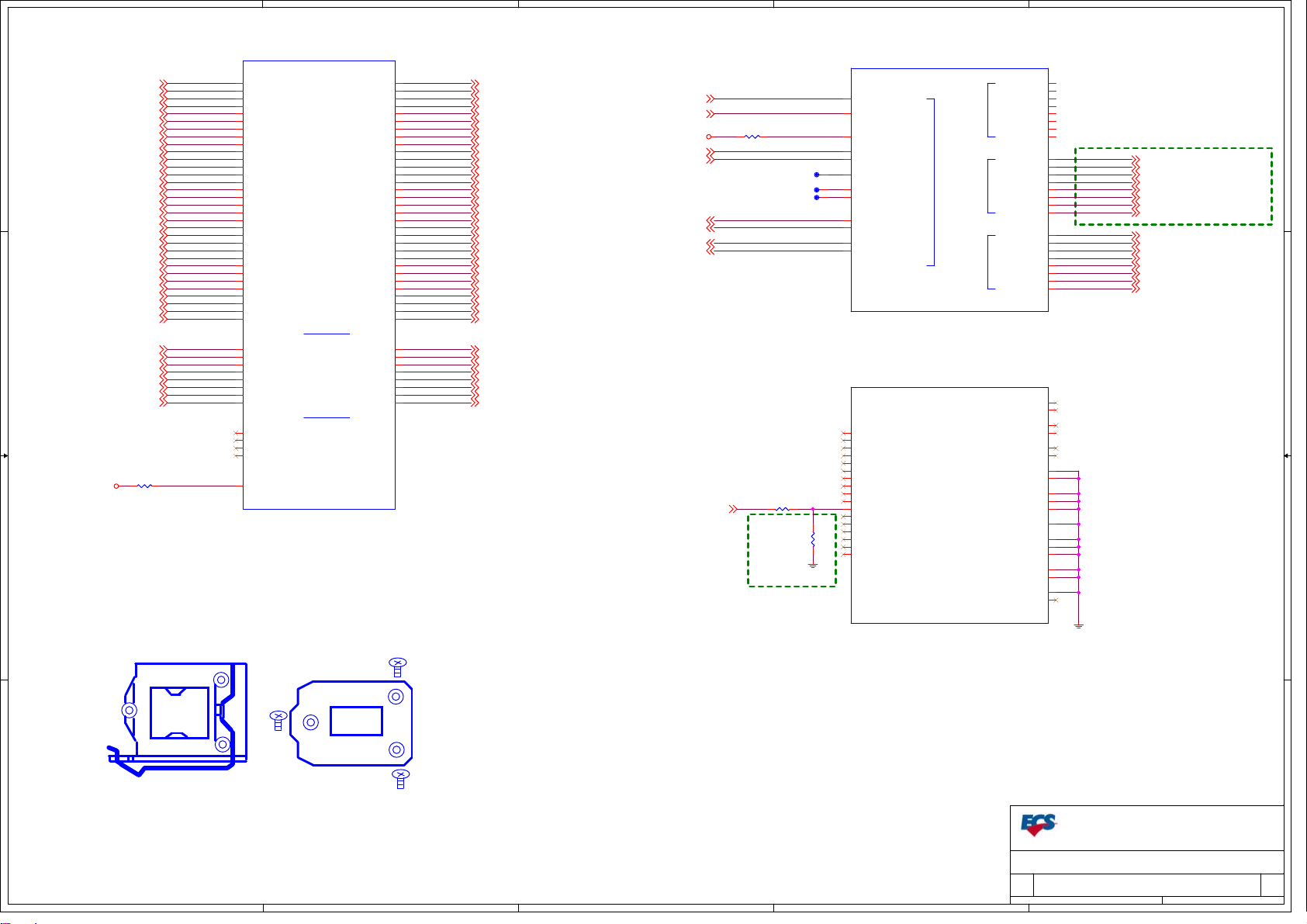

CPUC

PEG_RX_P021

PEG_RX_N021

PEG_RX_P121

PEG_RX_N121

PEG_RX_P221

D D

C C

VCOMP_OUT

B B

PEG_RX_N221

PEG_RX_P321

PEG_RX_N321

PEG_RX_P421

PEG_RX_N421

PEG_RX_P521

PEG_RX_N521

PEG_RX_P621

PEG_RX_N621

PEG_RX_P721

PEG_RX_N721

PEG_RX_P821

PEG_RX_N821

PEG_RX_P921

PEG_RX_N921

PEG_RX_P1021

PEG_RX_N1021

PEG_RX_P1121

PEG_RX_N1121

PEG_RX_P1221

PEG_RX_N1221

PEG_RX_P1321

PEG_RX_N1321

PEG_RX_P1421

PEG_RX_N1421

PEG_RX_P1521

PEG_RX_N1521

DMI_RX_P015

DMI_RX_N015

DMI_RX_P115

DMI_RX_N115

DMI_RX_P215

DMI_RX_N215

DMI_RX_P315

DMI_RX_N315

ER39 24.9-1-04

1 2

closetoCPU

PEG_RX_P0

PEG_RX_N0

PEG_RX_P1

PEG_RX_N1

PEG_RX_P2

PEG_RX_N2

PEG_RX_P3

PEG_RX_N3

PEG_RX_P4

PEG_RX_N4

PEG_RX_P5

PEG_RX_N5

PEG_RX_P6

PEG_RX_N6

PEG_RX_P7

PEG_RX_N7

PEG_RX_P8

PEG_RX_N8

PEG_RX_P9

PEG_RX_N9

PEG_RX_P10

PEG_RX_N10

PEG_RX_P11

PEG_RX_N11

PEG_RX_P12

PEG_RX_N12

PEG_RX_P13

PEG_RX_N13

PEG_RX_P14

PEG_RX_N14

PEG_RX_P15

PEG_RX_N15

DMI_RX_P0

DMI_RX_N0

DMI_RX_P1

DMI_RX_N1

DMI_RX_P2

DMI_RX_N2

DMI_RX_P3

DMI_RX_N3

PEG_RCOMP

CPU(104)

CPU_SUBASSY_STEEL(104)

E15

F15

D14

E14

E13

F13

D12

E12

E11

F11

F10

G10

E9

F9

F8

G8

D3

D4

E4

E5

F5

F6

G4

G5

H5

H6

J4

J5

K5

K6

L4

L5

U3

T3

U1

V1

W2

V2

Y3

W3

D1

C2

B3

A4

P3

PEG_RX[0]

PEG_RX#[0]

PEG_RX[1]

PEG_RX#[1]

PEG_RX[2]

PEG_RX#[2]

PEG_RX[3]

PEG_RX#[3]

PEG_RX[4]

PEG_RX#[4]

PEG_RX[5]

PEG_RX#[5]

PEG_RX[6]

PEG_RX#[6]

PEG_RX[7]

PEG_RX#[7]

PEG_RX[8]

PEG_RX#[8]

PEG_RX[9]

PEG_RX#[9]

PEG_RX[10]

PEG_RX#[10]

PEG_RX[11]

PEG_RX#[11]

PEG_RX[12]

PEG_RX#[12]

PEG_RX[13]

PEG_RX#[13]

PEG_RX[14]

PEG_RX#[14]

PEG_RX[15]

PEG_RX#[15]

DMI_RX[0]

DMI_RX#[0]

DMI_RX[1]

DMI_RX#[1]

DMI_RX[2]

DMI_RX#[2]

DMI_RX[3]

DMI_RX#[3]

RSVD_TP_D1

RSVD_TP_C2

RSVD_TP_B3

RSVD_TP_A4

PEG_RCOMP

HASWELL

REV = 1

3 OF 10

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[10]

PEG_TX#[10]

PEG_TX[11]

PEG_TX#[11]

PEG_TX[12]

PEG_TX#[12]

PEG_TX[13]

PEG_TX#[13]

PEG_TX[14]

PEG_TX#[14]

PEG_TX[15]

PEG_TX#[15]

DMI

GEN

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

DMI_TX[0]

DMI_TX#[0]

DMI_TX[1]

DMI_TX#[1]

DMI_TX[2]

DMI_TX#[2]

DMI_TX[3]

DMI_TX#[3]

HASWELL

A12

B12

B11

C11

C10

D10

B9

C9

C8

D8

B7

C7

A6

B6

B5

C5

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

M2

M3

L1

L2

AA4

AA5

AB3

AB4

AC5

AC4

AC1

AC2

PEG_TX_P0

PEG_TX_N0

PEG_TX_P1

PEG_TX_N1

PEG_TX_P2

PEG_TX_N2

PEG_TX_P3

PEG_TX_N3

PEG_TX_P4

PEG_TX_N4

PEG_TX_P5

PEG_TX_N5

PEG_TX_P6

PEG_TX_N6

PEG_TX_P7

PEG_TX_N7

PEG_TX_P8

PEG_TX_N8

PEG_TX_P9

PEG_TX_N9

PEG_TX_P10

PEG_TX_N10

PEG_TX_P11

PEG_TX_N11

PEG_TX_P12

PEG_TX_N12

PEG_TX_P13

PEG_TX_N13

PEG_TX_P14

PEG_TX_N14

PEG_TX_P15

PEG_TX_N15

DMI_TX_P0

DMI_TX_N0

DMI_TX_P1

DMI_TX_N1

DMI_TX_P2

DMI_TX_N2

DMI_TX_P3

DMI_TX_N3

PEG_TX_P0 21

PEG_TX_N0 21

PEG_TX_P1 21

PEG_TX_N1 21

PEG_TX_P2 21

PEG_TX_N2 21

PEG_TX_P3 21

PEG_TX_N3 21

PEG_TX_P4 21

PEG_TX_N4 21

PEG_TX_P5 21

PEG_TX_N5 21

PEG_TX_P6 21

PEG_TX_N6 21

PEG_TX_P7 21

PEG_TX_N7 21

PEG_TX_P8 21

PEG_TX_N8 21

PEG_TX_P9 21

PEG_TX_N9 21

PEG_TX_P10 21

PEG_TX_N10 21

PEG_TX_P11 21

PEG_TX_N11 21

PEG_TX_P12 21

PEG_TX_N12 21

PEG_TX_P13 21

PEG_TX_N13 21

PEG_TX_P14 21

PEG_TX_N14 21

PEG_TX_P15 21

PEG_TX_N15 21

DMI_TX_P0 15

DMI_TX_N0 15

DMI_TX_P1 15

DMI_TX_N1 15

DMI_TX_P2 15

DMI_TX_N2 15

DMI_TX_P3 15

DMI_TX_N3 15

FDI_CSYNC15

FDI_INT15

VCOMP_OUT

CK_DP_SSC_N16

CK_DP_SSC_P16

FDI_TX_N015

FDI_TX_P015

FDI_TX_N115

FDI_TX_P115

PCH_PWROK17,18,24

FDI_CSYNC

FDI_INT

ER38 24.9-1-04

1 2

FDI_TX_N0

FDI_TX_P0

FDI_TX_N1

FDI_TX_P1

change to 3.3k, voltage keep to 1.05

Devon 1109

DP_RCOMP

STP7

STP8

STP14

ER77

6.04K-1-04

ER78

3.3K-04

closetoCPU

12

12

GND

D16

FDI_CSYNC

D18

FDI_INT

R4

DP_COMP

U5

SSC_DPLL_REF_CLK#

U6

SSC_DPLL_REF_CLK

1

E16

EDP_DISP_UTIL

1

K11

RSVD_TP_K11

1

J12

RSVD_TP_J12

B14

FDI0_TX0#[0]

A14

FDI0_TX0[0]

C13

FDI0_TX0#[1]

B13

FDI0_TX0[1]

AY18

RSVD_AY18

AW24

RSVD_AW24

AW23

RSVD_AW23

AV29

RSVD_AV29

AV24

RSVD_AV24

AU39

RSVD_AU39

AU27

RSVD_AU27

AU1

RSVD_AU1

AT40

RSVD_AT40

AK20

RSVD_AK20

Y7

RSVD_Y7

T34

RSVD_T34

R34

RSVD_R34

J40

RSVD_J40

J17

RSVD_J17

J15

RSVD_J15

H12

RSVD_H12

CPUD

CPUH

REV = 1

HASWELL

REV = 1

FDI

4 OF 10

HASWELL

DDIB_TXB[0]

DDIB_TXB#[0]

DDIB_TXB[1]

DDIB_TXB#[1]

DDIB_TXB[2]

DDIB_TXB#[2]

DDIB

DDIB_TXB[3]

DDIB_TXB#[3]

DDIC_TXC[0]

DDIC_TXC#[0]

DDIC_TXC[1]

DDIC_TXC#[1]

DDIC_TXC[2]

DDIC_TXC#[2]

DDIC

DDIC_TXC[3]

DDIC_TXC#[3]

DDID_TXD[0]

DDID_TXD#[0]

DDID_TXD[1]

DDID_TXD#[1]

DDID_TXD[2]

DDID_TXD#[2]

DDID

DDID_TXD[3]

DDID_TXD#[3]

RSVD_TP_K12

RSVD_TP_J13

RSVD_TP_P37

RSVD_TP_N38

RSVD_TP_R36

RSVD_TP_C39

RSVD_TP_N36

HASWELL

VSS_U35

VSS_P40

VSS_R38

VSS_T37

VSS_V34

VSS_R39

VSS_T38

VSS_U36

VSS_P39

VSS_T36

VSS_R37

VSS_J14

8 OF 10

HASWELL

E17

F17

F18

G18

G19

H19

F20

G20

D19

E19

C20

D20

D21

E21

C22

D22

B15

C15

A16

B16

B17

C17

A18

B18

K12

J13

P37

N38

R36

C39

U35

P40

R38

T37

V34

R39

T38

U36

P39

T36

R37

J14

N36

HDMI_TXP2

HDMI_TXN2

HDMI_TXP1

HDMI_TXN1

HDMI_TXP0

HDMI_TXN0

HDMI_TXCP

HDMI_TXCN

DDPD_TX2

DDPD_TX2DDPD_TX1

DDPD_TX1DDPD_TX0

DDPD_TX0DDPD_TXC

DDPD_TXC-

GND

HDMI_TXP2 22

HDMI_TXN2 22

HDMI_TXP1 22

HDMI_TXN1 22

HDMI_TXP0 22

HDMI_TXN0 22

HDMI_TXCP 22

HDMI_TXCN 22

DDPD_TX2 22

DDPD_TX2- 22

DDPD_TX1 22

DDPD_TX1- 22

DDPD_TX0 22

DDPD_TX0- 22

DDPD_TXC 22

DDPD_TXC- 22

HDMI

Devon 1102

DVI

A A

CPU steel (T/U pahse)

PN:20-800-005711 CPU SOCKET STEEL SUBASSY.STEEL....LGA 1155/1156P.W/BACK PLATE,CAP.LOTES

CPU socket (SMD phase)

PN:11-018-115128 SOCKET.CPU..LGA 1150P SMD..15u...BLACK.ACA-ZIF-138-P01...HF.LEAD-FREE.LOTES

5

4

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

3

2

Date:

CPU-PEG/DMI/FDI/DDI

CPU-PEG/DMI/FDI/DDI

CPU-PEG/DMI/FDI/DDI

Document Number

Document Number

Document Number

H81H3-MV

H81H3-MV

H81H3-MV

Sheet

Sheet

Sheet

1

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

432Monday, March 03, 2014

432Monday, March 03, 2014

432Monday, March 03, 2014

Page 5

5

4

3

2

1

CPUE

V4

BCLK#

V5

BCLK

C38

VIDSCLK

C37

VIDSOUT

B37

VIDALERT

AK21

SM_DRAMPWROK

AB35

PWRGOOD

M39

RESET

P36

PM_SYNC

N37

PECI

M36

CATERR

K38

PROCHOT

F37

THERMTRIP

D38

SKTOCC

AB38

SM_VREF

AA37

CFG[0]

Y38

CFG[1]

AA36

CFG[2]

W38

CFG[3]

V39

CFG[4]

U39

CFG[5]

U40

CFG[6]

V38

CFG[7]

T40

CFG[8]

Y35

CFG[9]

AA34

CFG[10]

V37

CFG[11]

Y34

CFG[12]

U38

CFG[13]

W34

CFG[14]

V35

CFG[15]

Y36

CFG[17]

Y37

CFG[16]

V36

CFG[19]

W36

CFG[18]

D39

TCK

F38

TDI

F39

TDO

E39

TMS

E37

TRST

L39

PRDY

L37

PREQ

G40

DBR

N5

TESTLO_N5

K8

RSVD_K8

J10

RSVD_J10

CFG_[0..17] HAVE INTERNAL PULL-UPS

PCIE CONFIG

*

1 X 16

2 X 8

Reserved

X8,X4,X4

CFG6

GND

1 2

1 2

1 2

1 2

CK_DMI_100M_N

CK_DMI_100M_P

VR_SVID_CK

VR_SVID_DOUT

VID_ALERT_L_R

DRAM_PWROK

CPU_PWROK

CPU_PLTRST_L

PM_SYNC

SIO_PECI

1

VR_HOT_L

PCH_THERMTRIP_L

H_SKTOCC_L

DIMM_VREF_CPU

1

CFG0

1

CFG1

1

CFG2

1

CFG3

1

CFG4

CFG5

CFG6

1

CFG7

1

CFG8

1

CFG9

1

CFG10

1

CFG11

1

CFG12

CFG13

1

CFG14

1

CFG15

1

CFG17

1

CFG16

1

CFG19

1

CFG18

H_TCK

H_TDI

1

H_TDO

H_TMS

H_TRST_L

1

H_PRDY_L

1

H_PREQ_L

FP_RST_L_R

ER33 49.9-1-04

1 2

H_TDI

H_TMS

H_TCK

H_TRST_L

CK_DMI_100M_N16

CK_DMI_100M_P16

VR_SVID_CK11

VR_SVID_DATAOUT11

VR_SVID_ALERT_L11

D D

DIMM_VREF_CA_A8,10

DIMM_VREF_CA_B9,10

C92

R136

12

2 1

DIMM_VREF_CPU

.022U-16VX7-04

24.9-1-04

GND

V_1P05_PCH

R223 1K-04

1 2

GND

SLP_S3_L13,18,24

2 1

2 1

R120 10K-04

1 2

2 1

C C

B B

A A

.1U-16VX-04C80

.1U-16VX-04C54

.1U-16VX-04-OC68

R175

10K-04

1 2

PCH_THERMTRIP_L

DRAM_PWROK

CPU_PLTRST_L

CPU_PWROK

3VSB

1 2

B

E C

GND

CPU_THERMTRIP_LchangePCH_THERMTRIP_L

R155

10K-04

QN13

2N3904-S

R154

1K-04

1 2

R168

1K-04

1 2

R158

1K-04-O

1 2

B

QN9

2N3904-S

E C

GND GND

R164 100-04

B

QN11

2N3904-S

E C

GND

R157 100-04-O

B

QN10

2N3904-S-O

E C

GND

1 2

1 2

VR_SVID_ALERT_L

t9/L 只接{Lhٍ t9/I أ t/I 端59[9Ç9

DIMM_VREF_CA_A

DIMM_VREF_CA_B

HSW_STRAP_CFG1318

VR_EN 11

21

C98

1U-6.3VX-04-O

VR_READY 11,18

CPU_PWROK 5,18

FP_RST_L18,28

1 2

R84 44.2-1-04

DRAM_PWROK18

CPU_PWROK5,18

CPU_PLTRST_L17

PM_SYNC17

SIO_PECI24

VR_HOT_L11

PCH_THERMTRIP_L17

H_SKTOCC_L24

1 2

R137 0-04

1 2

R138 0-04

R104 1K-04-O

1 2

1 2

R105 1K-04-O

GND

R103 1K-04-O

1 2

R98

1 2

0-04

VCCIO_OUT

GND

STP12

TP17

TP10

TP14

TP9

TP6

TP7

TP4

TP11

TP13

TP5

TP8

TP12

TP15

TP16

TP18

TP19

TP20

TP3

STP11

STP13

R90 51-04-O

R92 51-04-O

R91 51-04

R97 51-04

Power Down Sequencing Circuit

5

4

3

HASWELL

5 OF 10

CFG5

11

0

1

01

0

0

REV = 1

G39

BPM#[0]

J39

BPM#[1]

G38

BPM#[2]

H37

BPM#[3]

H38

BPM#[4]

J38

BPM#[5]

K39

BPM#[6]

K37

BPM#[7]

T35

RSVD_T35

M38

RSVD_M38

RSVD_K9

RSVD_H15

RSVD_J9

RSVD_H14

VCC_M8

RSVD_AV2

RSVD_J16

RSVD_H16

VSS_N39

VSS_V7

VSS_AB6

RSVD_AC8

RSVD_U8

RSVD_T8

RSVD_Y8

RSVD_M10

RSVD_L10

RSVD_M11

RSVD_L12

RSVD_W8

RSVD_R33

RSVD_P33

VSS_N33

VSS_J11

VSS_M9

VSS_J7

RSVD_N35

HASWELL

2

P6

K9

H15

J9

H14

M8

AV2

J16

H16

N40

PWR_DEBUG

N39

V7

AB6

K13

J8

R1

P1

R2

AB36

AW2

AV1

AC8

P4

U8

AB33

T8

Y8

M10

L10

M11

L12

W8

R33

P33

E40

VCORE_VCC_SEN

N33

J11

M9

J7

F40

VCORE_VSS_SEN

N35

W6

CK_DP_NSSC_N

W5

CK_DP_NSSC_P

H40

TESTLO_P6

PWR_DEBUG

RSVD_TP_K13

RSVD_TP_J8

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

RSVD_AB36

RSVD_TP_AW2

RSVD_TP_AV1

VCOMP_OUT

RSVD_AB33

VCC_SENSE

VSS_SENSE

DPLL_REF_CLK#

DPLL_REF_CLK

CFG_RCOMP

CFG[1:0]: Reserved configuration lane.

CFG[2]: PCI Express* Static x16 Lane Numbering Reversal.

1 = Normal operation

0 = Lane numbers reversed.

CFG[3]: MSR Privacy Bit Feature

1 = Debug capability is determined by

IA32_Debug_Interface_MSR (0xC80) bit[0]

0 = IA32_Debug_Interface_MSR (0xC80) bit[0]

default setting overridden

CFG[4]: Reserved configuration lane.

CFG[6:5]: PCI Express* Bifurcation:

CFG[19:7]: Reserved configuration lanes.

1

H_BPM0_L

H_BPM1_L

ER37 49.9-1-04

R124 0-04

R129 0-04

ER34 100-1-04

ER36 75-1-04

ER35 100-1-04

1

R106 0-04-O

ER32 49.9-1-04

closetoCPU

1

1

1

1

1

1

1

12

R101 150-1-04

closetoCPU

STP16

1 2

12

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

Date:

STP4

STP1

STP6

STP5

STP3

STP2

STP10

STP9

12

12

12

12

12

12

VCORE_VCC_SEN 11

VCORE_VSS_SEN 11

CK_DP_NSSC_N 16

CK_DP_NSSC_P 16

Document Number

Document Number

Document Number

GND

VCCST

VCORE

V_1P05_PCH

GND

GND

VCOMP_OUT

GND

V_1P05_PCH

GND

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

CPU-MISC

CPU-MISC

CPU-MISC

H81H3-MV

H81H3-MV

H81H3-MV

Rev

Rev

Rev

1.0

1.0

1.0

of

of

Sheet

Sheet

Sheet

1

of

532Monday, March 03, 2014

532Monday, March 03, 2014

532Monday, March 03, 2014

Page 6

5

4

3

2

1

HASWELL

REV = 1

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_ECC_CB[0]

SA_ECC_CB[1]

SA_ECC_CB[2]

SA_ECC_CB[3]

SA_ECC_CB[4]

SA_ECC_CB[5]

SA_ECC_CB[6]

SA_ECC_CB[7]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CKE[0]

SA_CKE[1]

SA_CKE[2]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_CK[0]

SA_CK#[0]

SA_CK[1]

SA_CK#[1]

SA_CK[2]

SA_CK#[2]

SA_CK[3]

SA_CK#[3]

RSVD_AW12

SA_RAS

SA_WE

RSVD_AV20

RSVD_AW27

SA_CAS

SM_DRAMRST

1 OF 10

HASWELL

AU13

AV16

AU16

AW17

AU17

AW18

AV17

AT18

AU18

AT19

AW11

AV19

AU19

AY10

AT20

AU21

AW10

AY8

AW9

AU8

AW33

AV33

AU31

AV31

AT33

AU33

AT31

AW31

AV12

AY11

AT21

AV22

AT23

AU22

AU23

AU14

AV9

AU10

AW8

AY15

AY16

AW15

AV15

AV14

AW14

AW13

AY13

AW12

AU12

AU11

AV20

AW27

AU9

AK22

M_MA_A0

M_MA_A1

M_MA_A2

M_MA_A3

M_MA_A4

M_MA_A5

M_MA_A6

M_MA_A7

M_MA_A8

M_MA_A9

M_MA_A10

M_MA_A11

M_MA_A12

M_MA_A13

M_MA_A14

M_MA_A15

M_ODT_A2

M_ODT_A3

M_BS_A0

M_BS_A1

M_BS_A2

M_CKE_A2

M_CKE_A3

M_CS_A_L2

M_CS_A_L3

M_CLK_A_P2

M_CLK_A_N2

M_CLK_A_P3

M_CLK_A_N3

1

TP23

M_RAS_A_L

M_WE_A_L

1

TP21

1

TP22

M_CAS_A_L

DDR3_DRAMRST_L

21

C136

.1U-16VX-04-O

closetoDIMMslot

GND

Devon 1102

Devon 1103

NC M_ODT_B[0..1],M_CKE_B[0..1],M_CS_B_L[0..1],M_CLK_B_P[0..1],M_CLK_B_N[0..1]

Devon 20121016

External Connection

D D

C C

B B

M_DATA_A[0..63]8

M_DQS_A_P[0..7]8

M_DQS_A_N[0..7]8

M_MA_A[0..15]8

M_BS_A[0..2]8

M_CS_A_L[2..3]8

M_CKE_A[2..3]8

M_ODT_A[2..3]8

M_CLK_A_P[2..3]8

M_CLK_A_N[2..3]8

DIMM_DQ_CPU_VREF_A10

DDR3 CH.A

M_DATA_B[0..63]9

M_DQS_B_P[0..7]9

M_DQS_B_N[0..7]9

M_MA_B[0..15]9

M_BS_B[0..2]9

M_CS_B_L[2..3]9

M_CKE_B[2..3]9

M_ODT_B[2..3]9

M_CLK_B_P[2..3]9

M_CLK_B_N[2..3]9

DIMM_DQ_CPU_VREF_B10

M_WE_A_L8

M_CAS_A_L8

M_RAS_A_L8

M_WE_B_L9

M_CAS_B_L9

M_RAS_B_L9

DDR3 CH.B

DDR3_DRAMRST_L8,9

NC M_ODT_A[0..1],M_CKE_A[0..1],M_CS_A_L[0..1],M_CLK_A_P[0..1],M_CLK_A_N[0..1]

A A

Devon 20121016

M_DATA_A[0..63]

M_DQS_A_P[0..7]

M_DQS_A_N[0..7]

M_MA_A[0..15]

M_BS_A[0..2]

M_CS_A_L[2..3]

M_CKE_A[2..3]

M_ODT_A[2..3]

M_CLK_A_P[2..3]

M_CLK_A_N[2..3]

DIMM_DQ_CPU_VREF_A

M_WE_A_L

M_CAS_A_L

M_RAS_A_L

M_DATA_B[0..63]

M_DQS_B_P[0..7]

M_DQS_B_N[0..7]

M_MA_B[0..15]

M_BS_B[0..2]

M_CS_B_L[2..3]

M_CKE_B[2..3]

M_ODT_B[2..3]

M_CLK_B_P[2..3]

M_CLK_B_N[2..3]

DIMM_DQ_CPU_VREF_B

M_WE_B_L

M_CAS_B_L

M_RAS_B_L

DDR3_DRAMRST_L

Devon 1102

Devon 1103

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A9

M_DATA_A13

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A8

M_DATA_A14

M_DATA_A15

M_DATA_A17

M_DATA_A21

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A16

M_DATA_A22

M_DATA_A23

M_DATA_A25

M_DATA_A29

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A24

M_DATA_A30

M_DATA_A31

M_DATA_A33

M_DATA_A37

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A32

M_DATA_A38

M_DATA_A39

M_DATA_A41

M_DATA_A45

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A40

M_DATA_A46

M_DATA_A47

M_DATA_A49

M_DATA_A53

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A48

M_DATA_A54

M_DATA_A55

M_DATA_A57

M_DATA_A61

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A56

M_DATA_A62

M_DATA_A63

M_DQS_A_P0

M_DQS_A_P1

M_DQS_A_P2

M_DQS_A_P3

M_DQS_A_P4

M_DQS_A_P5

M_DQS_A_P6

M_DQS_A_P7

M_DQS_A_N0

M_DQS_A_N1

M_DQS_A_N2

M_DQS_A_N3

M_DQS_A_N4

M_DQS_A_N5

M_DQS_A_N6

M_DQS_A_N7

AD38

AD39

AF38

AF39

AD37

AD40

AF37

AF40

AH40

AH39

AK38

AK39

AH37

AH38

AK37

AK40

AM40

AM39

AP38

AP39

AM37

AM38

AP37

AP40

AV37

AW37

AU35

AV35

AT37

AU37

AT35

AW35

AY6

AU6

AV4

AU4

AW6

AV6

AW4

AY4

AR1

AR4

AN3

AN4

AR2

AR3

AN2

AN1

AL1

AL4

AL2

AL3

AG1

AG4

AE3

AE4

AG2

AG3

AE2

AE1

AE39

AJ39

AN39

AV36

AV5

AP3

AK3

AF3

AV32

AE38

AJ38

AN38

AU36

AW5

AP2

AK2

AF2

AU32

AJ3

AJ4

AJ2

AJ1

CPUA

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_DQS[8]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS#[8]

**Attention**Attention

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B17

M_DATA_B21

M_DATA_B19

M_DATA_B23

M_DATA_B20

M_DATA_B16

M_DATA_B18

M_DATA_B22

M_DATA_B25

M_DATA_B28

M_DATA_B27

M_DATA_B30

M_DATA_B24

M_DATA_B29

M_DATA_B26

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B45

M_DATA_B41

M_DATA_B47

M_DATA_B43

M_DATA_B44

M_DATA_B40

M_DATA_B46

M_DATA_B42

M_DATA_B52

M_DATA_B53

M_DATA_B50

M_DATA_B55

M_DATA_B48

M_DATA_B49

M_DATA_B54

M_DATA_B51

M_DATA_B61

M_DATA_B60

M_DATA_B59

M_DATA_B63

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B62

M_DQS_B_P0

M_DQS_B_P1

M_DQS_B_P2

M_DQS_B_P3

M_DQS_B_P4

M_DQS_B_P5

M_DQS_B_P6

M_DQS_B_P7

M_DQS_B_N0

M_DQS_B_N1

M_DQS_B_N2

M_DQS_B_N3

M_DQS_B_N4

M_DQS_B_N5

M_DQS_B_N6

M_DQS_B_N7

AE34

AE35

AG35

AH35

AD34

AD35

AG34

AH34

AL34

AL35

AK31

AL31

AK34

AK35

AK32

AL32

AN34

AP34

AN31

AP31

AN35

AP35

AN32

AP32

AM29

AM28

AR29

AR28

AL29

AL28

AP29

AP28

AR12

AP12

AL13

AL12

AR13

AP13

AM13

AM12

AR9

AP9

AR6

AP6

AR10

AP10

AR7

AP7

AM9

AL9

AL6

AL7

AM10

AL10

AM6

AM7

AH6

AH7

AE6

AE7

AJ6

AJ7

AF6

AF7

AF35

AL33

AP33

AN28

AN12

AP8

AL8

AG7

AN25

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AN26

CPUB

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_DQS[8]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS#[8]

HASWELL

REV = 1

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_ECC_CB[0]

SB_ECC_CB[1]

SB_ECC_CB[2]

SB_ECC_CB[3]

SB_ECC_CB[4]

SB_ECC_CB[5]

SB_ECC_CB[6]

SB_ECC_CB[7]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CKE[0]

SB_CKE[1]

SB_CKE[2]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_CK[0]

SB_CK#[0]

SB_CK[1]

SB_CK#[1]

SB_CK[2]

SB_CK#[2]

SB_CK[3]

SB_CK#[3]

SB_CAS

RSVD_AL20

SB_RAS

SB_WE

2 OF 10

HASWELL

AL19

M_MA_B0

AK23

M_MA_B1

AM22

M_MA_B2

AM23

M_MA_B3

AP23

M_MA_B4

AL23

M_MA_B5

AY24

M_MA_B6

AV25

M_MA_B7

AU26

M_MA_B8

AW25

M_MA_B9

AP18

M_MA_B10

AY25

M_MA_B11

AV26

M_MA_B12

AR15

M_MA_B13

AV27

M_MA_B14

AY28

M_MA_B15

AM17

AL16

AM16

M_ODT_B2

AK15

M_ODT_B3

AM26

AM25

AP25

AP26

AL26

AL25

AR26

AR25

AK17

M_BS_B0

AL18

M_BS_B1

AW28

M_BS_B2

AW29

AY29

AU28

M_CKE_B2

AU29

M_CKE_B3

AP17

AN15

AN17

M_CS_B_L2

AL15

M_CS_B_L3

AM20

AM21

AP22

AP21

AN20

M_CLK_B_P2

AN21

M_CLK_B_N2

AP19

M_CLK_B_P3

AP20

M_CLK_B_N3

AP16

M_CAS_B_L

1

AL20

AM18

M_RAS_B_L

AK16

M_WE_B_L

AB39

DIMM_DQ_CPU_VREF_A

AB40

DIMM_DQ_CPU_VREF_B

STP18

C81

.022U-16VX7-04

ER58

24.9-1-04

Devon 1103

Devon 1104

21

C82

.022U-16VX7-04

ER64

24.9-1-04

1 2

GND GND

21

1 2

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Document Number

Document Number

Document Number

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

5

4

3

2

Date:

CPU-DDR3

CPU-DDR3

CPU-DDR3

H81H3-MV

H81H3-MV

H81H3-MV

1

Sheet

Sheet

Sheet

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

632Monday, March 03, 2014

632Monday, March 03, 2014

632Monday, March 03, 2014

Page 7

5

VCCIO_OUT

GND

VCORE

R132 0-04-O

C95

10U-6.3VX-06-O

21

C72

10U-6.3VX-06

21

C61

10U-6.3VX-06

21

C71

10U-6.3VX-06-O

C53

10U-6.3VX-06

12

21

C62

10U-6.3VX-06

21

C60

10U-6.3VX-06

21

C58

10U-6.3VX-06-O

R150 0-04

V_1P05_PCH

VCCST

D D

C C

B B

VCORE

VCORE

A A

VCORE

12

21

C93

.1U-16VX-04-O

GND GND

21

C76

10U-6.3VX-06

21

C74

10U-6.3VX-06

21

C49

10U-6.3VX-06-O

P8

L40

AB8

L31

L18

L17

J33

A24

A25

A26

A27

A28

A29

A30

G33

B25

B27

B29

B31

J31

B33

G31

B35

C24

C25

C26

C27

C28

C29

C30

C32

C34

C35

D25

D27

D29

D31

E33

D33

E31

D35

E24

E25

E26

E27

E28

E29

E30

E32

E34

F23

F25

F27

F29

F31

E35

F33

F35

G22

G23

G24

G25

G26

G27

G28

G29

G30

G32

G34

G35

H23

H25

H27

H29

H31

L34

CPUF

VCC_P8

VCCIO_OUT

VCCIO2PCH

VCC_L31

VCC_L18

VCC_L17

VCC_J33

VCC_A24

VCC_A25

VCC_A26

VCC_A27

VCC_A28

VCC_A29

VCC_A30

VCC_G33

VCC_B25

VCC_B27

VCC_B29

VCC_B31

VCC_J31

VCC_B33

VCC_G31

VCC_B35

VCC_C24

VCC_C25

VCC_C26

VCC_C27

VCC_C28

VCC_C29

VCC_C30

VCC_C32

VCC_C34

VCC_C35

VCC_D25

VCC_D27

VCC_D29

VCC_D31

VCC_E33

VCC_D33

VCC_E31

VCC_D35

VCC_E24

VCC_E25

VCC_E26

VCC_E27

VCC_E28

VCC_E29

VCC_E30

VCC_E32

VCC_E34

VCC_F23

VCC_F25

VCC_F27

VCC_F29

VCC_F31

VCC_E35

VCC_F33

VCC_F35

VCC_G22

VCC_G23

VCC_G24

VCC_G25

VCC_G26

VCC_G27

VCC_G28

VCC_G29

VCC_G30

VCC_G32

VCC_G34

VCC_G35

VCC_H23

VCC_H25

VCC_H27

VCC_H29

VCC_H31

VCC_L34

21

C57

10U-6.3VX-06

21

C73

10U-6.3VX-06

21

C50

10U-6.3VX-06-O

HASWELL

REV = 1

21

C77

10U-6.3VX-06

21

C59

10U-6.3VX-06

21

C51

10U-6.3VX-06-O

6 OF 10

placecapsinCPUsocketcavity

5

VCC_C31

VCC_C33

VCC_L16

VCC_L15

VCC_J35

VCC_H33

VCC_H35

VCC_J21

VCC_J22

VCC_J23

VCC_J24

VCC_J25

VCC_J26

VCC_J27

VCC_J28

VCC_J29

VCC_J30

VCC_J32

VCC_J34

VCC_K19

VCC_K21

VCC_K23

VCC_K25

VCC_K27

VCC_K29

VCC_K31

VCC_M13

VCC_K33

VCC_K35

VCC_L19

VCC_L20

VCC_L21

VCC_L22

VCC_L23

VCC_L24

VCC_L25

VCC_L26

VCC_L27

VCC_L28

VCC_L29

VCC_L30

VCC_L32

VCC_L33

VCC_M17

VCC_M15

VCC_M19

VCC_M21

VCC_M23

VCC_M25

VCC_M27

VCC_M29

VCC_M33

VDDQ_AJ12

VDDQ_AJ13

VDDQ_AJ15

VDDQ_AJ17

VDDQ_AJ20

VDDQ_AJ21

VDDQ_AJ24

VDDQ_AJ25

VDDQ_AJ28

VDDQ_AJ29

VDDQ_AJ9

VDDQ_AT17

VDDQ_AT22

VDDQ_AU15

VDDQ_AU20

VDDQ_AU24

VDDQ_AV10

VDDQ_AV11

VDDQ_AV13

VDDQ_AV18

VDDQ_AV23

VDDQ_AV8

VDDQ_AW16

VDDQ_AY12

VDDQ_AY14

VDDQ_AY9

HASWELL

21

C78

10U-6.3VX-06

GND

21

C56

10U-6.3VX-06

GND

21

C64

10U-6.3VX-06-O

GND

4

VCORE

C31

C33

L16

L15

J35

H33

H35

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J32

J34

K19

K21

K23

K25

K27

K29

K31

M13

K33

K35

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

L32

L33

M17

M15

M19

M21

M23

M25

M27

VDIMM

M29

M33

AJ12

AJ13

AJ15

AJ17

AJ20

AJ21

AJ24

AJ25

AJ28

AJ29

AJ9

AT17

AT22

AU15

AU20

AU24

AV10

AV11

AV13

AV18

AV23

AV8

AW16

AY12

AY14

AY9

VDIMM

21

C90

10U-6.3VX-06

VDIMM

21

C84

10U-6.3VX-06

4

CPUG

AP11

VSS_AP11

AP14

VSS_AP14

AP15

VSS_AP15

AP24

VSS_AP24

AP27

VSS_AP27

AP30

VSS_AP30

AP36

VSS_AP36

AP4

VSS_AP4

AP5

VSS_AP5

AR11

VSS_AR11

AR14

VSS_AR14

AR16

VSS_AR16

AR17

VSS_AR17

AR18

VSS_AR18

AR19

VSS_AR19

AR20

VSS_AR20

AR21

VSS_AR21

AR22

VSS_AR22

AR23

VSS_AR23

AR24

VSS_AR24

AR27

VSS_AR27

AR30

VSS_AR30

AR31

VSS_AR31

AR32

VSS_AR32

AR33

VSS_AR33

AR34

VSS_AR34

AR35

VSS_AR35

AR36

VSS_AR36

AR37

VSS_AR37

AR38

VSS_AR38

AR39

VSS_AR39

AR40

VSS_AR40

AR5

VSS_AR5

AT1

VSS_AT1

AT10

VSS_AT10

AT11

VSS_AT11

AT12

VSS_AT12

AT13

VSS_AT13

AT14

VSS_AT14

AT15

VSS_AT15

AT16

VSS_AT16

AT2

VSS_AT2

AT24

VSS_AT24

AT25

VSS_AT25

AT26

VSS_AT26

AT27

VSS_AT27

AT28

VSS_AT28

AT29

VSS_AT29

AT3

VSS_AT3

AT30

VSS_AT30

AT32

VSS_AT32

AT34

VSS_AT34

AT36

VSS_AT36

AT38

VSS_AT38

AT39

VSS_AT39

AT4

VSS_AT4

AT5

VSS_AT5

AT6

VSS_AT6

AT7

VSS_AT7

AT8

VSS_AT8

AT9

VSS_AT9

AU2

VSS_AU2

AU25

VSS_AU25

AU3

VSS_AU3

AU30

VSS_AU30

AU34

VSS_AU34

AU38

VSS_AU38

AU5

VSS_AU5

AU7

VSS_AU7

AV21

VSS_AV21

AV28

VSS_AV28

AV3

VSS_AV3

AV30

VSS_AV30

AV34

VSS_AV34

AV38

VSS_AV38

AV7

VSS_AV7

AW26

VSS_AW26

AW3

VSS_AW3

AW30

VSS_AW30

GND GND

21

C88

10U-6.3VX-06

21

C89

10U-6.3VX-06

HASWELL

REV = 1

21

C85

10U-6.3VX-06

21

C91

10U-6.3VX-06

VSS_AW32

VSS_AW34

VSS_AW36

VSS_AY17

VSS_AY23

VSS_AY26

VSS_AY27

VSS_AY30

7 OF 10

HASWELL

GND

VSS_AW7

VSS_AY5

VSS_AY7

VSS_B24

VSS_B26

VSS_B28

VSS_B30

VSS_B34

VSS_B36

VSS_B4

VSS_B8

VSS_C4

VSS_C6

VSS_C12

VSS_C14

VSS_C16

VSS_C18

VSS_C19

VSS_C21

VSS_C23

VSS_C36

VSS_B10

VSS_B23

VSS_C3

VSS_D9

VSS_D11

VSS_D13

VSS_D15

VSS_D17

VSS_D2

VSS_D23

VSS_D24

VSS_D26

VSS_D28

VSS_D30

VSS_D34

VSS_D36

VSS_D37

VSS_D5

VSS_D6

VSS_D7

VSS_E7

VSS_E8

VSS_E10

VSS_E18

VSS_E3

VSS_E20

VSS_E22

VSS_E23

VSS_E36

VSS_E38

VSS_B32

VSS_E6

VSS_F1

VSS_F32

VSS_F12

VSS_F14

VSS_F16

VSS_F19

VSS_F21

VSS_F22

VSS_F24

VSS_F26

VSS_F28

VSS_F30

VSS_F34

VSS_F36

VSS_F4

VSS_D32

VSS_F7

VSS_G9

VSS_G11

21

C87

10U-6.3VX-06

21

C83

10U-6.3VX-06

3

HASWELL

AW32

AW34

AW36

AW7

AY17

AY23

AY26

AY27

AY30

AY5

AY7

B24

B26

B28

B30

B34

B36

B4

B8

C4

C6

C12

C14

C16

C18

C19

C21

C23

C36

B10

B23

C3

D9

D11

D13

D15

D17

D2

D23

D24

D26

D28

D30

D34

D36

D37

D5

D6

D7

E7

E8

E10

E18

E3

E20

E22

E23

E36

E38

B32

E6

F1

F32

F12

F14

F16

F19

F21

F22

F24

F26

F28

F30

F34

F36

F4

D32

F7

G9

G11

GND GND

21

C86

10U-6.3VX-06

GND

3

CPUI

A5

VSS_A5

A7

VSS_A7

A11

VSS_A11

A13

VSS_A13

A15

VSS_A15

A17

VSS_A17

A23

VSS_A23

AA3

VSS_AA3

AA6

VSS_AA6

AA7

VSS_AA7

AA8

VSS_AA8

AA33

VSS_AA33

AA35

VSS_AA35

AA38

VSS_AA38

AB5

VSS_AB5

AB7

VSS_AB7

AB34

VSS_AB34

AB37

VSS_AB37

AC3

VSS_AC3

AC6

VSS_AC6

AC7

VSS_AC7

AC33

VSS_AC33

AC34

VSS_AC34

AC35

VSS_AC35

AC36

VSS_AC36

AC37

VSS_AC37

AC38

VSS_AC38

AC39

VSS_AC39

AC40

VSS_AC40

AD1

VSS_AD1

AD2

VSS_AD2

AD3

VSS_AD3

AD4

VSS_AD4

AD5

VSS_AD5

AD6

VSS_AD6

AD7

VSS_AD7

AD8

VSS_AD8

AD33

VSS_AD33

AD36

VSS_AD36

AE5

VSS_AE5

AE8

VSS_AE8

AE33

VSS_AE33

AE36

VSS_AE36

AE37

VSS_AE37

AE40

VSS_AE40

AF1

VSS_AF1

AF4

VSS_AF4

AF5

VSS_AF5

AF8

VSS_AF8

AF33

VSS_AF33

AF36

VSS_AF36

AG5

VSS_AG5

AG8

VSS_AG8

AG33

VSS_AG33

AG36

VSS_AG36

AG37

VSS_AG37

AG38

VSS_AG38

AG39

VSS_AG39

AG40

VSS_AG40

AH1

VSS_AH1

AH2

VSS_AH2

AH3

VSS_AH3

AH4

VSS_AH4

AH5

VSS_AH5

AH8

VSS_AH8

AH33

VSS_AH33

AH36

VSS_AH36

AJ11

VSS_AJ11

AJ14

VSS_AJ14

AJ16

VSS_AJ16

AJ18

VSS_AJ18

AJ19

VSS_AJ19

AJ22

VSS_AJ22

AJ23

VSS_AJ23

AJ26

VSS_AJ26

AJ27

VSS_AJ27

AJ30

VSS_AJ30

AJ31

VSS_AJ31

AJ32

VSS_AJ32

AJ33

VSS_AJ33

VCORE

21

C52

10U-6.3VX-06

21

placecapsattopCPUsocketedge

REV = 1

9 OF 10

C75

10U-6.3VX-06

VSS_AJ34

VSS_AJ35

VSS_AJ36

VSS_AJ37

VSS_AJ40

VSS_AK10

VSS_AK11

VSS_AK12

VSS_AK13

VSS_AK14

VSS_AK18

VSS_AK19

VSS_AK24

VSS_AK25

VSS_AK26

VSS_AK27

VSS_AK28

VSS_AK29

VSS_AK30

VSS_AK36

VSS_AL11

VSS_AL14

VSS_AL17

VSS_AL21

VSS_AL22

VSS_AL24

VSS_AL27

VSS_AL30

VSS_AL36

VSS_AL37

VSS_AL38

VSS_AL39

VSS_AL40

VSS_AM11

VSS_AM14

VSS_AM15

VSS_AM19

VSS_AM24

VSS_AM27

VSS_AM30

VSS_AM31

VSS_AM32

VSS_AM33

VSS_AM34

VSS_AM35

VSS_AM36

VSS_AN10

VSS_AN11

VSS_AN14

VSS_AN16

VSS_AN18

VSS_AN19

VSS_AN22

VSS_AN23

VSS_AN24

VSS_AN27

VSS_AN30

VSS_AN36

VSS_AN37

VSS_AN40

HASWELL

21

2

VSS_AJ5

VSS_AJ8

VSS_AK1

VSS_AK4

VSS_AK5

VSS_AK6

VSS_AK7

VSS_AK8

VSS_AK9

VSS_AL5

VSS_AM1

VSS_AM2

VSS_AM3

VSS_AM4

VSS_AM5

VSS_AN5

VSS_AN6

VSS_AN7

VSS_AN8

VSS_AN9

VSS_AP1

C63

10U-6.3VX-06

2

AJ5

AJ8

AJ34

AJ35

AJ36

AJ37

AJ40

AK1

AK4

AK5

AK6

AK7

AK8

AK9

AK10

AK11

AK12

AK13

AK14

AK18

AK19

AK24

AK25

AK26

AK27

AK28

AK29

AK30

AK36

AL5

AL11

AL14

AL17

AL21

AL22

AL24

AL27

AL30

AL36

AL37

AL38

AL39

AL40

AM1

AM2

AM3

AM4

AM5

AM11

AM14

AM15

AM19

AM24

AM27

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN5

AN6

AN7

AN8

AN9

AN10

AN11

AN14

AN16

AN18

AN19

AN22

AN23

AN24

AN27

AN30

AN36

AN37

AN40

AP1

21

C79

10U-6.3VX-06

GND

GND

G3

G6

G7

G12

G13

G14

G15

G16

G17

G21

G36

G37

H1

H4

H7

H8

H9

H10

H11

H13

H17

H18

H20

H21

H22

H24

H26

H28

H30

H32

H34

H36

H39

J3

J6

J18

J19

J20

J36

J37

K1

K4

K7

K10

K14

K17

K18

K20

K22

K24

K26

K28

K30

K34

K36

K40

L3

L6

L7

L8

L9

L11

L13

L14

L35

L38

M1

M12

M14

M16

M18

M20

M22

M24

M26

M28

M30

M32

M34

M37

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

Date:

1

HASWELL

CPUJ

VSS_G3

VSS_G6

VSS_G7

VSS_G12

VSS_G13

VSS_G14

VSS_G15

VSS_G16

VSS_G17

VSS_G21

VSS_G36

VSS_G37

VSS_H1

VSS_H4

VSS_H7

VSS_H8

VSS_H9

VSS_H10

VSS_H11

VSS_H13

VSS_H17

VSS_H18

VSS_H20

VSS_H21

VSS_H22

VSS_H24

VSS_H26

VSS_H28

VSS_H30

VSS_H32

VSS_H34

VSS_H36

VSS_H39

VSS_J3

VSS_J6

VSS_J18

VSS_J19

VSS_J20

VSS_J36

VSS_J37

VSS_K1

VSS_K4

VSS_K7

VSS_K10

VSS_K14

VSS_K17

VSS_K18

VSS_K20

VSS_K22

VSS_K24

VSS_K26

VSS_K28

VSS_K30

VSS_K34

VSS_K36

VSS_K40

VSS_L3

VSS_L6

VSS_L7

VSS_L8

VSS_L9

VSS_L11

VSS_L13

VSS_L14

VSS_L35

VSS_L38

VSS_M1

VSS_M12

VSS_M14

VSS_M16

VSS_M18

VSS_M20

VSS_M22

VSS_M24

VSS_M26

VSS_M28

VSS_M30

VSS_M32

VSS_M34

VSS_M37

REV = 1

VSS_K15

VSS_K16

VSS_K32

VSS_L36

VSS_M4

VSS_M5

VSS_M6

VSS_M7

VSS_M35

VSS_M40

VSS_N1

VSS_N2

VSS_N3

VSS_N4

VSS_N6

VSS_N7

VSS_N8

VSS_N34

VSS_P2

VSS_P5

VSS_P7

VSS_P34

VSS_P35

VSS_P38

VSS_R3

VSS_R5

VSS_R6

VSS_R7

VSS_R8

VSS_R35

VSS_R40

VSS_T1

VSS_T2

VSS_T4

VSS_T5

VSS_T6

VSS_T7

VSS_T33

VSS_T39

VSS_U2

VSS_U4

VSS_U7

VSS_U33

VSS_U34

VSS_U37

VSS_V3

VSS_V6

VSS_V8

VSS_V33

VSS_V40

VSS_W1

VSS_W4

VSS_W7

VSS_W33

VSS_W35

VSS_W37

VSS_Y4

VSS_Y5

VSS_Y6

VSS_Y33

VSS_NCTF_AU40

VSS_NCTF_AV39

VSS_NCTF_AW38

VSS_NCTF_AY3

VSS_NCTF_B38

VSS_NCTF_B39

VSS_NCTF_C40

VSS_NCTF_D40

10 OF 10

HASWELL

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

CPU-PWR/GND

CPU-PWR/GND

Document Number

Document Number

Document Number

CPU-PWR/GND

H81H3-MV

H81H3-MV

H81H3-MV

Sheet

Sheet

Sheet

1

K15

K16

K32

L36

M4

M5

M6

M7

M35

M40

N1

N2

N3

N4

N6

N7

N8

N34

P2

P5

P7

P34

P35

P38

R3

R5

R6

R7

R8

R35

R40

T1

T2

T4

T5

T6

T7

T33

T39

U2

U4

U7

U33

U34

U37

V3

V6

V8

V33

V40

W1

W4

W7

W33

W35

W37

Y4

Y5

Y6

Y33

AU40

AV39

AW38

AY3

B38

B39

C40

D40

GND

732Monday, March 03, 2014

732Monday, March 03, 2014

732Monday, March 03, 2014

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

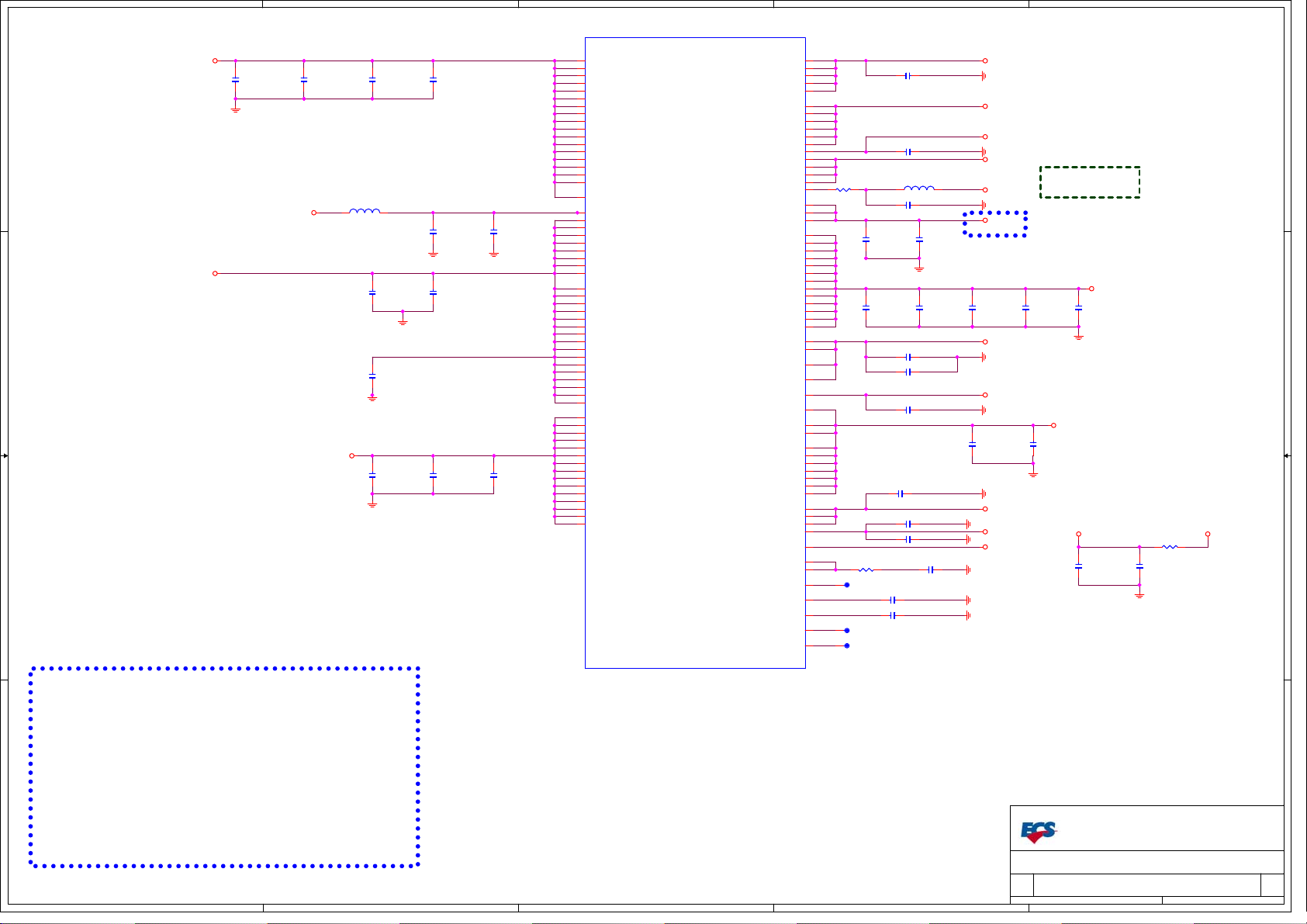

Page 8

5

4

3

2

1

167

68

53

NC/TEST4

NC/PAR IN

NC/ERR OUT

FREE349FREE448VTT_1

VTT_2

240

120

M_ODT_A[2..3]6

M_CS_A_L[2..3]6

M_CKE_A[2..3]6

M_DQS_A_N[0..7]

158

159

CB(0)39CB(1)40CB(2)45CB(3)46CB(4)

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

239

235

232

229

226

223

164

CB(5)

CB(6)

VSS_6

VSS_7

220

M_DQS_A_P0

165

7

CB(7)

VSS_8

VSS_9

217

214

211

M_DQS_A_N1

M_DQS_A_P1

M_DQS_A_N0

16

6

15

DQS(0)

DSQ(1)

DQS-(0)

DSQ-(1)

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

208

205

202

199

166

M_ODT_A[2..3]

M_CS_A_L[2..3]

M_CKE_A[2..3]

M_DQS_A_N2

M_DQS_A_P2

M_DQS_A_P3

25

34

24

DSQ(2)

DSQ-(2)

VSS_15

VSS_16

VSS_17

VSS_18

163

160

157

154

M_DQS_A_N3

M_DQS_A_N4

M_DQS_A_P4

85

33

84

DSQ(3)

DQS(4)

DSQ-(3)

VSS_19

VSS_20

VSS_21

VSS_22

151

148

145

142

M_DQS_A_N5

M_DQS_A_P5

94

93

DQS(5)

DQS-(4)

VSS_23

VSS_24

VSS_25

139

136

133

M_DQS_A_P6

M_DQS_A_N6

103

102

DSQ(6)

DQS-(5)

VSS_26

VSS_27

VSS_28

130

127

124

M_CLK_A_P[2..3]6

M_CLK_A_N[2..3]6

M_DQS_A_P7

M_DQS_A_N7

112

111

DQS(7)

DSQ-(6)

VSS_29

VSS_30

VSS_31

121

119

116

M_DATA_A[0..63]6

126

125

135

144

153

134

43

DQS-(7)

VSS_32

VSS_33

113

110

42

DQS(8)

DQS-(8)

VSS_34

VSS_35

107

104

VSS_36

143

NC/DQS9*

DM0/DQS9

NC/DQS10*

DM1/DQS10

DM2/DQS11

VSS_37

VSS_3898VSS_3995VSS_4092VSS_4189VSS_4286VSS_4383VSS_4480VSS_4547VSS_4644VSS_4741VSS_4838VSS_4935VSS_5032VSS_5129VSS_5226VSS_5323VSS_5420VSS_5517VSS_5614VSS_5711VSS_588VSS_595VSS_602VDD_5

101

M_CLK_A_P[2..3]

M_CLK_A_N[2..3]

204

152

203

212

NC/DQS11*

NC/DQS12*

NC/DQS13*

DM3/DQS12

DM4/DQS13

M_DATA_A[0..63]M_DQS_A_P[0..7]

GND

213

222

231

221

230

161

NC/DQS14*

NC/DQS15*

DM5/DQS14

NC/DQS16*

DM6/DQS15

DM7/DQS16

DM8/DQS17

VDD_1

197

VDIMM VCC3

DIMM_VREF_CA_A5,10

DIMM_VREF_DQ_A10

SMBCLK_STBY9,13,17,18,21

SMBDATA_STBY9,13,17,18,21

M_BS_A[0..2]6

162

NC/DQS17*

VDD_2

194

191

M_DATA_A0

M_DATA_A1

M_DATA_A2

DQ(0)3DQ(1)4DQ(2)9DQ(3)10DQ(4)

VDD_6

VDD_3

VDD_4

186

183

189

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A3

VDD_7

182

VCC3

M_DATA_A10

122

123

128

129

12

13

18

DQ(5)

DQ(6)

DQ(7)

DQ(8)

DQ(9)

DQ(10)

VDD_8

VDD_9

VDD_10

VDD_11

VDD_1278VDD_1375VDD_1569VDD_1666VDD_1765VDD_1862VDD_1960VDD_2057VDDSPD

VDD_14

72

179

176

173

170

DIMM_VREF_CA_A DDR3_DRAMRST_L

DIMM_VREF_DQ_A

SMBCLK_STBY

SMBDATA_STBY

M_BS_A[0..2]

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

131

132

137

138

DQ(11)19DQ(12)

DQ(13)

DQ(14)

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A16

DQ(15)

DQ(16)21DQ(17)22DQ(18)27DQ(19)28DQ(20)

VDD_2154VDD_2251VREFCA67VREFDQ1BA2

M_DATA_A24

140

141

146

147

DQ(21)

DQ(22)

DQ(23)

DQ(24)30DQ(25)31DQ(26)36DQ(27)37DQ(28)

SCL

SDA

236

118

238

GNDGND

M_DATA_A25

SA1

237

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

149

150

155

DQ(29)

SA0

BA1

52

117

190

M_BS_A1

M_BS_A2

CH.A

DIMM0

DIMM1

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A30

M_DATA_A31

156

DQ(30)

DQ(31)

DQ(32)81DQ(33)82DQ(34)87DQ(35)88DQ(36)

BA071CKE1

CKE050S1*76S0*

169

M_CKE_A3

M_CKE_A2

M_BS_A0

L

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

200

201

206

207

DQ(37)

DQ(38)

CK1/NU*64CK1/NU63CK0*

193

M_CS_A_L2

M_CS_A_L3

SA0SA1

LL

H

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

DQ(39)

DQ(40)90DQ(41)91DQ(42)96DQ(43)97DQ(44)

CK0

185

184A0188A1181

M_MA_A0

M_DATA_A47

M_DATA_A48

M_DATA_A44

M_DATA_A45

M_DATA_A46

209

210

215

216

DQ(45)

DQ(46)

DQ(47)

A261A3

A459A558A6

180

M_MA_A1

M_MA_A3

M_MA_A2

M_MA_A5

M_MA_A4

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

100

105

106

218

DQ(48)99DQ(49)

DQ(50)

DQ(51)

A756A8

178

177A9175

M_MA_A8

M_MA_A7

M_MA_A6

M_MA_A9

M_CLK_A_P2

M_CLK_A_N2

M_CLK_A_P3

M_CLK_A_N3

M_DATA_A53

219

DQ(52)

DQ(53)

A10/AP70A1155A12

M_MA_A10

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

224

225

108

109

DQ(54)

DQ(55)

DQ(56)

DQ(57)

A13

A14

174

196

172

M_MA_A12

M_MA_A14

M_MA_A13

M_MA_A11

M_DATA_A60

M_DATA_A58

M_DATA_A59

114

115

227

DQ(58)

DQ(59)

A15

171

168

M_MA_A15

M_DATA_A61

M_DATA_A62

M_DATA_A63

228

233

234

DQ(60)

DQ(61)

DQ(62)

DQ(63)

CAS*74RAS*

WE*

RESET*

73

192

M_WE_A_L

M_RAS_A_L

M_CAS_A_L

M_MA_A[0..15]

DIMM1DDR3-240P-GY

Change Dram ref value

Devon 1102

M_WE_A_L 6

M_RAS_A_L 6

M_CAS_A_L 6

DDR3_DRAMRST_L 6,9

M_MA_A[0..15] 6

D D

C C

M_DQS_A_N[0..7]6

M_DQS_A_P[0..7]6

DDR_VTT

M_ODT_A2

M_ODT_A3

195

79

ODT177ODT0

RSVD

FREE1

FREE2

198

187

CHANNEL A DIMM

B B

[0..3]=>[2..3]

Devon 12/10/15

VDIMM

C185

10U-6.3VX-06

2 1

A A

VDIMM

GND

C151

.1U-16VX-04

2 1

C133

.1U-16VX-04

2 1

closetoCHA‐DIMM1

5

C129

.1U-16VX-04

2 1

C132

1U-6.3VX-04

2 1

C152

.1U-16VX-04

2 1

C130

1U-6.3VX-04

2 1

C131

.1U-16VX-04

2 1

4

3

DDR_VTT VCC3

C189

10U-6.3VX-06

2 1

closetoCHA‐DIMM1

GND

2

C181

.1U-16VX-04

2 1

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

Date:

GNDGND

Document Number

Document Number

Document Number

C182

.1U-16VX-04

2 1

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

C157

.1U-16VX-04-O

2 1

placebetweenCHA&CHB

Don'tpunchVIAS

DDR3-CHA

DDR3-CHA

DDR3-CHA

H81H3-MV

H81H3-MV

H81H3-MV

Sheet

Sheet

Sheet

1

832Monday, March 03, 2014

832Monday, March 03, 2014

832Monday, March 03, 2014

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

Page 9

5

M_ODT_B2

68

195

ODT177ODT0

FREE2

FREE349FREE448VTT_1

167

53

NC/TEST4

NC/PAR IN

NC/ERR OUT

VTT_2

240

120

GND

M_DQS_B_N[0..7]

158

159

CB(0)39CB(1)40CB(2)45CB(3)46CB(4)

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

239

235

232

229

226

223

164

CB(5)

CB(6)

VSS_6

VSS_7

220

M_DQS_B_P0

165

7

CB(7)

VSS_8

VSS_9

217

214

211

M_DQS_B_N1

M_DQS_B_P1

M_DQS_B_N0

16

6

15

DQS(0)

DSQ(1)

DQS-(0)

VSS_10

VSS_11

VSS_12

VSS_13

208

205

202

199

M_DQS_B_N2

M_DQS_B_P2

25

24

DSQ(2)

DSQ-(1)

VSS_14

VSS_15

VSS_16

166

163

160

M_DQS_B_N3

M_DQS_B_P3

34

33

DSQ(3)

DSQ-(2)

VSS_17

VSS_18

VSS_19

157

154

151

M_DQS_B_N4

M_DQS_B_P4

85

84

DQS(4)

DSQ-(3)

VSS_20

VSS_21

VSS_22

148

145

142

M_DQS_B_N5

M_DQS_B_P5

94

93

DQS(5)

DQS-(4)

VSS_23

VSS_24

VSS_25

139

136

133

DQS-(5)

VSS_26

130

M_DQS_B_N[0..7]6

M_DQS_B_P[0..7]6

M_ODT_B3

D D

79

198

DDR_VTT

RSVD

FREE1

187

CHANNEL B DIMM

C C

M_DQS_B_P6

M_DQS_B_P7

M_DQS_B_N6

103

112

102

DSQ(6)

DSQ-(6)

VSS_27

VSS_28

VSS_29

VSS_30

127

124

121

119

4

M_DQS_B_N7

43

111

42

DQS(7)

DQS(8)

DQS-(7)

VSS_31

VSS_32

VSS_33

VSS_34

116

113

110

107

M_DATA_B[0..63]6

126

125

135

144

134

DQS-(8)

NC/DQS9*

DM0/DQS9

DM1/DQS10

VSS_35

VSS_36

VSS_37

VSS_3898VSS_3995VSS_4092VSS_4189VSS_4286VSS_4383VSS_4480VSS_4547VSS_4644VSS_4741VSS_4838VSS_4935VSS_5032VSS_5129VSS_5226VSS_5323VSS_5420VSS_5517VSS_5614VSS_5711VSS_588VSS_595VSS_602VDD_5

104

101

153

143

152

NC/DQS10*

NC/DQS11*

NC/DQS12*

DM2/DQS11

DM3/DQS12

M_DATA_B[0..63]M_DQS_B_P[0..7]

204

213

203

DM4/DQS13

222

212

221

230

NC/DQS13*

NC/DQS14*

NC/DQS15*

DM5/DQS14

DM6/DQS15

DM7/DQS16

VDIMM

3

GND

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

231

162

161

NC/DQS16*

DM8/DQS17

VDD_1

197

DIMM_VREF_CA_B5,10

DIMM_VREF_DQ_B10 M_MA_B[0..15] 6

SMBCLK_STBY8,13,17,18,21

SMBDATA_STBY8,13,17,18,21

M_BS_B[0..2]6

194

NC/DQS17*

VDD_2

191

DQ(0)3DQ(1)4DQ(2)9DQ(3)10DQ(4)

VDD_3

VDD_4

186

189

VDD_6

183

VCC3

122

123

128

129

12

13

18

DQ(5)

DQ(6)

DQ(7)

DQ(8)

DQ(9)

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_1278VDD_1375VDD_1569VDD_1666VDD_1765VDD_1862VDD_1960VDD_2057VDDSPD

179

176

173

72

170

DIMM_VREF_CA_B

DIMM_VREF_DQ_B

SMBCLK_STBY

SMBDATA_STBY

M_BS_B[0..2]

182

DQ(10)

VDD_14

131

DQ(11)19DQ(12)

132

137

138

DQ(13)

DQ(14)

DQ(15)

140

141

146

147

DQ(16)21DQ(17)22DQ(18)27DQ(19)28DQ(20)

DQ(21)

DQ(22)

DQ(23)

SCL

VDD_2154VDD_2251VREFCA67VREFDQ1BA2

236

118

M_DATA_B24

149

DQ(24)30DQ(25)31DQ(26)36DQ(27)37DQ(28)

SDA

SA0

SA1

52

238

117

237

M_BS_B2

M_DATA_B30

150

155

DQ(29)

BA1

190

M_BS_B1

M_BS_B0

CH.BHSA1 SA0

DIMM0

DIMM1

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

156

DQ(30)

DQ(31)

DQ(32)81DQ(33)82DQ(34)87DQ(35)88DQ(36)

BA071CKE1

CKE050S1*76S0*

169

M_CKE_B3

M_CKE_B2

HL

H

2

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

200

201

206

207

DQ(37)

DQ(38)

CK1/NU*64CK1/NU63CK0*

193

M_CS_B_L3

M_CS_B_L2

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

DQ(39)

DQ(40)90DQ(41)91DQ(42)96DQ(43)97DQ(44)

CK0

185

184A0188A1181

M_MA_B0

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48M_MA_B5

209

210

215

216

DQ(45)

DQ(46)

DQ(47)

A261A3

A459A558A6

180

M_MA_B2

M_MA_B3

M_MA_B4

M_MA_B1

M_DATA_B49

M_DATA_B50

M_DATA_B51

M_DATA_B52

100

105

106

218

DQ(48)99DQ(49)

DQ(50)

DQ(51)

A756A8

178

177A9175

M_MA_B8

M_MA_B9

M_MA_B6

M_MA_B7

M_CLK_B_P2

M_CLK_B_N2

M_CLK_B_P3

M_CLK_B_N3

M_DATA_B53

M_DATA_B54

M_DATA_B55

M_DATA_B56

219

224

225

108

DQ(52)

DQ(53)

DQ(54)

DQ(55)

A10/AP70A1155A12

174

196

M_MA_B11

M_MA_B10

M_MA_B12

M_MA_B13

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

109

114

115

227

DQ(56)

DQ(57)

DQ(58)

DQ(59)

A13

A14

A15

172

171

168

M_MA_B15

M_MA_B14

M_DATA_B61

M_DATA_B62

M_DATA_B63

228

233

234

DQ(60)

DQ(61)

DQ(62)

DQ(63)

CAS*74RAS*

WE*

RESET*

73

192

M_WE_B_L

M_RAS_B_L

M_CAS_B_L

DDR3_DRAMRST_L

M_MA_B[0..15]

1

DIMM2DDR3-240P-GY

M_WE_B_L 6

M_RAS_B_L 6

M_CAS_B_L 6

DDR3_DRAMRST_L 6,8

C128

10U-6.3VX-06

C180

.1U-16VX-04

5

M_ODT_B[2..3]

M_CS_B_L[2..3]

M_CKE_B[2..3]

C188

1U-6.3VX-04

2 1

M_ODT_B[2..3]6

VDIMM

2 1

GND

VDIMM

2 1

GND

M_CS_B_L[2..3]6

M_CKE_B[2..3]6

C161

10U-6.3VX-06

C154

.1U-16VX-04

closetoCHB‐DIMM2

2 1

2 1

B B

A A

C187

1U-6.3VX-04

2 1

M_CLK_B_P[2..3]6

M_CLK_B_N[2..3]6

C186

10U-6.3VX-06

2 1

M_CLK_B_P[2..3]

M_CLK_B_N[2..3]

[0..3]=>[2..3]

Devon 20121015

4

DDR_VTT

C156

10U-6.3VX-06

2 1

GND

closetoCHB‐DIMM2

3

C155

.1U-16VX-04

2 1

2

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

Date:

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

DDR3-CHB

DDR3-CHB

Document Number

Document Number

Document Number

DDR3-CHB

H81H3-MV

H81H3-MV

H81H3-MV

1

Sheet

Sheet

Sheet

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

932Monday, March 03, 2014

932Monday, March 03, 2014

932Monday, March 03, 2014

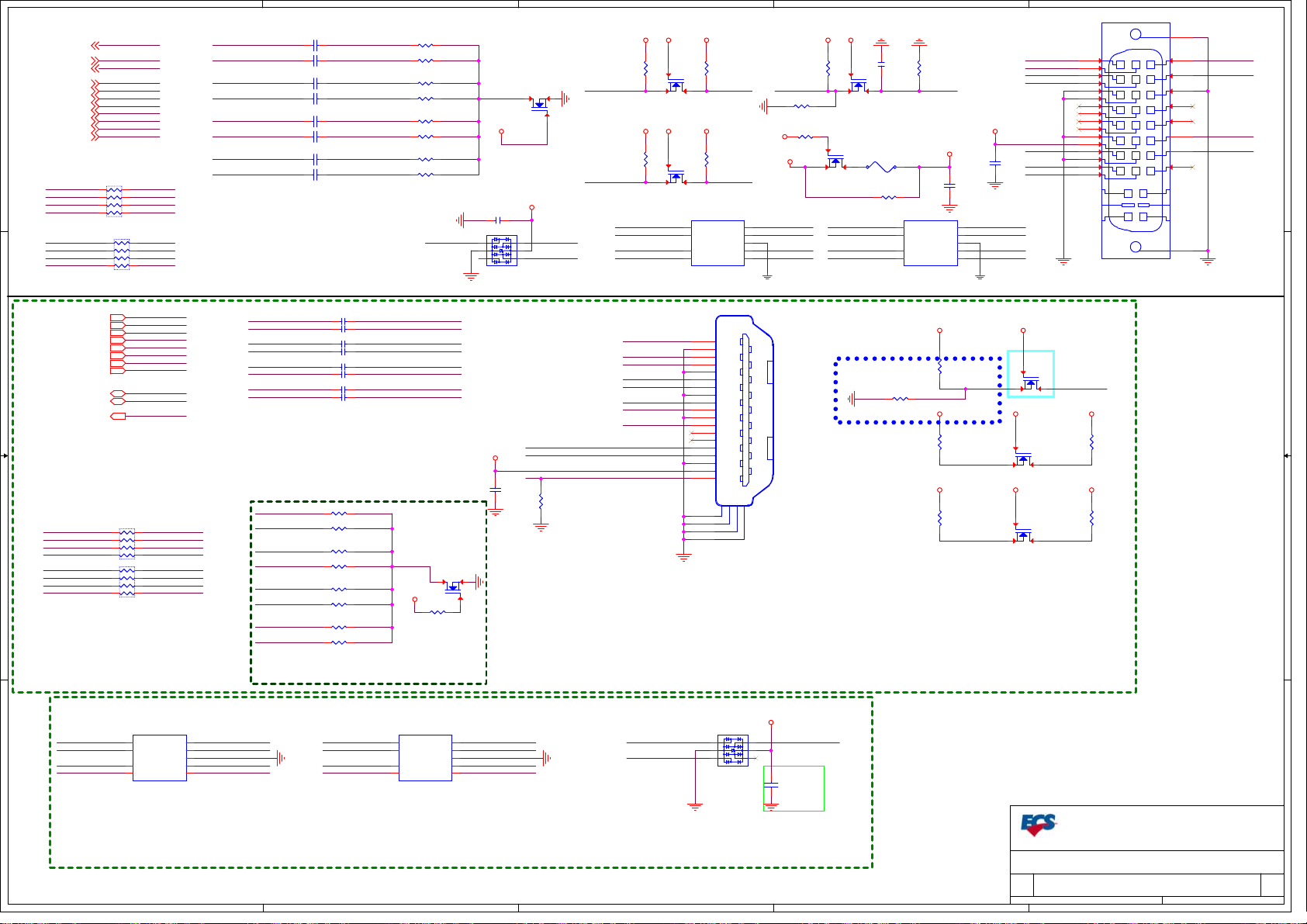

Page 10

5

4

3

2

1

D D

C C

B B

DIMM_VREF_CACircuit

VDIMM

12

ER95

1K-1-04

DIMM_VREF_CA_A 5,8 DIMM_VREF_CA_B 5,9

close to DIMM

close to DIMM

12

ER94

1K-1-04

GND GND GND

C153

.1U-16VX-04

2 1

C149

10U-6.3VX-06-O

2 1

GND GND

DIMM_VREF_DQCircuit

VDIMM

GND

12

12

ER91

1K-1-04

ER92

1K-1-04

C135

.1U-16VX-04-O

2 1

GND

close to DIMM close to DIMM

R196

0-04

1 2

2 1

GND

C134

.1U-16VX-04

DIMM_VREF_DQ_A 8

DIMM_DQ_CPU_VREF_B6

C158

.1U-16VX-04-O

2 1

GND

close to DIMM's vref close to DIMM's vref

DIMM_DQ_CPU_VREF_A6

VDIMM

12

R258

1K-1-04

12

R257

1K-1-04

VDIMM

12

ER97

1K-1-04

12

ER96

1K-1-04

GND GND

DIMM_VREF_CA_BDIMM_VREF_CA_A

2 1

GND

2 1

C183

.1U-16VX-04

C159

.1U-16VX-04

C184

10U-6.3VX-06-O

2 1

R230

0-04

1 2

DIMM_VREF_DQ_B 9

Del .1U capacitance 20130520 AmosDel .1U capacitance 20130520 Amos

A A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Document Number

Document Number

Document Number

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

5

4

3

2

Date:

DDR3-Vref

DDR3-Vref

DDR3-Vref

H81H3-MV

H81H3-MV

H81H3-MV

1

Sheet

Sheet

Sheet

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

10 32Monday, March 03, 2014

10 32Monday, March 03, 2014

10 32Monday, March 03, 2014

Page 11

5

4

3

2

1

R117

0-04

ER44

2 1

1.27K-1-04

ER41

13K-1-04

VR_EN

VR_READY

VR_HOT

AU1_SET3

AU1_SET1

AU1_SET2

AU1_VSEN

AU1_COMP

AU1_FB

R151

2 1

2.2-08

21

2

1

29

23

18

15

13

14

10

8

9

PWM

RT8884BGQW

5VS

2 1

NTC1N

106A for ICCMAX=2.2V

D D

C C

B B

External Connection

VCCIO_OUT

VIN VIN

VCC3 VCC3

I_VCORE13

VR_EN5

VR_SVID_ALERT_L5

VR_SVID_DATAOUT5

VR_SVID_CK5

VR_HOT_L5

AU1_ISEN1P12

AU1_ISEN1N12

AU1_ISEN2P12

AU1_ISEN2N12

AU1_ISEN3P12

AU1_ISEN3N12

AU1_ISEN4P12

AU1_ISEN4N12

PWM112

PWM212

PWM312

PWM412

VCORE_VCC_SEN5

VCORE_VSS_SEN5

VR_READY5,18

NTC1N12

NTC1P12

I_VCORE

VR_EN

ALERT

VDIO

VCLK

VR_HOT

AU1_ISEN1P

AU1_ISEN1N

AU1_ISEN2P

AU1_ISEN2N

AU1_ISEN3P

AU1_ISEN3N

AU1_ISEN4P

AU1_ISEN4N

PWM1

PWM2

PWM3

PWM4

VCC_SEN

VSS_SEN

VR_READY

NTC1N

NTC1P

AVTT

VCCVCC

VCOREVCORE

12V_4P12V_4P

5VSB5VSB