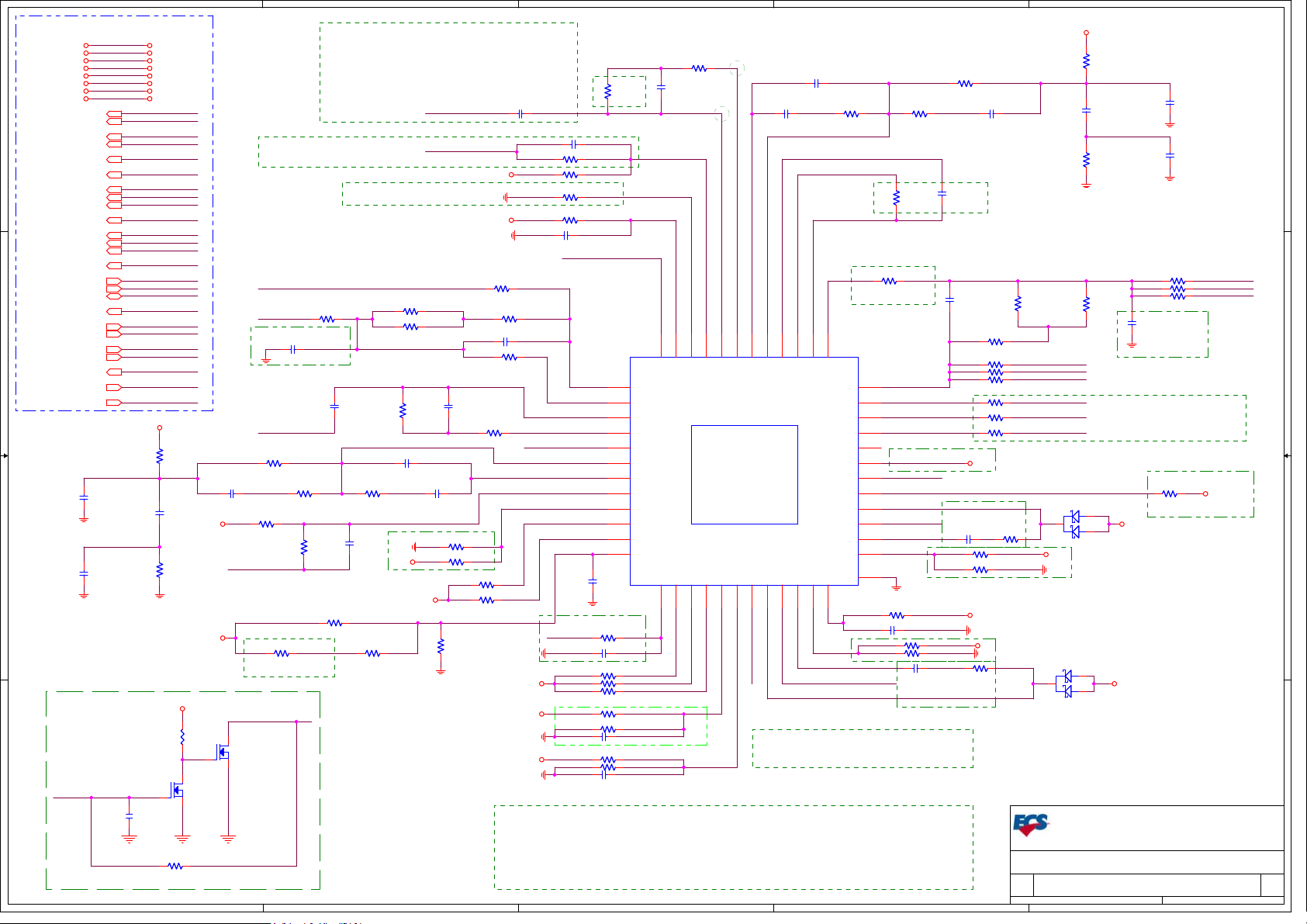

ECS H61H2-M12 Schematics REV 1.0

5

4

3

2

1

H61H2-M12

D D

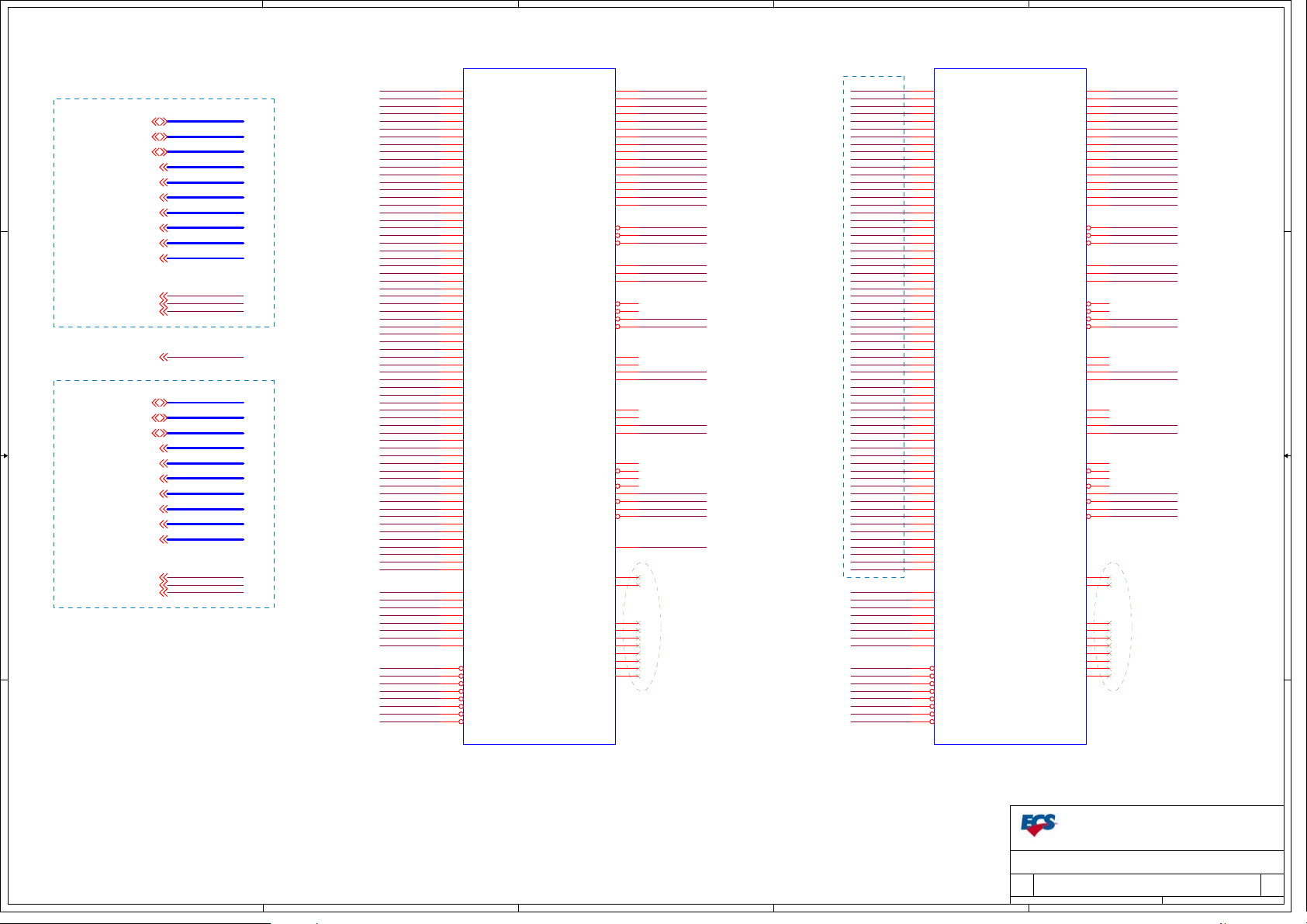

TABLE OF CONTENTS

Page Index

------- ------------------------

1

Cover Page

2

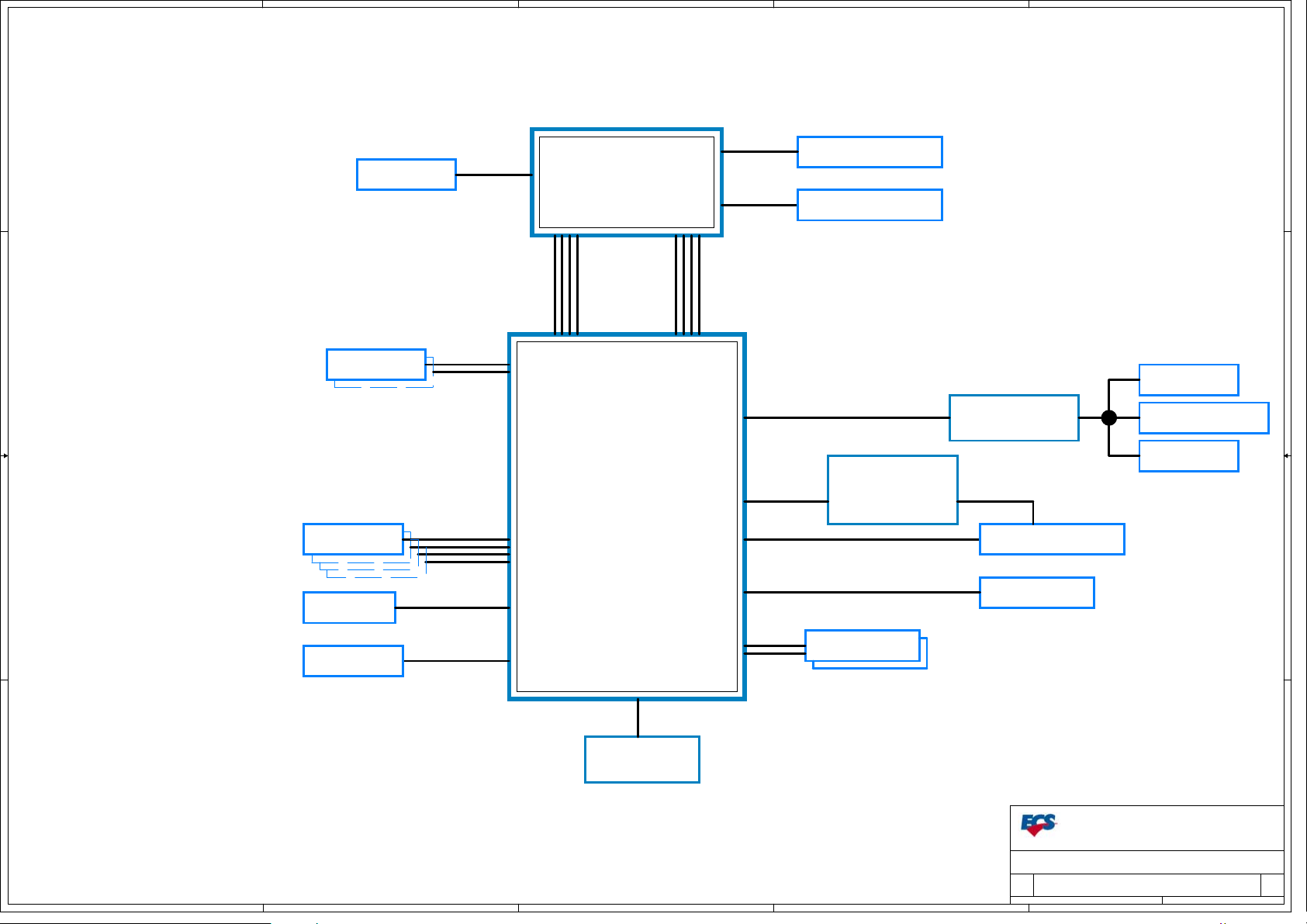

Block Diagram

3

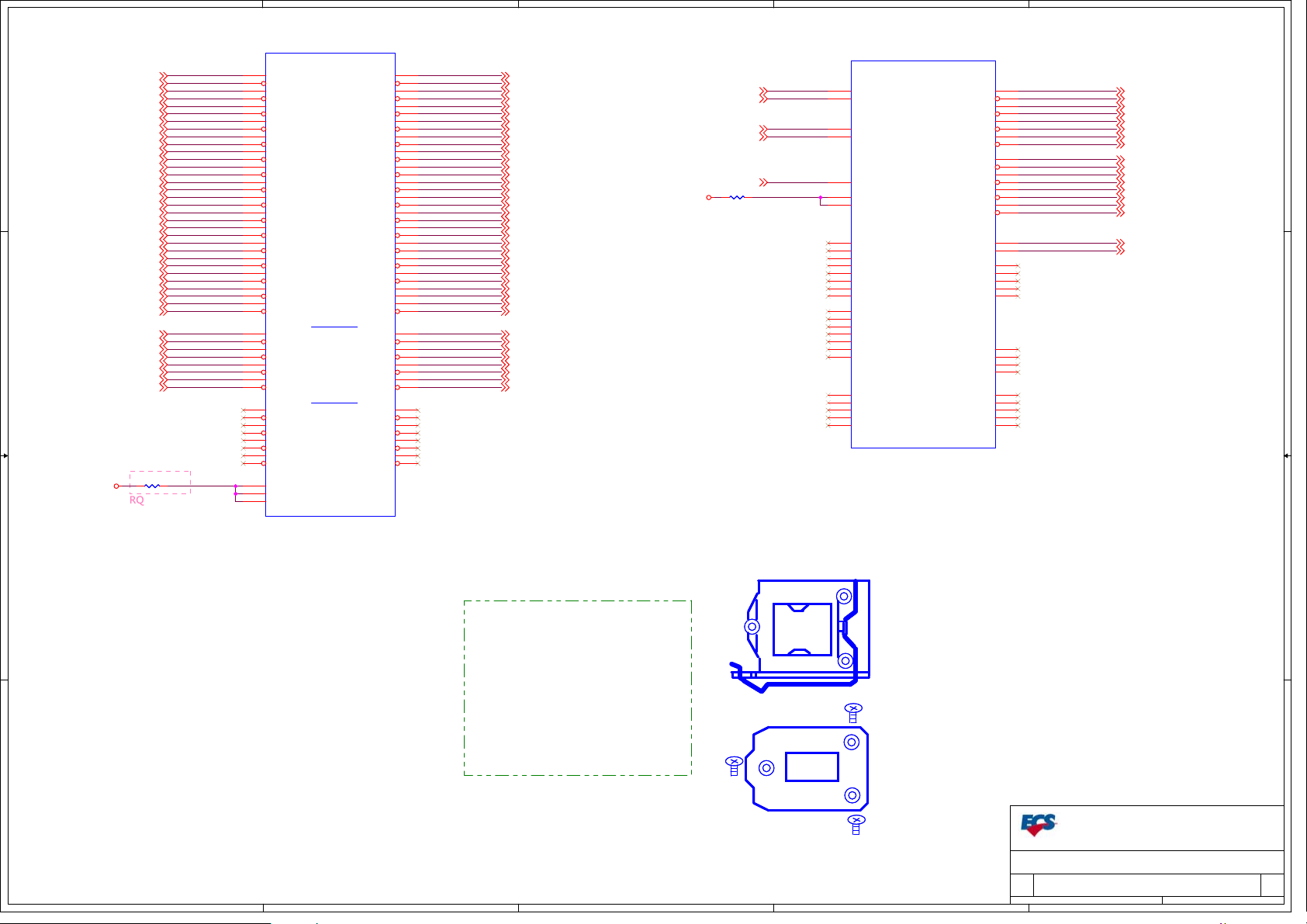

CPU - DMI/FDI/PEG

4

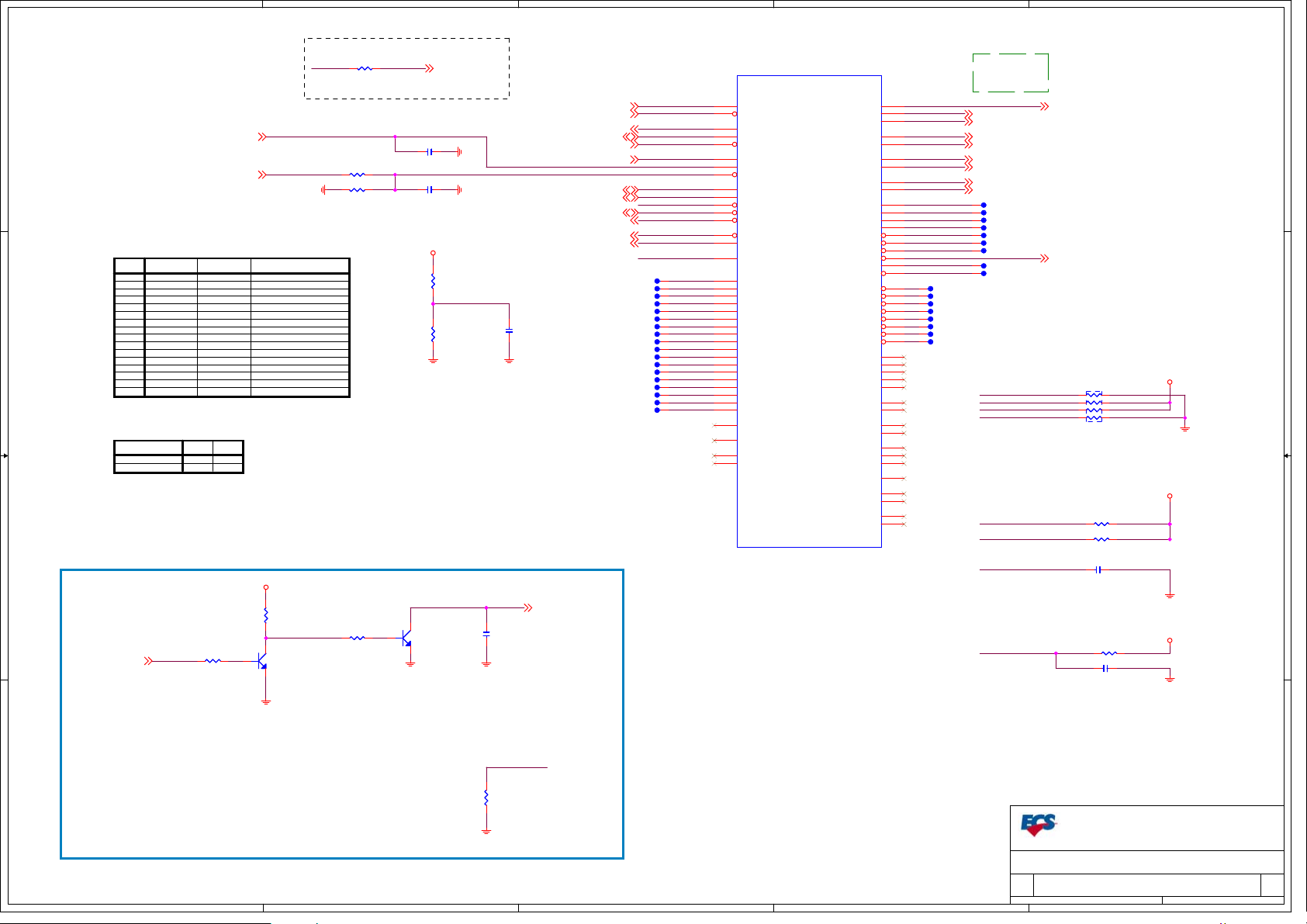

CPU - MISC

5

CPU - DDR3

6

C C

10

11

12

13

14

15

B B

16

17

18

19

20

21

22

23

24

25

A A

CPU - PWR/GND

7

DDR3 - CH_A_DIMM1

8

DDR3 - CH_B_DIMM3

9

VCore & VAXG-UP1625

VCore & VAXG- UP6281

DC/DC CPUVTT-UP1525 / VCCSA

DC/DC VDIMM/DDR_VTT/5VDUAL

Front Panel,FAN,PowerConn,GND,104

PCH - DMI/PCI/PE/USB

PCH - SATA / CLK

PCH - MISC, Strap Function

PCH - DP/VGA/FDI

PCH - PWR

PCH - GND

Slot - PCI-EX16/PCI-EX1

COM&PS2

USB/SATA/SPI

SIO-F71808A

AUDIO VT1705/ALC662(CHIP)

AUDIO VT1705/ALC662(PANEL)

Page Index

------- ------------------------

26

27

28

29

PCIE LAN AR8151-B/AR8152-B

Power Delivery

Power Sequence, Reset Diagram

Clock Distribution

REVISION HISTORY:

Rev Date Notes

------ -------------- ---------------------------------------------------------------------------------

P61G V1.0 2011/04/07

H61H2-M12 V1.02011/07/12

RD : Jayson

LAYOUT :

EMI :

Rev : 1.0

RED_PCB P/N : 15-Y97-011001 (GE1) / 15-Y97-011000 (CHUANYI)

BOM P/N : 81-605-Y97100

EC35 change to EC-cap 1000U-6.3DL

EC1, EC4 from 100uF change to 220uF

Del RT1, RT3, R137, R180 ( Not need compensation of temperature ).

For 5VSB Inrush Current : R102 from 100k change to 33k.

Select TACH0_GPIO17 to decide COM .

2011/05/04H61H2-M12 VA

Black_PCB P/N : 15-EC7-010010

BOM P/N : 81-605-EC7000/81-605-EC7001(10/100 ; GiGA)

PCB Size change to 225*170 mm

Del DVI

Vcore 減少一相

VIN 電容減少一顆

LAN change to Atheros 8152/8151/8161

Codec change to VT1705CE.

USB Power use fuse & Jumper.

Black_PCB P/N : 15-EC7-011000/15-EC7-011001

BOM P/N :

PCB Size change to 225*170 mm

ECS CONFIDENTIAL

NOTE:

Design by 428971_428971_Sugar_Bay_and_BromolowWS_PDG_Rev_0_8.pdf,

428880_428880_Cougar_Point_Desktop_Ballout_Mech_Package_Rev1p0.zip

5

4

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Cover Page

Cover Page

Cover Page

H61H2-M12

H61H2-M12

H61H2-M12

1

1.0

1.0

129Wednesday, July 13, 2011

129Wednesday, July 13, 2011

129Wednesday, July 13, 2011

1.0

5

4

3

2

1

---------------------------------------------------------

Pin Name Power Well Usage

---------------------------------------------------------

GPIO71 VCC3

GPIO22 VCC3

GPIO38 VCC3

D D

GPIO39

GPIO48

GPIO21 VCC3

GPIO36

GPIO37

GPIO16 VCC3

GPIO49 VCC3

GPIO0 VCC3 F_AUDIO Detect

GPIO15 Down Voltage for DIMM

C C

GPIO48 Down Voltage for DIMM

VCC3

VCC3

VCC3

VCC3

Reserve for TPM

Reserve for TPM GPI

3VSB GPO

VCC3 GPI

Default Status

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPOVCC3 ME Enable/DisableGPIO33

GPIVCC3 pull-upGPIO34

GPI3VSB PMEGPIO13

GPO3VSB SKTOCCGPIO24

GPI3VSB Board ID(CRB_0.7)GPIO57

GPI3VSB TPM_LPCPDGPIO61

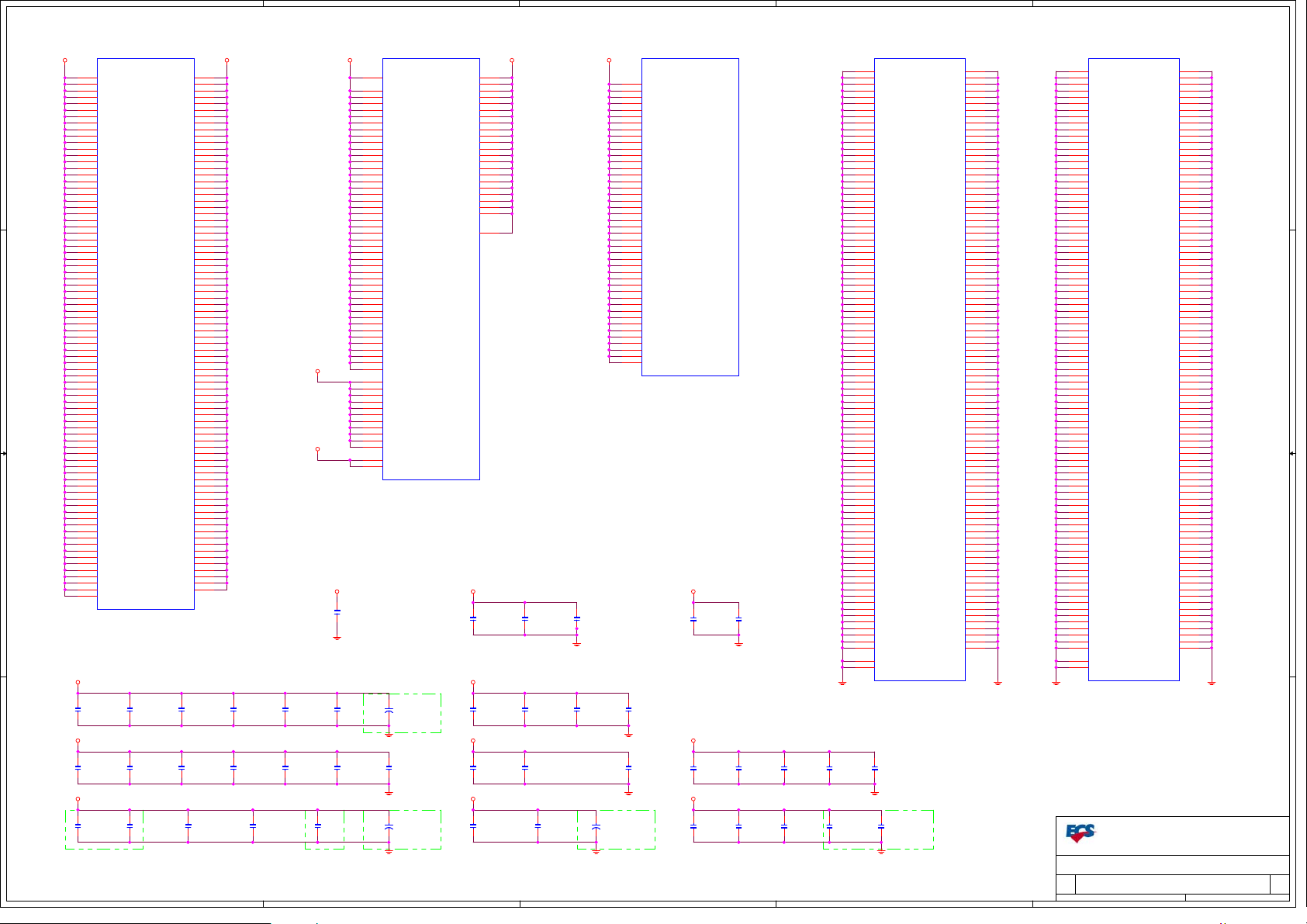

PCI-E X16

PCI-E X1

Sandy Bridge

Desktop Processor

Socket H2

FDI

DDR3 Channel A

DDR3

1333MHz/1066MHz

DDR3 Channel B

Total Max 8GB

DMI

Jack 3 in 1

AUDIO CODEC:

(Delete) SPDIF OUT

VT1705CE

PCH-GPIO function

F_AUDIO

LAN:

Cougar

Point

SATA 2.0

B B

3Gbps

Chipset

RTL8105E-VL/

RTL8111E-VL

RJ-45 & USB2.0 x2

USB2.0 x2Ports

VGA

F_USB 2 Headers

DVI-D

SIO-GPIO function

---------------------------------------------------------

Pin Name Power Well Usage

---------------------------------------------------------

PIN23

A A

5VSB

5VSB

5

Power LED GPIO25/LEDVCC/WDTRST#

Power LEDPIN22

UsagePin Name

UsagePin Name

UsagePin Name

UsagePin Name

Default Status

GPIO24/LEDVSB

www.schematic-x.blogspot.com

4

SIO:

F71808A

3

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Block Diagram

Block Diagram

Block Diagram

H61H2-M12

H61H2-M12

H61H2-M12

1

1.0

1.0

229Wednesday, July 13, 2011

229Wednesday, July 13, 2011

229Wednesday, July 13, 2011

1.0

5

CPUA

CPUA

BALLMAP_REV=1.4

BALLMAP_REV=1.4

PEG_RX_P020

PEG_RX_N020

PEG_RX_P120

PEG_RX_N120

PEG_RX_P220

PEG_RX_N220

V_CPUVTT

PEG_RX_P320

PEG_RX_N320

PEG_RX_P420

PEG_RX_N420

PEG_RX_P520

PEG_RX_N520

PEG_RX_P620

PEG_RX_N620

PEG_RX_P720

PEG_RX_N720

PEG_RX_P820

PEG_RX_N820

PEG_RX_P920

PEG_RX_N920

PEG_RX_P1020

PEG_RX_N1020

PEG_RX_P1120

PEG_RX_N1120

PEG_RX_P1220

PEG_RX_N1220

PEG_RX_P1320

PEG_RX_N1320

PEG_RX_P1420

PEG_RX_N1420

PEG_RX_P1520

PEG_RX_N1520

DMI_RX_P014

DMI_RX_N014

DMI_RX_P114

DMI_RX_N114

DMI_RX_P214

DMI_RX_N214

DMI_RX_P314

DMI_RX_N314

ER25 24.9-1-04ER25 24.9-1-04

1 2

R

D D

C C

B B

PEG_RX_P0

PEG_RX_N0

PEG_RX_P1

PEG_RX_N1

PEG_RX_P2

PEG_RX_N2

PEG_RX_P3

PEG_RX_N3

PEG_RX_P4

PEG_RX_N4

PEG_RX_P5

PEG_RX_N5

PEG_RX_P6

PEG_RX_N6

PEG_RX_P7

PEG_RX_N7

PEG_RX_P8

PEG_RX_N8

PEG_RX_P9

PEG_RX_N9

PEG_RX_P10

PEG_RX_N10

PEG_RX_P11

PEG_RX_N11

PEG_RX_P12

PEG_RX_N12

PEG_RX_P13

PEG_RX_N13

PEG_RX_P14

PEG_RX_N14

PEG_RX_P15

PEG_RX_N15

DMI_RX_P0

DMI_RX_N0

DMI_RX_P1

DMI_RX_N1

DMI_RX_P2

DMI_RX_N2

DMI_RX_P3

DMI_RX_N3

Q

PEG_COMP

SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLE 4MIL TRACE TO RQ.

1 ROUTE B5 TO RQ. 1 AS A SEPERATE 12MIL TRACE.

B11

B12

D12

D11

C10

E10

AA4

AA5

C9

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

W5

W4

V3

V4

Y3

Y4

P3

P4

R2

R1

T4

T3

U2

U1

B5

C4

B4

PEG_RX_0

PEG_RX#_0

PEG_RX_1

PEG_RX#_1

PEG_RX_2

PEG_RX#_2

PEG_RX_3

PEG_RX#_3

PEG_RX_4

PEG_RX#_4

PEG_RX_5

PEG_RX#_5

PEG_RX_6

PEG_RX#_6

PEG_RX_7

PEG_RX#_7

PEG_RX_8

PEG_RX#_8

PEG_RX_9

PEG_RX#_9

PEG_RX_10

PEG_RX#_10

PEG_RX_11

PEG_RX#_11

PEG_RX_12

PEG_RX#_12

PEG_RX_13

PEG_RX#_13

PEG_RX_14

PEG_RX#_14

PEG_RX_15

PEG_RX#_15

DMI_RX_0

DMI_RX#_0

DMI_RX_1

DMI_RX#_1

DMI_RX_2

DMI_RX#_2

DMI_RX_3

DMI_RX#_3

PE_RX_0

PE_RX#_0

PE_RX_1

PE_RX#_1

PE_RX_2

PE_RX#_2

PE_RX_3

PE_RX#_3

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

SKT_H2_CRB

SKT_H2_CRB

PEGDMIGEN

PEGDMIGEN

PEG_TX_0

PEG_TX#_0

PEG_TX_1

PEG_TX#_1

PEG_TX_2

PEG_TX#_2

PEG_TX_3

PEG_TX#_3

PEG_TX_4

PEG_TX#_4

PEG_TX_5

PEG_TX#_5

PEG_TX_6

PEG_TX#_6

PEG_TX_7

PEG_TX#_7

PEG_TX_8

PEG_TX#_8

PEG_TX_9

PEG_TX#_9

PEG_TX_10

PEG_TX#_10

PEG_TX_11

PEG_TX#_11

PEG_TX_12

PEG_TX#_12

PEG_TX_13

PEG_TX#_13

PEG_TX_14

PEG_TX#_14

PEG_TX_15

PEG_TX#_15

DMI_TX_0

DMI_TX#_0

DMI_TX_1

DMI_TX#_1

DMI_TX_2

DMI_TX#_2

DMI_TX_3

DMI_TX#_3

PE_TX_0

PE_TX#_0

PE_TX_1

PE_TX#_1

PE_TX_2

PE_TX#_2

PE_TX_3

PE_TX#_3

1 OF 10

1 OF 10

4

C13

PEG_TX_P0

C14

PEG_TX_N0

E14

PEG_TX_P1

E13

PEG_TX_N1

G14

PEG_TX_P2

G13

PEG_TX_N2

F12

PEG_TX_P3

F11

PEG_TX_N3

J14

PEG_TX_P4

J13

PEG_TX_N4

D8

PEG_TX_P5

D7

PEG_TX_N5

D3

PEG_TX_P6

C3

PEG_TX_N6

E6

PEG_TX_P7

E5

PEG_TX_N7

F8

PEG_TX_P8

F7

PEG_TX_N8

G10

PEG_TX_P9

G9

PEG_TX_N9

G5

PEG_TX_P10

G6

PEG_TX_N10

K7

PEG_TX_P11

K8

PEG_TX_N11

J5

PEG_TX_P12

J6

PEG_TX_N12

M8

PEG_TX_P13

M7

PEG_TX_N13

L6

PEG_TX_P14

L5

PEG_TX_N14

N5

PEG_TX_P15

N6

PEG_TX_N15

V7

DMI_TX_P0

V6

DMI_TX_N0

W7

DMI_TX_P1

W8

DMI_TX_N1

Y6

DMI_TX_P2

Y7

DMI_TX_N2

AA7

DMI_TX_P3

AA8

DMI_TX_N3

P8

P7

T7

T8

These signals are

R6

available for Workstation only

R5

U5

U6

PEG_TX_P0 20

PEG_TX_N0 20

PEG_TX_P1 20

PEG_TX_N1 20

PEG_TX_P2 20

PEG_TX_N2 20

PEG_TX_P3 20

PEG_TX_N3 20

PEG_TX_P4 20

PEG_TX_N4 20

PEG_TX_P5 20

PEG_TX_N5 20

PEG_TX_P6 20

PEG_TX_N6 20

PEG_TX_P7 20

PEG_TX_N7 20

PEG_TX_P8 20

PEG_TX_N8 20

PEG_TX_P9 20

PEG_TX_N9 20

PEG_TX_P10 20

PEG_TX_N10 20

PEG_TX_P11 20

PEG_TX_N11 20

PEG_TX_P12 20

PEG_TX_N12 20

PEG_TX_P13 20

PEG_TX_N13 20

PEG_TX_P14 20

PEG_TX_N14 20

PEG_TX_P15 20

PEG_TX_N15 20

DMI_TX_P0 14

DMI_TX_N0 14

DMI_TX_P1 14

DMI_TX_N1 14

DMI_TX_P2 14

DMI_TX_N2 14

DMI_TX_P3 14

DMI_TX_N3 14

3

V_CPUVTT

FDI_FSYNC017

FDI_LSYNC017

FDI_FSYNC117

FDI_LSYNC117

FDI_INT17

1 2

ER36 24.9-1-04ER36 24.9-1-04

FDI_FSYNC0

FDI_LSYNC0

FDI_FSYNC1

FDI_LSYNC1

FDI_INT

FDI_COMP

CPU(104)

CPU(104)

CPU_SUBASSY_STEEL

CPU_SUBASSY_STEEL

AC5

AC4

AE5

AE4

AG3

AE2

AE1

AB7

AD37

AG4

AJ29

AJ30

AJ31

AV34

AW34

R34

R36

R38

R40

AU40

AW38

P35

P37

P39

A38

CPUB

CPUB

C2

D1

SKT_H2_CRB

SKT_H2_CRB

FDI_FSYNC_0

FDI_LSYNC_0

FDI_FSYNC_1

FDI_LSYNC_1

FDI_INT

FDI_COMPIO

FDI_ICOMPO

RSVD_04

RSVD_05

RSVD_08

RSVD_10

RSVD_11

RSVD_12

RSVD_19

RSVD_21

RSVD_43

RSVD_44

RSVD_45

RSVD_46

RSVD_47

RSVD_48

RSVD_49

NCTF_01

NCTF_02

NCTF_03

NCTF_04

NCTF_05

2

BALLMAP_REV=1.4

BALLMAP_REV=1.4

FDI_TX_0

FDI_TX#_0

FDI_TX_1

FDI_TX#_1

FDI_TX_2

FDI_TX#_2

FDI_TX_3

FDI LINK

FDI LINK

2 OF 10

2 OF 10

FDI_TX#_3

FDI_TX_4

FDI_TX#_4

FDI_TX_5

FDI_TX#_5

FDI_TX_6

FDI_TX#_6

FDI_TX_7

FDI_TX#_7

SB_DIMM_DQVREF

SA_DIMM_DQVREF

RSVD_15

RSVD_14

RSVD_13

RSVD_17

RSVD_22

RSVD_07

RSVD_03

RSVD_06

RSVD_09

RSVD_27

RSVD_26

RSVD_25

RSVD_31

RSVD_41

AC8

FDI_TX_P0

AC7

FDI_TX_N0

AC2

FDI_TX_P1

AC3

FDI_TX_N1

AD2

FDI_TX_P2

AD1

FDI_TX_N2

AD4

FDI_TX_P3

AD3

FDI_TX_N3

AD7

FDI_TX_P4

AD6

FDI_TX_N4

AE7

FDI_TX_P5

AE8

FDI_TX_N5

AF3

FDI_TX_P6

AF2

FDI_TX_N6

AG2

FDI_TX_P7

AG1

FDI_TX_N7

AH1

DIMM_DQ_CPU_VREF_B

AH4

DIMM_DQ_CPU_VREF_A

AT11

AP20

AN20

AU10

AY10

AF4

AB6

AE6

AJ11

D38

C39

C38

J34

N34

1

FDI_TX_P0 17

FDI_TX_N0 17

FDI_TX_P1 17

FDI_TX_N1 17

FDI_TX_P2 17

FDI_TX_N2 17

FDI_TX_P3 17

FDI_TX_N3 17

FDI_TX_P4 17

FDI_TX_N4 17

FDI_TX_P5 17

FDI_TX_N5 17

FDI_TX_P6 17

FDI_TX_N6 17

FDI_TX_P7 17

FDI_TX_N7 17

DIMM_DQ_CPU_VREF_B 8

DIMM_DQ_CPU_VREF_A 7

11-018-115124 SOCKET.CPU..LGA 1155P

SMD..G/F...BLACK.ACA-ZIF-096-P02....

LEAD-FREE(RoHS/HF).LOTES

1228'10 Jayson :

Part number modified

A A

5

。

20-800-005111 SUBASSY.STEEL....LGA 1155P.....W/BACK

PLATE.ACA-ZIF-082-P23

....LEAD-FREE(RoHS/HF).LOTES

Elitegroup Computer Systems

Elitegroup Computer Systems

01D201-000060 PCH ES0

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Elitegroup Computer Systems

CPU - DMI/FDI/PEG

CPU - DMI/FDI/PEG

CPU - DMI/FDI/PEG

H61H2-M12

H61H2-M12

H61H2-M12

329Wednesday, July 13, 2011

329Wednesday, July 13, 2011

329Wednesday, July 13, 2011

1

1.0

1.0

1.0

5

4

3

2

1

1130'10

pull high By Jayson Del,

Pull high on Page11

VTT_SEL 11

FP_RST_L 13,16

1 2

RN2 51-8P4R-ORN2 51-8P4R-O

3 4

5 6

7 8

V_CPUVTT

STP15STP15

STP14STP14

STP13STP13

STP12STP12

STP11STP11

STP5STP5

STP6STP6

STP10STP10

VCCSA_VID 11

VCCSA_SEN 11

VCC_SEN 9

VSS_SEN 9

VCCIO_SEN 11

VSSIO_SEN 11

VCCAXG_SEN 9

VSSAXG_SEN 9

1

STP31STP31

1

STP26STP26

1

STP27STP27

1

STP29STP29

1

STP22STP22

1

STP24STP24

1

STP23STP23

1

STP4STP4

1

STP3STP3

H_TRST_L

H_TMS

H_TDI

H_TCK

EDS P68/132 has internal PU Jack05/25

V_CPUVTT

CATERR_L

VR_HOT_L

CPU_PWROK

PROC_SEL

DMI/FDI termination voltage:

DC coupled: TX/RX to VCC ISF sampled high

DC coupled: TX/RX TO VSS IF sampled low

AC COUPLED: TX set to VCC/2, RX set to VSS regardless of this strap

1 2

R73 1K-04-OR73 1K-04-O

1 2

R133 51-04R133 51-04

.1U-16VY-04-OBC185 .1U-16VY-04-OBC185

21

2 1

12

.1U-16VY-04BC187 .1U-16VY-04BC187

R110 2.2K-04R110 2.2K-04

V_1P8_SFR

GND

CATERR_L,

CPU_THERMTRIP_L

Pull Up Resistor

2010 MoW05 Remove

GND

GND

R78 0-04-OR78 0-04-O

ER26 2K-1-04ER26 2K-1-04

1 2

ER27 1K-1-04ER27 1K-1-04

1 2

1 2

R230 1K-04R230 1K-04

12

1.1V

V_1P5_SM

B

QN7

QN7

2N3904-S

2N3904-S

E C

GND GND

PECI_PCH 15

.1U-16VY-04-OBC151 .1U-16VY-04-OBC151

21

GND

.1U-16VY-04-OBC76 .1U-16VY-04-OBC76

21

R97

R97

100-1-04

100-1-04

1 2

DIMM_VREF_CPU

R98

R98

100-1-04

100-1-04

1 2

VR_EN

21

C39

C39

2.2U-6VY-06-O

2.2U-6VY-06-O

CK_CPU_100M_P15

CK_CPU_100M_N15

VR_SVID_CK9

VR_SVID_DATAOUT9

VR_SVID_ALERT_L9

CPU_PWROK16

PM_SYNC15

PECI23

VR_HOT_L9

CPU_THERMTRIP_L15

H_SKTOCC_L9,23

PROC_SEL17

STP1STP1

STP8STP8

STP16STP16

STP9STP9

STP20STP20

STP25STP25

2 1

GNDGND

C33

C33

.1U-16VY-04

.1U-16VY-04

STP19STP19

STP17STP17

STP21STP21

STP18STP18

STP28STP28

STP30STP30

STP33STP33

STP32STP32

STP34STP34

STP35STP35

STP7STP7

STP2STP2

change test point for internal PU Jack05/25

TO VRD FOR S0->S5

VR_EN 9

FROM VRD

CK_CPU_100M_P

CK_CPU_100M_N

VR_SVID_CK

VR_SVID_DATAOUT

VR_SVID_ALERT_L

CPU_PWROK

DRAM_PWROK

PM_SYNC

PECI

CATERR_L

VR_HOT_L

CPU_THERMTRIP_L

H_SKTOCC_L

PROC_SEL

DIMM_VREF_CPU

1

CFG_0

1

CFG_1

1

CFG_2

1

CFG_3

1

CFG_4

1

CFG_5

1

CFG_6

1

CFG_7

1

CFG_8

1

CFG_9

1

CFG_10

1

CFG_11

1

CFG_12

1

CFG_13

1

CFG_14

1

CFG_15

1

CFG_16

1

CFG_17

W2

BCLK_0

W1

BCLK#_0

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

F36

RESET#

E38

PM_SYNC

J35

PECI

E37

CATERR#

H34

PROCHOT#

G35

THERMTRIP#

AJ33

SKTOCC#

K32

PROC_SEL

AJ22

SM_VREF

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_016

AY3

RSVD_023

H7

RSVD_028

H8

RSVD_029

SKT_H2_CRB

SKT_H2_CRB

CPUE

CPUE

BALLMAP_REV=1.4

BALLMAP_REV=1.4

VCCP_SELECT

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

5 OF 10

5 OF 10

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

RSVD_001

RSVD_002

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD_024

RSVD_030

RSVD_037

RSVD_036

RSVD_033

RSVD_040

RSVD_039

RSVD_018

RSVD_020

RSVD_038

RSVD_032

RSVD_034

RSVD_035

RSVD_050

RSVD_053

RSVD_051

RSVD_052

P33

VTT_SEL

P34

VCCSA_VID

T2

VCCSA_SEN

A36

VCC_SEN

B36

VSS_SEN

AB4

VCCIO_SEN

AB3

VSSIO_SEN

L32

VCCAXG_SEN

M32

VSSAXG_SEN

L39

H_TDO

L40

M40

L38

J39

K38

K40

E39

C40

D40

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

H_TDI

H_TCK

H_TMS

H_TRST_L

H_PRDY_L

H_PREQ_L

FP_RST_L

XDP_H_CLK_DP

XDP_H_CLK_DN

1

1

1

1

1

1

1

1

TDI

PECI PECI_PCH

D D

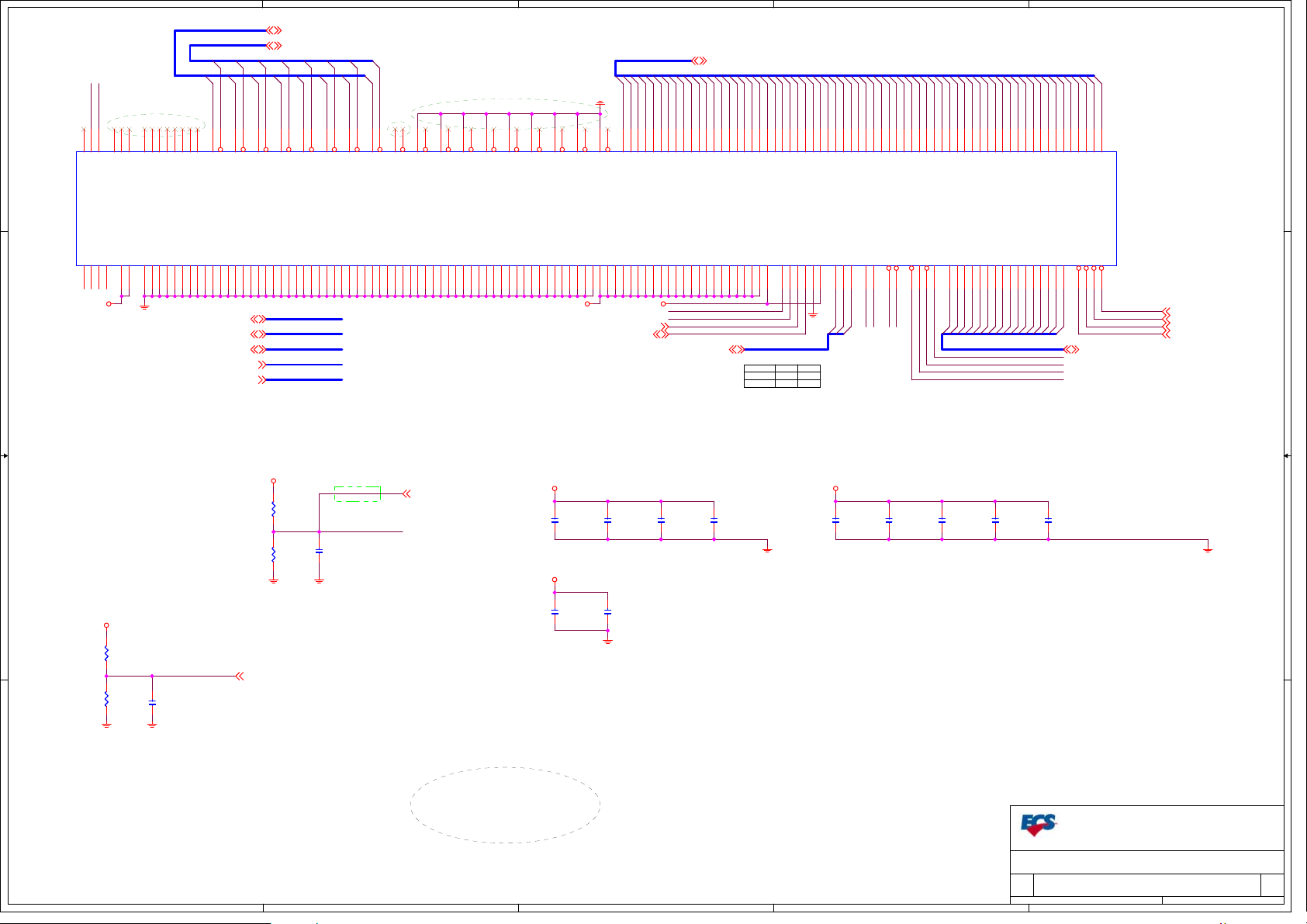

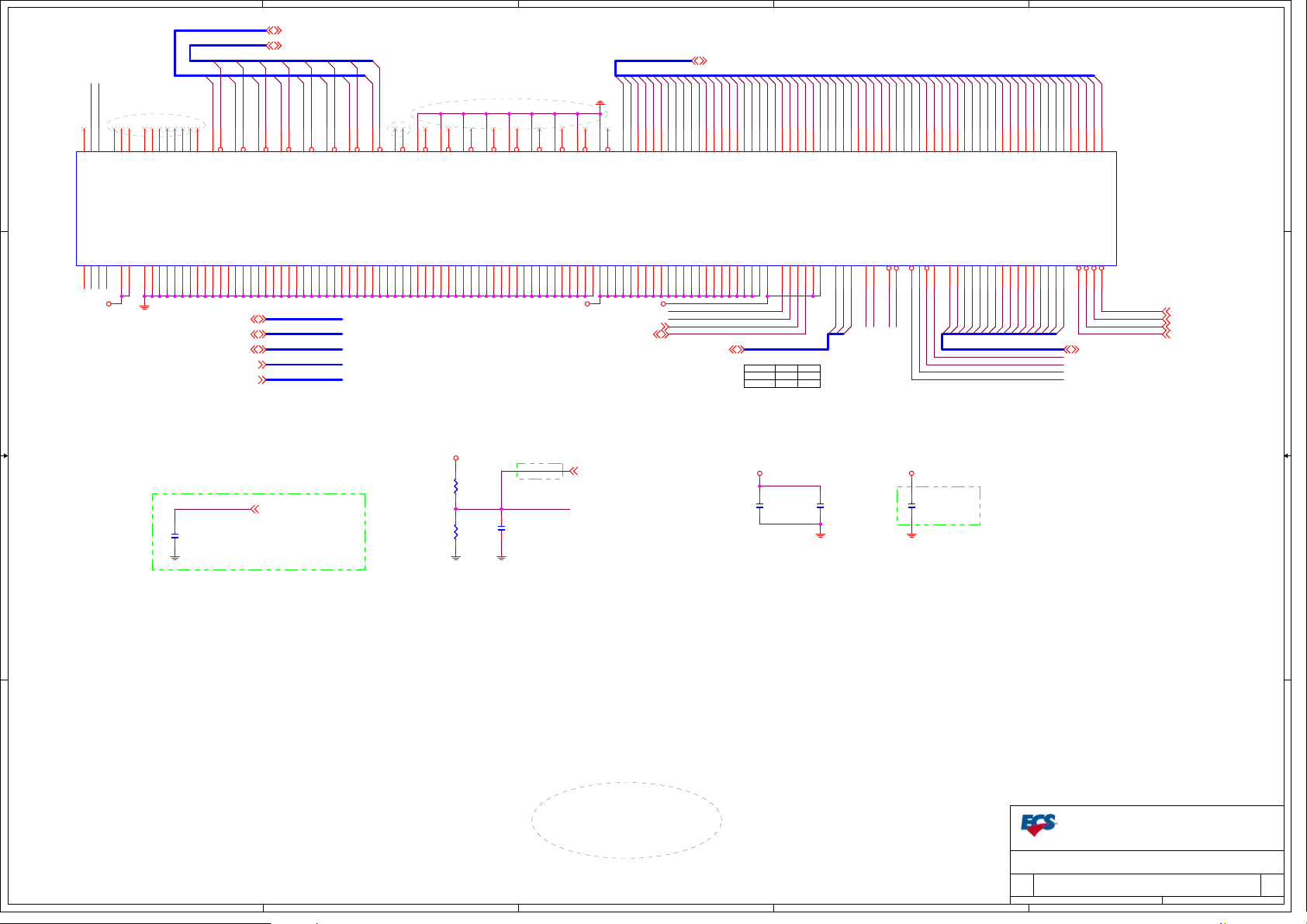

CFG H L

01reserved

2

3

4

5

6

7

8

C C

9

10

11

12

13

14

15

CFG_[0..17] HAVE INTERNAL PULL-UPS

1 X 16

*

2 X 8

DRAM_PWROK16

SIO_PCIRST2_L23

reserved reserved

NORMAL PEGLANE REVERSAL[0], X16

reserved reserved

reserved reserved

reserved reserved reserved

reserved

reserved

reserved

reserved reserved reserved

reserved

reserved

reserved

reserved

REVERSE

*

*

reserved

reserved

reserved

reserved

*

*

reserved

reserved

reserved reserved

reserved

reserved

reserved

reserved

SEL0 SEL1PCIE CONFIG

0111

DRAM_PWROK

SIO_PCIRST2_L CPU_RST_L

GND GND

DESCRIPTION

reserved

PEOFGSEL[0]

PEOFGSEL[1]

reserved

reserved

reserved

reserved

reserved

reserved

CFG[5:6]:

11=DEFAULT X16,

01=2X8,

10=RESERVED,

00=X8,X4,X4

Power Down Sequencing Circuit

B B

R236 10K-04R236 10K-04

1 2

SLP3_L

SLP3_L11,16,23

3VSB

R231

R231

10K-04

10K-04

1 2

B

QN8

QN8

2N3904-S

2N3904-S

E C

GND

CPU_PWROK

20100927

A A

5

Del By Andy lu

4

GND

R216

R216

1K-04

1K-04

1 2

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

3

2

Date: Sheet

CPU - MISC

CPU - MISC

CPU - MISC

H61H2-M12

H61H2-M12

H61H2-M12

1

1.0

1.0

429Wednesday, July 13, 2011

429Wednesday, July 13, 2011

429Wednesday, July 13, 2011

1.0

of

of

of

5

4

3

2

1

CPUC

CPUC

BALLMAP_REV=1.4

BALLMAP_REV=1.4

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SKT_H2_CRB

SKT_H2_CRB

AV27

AY24

AW24

AW23

AV23

AT24

AT23

AU22

AV22

AT22

AV28

AU21

AT21

AW32

AU20

AT20

AW29

AV30

AU28

AY29

AW28

AV20

AU29

AV32

AW30

AU33

AV19

AT19

AU18

AV18

AV31

AU32

AU30

AW33

AY25

AW25

AU24

AU25

AW27

AY27

AV26

AW26

AW18

AV13

AV12

AU12

AU14

AW13

AY13

AU13

AU11

AY12

AW12

DDR3_DRAMRST_L

M_MA_A0

M_MA_A1

M_MA_A2

M_MA_A3

M_MA_A4

M_MA_A5

M_MA_A6

M_MA_A7

M_MA_A8

M_MA_A9

M_MA_A10

M_MA_A11

M_MA_A12

M_MA_A13

M_MA_A14

M_MA_A15

M_WE_A_L

M_CAS_A_L

M_RAS_A_L

M_BS_A0

M_BS_A1

M_BS_A2

M_CS_A_L0

M_CS_A_L1

M_CKE_A0

M_CKE_A1

M_ODT_A0

M_ODT_A1

Del DIMM0 for always populate

DIMM1 first Jack 05/13

M_CLK_A_P0

M_CLK_A_N0

M_CLK_A_P1

M_CLK_A_N1

Desktop dosen't support

ECC

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS#_0

SA_CS#_1

SA_CS#_2

SA_CS#_3

SA_CKE_0

SA_CKE_1

SA_CKE_2

SA_CKE_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_CK_0

SA_CK#_0

SA_CK_1

SA_CK#_1

SA_CK_2

SA_CK#_2

SA_CK_3

SA_CK#_3

SM_DRAMRST#

SA_DQS_8

SA_DQS#_8

SA_ECC_CB_0

SA_ECC_CB_1

SA_ECC_CB_2

SA_ECC_CB_3

SA_ECC_CB_4

SA_ECC_CB_5

SA_ECC_CB_6

SA_ECC_CB_7

DDR_0

DDR_0

3 OF 10

3 OF 10

DDR3 CH.A DDR3 CH.B

AW3

AW5

AW7

AW9

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AW4

AV37

AP38

AK38

AF38

AW8

AV36

AP39

AK39

AF39

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV2

AV5

AU2

AU3

AU5

AY5

AY7

AU7

AV9

AU9

AV7

AY9

AK3

AP3

AV8

AK2

AP2

AV4

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

M_DATA_A0

M_DATA_A1

M_DATA_A2

D D

M_DATA_A[0..63]7

M_DQS_A_P[0..7]7

M_DQS_A_N[0..7]7

M_MA_A[0..15]7

M_BS_A[0..2]7

M_CS_A_L[0..1]7

M_CKE_A[0..1]7

M_ODT_A[0..1]7

M_CLK_A_P[0..1]7

M_CLK_A_N[0..1]7

M_WE_A_L7

M_CAS_A_L7

M_RAS_A_L7

M_DATA_A[0..63]

M_DQS_A_P[0..7]

M_DQS_A_N[0..7]

M_MA_A[0..15]

M_BS_A[0..2]

M_CS_A_L[0..1]

M_CKE_A[0..1]

M_ODT_A[0..1]

M_CLK_A_P[0..1]

M_CLK_A_N[0..1]

M_WE_A_L

M_CAS_A_L

M_RAS_A_L

DDR3 CH.A

C C

B B

DDR3_DRAMRST_L7,8

M_DATA_B[0..63]8

M_DQS_B_P[0..7]8

M_DQS_B_N[0..7]8

M_MA_B[0..15]8

M_BS_B[0..2]8

M_CS_B_L[0..1]8

M_CKE_B[0..1]8

M_ODT_B[0..1]8

M_CLK_B_P[0..1]8

M_CLK_B_N[0..1]8

M_WE_B_L8

M_CAS_B_L8

M_RAS_B_L8

DDR3_DRAMRST_L

M_DATA_B[0..63]

M_DQS_B_P[0..7]

M_DQS_B_N[0..7]

M_MA_B[0..15]

M_BS_B[0..2]

M_CS_B_L[0..1]

M_CKE_B[0..1]

M_ODT_B[0..1]

M_CLK_B_P[0..1]

M_CLK_B_N[0..1]

M_WE_B_L

M_CAS_B_L

M_RAS_B_L

DDR3 CH.B

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

M_DQS_A_P0

M_DQS_A_P1

M_DQS_A_P2

M_DQS_A_P3

M_DQS_A_P4

M_DQS_A_P5

M_DQS_A_P6

M_DQS_A_P7

M_DQS_A_N0

M_DQS_A_N1

M_DQS_A_N2

M_DQS_A_N3

M_DQS_A_N4

M_DQS_A_N5

M_DQS_A_N6

M_DQS_A_N7

Pay Attention to

This Part!

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B13

M_DATA_B9

M_DATA_B11

M_DATA_B15

M_DATA_B12

M_DATA_B8

M_DATA_B14

M_DATA_B10

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B52

M_DATA_B55

M_DATA_B51

M_DATA_B54

M_DATA_B49

M_DATA_B53

M_DATA_B50

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

M_DQS_B_P0

M_DQS_B_P1

M_DQS_B_P2

M_DQS_B_P3

M_DQS_B_P4

M_DQS_B_P5

M_DQS_B_P6

M_DQS_B_P7

M_DQS_B_N0

M_DQS_B_N1

M_DQS_B_N2

M_DQS_B_N3

M_DQS_B_N4

M_DQS_B_N5

M_DQS_B_N6

M_DQS_B_N7

AG7

AG8

AG5

AG6

AM7

AM10

AL10

AM6

AM9

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AH7

AM8

AR8

AN13

AN29

AP33

AL33

AG35

AH6

AP8

AN12

AN28

AR33

AM33

AG34

AJ9

AJ8

AJ6

AJ7

AL7

AL6

AL9

AL8

CPUD

CPUD

BALLMAP_REV=1.4

BALLMAP_REV=1.4

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SKT_H2_CRB

SKT_H2_CRB

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SA_CK[2]

SA_CK[1]

SA_ODT[2]

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS#_0

SB_CS#_1

SB_CS#_2

SB_CS#_3

SB_CKE_0

SB_CKE_1

SB_CKE_2

SB_CKE_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK_0

SB_CK#_0

SB_CK_1

SB_CK#_1

SB_CK_2

SB_CK#_2

SB_CK_3

SB_CK#_3

SB_DQS_8

SB_DQS#_8

SB_ECC_CB_0

SB_ECC_CB_1

SB_ECC_CB_2

SB_ECC_CB_3

SB_ECC_CB_4

SB_ECC_CB_5

SB_ECC_CB_6

SB_ECC_CB_7

DDR_1

DDR_1

4 OF 10

4 OF 10

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

M_MA_B0

M_MA_B1

M_MA_B2

M_MA_B3

M_MA_B4

M_MA_B5

M_MA_B6

M_MA_B7

M_MA_B8

M_MA_B9

M_MA_B10

M_MA_B11

M_MA_B12

M_MA_B13

M_MA_B14

M_MA_B15

M_WE_B_L

M_CAS_B_L

M_RAS_B_L

M_BS_B0

M_BS_B1

M_BS_B2

M_CS_B_L0

M_CS_B_L1

M_CKE_B0

M_CKE_B1

M_ODT_B0

M_ODT_B1

Del DIMM0 for always populate

DIMM1 first Jack 05/13

M_CLK_B_P0

M_CLK_B_N0

M_CLK_B_P1

M_CLK_B_N1

Desktop dosen't support

ECC

A A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

CPU - DDR3

CPU - DDR3

CPU - DDR3

H61H2-M12

H61H2-M12

H61H2-M12

1

1.0

1.0

529Wednesday, July 13, 2011

529Wednesday, July 13, 2011

529Wednesday, July 13, 2011

1.0

of

of

of

5

4

3

2

1

1.5V

MAX 4.5A

AJ13

VDDQ_01

AJ14

VDDQ_02

AJ23

VDDQ_04

AJ24

VDDQ_05

AR20

VDDQ_06

AR21

VDDQ_07

AR22

VDDQ_08

AR23

VDDQ_09

AR24

VDDQ_10

AU19

VDDQ_11

AU23

VDDQ_12

AU27

VDDQ_13

AU31

VDDQ_14

AV21

VDDQ_15

AV24

VDDQ_16

AV25

VDDQ_17

AV29

VDDQ_18

AV33

VDDQ_19

AW31

VDDQ_20

AY23

VDDQ_21

AY26

VDDQ_22

AY28

VDDQ_23

AJ20

VDDQ_03

V_1P5_SM

21

V_CPUVTT

21

V_CPUVTT

21

V_CPUVTT V_CPUVTT

21

MC38

MC38

10U-6VX-08

10U-6VX-08

MC33

MC33

10U-6VX-08

10U-6VX-08

SC8

SC8

10U-6VX-08-X-O

10U-6VX-08-X-O

MC44

MC44

10U-6VX-08

10U-6VX-08

21

MC40

MC40

10U-6VX-08

10U-6VX-08

21

MC25

MC25

10U-6VX-08

10U-6VX-08

21

MC43

MC43

10U-6VX-08-O

10U-6VX-08-O

21

GND

MC36

MC36

10U-6VX-08-O

10U-6VX-08-O

21

MC41

MC41

10U-6VX-08

10U-6VX-08

21

MC42

MC42

10U-6VX-08

10U-6VX-08

MAX 35A

PN

GND

CPUH

CPUH

VBALLMAP_REV=1.4

VBALLMAP_REV=1.4

AB33

VCCAXG_01

AB34

VCCAXG_02

AB35

VCCAXG_03

AB36

VCCAXG_04

AB37

VCCAXG_05

AB38

VCCAXG_06

AB39

VCCAXG_07

AB40

VCCAXG_08

AC33

VCCAXG_09

AC34

VCCAXG_10

AC35

VCCAXG_11

AC36

VCCAXG_12

AC37

VCCAXG_13

AC38

VCCAXG_14

AC39

VCCAXG_15

AC40

VCCAXG_16

T33

VCCAXG_17

T34

VCCAXG_18

T35

VCCAXG_19

T36

VCCAXG_20

T37

VCCAXG_21

T38

VCCAXG_22

T39

VCCAXG_23

T40

VCCAXG_24

U33

VCCAXG_25

U34

VCCAXG_26

U35

VCCAXG_27

U36

VCCAXG_28

U37

VCCAXG_29

U38

VCCAXG_30

U39

VCCAXG_31

U40

VCCAXG_32

W33

VCCAXG_33

W34

VCCAXG_34

W35

VCCAXG_35

W36

VCCAXG_36

W37

VCCAXG_37

W38

VCCAXG_38

Y33

VCCAXG_39

Y34

VCCAXG_40

Y35

VCCAXG_41

Y36

VCCAXG_42

Y37

VCCAXG_43

Y38

VCCAXG_44

SKT_H2_CRB

SKT_H2_CRB

21

MC39

MC39

10U-6VX-08

10U-6VX-08

GND

21

SC9

SC9

10U-6VX-08-X-O

10U-6VX-08-X-O

GND GND

SC6

SC6

100U-2V-9M-X-O

100U-2V-9M-X-O

20101014

Add By Andy lu

3

8 OF 10

8 OF 10

V_1P8_SFR

BC109

BC109

.1U-10VX-04

.1U-10VX-04

2 1

V_CPUVTT

BC66

BC66

.1U-16VY-04

.1U-16VY-04

2 1

BC91

BC91

.1U-16VY-04

.1U-16VY-04

2 1

2 1

GND

2 1

2 1

MC37

MC37

10U-6VX-08

10U-6VX-08

BC77

BC77

.1U-16VY-04

.1U-16VY-04

BC85

BC85

.1U-16VY-04

.1U-16VY-04

BC80

BC80

.1U-16VY-04

.1U-16VY-04

2 1

BC86

BC86

.1U-16VY-04

.1U-16VY-04

2 1

BC69

BC69

.1U-16VY-04

.1U-16VY-04

2 1

BC68

BC68

.1U-16VY-04-O

.1U-16VY-04-O

2 1

CPUI

CPUI

BALLMAP_REV=1.4

BALLMAP_REV=1.4

A17

VSS_001

A23

VSS_002

A26

VSS_003

A29

VSS_004

A35

VSS_005

AA33

VSS_006

AA34

VSS_007

AA35

VSS_008

AA36

VSS_009

AA37

VSS_010

AA38

VSS_011

AA6

VSS_012

AB5

VSS_013

AC1

VSS_014

AC6

VSS_015

AD33

VSS_016

AD36

VSS_017

AD38

VSS_018

AD39

VSS_019

AD40

VSS_020

AD5

VSS_021

AD8

VSS_022

AE3

VSS_023

AE33

VSS_024

AE36

VSS_025

AF1

VSS_026

AF34

VSS_027

AF36

VSS_028

AF37

VSS_029

AF40

VSS_030

AF5

VSS_031

AF6

VSS_032

AF7

VSS_033

AG36

VSS_034

AH2

VSS_035

AH3

VSS_036

AH33

VSS_037

AH36

VSS_038

AH37

VSS_039

AH38

VSS_040

AH39

VSS_041

AH40

VSS_042

AH5

VSS_043

AH8

VSS_044

AJ12

VSS_045

AJ15

VSS_046

AJ18

VSS_047

AJ21

VSS_048

AJ25

VSS_049

AJ27

VSS_050

AJ36

VSS_051

AJ5

VSS_052

AK1

VSS_053

AK10

VSS_054

AK13

VSS_055

AK14

VSS_056

AK16

VSS_057

AK22

VSS_058

AK28

VSS_059

AK31

VSS_060

AK32

VSS_061

AK33

VSS_062

AK34

VSS_063

AK35

VSS_064

AK36

VSS_065

AK37

VSS_066

AK4

VSS_067

AK40

VSS_068

AK5

VSS_069

AK6

VSS_070

AK7

VSS_071

AK8

VSS_072

AK9

VSS_073

AL11

VSS_074

AL14

VSS_075

AL17

VSS_076

AL19

VSS_077

AL24

VSS_078

AL27

VSS_079

AL30

VSS_080

AL36

VSS_081

AL5

VSS_082

AM1

VSS_083

AM11

VSS_084

AM14

VSS_085

AM17

VSS_086

AM2

VSS_087

AM21

VSS_088

AM23

VSS_089

AM25

VSS_090

A4

VSS_NCTF_01

AV39

VSS_NCTF_02

SKT_H2_CRB

SKT_H2_CRB

BC65

BC65

.1U-16VY-04

.1U-16VY-04

2 1

BC83

BC83

.1U-16VY-04-O

.1U-16VY-04-O

2 1

GND

VSS_091

VSS_092

VSS_093

VSS_094

VSS_095

VSS_096

VSS_097

VSS_098

VSS_099

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

9 OF 10

9 OF 10

20100929

Change By Andy lu

2

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

CPUJ

CPUJ

BALLMAP_REV=1.4

BALLMAP_REV=1.4

AV11

VSS_181

AV14

VSS_182

AV17

VSS_183

AV3

VSS_184

AV35

VSS_185

AV38

VSS_186

AV6

VSS_187

AW10

VSS_188

AW11

VSS_189

AW14

VSS_190

AW16

VSS_191

AW36

VSS_192

AW6

VSS_193

AY11

VSS_194

AY14

VSS_195

AY18

VSS_196

AY35

VSS_197

AY4

VSS_198

AY6

VSS_199

AY8

VSS_200

B10

VSS_201

B13

VSS_202

B14

VSS_203

B17

VSS_204

B23

VSS_205

B26

VSS_206

B29

VSS_207

B32

VSS_208

B35

VSS_209

B38

VSS_210

B6

VSS_211

C11

VSS_212

C12

VSS_213

C17

VSS_214

C20

VSS_215

C23

VSS_216

C26

VSS_217

C29

VSS_218

C32

VSS_219

C35

VSS_220

C7

VSS_221

C8

VSS_222

D17

VSS_223

D2

VSS_224

D20

VSS_225

D23

VSS_226

D26

VSS_227

D29

VSS_228

D32

VSS_229

D37

VSS_230

D39

VSS_231

D4

VSS_232

D5

VSS_233

D9

VSS_234

E11

VSS_235

E12

VSS_236

E17

VSS_237

E20

VSS_238

E23

VSS_239

E26

VSS_240

E29

VSS_241

E32

VSS_242

E36

VSS_243

E7

VSS_244

E8

VSS_245

F1

VSS_246

F10

VSS_247

F13

VSS_248

F14

VSS_249

F17

VSS_250

F2

VSS_251

F20

VSS_252

F23

VSS_253

F26

VSS_254

F29

VSS_255

F35

VSS_256

F37

VSS_257

F39

VSS_258

F5

VSS_259

F6

VSS_260

F9

VSS_261

G11

VSS_262

G12

VSS_263

G17

VSS_264

G20

VSS_265

G23

VSS_266

G26

VSS_267

G29

VSS_268

G34

VSS_269

G7

VSS_270

AY37

VSS_NCTF_03

B3

VSS_NCTF_04

SKT_H2_CRB

SKT_H2_CRB

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

10 of 10

10 of 10

CPU - PWR

CPU - PWR

CPU - PWR

H61H2-M12

H61H2-M12

H61H2-M12

1

G8

H1

H17

H2

H20

H23

H26

H29

H33

H35

H37

H39

H5

H6

H9

J11

J17

J20

J23

J26

J29

J32

K1

K12

K13

K14

K17

K2

K20

K23

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

GNDGNDGND GND

629Wednesday, July 13, 2011

629Wednesday, July 13, 2011

629Wednesday, July 13, 2011

of

of

of

1.0

1.0

1.0

V_SA

V_1P8_SFR

21

SC4

SC4

10U-6VX-08-X-O

10U-6VX-08-X-O

21

MC21

MC21

10U-6VX-08

10U-6VX-08

20101014

Add By Andy lu

1.05V/1.00V

MAX 8.5A

V_CPUVTT VAXGVCORE V_1P5_SM

V_SA

21

GND

21

21

21

SC1

SC1

10U-10VY-08-X-O

10U-10VY-08-X-O

M13

A11

A7

AA3

AB8

AF8

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

B9

D10

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

H10

H11

H12

J10

K10

K11

L11

L12

M10

M11

M12

AK11

AK12

MC15

MC15

10U-6VX-08

10U-6VX-08

SC7

SC7

10U-6VX-08-X-O

10U-6VX-08-X-O

MC22

MC22

10U-6VX-08

10U-6VX-08

CPUG

CPUG

BALLMAP_REV=1.4

BALLMAP_REV=1.4

VCCIO_34

VCCIO_01

VCCIO_02

VCCIO_03

VCCIO_04

VCCIO_05

VCCIO_06

VCCIO_07

VCCIO_08

VCCIO_09

VCCIO_10

VCCIO_11

VCCIO_12

VCCIO_13

VCCIO_14

VCCIO_15

VCCIO_16

VCCIO_17

VCCIO_18

VCCIO_19

VCCIO_20

VCCIO_21

VCCIO_22

VCCIO_23

VCCIO_24

VCCIO_25

VCCIO_26

VCCIO_27

VCCIO_28

VCCIO_29

VCCIO_30

VCCIO_31

VCCIO_32

VCCIO_33

VCCIO_35

VCCIO_36

VCCIO_37

VCCIO_38

VCCIO_39

VCCIO_40

VCCIO_41

VCCIO_42

VCCIO_43

VCCIO_44

VCCIO_45

VCCSA_01

VCCSA_02

VCCSA_03

VCCSA_04

VCCSA_05

VCCSA_06

VCCSA_07

VCCSA_08

VCCSA_09

VCCSA_10

VCCSA_11

VCCPLL_01

VCCPLL_02

SKT_H2_CRB

SKT_H2_CRB

PN

SC5

SC5

100U-2V-9M-X-O

100U-2V-9M-X-O

GND

20101021

Add By Andy lu

21

MC16

MC16

10U-6VX-08

10U-6VX-08

GND

PN

SC3

SC3

100U-2V-9M-X-O

100U-2V-9M-X-O

GND

20101014

Add By Andy lu

4

POWER

POWER

7 OF 10

7 OF 10

CPUF

MAX 112A

A12

A13

A14

A15

A16

A18

A24

A25

A27

A28

B15

B16

B18

B24

B25

B27

B28

B30

B31

B33

B34

C15

C16

C18

C19

C21

C22

C24

C25

C27

C28

C30

C31

C33

C34

C36

D13

D14

D15

D16

D18

D19

D21

D22

D24

D25

D27

D28

D30

D31

D33

D34

D35

D36

E15

E16

E18

E19

E21

E22

E24

E25

E27

E28

E30

E31

E33

E34

E35

F15

F16

F18

F19

F21

F22

F24

F25

F27

F28

F30

F31

VAXG

21

MC18

MC18

10U-6VX-08

10U-6VX-08

VCORE

21

MC17

MC17

10U-6VX-08

10U-6VX-08

VCORE

21

MC19

MC19

10U-6VX-08

10U-6VX-08

20100929

Change By Andy lu

CPUF

BALLMAP_REV=1.4

BALLMAP_REV=1.4

VCC_001

VCC_002

VCC_003

VCC_004

VCC_005

VCC_006

VCC_007

VCC_008

VCC_009

VCC_010

VCC_011

VCC_012

VCC_013

VCC_014

VCC_015

VCC_016

VCC_017

VCC_018

VCC_019

VCC_020

VCC_021

VCC_022

VCC_023

VCC_024

VCC_025

VCC_026

VCC_027

VCC_028

VCC_029

VCC_030

VCC_031

VCC_032

VCC_033

VCC_034

VCC_035

VCC_036

VCC_037

VCC_038

VCC_039

VCC_040

VCC_041

VCC_042

VCC_043

VCC_044

VCC_045

VCC_046

VCC_047

VCC_048

VCC_049

VCC_050

VCC_051

VCC_052

VCC_053

VCC_054

VCC_055

VCC_056

VCC_057

VCC_058

VCC_059

VCC_060

VCC_061

VCC_062

VCC_063

VCC_064

VCC_065

VCC_066

VCC_067

VCC_068

VCC_069

VCC_070

VCC_071

VCC_072

VCC_073

VCC_074

VCC_075

VCC_076

VCC_077

VCC_078

VCC_079

VCC_080

VCC_081

SKT_H2_CRB

SKT_H2_CRB

6 OF 10

6 OF 10

VCC_082

VCC_083

VCC_084

VCC_085

VCC_086

VCC_087

VCC_088

VCC_089

VCC_090

VCC_091

VCC_092

VCC_093

VCC_094

VCC_095

VCC_096

VCC_097

VCC_098

VCC_099

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

MC34/MC107 move to Vaxg path as vendor 08/04

MC23

MC23

10U-6VX-08-O

10U-6VX-08-O

MC27

MC27

10U-6VX-08-O

10U-6VX-08-O

MC20

MC20

10U-6VX-08

10U-6VX-08

5

21

MC24

MC24

10U-6VX-08

10U-6VX-08

21

MC31

MC31

10U-6VX-08-O

10U-6VX-08-O

21

MC26

MC26

10U-10VY-08-O

10U-10VY-08-O

21

21

21

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

21

MC32

MC32

10U-6VX-08

10U-6VX-08

21

MC30

MC30

10U-6VX-08

10U-6VX-08

0.925V/0.85V

MAX 8.8A

1.8V

MAX 1A

21

SC2

SC2

10U-10VY-08-X-O

10U-10VY-08-X-O

VCORE

D D

C C

B B

A A

5

M_DQS_A_P[0..7]

M_DQS_A_N[0..7]

Desktop dosen't support

79

198

V_SM_VTT

0.75V

MAX 1A

ECC

M_ODT_A0

M_ODT_A1

195

ODT177ODT0

RSVD

FREE1

FREE2

FREE349FREE448VTT

187

167

68

53

NC/PAR IN

NC/ERR OUT

240

120

CB(0)39CB(1)40CB(2)45CB(3)46CB(4)

NC/TEST4

VSS

VTT

239

235

GND

VSS

M_DQS_A_P0

M_DQS_A_P1

M_DQS_A_N0

158

159

164

165

7

16

6

CB(5)

CB(6)

CB(7)

DQS(0)

DSQ(1)

DQS*(0)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

232

229

226

223

220

217

214

211

208

205

202

M_ODT_A[0..1]5

M_CS_A_L[0..1]5

M_CKE_A[0..1]5

M_CLK_A_P[0..1]5

M_CLK_A_N[0..1]5

D D

C C

M_DQS_A_P2

M_DQS_A_N1

M_DQS_A_N2

25

15

24

DSQ(2)

DSQ*(1)

DSQ*(2)

VSS

VSS

VSS

VSS

199

166

163

160

157

M_DQS_A_P[0..7] 5

M_DQS_A_N[0..7] 5

M_DQS_A_P3

M_DQS_A_P4

M_DQS_A_N3

M_DQS_A_N4

34

85

33

84

DSQ(3)

DQS(4)

DSQ*(3)

DQS*(4)

VSS

VSS

VSS

VSS

VSS

VSS

154

151

148

145

142

M_ODT_A[0..1]

M_CS_A_L[0..1]

M_CKE_A[0..1]

M_CLK_A_P[0..1]

M_CLK_A_N[0..1]

M_DQS_A_P5

M_DQS_A_N5

94

93

DQS(5)

DQS*(5)

VSS

VSS

VSS

139

136

133

130

4

The processor memory controller does not

have any DDR3 Data Mask (DM) signals

for either channel. As a result the DM[8:0]

pins of each DDR3 DIMM connector must

be tied directly to ground.

M_DQS_A_N7

M_DQS_A_P6

M_DQS_A_P7

M_DQS_A_N6

126

125

135

144

153

204

203

NC/DQS12*

NC/DQS13*

DM4/DQS13

1.5V

MAX 15A

S3 1.0A

213

212

NC/DQS14*

DM5/DQS14

VSS

134

143

103

112

43

102

111

42

DSQ(6)

DQS(7)

DQS(8)

DSQ*(6)

DQS*(7)

DQS*(8)

NC/DQS9*

DM0/DQS9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS98VSS95VSS92VSS89VSS86VSS83VSS80VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS2VDD

127

124

121

119

116

113

110

107

104

101

152

NC/DQS10*

NC/DQS11*

DM1/DQS10

DM2/DQS11

DM3/DQS12

CHANNEL A DIMMs

3

M_DATA_A[0..63]

GND

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A0

222

231

221

DM6/DQS15

162

230

161

NC/DQS15*

NC/DQS16*

DM7/DQS16

DM8/DQS17

VDD

197

122

123

DQ(0)3DQ(1)4DQ(2)9DQ(3)10DQ(4)

DQ(5)

NC/DQS17*

VDD

VDD

VDD

VDD

VDD

VDD

186

183

182

179

176

189

VCC3V_1P5_SM

SMBCLK8,16,20,26

SMBDATA8,16,20,26

VDD

194

191

M_DATA_A[0..63] 5

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A6

M_DATA_A7

M_DATA_A8

128

129

12

13

DQ(6)

DQ(7)

DQ(8)

DQ(9)

VDD

VDD

VDD78VDD75VDD69VDD66VDD65VDD62VDD60VDD57VDDSPD

173

170

DIMM_VREF_CA_A

DIMM_VREF_DQ_A

SMBCLK

SMBDATA

M_BS_A[0..2]5

M_DATA_A16

18

131

132

137

138

DQ(10)

DQ(11)19DQ(12)

DQ(13)

DQ(14)

DQ(15)

VDD

72

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A20

M_DATA_A21

M_DATA_A22

140

141

146

147

DQ(21)

DQ(22)

DQ(23)

SCL

118

238

M_DATA_A26

DQ(24)30DQ(25)31DQ(26)36DQ(27)37DQ(28)

SDA

SA1

117

237

GND

SA0SA1

HLDIMM1

M_DATA_A17

M_DATA_A18

M_DATA_A19

DQ(16)21DQ(17)22DQ(18)27DQ(19)28DQ(20)

VDD54VDD51VREFCA67VREFDQ1BA2

236

M_BS_A[0..2]

CH.A

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

149

150

155

DQ(29)

SA0

BA1

52

190

M_BS_A1

M_BS_A2

M_BS_A0

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

156

DQ(30)

DQ(31)

DQ(32)81DQ(33)82DQ(34)87DQ(35)88DQ(36)

BA071CKE1

CKE050S1*76S0*

169

M_CKE_A1

M_CKE_A0

2

M_DATA_A37

M_DATA_A38

M_DATA_A35

M_DATA_A36

200

201

206

DQ(37)

DQ(38)

CK1/NU*64CK1/NU63CK0*

193

M_CS_A_L0

M_CS_A_L1

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

207

DQ(39)

DQ(40)90DQ(41)91DQ(42)96DQ(43)97DQ(44)

CK0

185

184A0188A1181

M_MA_A0

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

209

210

215

216

DQ(45)

DQ(46)

DQ(47)

A261A3

A459A558A6

180

M_MA_A1

M_MA_A3

M_MA_A2

M_MA_A5

M_MA_A4

M_DATA_A51

M_DATA_A52

M_DATA_A49

M_DATA_A50

100

105

106

218

DQ(48)99DQ(49)

DQ(50)

DQ(51)

A756A8

178

177A9175

M_MA_A8

M_MA_A7

M_MA_A6

M_MA_A9

M_MA_A[0..15]

M_CLK_A_P0

M_CLK_A_N0

M_CLK_A_P1

M_CLK_A_N1

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

219

224

225

108

DQ(52)

DQ(53)

DQ(54)

DQ(55)

A10/AP70A1155A12

174

196

M_MA_A12

M_MA_A13

M_MA_A10

M_MA_A11

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

109

114

115

227

DQ(56)

DQ(57)

DQ(58)

DQ(59)

A13

A14

A15

172

171

168

M_MA_A15

M_MA_A14

M_DATA_A61

M_DATA_A62

M_DATA_A63

228

233

234

DQ(60)

DQ(61)

DQ(62)

DQ(63)

CAS*74RAS*

WE*

RESET*

73

192

M_WE_A_L

M_RAS_A_L

M_CAS_A_L

DDR3_DRAMRST_L

M_MA_A[0..15] 5

1

DDR3_1DDR3-240P-GY DDR3_1DDR3-240P-GY

M_WE_A_L 5

M_RAS_A_L 5

M_CAS_A_L 5

DDR3_DRAMRST_L 5,8

V_1P5_SM

ER51

ER51

1K-1-04

1K-1-04

1 2

ER52

ER52

1K-1-04

1K-1-04

B B

V_1P5_SM

12

ER55

ER55

1K-1-04

1K-1-04

0.75V

12

ER54

ER54

1K-1-04

1K-1-04

GND GND

A A

DIMM_VREF_CA_A

BC179

BC179

.1U-10VX-04

.1U-10VX-04

2 1

1 2

DIMM_VREF_CA_A 8

20100929

Short By Andy lu

DIMM_VREF_DQ_A

BC171

BC171

.1U-10VX-04

.1U-10VX-04

2 1

GNDGND

DIMM_DQ_CPU_VREF_A 3

V_1P5_SM

2 1

V_SM_VTT

2 1

MC83

MC83

10U-6VX-08

10U-6VX-08

MC74

MC74

10U-10VY-08

10U-10VY-08

2 1

2 1

GND

MC69

MC69

10U-6VX-08

10U-6VX-08

BC193

BC193

.1U-16VY-04

.1U-16VY-04

MC76

MC76

10U-6VX-08

10U-6VX-08

2 1

MC82

MC82

10U-6VX-08

10U-6VX-08

2 1

GND

V_1P5_SM

2 1

BC172

BC172

.1U-16VY-04

.1U-16VY-04

BC177

BC177

.1U-16VY-04

.1U-16VY-04

2 1

BC183

BC183

.1U-16VY-04

.1U-16VY-04

2 1

BC180

BC180

.1U-16VY-04

.1U-16VY-04

2 1

MC75

MC75

.1U-16VY-04

.1U-16VY-04

2 1

GND

Del DIMM1 for always populate DIMM2 first Jack 05/13

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

DDR3 - CH_A_DIMM1

DDR3 - CH_A_DIMM1

DDR3 - CH_A_DIMM1

H61H2-M12

H61H2-M12

H61H2-M12

1

1.0

1.0

729Wednesday, July 13, 2011

729Wednesday, July 13, 2011

729Wednesday, July 13, 2011

1.0

of

of

of

5

M_DQS_B_P[0..7]

M_DQS_B_N[0..7]

Desktop dosen't support

79

RSVD

FREE1

198

V_SM_VTT

ECC

M_ODT_B0

M_ODT_B1

68

195

ODT177ODT0

FREE2

FREE349FREE448VTT

187

167

53

NC/TEST4

NC/PAR IN

NC/ERR OUT

VTT

240

120

GND

CB(0)39CB(1)40CB(2)45CB(3)46CB(4)

VSS

VSS

239

235

M_DQS_B_P0

M_DQS_B_P1

M_DQS_B_N0

158

159

164

165

7

16

6

CB(5)

CB(6)

CB(7)

DQS(0)

DSQ(1)

DQS*(0)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

232

229

226

223

220

217

214

211

208

205

202

M_ODT_B[0..1]5

M_CS_B_L[0..1]5

M_CKE_B[0..1]5

M_CLK_B_P[0..1]5

M_CLK_B_N[0..1]5

D D

0.75V

C C

MAX 1A

M_DQS_B_N1

M_DQS_B_N2

M_DQS_B_P2

25

15

24

DSQ(2)

DSQ*(1)

DSQ*(2)

VSS

VSS

VSS

VSS

199

166

163

160

157

M_DQS_B_P[0..7] 5

M_DQS_B_N[0..7] 5

M_DQS_B_N3

M_DQS_B_N4

M_DQS_B_P3

M_DQS_B_P4

34

85

33

84

DSQ(3)

DQS(4)

DSQ*(3)

DQS*(4)

VSS

VSS

VSS

VSS

VSS

VSS

154

151

148

145

142

M_ODT_B[0..1]

M_CS_B_L[0..1]

M_CKE_B[0..1]

M_CLK_B_P[0..1]

M_CLK_B_N[0..1]

M_DQS_B_N5

M_DQS_B_P5

94

93

DQS(5)

DQS*(5)

VSS

VSS

VSS

139

136

133

130

4

The processor memory controller does not

have any DDR3 Data Mask (DM) signals

for either channel. As a result the DM[8:0]

pins of each DDR3 DIMM connector must

be tied directly to ground.

M_DQS_B_P6

M_DQS_B_P7

M_DQS_B_N6

M_DQS_B_N7

126

125

135

144

153

204

203

NC/DQS12*

NC/DQS13*

DM4/DQS13

1.5V

MAX 15A

S3 1.0A

213

212

DM5/DQS14

NC/DQS14*

V_1P5_SM

VSS

134

143

103

112

43

102

111

42

DSQ(6)

DQS(7)

DQS(8)

DSQ*(6)

DQS*(7)

DQS*(8)

NC/DQS9*

DM0/DQS9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS98VSS95VSS92VSS89VSS86VSS83VSS80VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS2VDD

127

124

121

119

116

113

110

107

104

101

152

NC/DQS10*

NC/DQS11*

DM1/DQS10

DM2/DQS11

DM3/DQS12

CHANNEL B DIMMs

3

M_DATA_B[0..63]

GND

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

222

231

221

DM6/DQS15

162

230

161

NC/DQS15*

NC/DQS16*

DM7/DQS16

DM8/DQS17

VDD

197

122

123

DQ(0)3DQ(1)4DQ(2)9DQ(3)10DQ(4)

DQ(5)

NC/DQS17*

VDD

VDD

VDD

VDD

VDD

VDD

186

183

182

179

176

189

VCC3

SMBCLK7,16,20,26

SMBDATA7,16,20,26

VDD

194

191

M_DATA_B[0..63] 5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B16

128

129

12

13

18

131

132

137

138

DQ(6)

DQ(7)

DQ(8)

DQ(9)

DQ(10)

DQ(11)19DQ(12)

DQ(13)

DQ(14)

DQ(15)

VDD

VDD

VDD78VDD75VDD69VDD66VDD65VDD62VDD60VDD57VDDSPD

VDD

72

173

170

DIMM_VREF_CA_B

DIMM_VREF_DQ_B

SMBCLK

SMBDATA

M_BS_B[0..2]5

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

140

141

146

147

DQ(16)21DQ(17)22DQ(18)27DQ(19)28DQ(20)

DQ(21)

DQ(22)

DQ(23)

DQ(24)30DQ(25)31DQ(26)36DQ(27)37DQ(28)

SCL

SDA

118

238

237

HH

SA1

117

VDD54VDD51VREFCA67VREFDQ1BA2

236

M_BS_B[0..2]

CH.B SA1 SA0

DIMM1

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

149

150

155

DQ(29)

SA0

BA1

52

190

M_BS_B2

M_BS_B1

M_BS_B0

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

156

DQ(30)

DQ(31)

DQ(32)81DQ(33)82DQ(34)87DQ(35)88DQ(36)

BA071CKE1

CKE050S1*76S0*

169

M_CKE_B1

M_CKE_B0

2

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

200

201

206

DQ(37)

DQ(38)

CK1/NU*64CK1/NU63CK0*

193

M_CS_B_L1

M_CS_B_L0

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

207

DQ(39)

DQ(40)90DQ(41)91DQ(42)96DQ(43)97DQ(44)

CK0

185

184A0188A1181

M_MA_B0

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

209

210

215

216

DQ(45)

DQ(46)

DQ(47)

A261A3

A459A558A6

180

M_MA_B1

M_MA_B2

M_MA_B5

M_MA_B3

M_MA_B4

M_DATA_B49

M_DATA_B50

M_DATA_B51

M_DATA_B52

100

105

106

218

DQ(48)99DQ(49)

DQ(50)

DQ(51)

A756A8

178

177A9175

M_MA_B8

M_MA_B9

M_MA_B6

M_MA_B7

M_MA_B[0..15]

M_CLK_B_P0

M_CLK_B_N0

M_CLK_B_P1

M_CLK_B_N1

M_DATA_B53

M_DATA_B54

M_DATA_B55

M_DATA_B56

219

224

225

108

DQ(52)

DQ(53)

DQ(54)

DQ(55)

A10/AP70A1155A12

174

196

M_MA_B11

M_MA_B10

M_MA_B12

M_MA_B13

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

109

114

115

227

DQ(56)

DQ(57)

DQ(58)

DQ(59)

A13

A14

A15

172

171

168

M_MA_B15

M_MA_B14

M_DATA_B61

M_DATA_B62

M_DATA_B63

228

233

234

DQ(60)

DQ(61)

DQ(62)

DQ(63)

CAS*74RAS*

WE*

RESET*

73

192

M_WE_B_L

M_RAS_B_L

M_CAS_B_L

DDR3_DRAMRST_L

M_MA_B[0..15] 5

1

DDR3_2DDR3-240P-GY DDR3_2DDR3-240P-GY

M_WE_B_L 5

M_RAS_B_L 5

M_CAS_B_L 5

DDR3_DRAMRST_L 5,7

V_1P5_SM

20100929

Change By Andy lu

DIMM_VREF_CA_B DIMM_VREF_DQ_B

BC192

BC192

.1U-10VX-04

.1U-10VX-04

2 1

B B

A A

GND

5

DIMM_VREF_CA_A 7

4

ER53

ER53

1K-1-04

1K-1-04

1 2

ER56

ER56

1K-1-04

1K-1-04

1 2

GND GND

20100929

Short By Andy lu

DIMM_DQ_CPU_VREF_B 3

BC182

BC182

.1U-10VX-04

.1U-10VX-04

2 1

Del DIMM3 for always populate DIMM4 first Jack 05/13

3

V_SM_VTT

2 1

MC84

MC84

10U-10VY-08-O

10U-10VY-08-O

BC178

BC178

.1U-16VY-04-O

.1U-16VY-04-O

2 1

GND

VCC3

2 1

GND

2

BC181

BC181

.1U-16VY-04-O

.1U-16VY-04-O

20100929

Change By Andy lu

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DDR3 - CH_B_DIMM3

DDR3 - CH_B_DIMM3

DDR3 - CH_B_DIMM3

H61H2-M12

H61H2-M12

H61H2-M12

1

829Wednesday, July 13, 2011

829Wednesday, July 13, 2011

829Wednesday, July 13, 2011

of

of

of

1.0

1.0

1.0

5

External Connection

VCCVCC

V_CPUVTT

VCC3

VIN VIN

5VSB 5VSB

UG110

D D

C C

B B

A A

LG110

UG210

LG210

PWM310

SPWM10

PHASE110

PHASE210

PHASE310

PHASE_GT10

VOUT110

VOUT210

VOUT310

VOUT_GT10

VR_SVID_ALERT_L4

VR_SVID_CK4

VR_SVID_DATAOUT4

VR_HOT_L4

VCC_SEN4

VSS_SEN4

VCCAXG_SEN4

VSSAXG_SEN4

VR_READY16

VR_EN4

H_SKTOCC_L4,23

VGT_VCCSENSE

12

BC162

BC162

1000P-04-O

1000P-04-O

VGT_VSSSENSE

12

BC159

BC159

1000P-04-O

1000P-04-O

1130'10 By Jayson add.

Page23, H_SKTOCC_N has

place pull high

resistor.

H_SKTOCC_N

VCOREVCORE

V_CPUVTT

+12V_4P+12V_4P

VCC3

VAXGVAXG

UG1

LG1

UG2

LG2

PWM3

SPWM

PHASE1

PHASE2

PHASE3

PHASE_GT

VOUT1

VOUT2

VOUT3

VOUT_GT

ALERT

SCLK

SDATA