Page 1

5

4

3

2

1

H61H2-LM5

D D

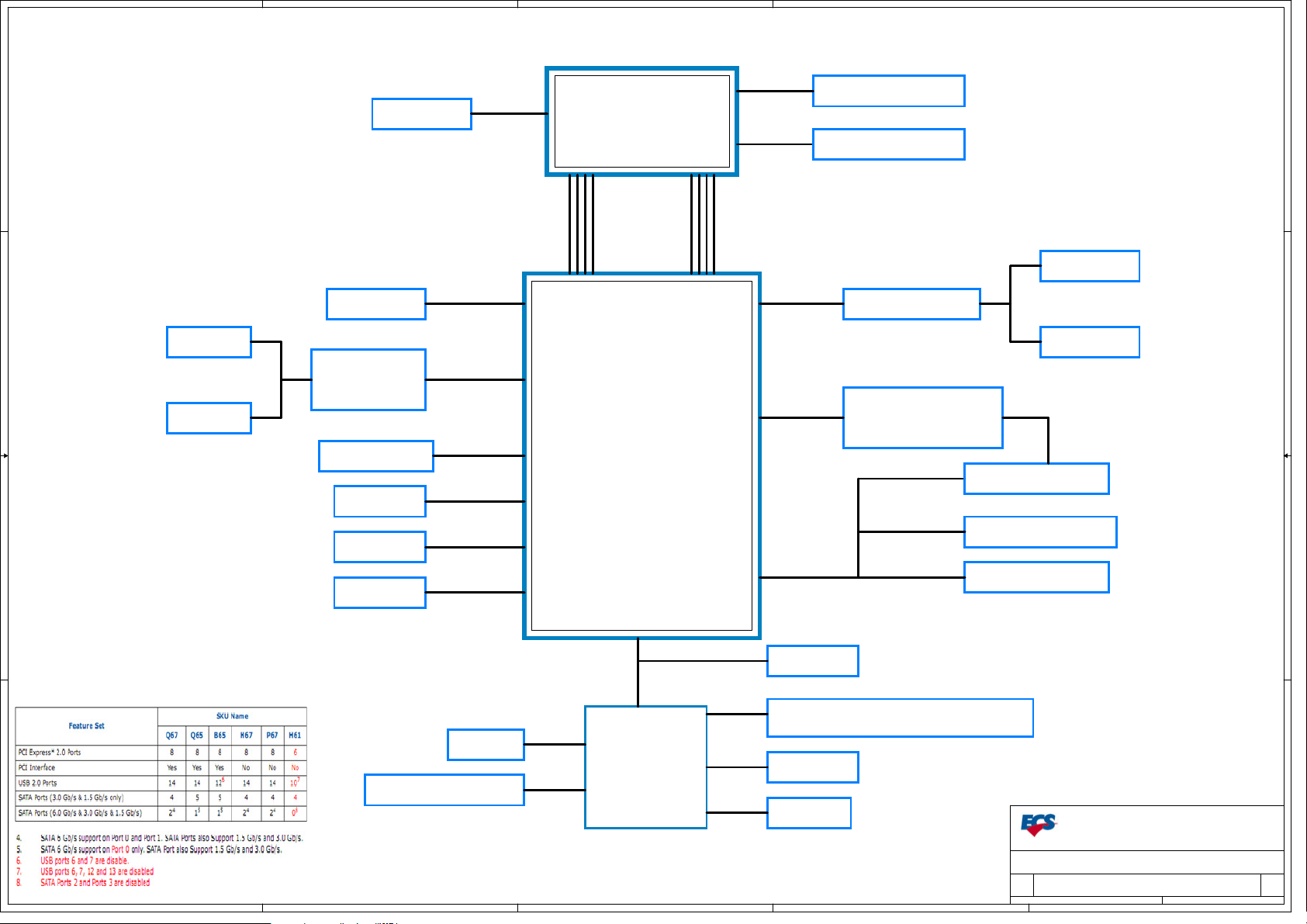

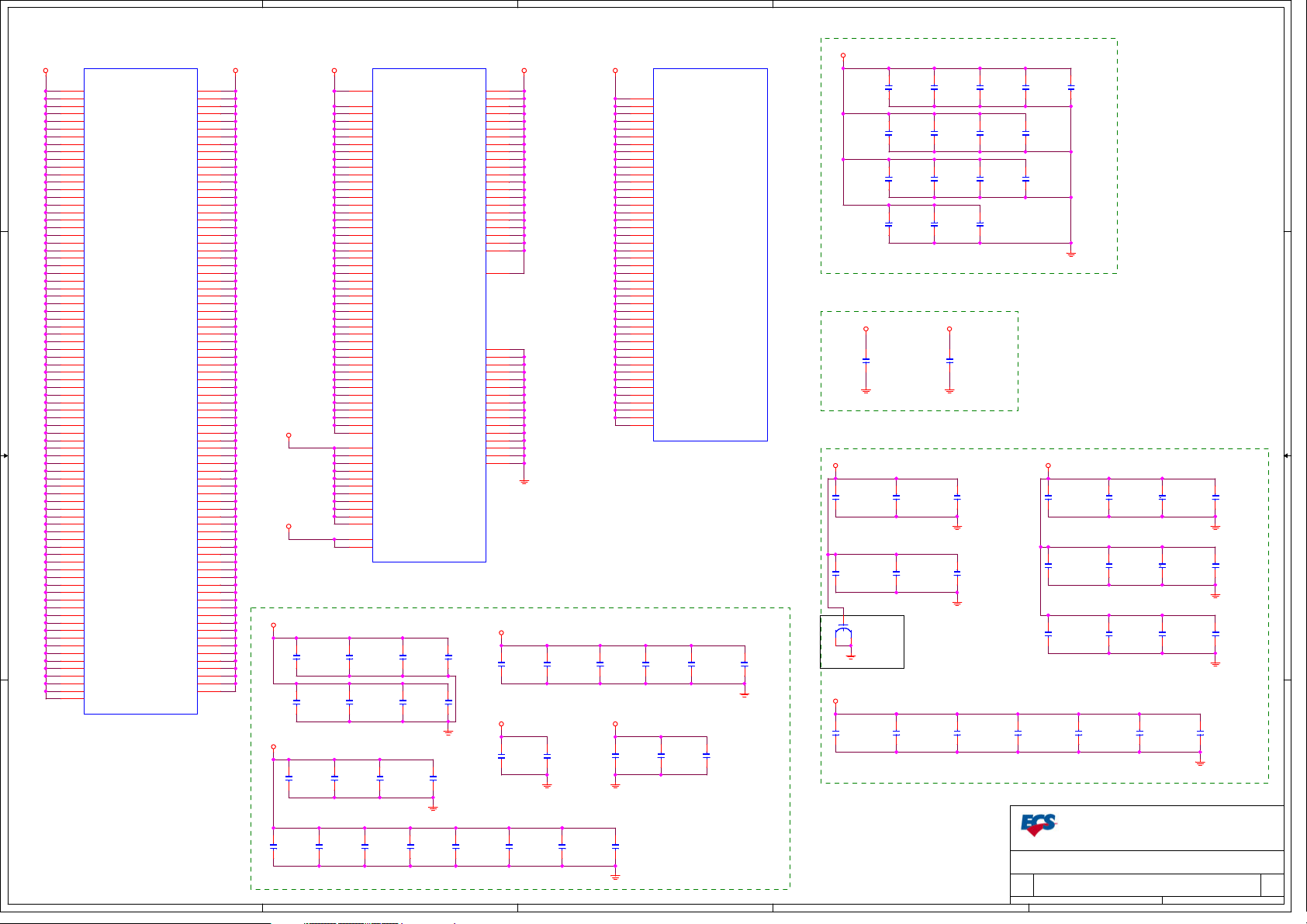

TABLE OF CONTENTS

Page Index

------- ------------------------

1

Cover Page

2

Block Diagram

3

GPIO Function Map

4

CPU - DMI/FDI/PEG

5

CPU - MISC

6

C C

10

11

12

13

14

15

B B

16

17

18

19

20

21

22

23

24

25

A A

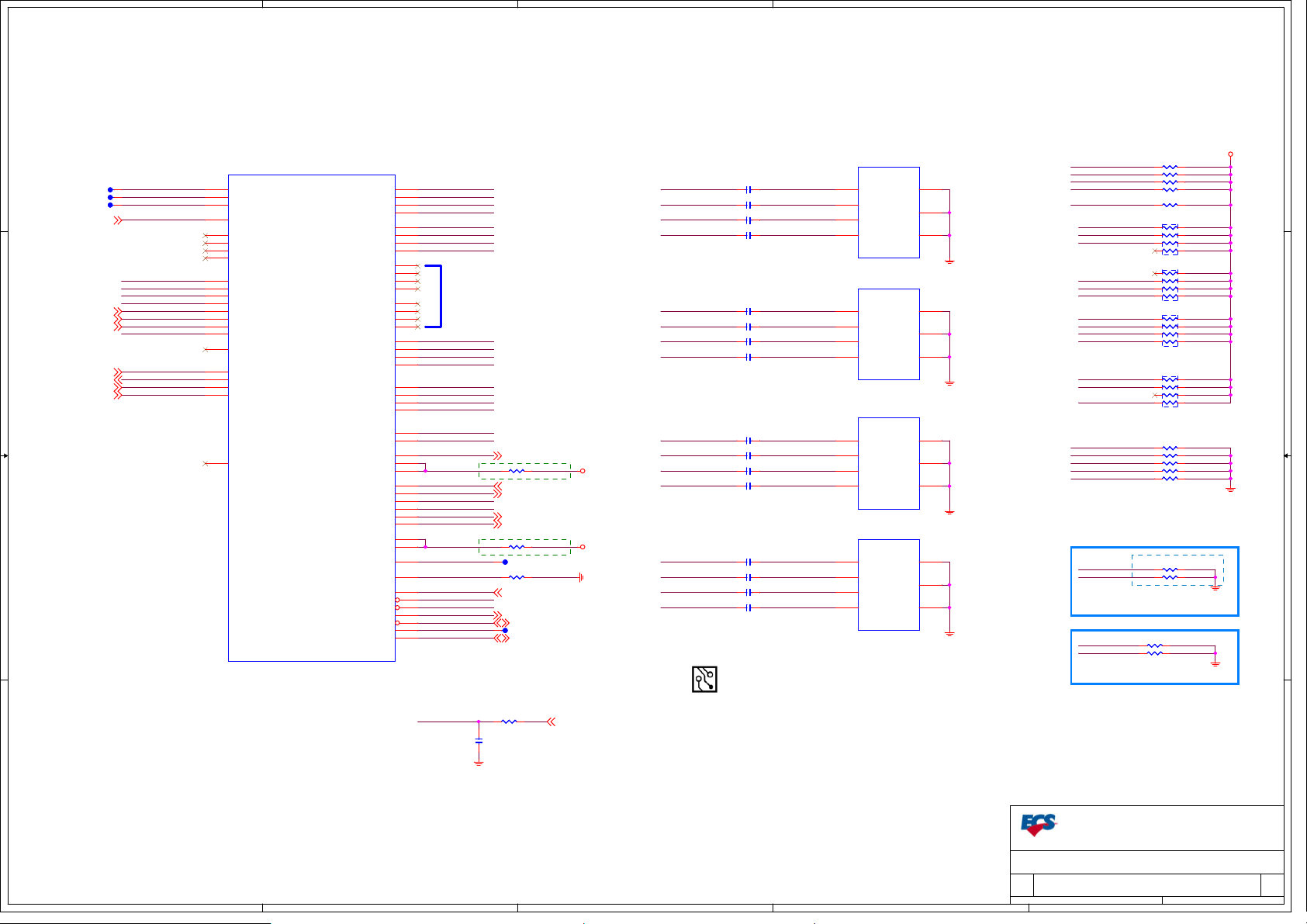

CPU - DDR3

7

CPU - PWR

8

CPU - GND, CPU_RST_L

9

DDR3 - CHA DIMM

DDR3 - CHB DIMM

DDR3 - VREF

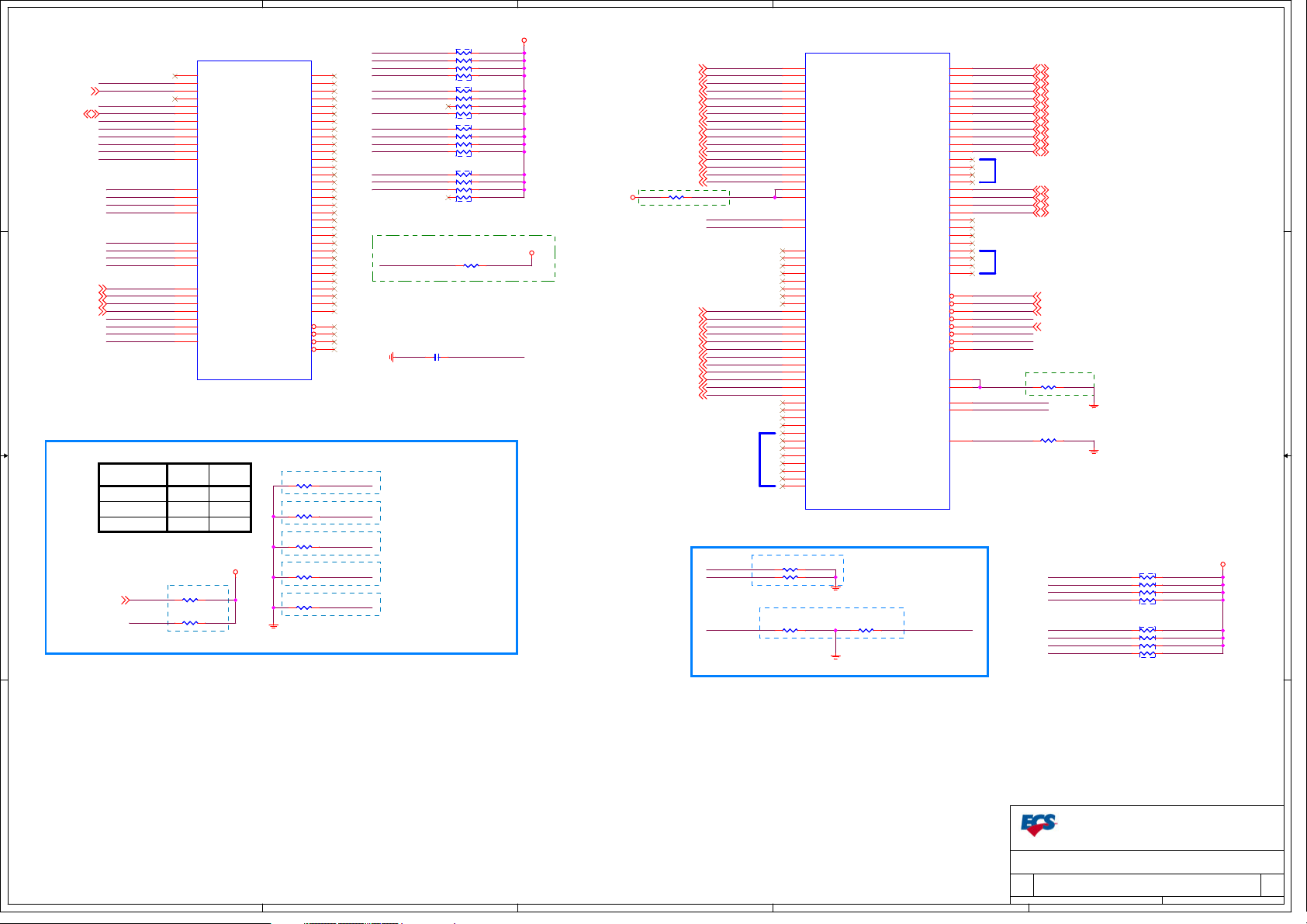

PCH - DMI/PCH-PE/USB

PCH - SATA, SATA CONN

PCH - MISC, Strap Function

PCH - CLK IO

PCH - FDI,CLR_CMOS,ROM,SMbus

PCH - DVI/VGA

PCH - PWR

PCH - GND,VGA CONN

PCIE*16,PCIE*1 Slot

P21 PCI Bridge (IT8893E-FX)

P22 PCI Slot

LAN(RTL8111F-VB/8111E-VB)

USBLAN Connector

Audio (ALC662-VD)

Page Index

------- ------------------------

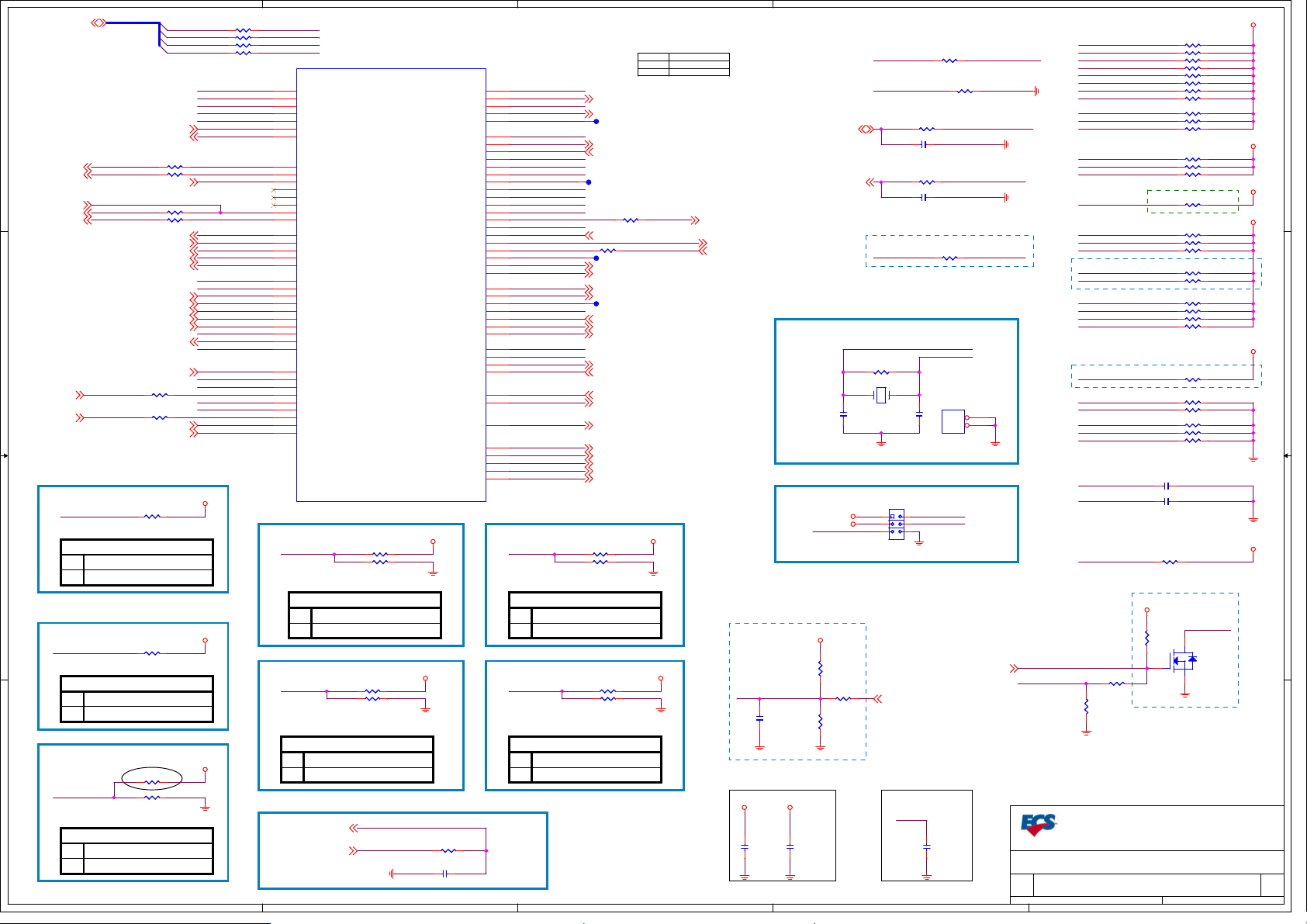

Audio - CONN&HDR26

USB - PWR&CONN&HDR27

28

29

30

31

32

33

34

35

36

37

38

39

40

41 104 & STRAPPING

42

43

44

LPC Device

SIO (IT8728F-FX)

FAN,COM,CASE_OPEN,THERMAL

F_PANEL,BUZ,PS2,LPT

DC/DC 3VDUAL

DC/DC V1P05_PCH,ME/V1P8_SFR

DC/DC VDIMM/DDR_VTT/5VDUAL

DC/DC VCCSA, ATXPWR

DC/DC V_CPUVTT

DC/DC VCORE/VAXG1

DC/DC VCORE/VAXG2

XDP

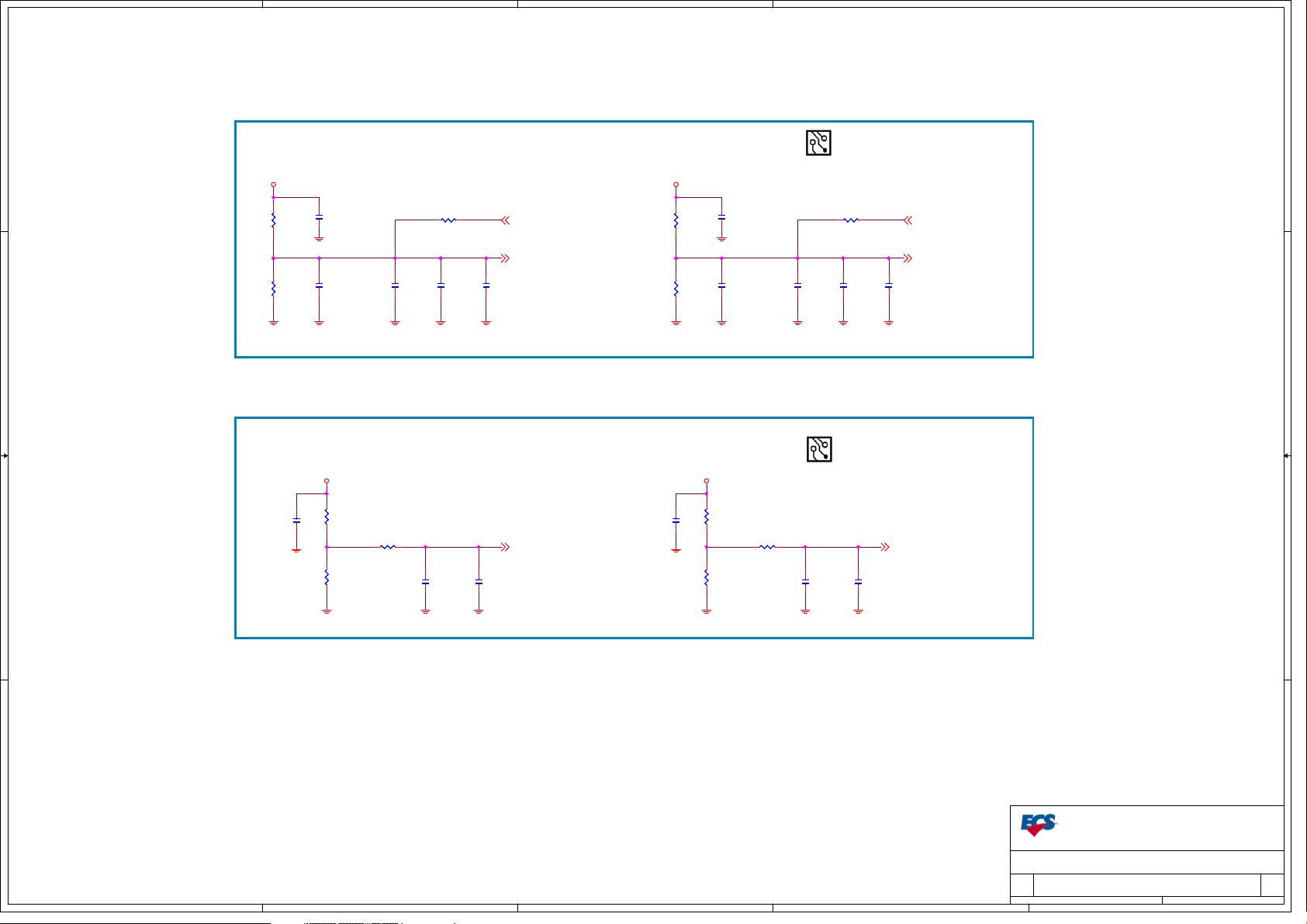

Deep Sleep Well

Power Delivery

Power Sequence, Reset Diagram

Clock Distribution

REVISION HISTORY:

Rev Date Notes

------ -------------- ---------------------------------------------------------------------------------

Rev : 0.1

ECS

CONFIDENTIAL

Note:

design by

428971_428971_Sugar Bay and Bromolow-WS_PDG_Rev2_0_December 2010

443554_443554_Intel 6 Series Chipset and Intel C200 Series Chipset_EDS_Rev1_5_January 2011

5

4

3

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

H61H2-LM5

H61H2-LM5

H61H2-LM5

1

1 44Friday, March 02, 2012

1 44Friday, March 02, 2012

1 44Friday, March 02, 2012

V 0.1

V 0.1

V 0.1

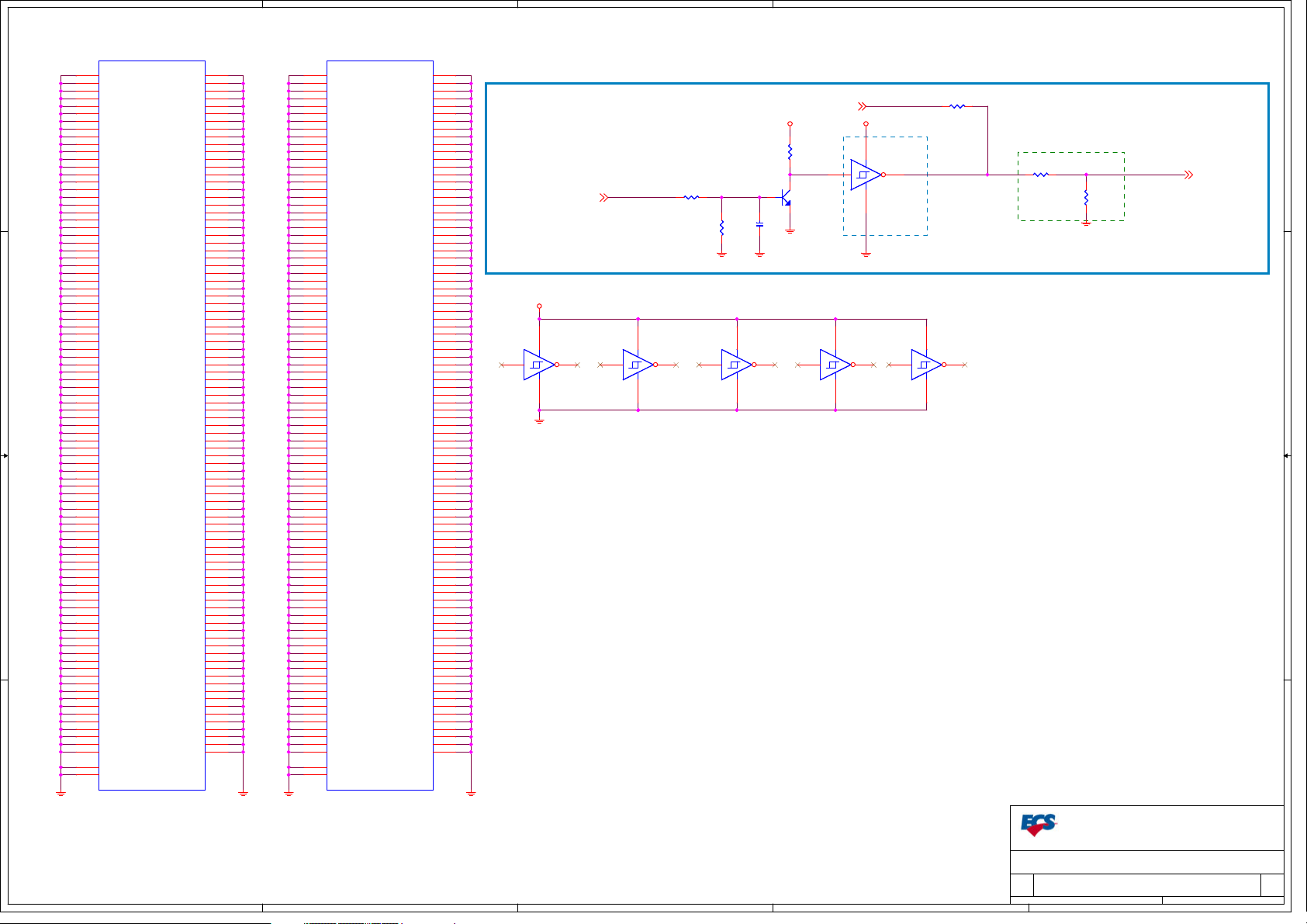

Page 2

5

4

3

2

1

DDR3 1600MHz/1333MHz/1066MHz

Total Max 8GB

Sandy

D D

PCIe X16

Bridge

Desktop Processor

Socket H2

FDI

DMI

DDR3 Channel A

DDR3 Channel B

Jack 3 in 1

3Gbps

PCIe

PCIe

H61

Cougar Point

Chipset

PCIe

PCIe X1

C C

PCI1

PCI Bridge

(IT8893FX)

PCI2

SATA 2.0 x 4

AUDIO-ALC662

Realtek LAN

8111F-VB/8105E/

8111E-VB(co-lay)

F_AUDIO

RJ-45 & USB x 2

Rear IO

VGA

USB Conn. 2Ports

Rear IO

DVI

B B

USB

F_USB 2Ports x 2

Front header

SPI ROM

LPC

TPM / TCM

COM1(Rear IO)

COM2(Front header),8*2/6*2 co-layout

FAN 1,2,3

A A

Temp. Sensor Header

SIO

IT8728F-FX

LPT header

PS2 Conn.

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H61H2-LM5

H61H2-LM5

H61H2-LM5

1

2 44Friday, March 02, 2012

2 44Friday, March 02, 2012

2 44Friday, March 02, 2012

V 0.1

V 0.1

V 0.1

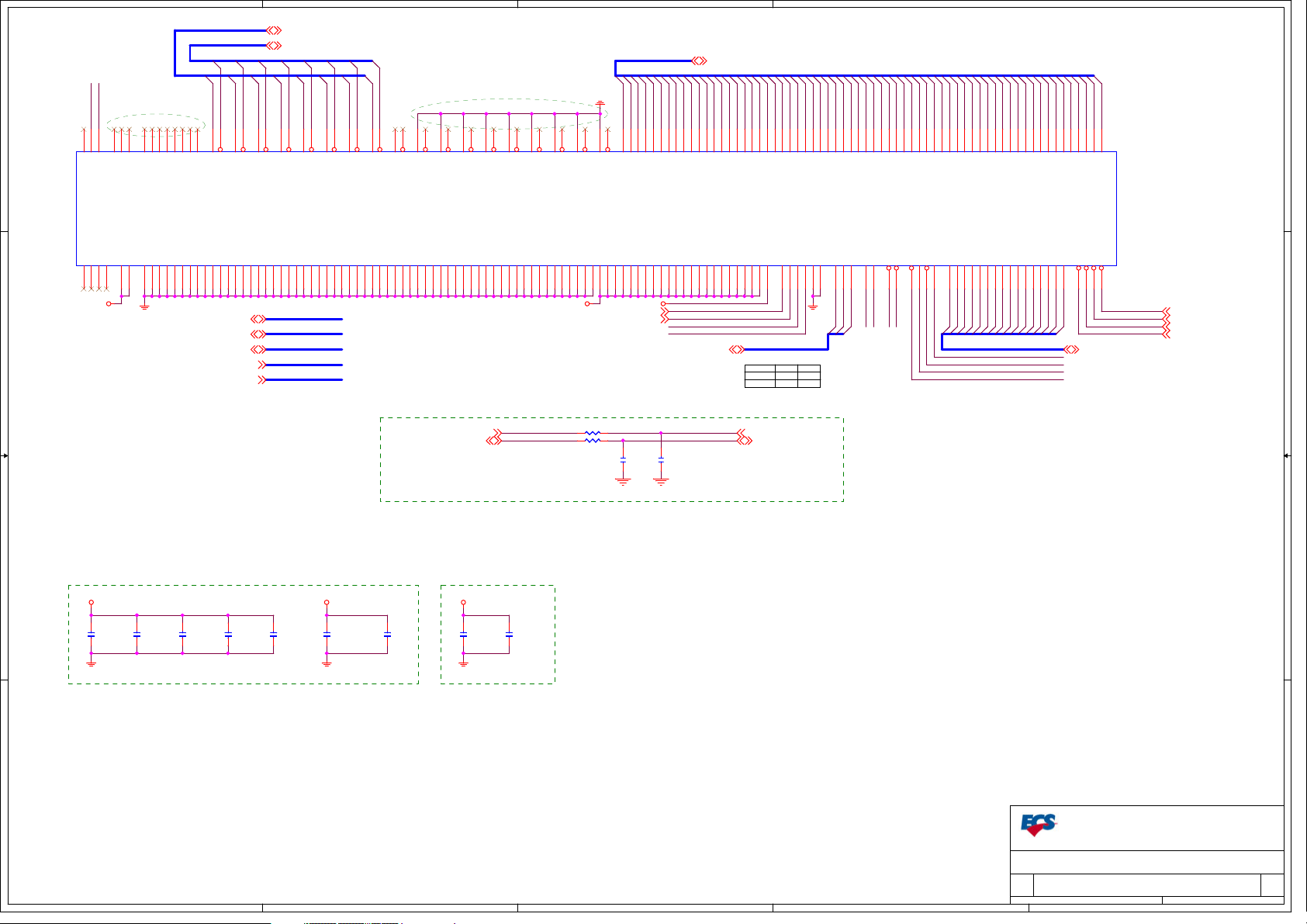

Page 3

5

4

3

2

1

PCH-GPIO function

------------------------------------------------------------------------------------------------------------

Pin Name Power Well Usage

------------------------------------------------------------------------------------------------------------

D D

GPIO51

GPIO53

GPIO55

GPIO50

GPIO52

GPIO54

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPI

GPI

GPI

GPI

GPI

GPI

Data: 2012 / 01 / 30 Data: 2012 / 01 / 30

GPIO59 3VSB NativeUSB_OC_L0

GPIO40

GPIO41

GPIO42

GPIO43

GPIO10

3VSB

3VSB

3VSB

3VSB

3VSB

3VSB Native

USB_OC_L1

USB_OC_L2

USB_OC_L3

USB_OC_L4

USB_OC_L5

USB_OC_L6

Native

Native

Native

Native

NativeGPIO9

SIO-GPIO function

------------------------------------------------------------------------------------------------------------

Pin Name Power Well UsageDefault Status

------------------------------------------------------------------------------------------------------------

VCC3

3VSB

3VSB

Chipset PCIE INT Fuction

Fucntion PCIEX1 port

PCIE to PCI IT8893FX

PCI-E Slot PCI-E Slot

LAN

Sata Controller

INT Port

PCI Express #3 Pin

INTC#

INTD#

PCI Express #4 Pin

INTA#

PCI Express #5 Pin

INTB# H61 intergrated

Data: 2012 / 01 / 30

N/A

SIO_BEEPGP16

Power LEDGP22

5VDUAL controlGP40

Chipset

Realtek LAN

Default Status

3VSB NativeUSB_OC_L7GPIO14

C C

GPIO6 VCC3 GPIO6_KMDET

GPIO68

GPIO69

VCC3 GPIGP17_BOMDET1GPIO17

VCC3

VCC3

GPIO68_USBDET1

GPIO69_USBDET2

GPIGPIO1 VCC3 GP1_BOMDET2

GPI

GPIGPIO7 VCC3 GPIO

GPI

GPI

Chipset PCI Fuction

Fucntion IDSEL

INT Port

PCI1 N/AAD16A/B/C/D

PCI2 N/A

B/C/D/A AD17

Data: 2012 / 01 / 30

Chipset

GPIO70 VCC3 GPIGPIO70_LPTDET3

GPIO71 VCC3 GPIGP71_BOMDET3

GPIO22 VCC3 GPICLR_CMOS_GP22

GPIO38 VCC3 GPIGPIO38_TCM

GPIO39

GPIO48

VCC3

VCC3

GPIO39_CASE0

GPIO48_CASE1

GPI

GPI

GPIO21 VCC3 GPIGPIO21_COM2_DET

GPIO32 VCC3 GPOTCM_DIS_L

B B

GPIO34 VCC3 GPIGPIO34_TCM_PST_L

GPIO35 VCC3 GPOTP_VGA

+DIMM_5VDUAL NativePOWER LEDGPIO12

GPIO13

3VSB GPILPC_PME_L

GPIO45 3VSB GPIGP45_BOMDET4

GPIO72 3VSB GPIGP72_BOMDET5

VCC3 GPIReserve for TPMGPIO16

GPIO49 VCC3 GPIReserve for TPM

GPIO24 3VSB GPOPCH_SKTOCC_L

GPIO61 VCC3 NativeLPCPD_L

GPIO60 3VSB NativeLAN_OE

GPIO74 3VSB NativeLAN_SEL

GPIO57 3VSB NativeLAN_SEL

NOTE: GPIO60,74,57 Reserve for Dual LAN solution

A A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

GPIO Function Map

GPIO Function Map

GPIO Function Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H61H2-LM5

H61H2-LM5

H61H2-LM5

1

3 44Monday, March 05, 2012

3 44Monday, March 05, 2012

3 44Monday, March 05, 2012

V 0.1

V 0.1

V 0.1

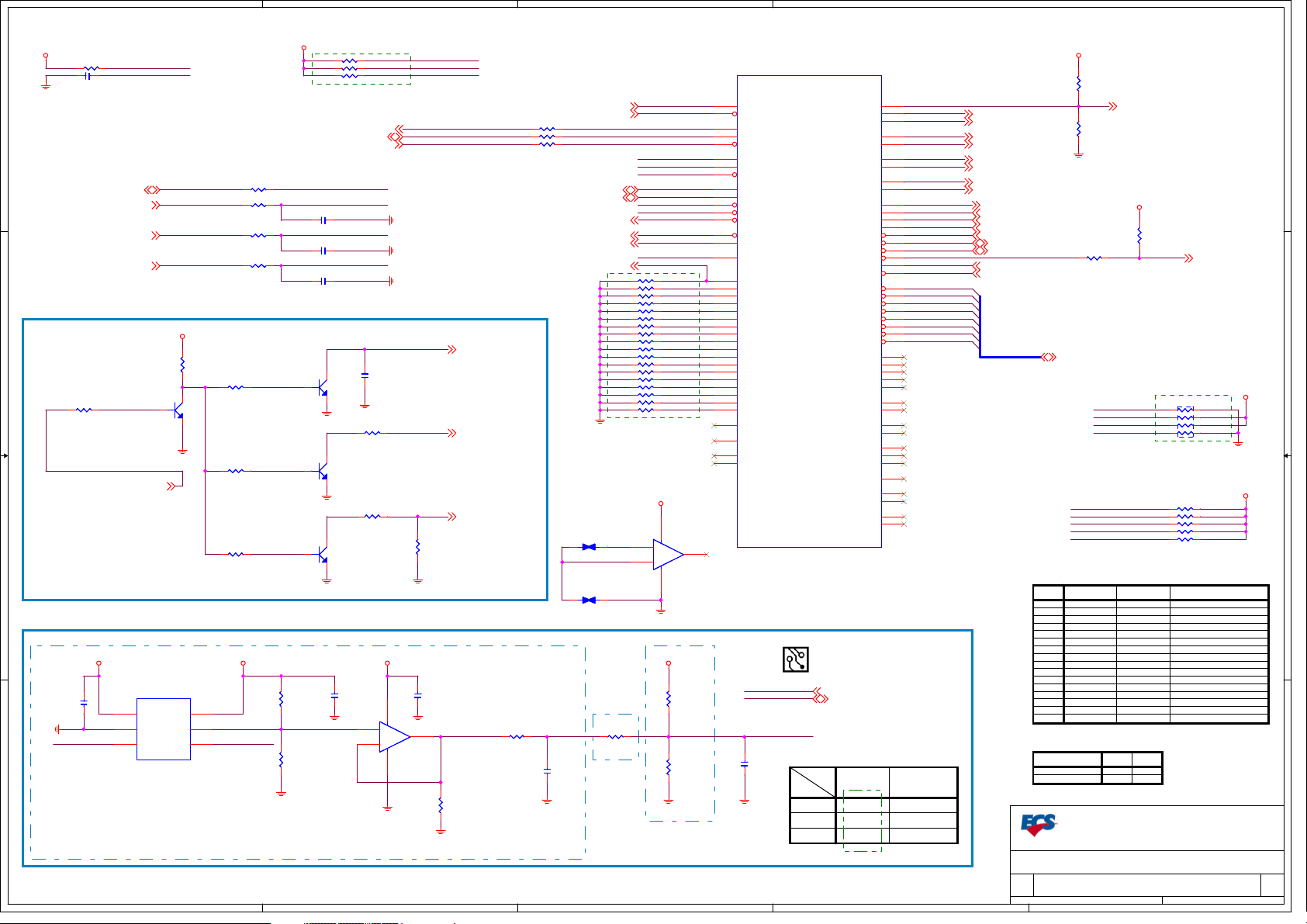

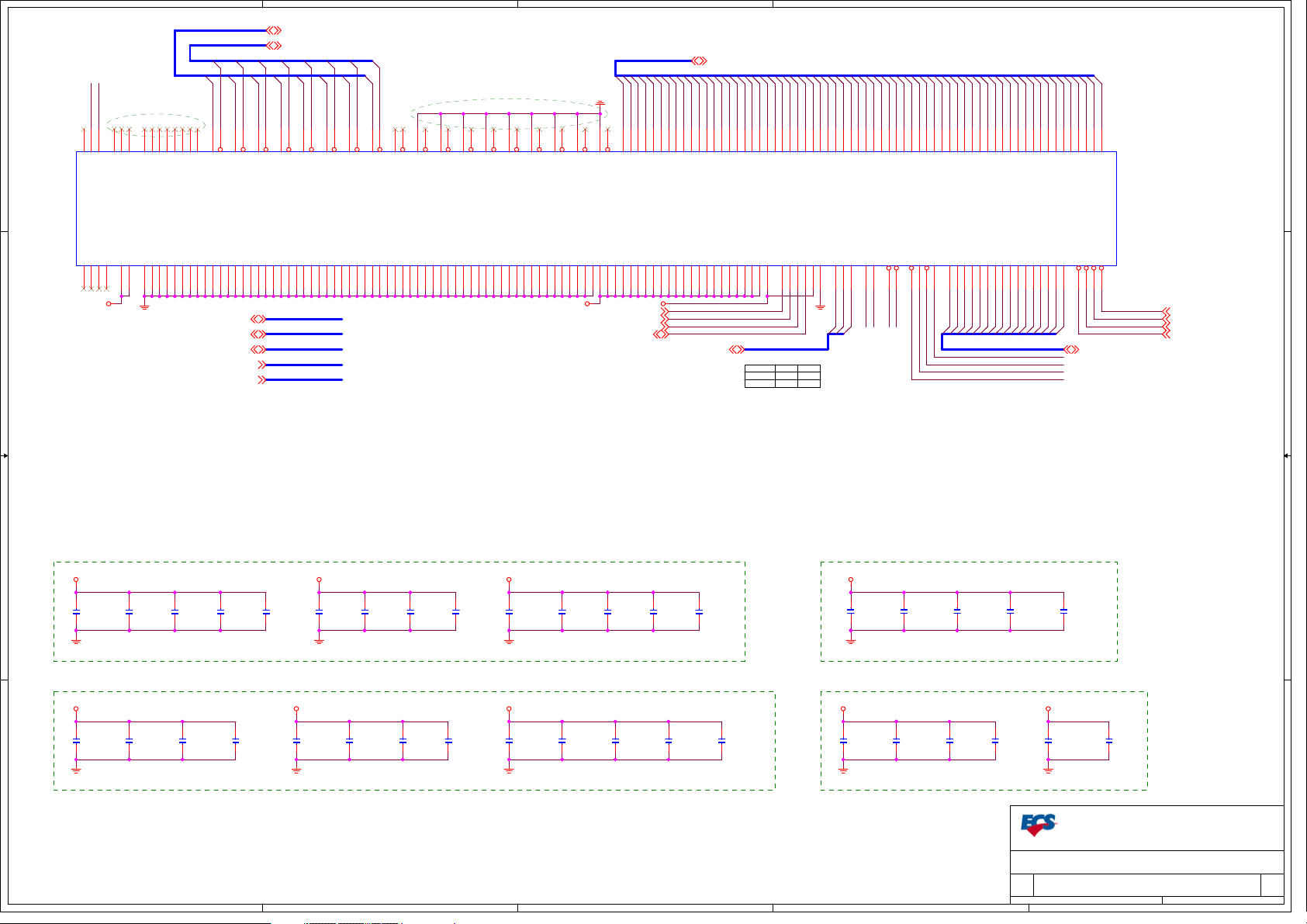

Page 4

5

CPU1A

CPU1A

BALLMAP_REV=1.4

BALLMAP_REV=1.4

PEG_RX_P0<20>

PEG_RX_N0<20>

PEG_RX_P1<20>

PEG_RX_N1<20>

PEG_RX_P2<20>

PEG_RX_N2<20>

D D

C C

+V_CPUVTT

PEG_RX_P3<20>

PEG_RX_N3<20>

PEG_RX_P4<20>

PEG_RX_N4<20>

PEG_RX_P5<20>

PEG_RX_N5<20>

PEG_RX_P6<20>

PEG_RX_N6<20>

PEG_RX_P7<20>

PEG_RX_N7<20>

PEG_RX_P8<20>

PEG_RX_N8<20>

PEG_RX_P9<20>

PEG_RX_N9<20>

PEG_RX_P10<20>

PEG_RX_N10<20>

PEG_RX_P11<20>

PEG_RX_N11<20>

PEG_RX_P12<20>

PEG_RX_N12<20>

PEG_RX_P13<20>

PEG_RX_N13<20>

PEG_RX_P14<20>

PEG_RX_N14<20>

PEG_RX_P15<20>

PEG_RX_N15<20>

DMI_RX_P0<12>

DMI_RX_N0<12>

DMI_RX_P1<12>

DMI_RX_N1<12>

DMI_RX_P2<12>

DMI_RX_N2<12>

DMI_RX_P3<12>

DMI_RX_N3<12>

R285 24.9-1-04R285 24.9-1-04

1 2

SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLE 4mils TRACE TO R285.

ROUTE B5 TO R285 AS A SEPERATE 12mils TRACE.

PEG_RX_P0

PEG_RX_N0

PEG_RX_P1

PEG_RX_N1

PEG_RX_P2

PEG_RX_N2

PEG_RX_P3

PEG_RX_N3

PEG_RX_P4

PEG_RX_N4

PEG_RX_P5

PEG_RX_N5

PEG_RX_P6

PEG_RX_N6

PEG_RX_P7

PEG_RX_N7

PEG_RX_P8

PEG_RX_N8

PEG_RX_P9

PEG_RX_N9

PEG_RX_P10

PEG_RX_N10

PEG_RX_P11

PEG_RX_N11

PEG_RX_P12

PEG_RX_N12

PEG_RX_P13

PEG_RX_N13

PEG_RX_P14

PEG_RX_N14

PEG_RX_P15

PEG_RX_N15

DMI_RX_P0

DMI_RX_N0

DMI_RX_P1

DMI_RX_N1

DMI_RX_P2

DMI_RX_N2

DMI_RX_P3

DMI_RX_N3

PEG_COMP

B11

B12

D12

D11

C10

E10

AA4

AA5

C9

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

W5

W4

V3

V4

Y3

Y4

P3

P4

R2

R1

T4

T3

U2

U1

B5

C4

B4

PEG_RX_ 0

PEG_RX# _0

PEG_RX_ 1

PEG_RX# _1

PEG_RX_ 2

PEG_RX# _2

PEG_RX_ 3

PEG_RX# _3

PEG_RX_ 4

PEG_RX# _4

PEG_RX_ 5

PEG_RX# _5

PEG_RX_ 6

PEG_RX# _6

PEG_RX_ 7

PEG_RX# _7

PEG_RX_ 8

PEG_RX# _8

PEG_RX_ 9

PEG_RX# _9

PEG_RX_ 10

PEG_RX# _10

PEG_RX_ 11

PEG_RX# _11

PEG_RX_ 12

PEG_RX# _12

PEG_RX_ 13

PEG_RX# _13

PEG_RX_ 14

PEG_RX# _14

PEG_RX_ 15

PEG_RX# _15

DMI_RX_0

DMI_RX#_0

DMI_RX_1

DMI_RX#_1

DMI_RX_2

DMI_RX#_2

DMI_RX_3

DMI_RX#_3

PE_RX_0

PE_RX#_ 0

PE_RX_1

PE_RX#_ 1

PE_RX_2

PE_RX#_ 2

PE_RX_3

PE_RX#_ 3

PEG_ICOMP O

PEG_RCO MPO

PEG_COM PI

SKT_H2_CRB

SKT_H2_CRB

PEGDMIGEN

PEGDMIGEN

PEG_TX_ 0

PEG_TX# _0

PEG_TX_ 1

PEG_TX# _1

PEG_TX_ 2

PEG_TX# _2

PEG_TX_ 3

PEG_TX# _3

PEG_TX_ 4

PEG_TX# _4

PEG_TX_ 5

PEG_TX# _5

PEG_TX_ 6

PEG_TX# _6

PEG_TX_ 7

PEG_TX# _7

PEG_TX_ 8

PEG_TX# _8

PEG_TX_ 9

PEG_TX# _9

PEG_TX_ 10

PEG_TX# _10

PEG_TX_ 11

PEG_TX# _11

PEG_TX_ 12

PEG_TX# _12

PEG_TX_ 13

PEG_TX# _13

PEG_TX_ 14

PEG_TX# _14

PEG_TX_ 15

PEG_TX# _15

DMI_TX_0

DMI_TX#_0

DMI_TX_1

DMI_TX#_1

DMI_TX_2

DMI_TX#_2

DMI_TX_3

DMI_TX#_3

PE_TX_0

PE_TX#_ 0

PE_TX_1

PE_TX#_ 1

PE_TX_2

PE_TX#_ 2

PE_TX_3

PE_TX#_ 3

1 OF 10

1 OF 10

4

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

V6

W7

W8

Y6

Y7

AA7

AA8

P8

P7

T7

T8

R6

R5

U5

U6

PEG_TX_P0

PEG_TX_N0

PEG_TX_P1

PEG_TX_N1

PEG_TX_P2

PEG_TX_N2

PEG_TX_P3

PEG_TX_N3

PEG_TX_P4

PEG_TX_N4

PEG_TX_P5

PEG_TX_N5

PEG_TX_P6

PEG_TX_N6

PEG_TX_P7

PEG_TX_N7

PEG_TX_P8

PEG_TX_N8

PEG_TX_P9

PEG_TX_N9

PEG_TX_P10

PEG_TX_N10

PEG_TX_P11

PEG_TX_N11

PEG_TX_P12

PEG_TX_N12

PEG_TX_P13

PEG_TX_N13

PEG_TX_P14

PEG_TX_N14

PEG_TX_P15

PEG_TX_N15

DMI_TX_P0

DMI_TX_N0

DMI_TX_P1

DMI_TX_N1

DMI_TX_P2

DMI_TX_N2

DMI_TX_P3

DMI_TX_N3

PEG_TX_P0 <20>

PEG_TX_N0 <20>

PEG_TX_P1 <20>

PEG_TX_N1 <20>

PEG_TX_P2 <20>

PEG_TX_N2 <20>

PEG_TX_P3 <20>

PEG_TX_N3 <20>

PEG_TX_P4 <20>

PEG_TX_N4 <20>

PEG_TX_P5 <20>

PEG_TX_N5 <20>

PEG_TX_P6 <20>

PEG_TX_N6 <20>

PEG_TX_P7 <20>

PEG_TX_N7 <20>

PEG_TX_P8 <20>

PEG_TX_N8 <20>

PEG_TX_P9 <20>

PEG_TX_N9 <20>

PEG_TX_P10 <20>

PEG_TX_N10 <20>

PEG_TX_P11 <20>

PEG_TX_N11 <20>

PEG_TX_P12 <20>

PEG_TX_N12 <20>

PEG_TX_P13 <20>

PEG_TX_N13 <20>

PEG_TX_P14 <20>

PEG_TX_N14 <20>

PEG_TX_P15 <20>

PEG_TX_N15 <20>

DMI_TX_P0 <12>

DMI_TX_N0 <12>

DMI_TX_P1 <12>

DMI_TX_N1 <12>

DMI_TX_P2 <12>

DMI_TX_N2 <12>

DMI_TX_P3 <12>

DMI_TX_N3 <12>

3

+V_CPUVTT

Close to CPU and Length <250mils

FDI_FSYNC0<16>

FDI_LSYNC0<16>

FDI_FSYNC1<16>

FDI_LSYNC1<16>

FDI_INT<16>

1 2

R387 24.9-1-04R387 24.9-1-04

FDI_FSYNC0

FDI_LSYNC0

FDI_FSYNC1

FDI_LSYNC1

FDI_INT

FDI_COMP

AC5

AC4

AE5

AE4

AG3

AE2

AE1

AB7

AD37

AG4

AJ29

AJ30

AJ31

AV34

AW3 4

R34

R36

R38

R40

AU40

AW3 8

P35

P37

P39

A38

C2

D1

CPU1B

CPU1B

BALLMAP_REV=1.4

BALLMAP_REV=1.4

FDI_FSYNC_0

FDI_LSYNC_0

FDI_FSYNC_1

FDI_LSYNC_1

FDI_INT

FDI_COMPIO

FDI_ICOMPO

RSVD_04

RSVD_05

RSVD_08

RSVD_10

RSVD_11

RSVD_12

RSVD_19

RSVD_21

RSVD_43

RSVD_44

RSVD_45

RSVD_46

RSVD_47

RSVD_48

RSVD_49

NCTF_01

NCTF_02

NCTF_03

NCTF_04

NCTF_05

SKT_H2_CRB

SKT_H2_CRB

2

FDI LINK

FDI LINK

2 OF 10

2 OF 10

FDI_TX_0

FDI_TX#_0

FDI_TX_1

FDI_TX#_1

FDI_TX_2

FDI_TX#_2

FDI_TX_3

FDI_TX#_3

FDI_TX_4

FDI_TX#_4

FDI_TX_5

FDI_TX#_5

FDI_TX_6

FDI_TX#_6

FDI_TX_7

FDI_TX#_7

SB_DIMM_D QVREF

SA_DIMM_D QVREF

RSVD_15

RSVD_14

RSVD_13

RSVD_17

RSVD_22

RSVD_07

RSVD_03

RSVD_06

RSVD_09

RSVD_27

RSVD_26

RSVD_25

RSVD_31

RSVD_41

AC8

FDI_TX_P0

AC7

FDI_TX_N0

AC2

FDI_TX_P1

AC3

FDI_TX_N1

AD2

FDI_TX_P2

AD1

FDI_TX_N2

AD4

FDI_TX_P3

AD3

FDI_TX_N3

AD7

FDI_TX_P4

AD6

FDI_TX_N4

AE7

FDI_TX_P5

AE8

FDI_TX_N5

AF3

FDI_TX_P6

AF2

FDI_TX_N6

AG2

FDI_TX_P7

AG1

FDI_TX_N7

AH1

DIMM_DQ_CPU_VREF_B

AH4

DIMM_DQ_CPU_VREF_A

AT11

AP20

AN20

AU10

AY10

AF4

AB6

AE6

AJ11

D38

C39

C38

J34

N34

FDI_TX_P0 <16>

FDI_TX_N0 <16>

FDI_TX_P1 <16>

FDI_TX_N1 <16>

FDI_TX_P2 <16>

FDI_TX_N2 <16>

FDI_TX_P3 <16>

FDI_TX_N3 <16>

FDI_TX_P4 <16>

FDI_TX_N4 <16>

FDI_TX_P5 <16>

FDI_TX_N5 <16>

FDI_TX_P6 <16>

FDI_TX_N6 <16>

FDI_TX_P7 <16>

FDI_TX_N7 <16>

C384

C384

.1U-04

.1U-04

2 1

GND GND

1

DIMM_DQ_CPU_VREF_B <11>

DIMM_DQ_CPU_VREF_A <11>

C379

C379

.1U-04

.1U-04

2 1

B B

A A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

CPU - DMI/FDI/PEG

CPU - DMI/FDI/PEG

CPU - DMI/FDI/PEG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H61H2-LM5

H61H2-LM5

H61H2-LM5

1

4 44Friday, March 02, 2012

4 44Friday, March 02, 2012

4 44Friday, March 02, 2012

V 0.1

V 0.1

V 0.1

Page 5

5

4

3

2

1

1 2

+V_CPUVTT

12

12

12

QN1_B

PMBS3904-S

PMBS3904-S

QN3_B

PMBS3904-S

PMBS3904-S

QN4_B

PMBS3904-S-O

PMBS3904-S-O

QN1

QN1

QN3

QN3

QN4

QN4

B

B

B

R234 90.9-1-04-OR234 90.9-1-04-O

R242 110-1-04R242 110-1-04

R233 75-1-04R233 75-1-04

VR_SVID_CK<37>

VR_SVID_DATAOUT<37>

VR_SVID_ALERT_L<37>

12

12

12

Close to CPU

PROCHOT_LVR_HOT_L

DRAM_PWROK_RC

21

.1U-X7-04-OC364 .1U-X7-04-OC364

CPU_RST_L_RCCPU_RST_L

21

.1U-X7-04-OC247 .1U-X7-04-OC247

CPU_PWROK_RCCPU_PWROK

21

.1U-X7-04-OC258 .1U-X7-04-OC258

21

C269

C269

2.2U-6V3-O

2.2U-6V3-O

E C

GND

GND

1 2

QN3_C

R352 100-04R352 100-04

E C

GND

1 2

QN4_C

R353 100-04-OR353 100-04-O

E C

GND GND

SVID_CK

SVID_DATAOUT

VR_SVID_ALERT_L

VR_SVID_CK

VR_SVID_DATAOUT

VR_SVID_ALERT_L

GND

GND

GND

VR_EN

VR_READY

CPU_PWROK

R344

R344

1K-04

1K-04

1 2

VR_EN <37>

TO VRD FOR S0->S5

VR_READY <14,37,39>

FROM VRD

CPU_PWROK <14,39>

Power Down Sequencing Circuit

+DIMM_5VDUAL+V_1P5_SM+3VSB

12

R441

12

GND

R441

12.1K-1-04-O

12.1K-1-04-O

R443

R443

12.1K-1-04-O

12.1K-1-04-O

C385

C385

1U-6V3X-04-O

1U-6V3X-04-O

2 1

GND

C397

C397

1U-25VX7-08-O

1U-25VX7-08-O

2 1

84

3

GND

+

+

1

2

-

-

U6A

U6A

LM358DS-O

LM358DS-O

R438

R438

12.1K-1-04-O

GND

4

1 2

GND

12.1K-1-04-O

1 2

R227 0-04R227 0-04

1 2

R251 0-04R251 0-04

1 2

R231 44.2-1-04R231 44.2-1-04

1 2

R437 2.2-04-OR437 2.2-04-O

MCPU_NCPU

2 1

CK_CPU_100M_P<15>

CK_CPU_100M_N<15>

PM_SYNC<13>

CPU_THERMTRIP_L<13>

H_SKTOCC_L<14,37>

PROC_SEL<16>

R600

R600

Short PAD

Short PAD

R611

R611

Short PAD

Short PAD

C380

C380

1U-6V3X-04-O

1U-6V3X-04-O

CK_CPU_100M_P

SVID_CK

SVID_DATAOUT

GND

CK_CPU_100M_N

VIDALERT_R_L

CPU_PWROK_RC

DRAM_PWROK_RC

CPU_RST_L_RC

PM_SYNC

PECI

PECI<29>

CATERR_L

PROCHOT_L

CPU_THERMTRIP_L

H_SKTOCC_L

PROC_SEL

DIMM_VREF_CPU

CFG_0

CFG_0<39>

1 2

R332 1K-04-OR332 1K-04-O

1 2

R266 1K-04-OR266 1K-04-O

1 2

R281 1K-04-OR281 1K-04-O

1 2

R267 1K-04-OR267 1K-04-O

1 2

R290 1K-04-OR290 1K-04-O

1 2

R312 1K-04-OR312 1K-04-O

1 2

R303 1K-04-OR303 1K-04-O

1 2

R302 1K-04-OR302 1K-04-O

1 2

R289 1K-04-OR289 1K-04-O

1 2

R282 1K-04-OR282 1K-04-O

1 2

R327 1K-04-OR327 1K-04-O

1 2

R313 1K-04-OR313 1K-04-O

1 2

R329 1K-04-OR329 1K-04-O

1 2

R330 1K-04-OR330 1K-04-O

1 2

R328 1K-04-OR328 1K-04-O

1 2

R331 1K-04-OR331 1K-04-O

1 2

R258 1K-04-OR258 1K-04-O

1 2

R257 1K-04-OR257 1K-04-O

Close to CPU

+DIMM_5VDUAL

5

U6_GND1

6

U6_GND2

PcpuMcpu

Ncpu

R430

R430

1 2

0-04-O

0-04-O

Place Pcpu in

Socket Cavity.

3

84

+

+

-

-

GND

+V_1P5_SM

1 2

1 2

CPU1E

CPU1E

BALLMAP_REV=1.4

BALLMAP_REV=1.4

W2

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

7

U6B

U6B

LM358DS-O

LM358DS-O

R426

R426

100-1-04

100-1-04

R422

R422

100-1-04

100-1-04

BCLK_0

W1

BCLK#_0

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

J40

UNCOREP WRGOOD

AJ19

SM_DRAM PWROK

F36

RESET#

E38

PM_SYNC

J35

PECI

E37

CATERR#

H34

PROCHOT #

G35

THERMTR IP#

AJ33

SKTOCC#

K32

PROC_SE L

AJ22

SM_VREF

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_01 6

AY3

RSVD_02 3

H7

RSVD_02 8

H8

RSVD_02 9

SKT_H2_CRB

SKT_H2_CRB

2 1

GNDGNDGND

5 OF 10

5 OF 10

SMBCLK_STBY

SMBDATA_STBY

DIMM_VREF_CPUDIMM_VREF_CPU_2

SC37

SC37

.1U-X7-04-X

.1U-X7-04-X

VCCP_SE LECT

VCCSA_V ID

VCCSA_S ENSE

VCC_SEN SE

VSS_SEN SE

VCCIO_SEN SE

VSSIO_SEN SE

VCCAXG_ SENSE

VSSAXG_ SENSE

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

RSVD_00 1

RSVD_00 2

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD_02 4

RSVD_03 0

RSVD_03 7

RSVD_03 6

RSVD_03 3

RSVD_04 0

RSVD_03 9

RSVD_01 8

RSVD_02 0

RSVD_03 8

RSVD_03 2

RSVD_03 4

RSVD_03 5

RSVD_05 0

RSVD_05 3

RSVD_05 1

RSVD_05 2

Layout Note:

All Parts Close to CPU

SMBCLK_STBY <14,16,20,22,23>

SMBDATA_STBY <14,16,20,22,23>

DIMM_VREF_CPU Control Mode:

Control

Mode

Divider

Part

Mcpu

Ncpu

X

X

Pcpu V

Default

DIMM_VREF_CPU Control Circuit

TDI

P33

VTT_SEL

P34

VCCSA_VID

T2

VCCSA_SEN

A36

VCC_SEN

B36

VSS_SEN

AB4

VCCIO_SEN

AB3

VSSIO_SEN

L32

VCCAXG_SEN

M32

VSSAXG_SEN

L39

H_TDO

L40

H_TDI

M40

H_TCK

L38

H_TMS

J39

H_TRST_L

K38

H_PRDY_L

K40

H_PREQ_L

E39

CPU_DRB

C40

XDP_H_CLK_DP

D40

XDP_H_CLK_DN

H40

BPM_L_0

H38

BPM_L_1

G38

BPM_L_2

G40

BPM_L_3

G39

BPM_L_4

F38

BPM_L_5

E40

BPM_L_6

F40

BPM_L_7

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

PCH +

Controller

V

V

X

2

+VCC

R245

R245

10K-04

10K-04

1 2

VCCSA_VID <35>

VCCSA_SEN <35>

VCC_SEN <37>

VSS_SEN <37>

VCCIO_SEN <36>

VSSIO_SEN <36>

VCCAXG_SEN <37>

VSSAXG_SEN <37>

H_TDO <39>

H_TDI <39>

H_TCK <39>

H_TMS <39>

H_TRST_L <39>

H_PRDY_L <39>

H_PREQ_L <39>

XDP_H_CLK_DP <39>

XDP_H_CLK_DN <39>

BPM_L_[0..7]

*

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 2

GND

1 2

R335 0-04R335 0-04

BPM_L_[0..7] <39>

CPU_PWROK

PECI

CATERR_L

PROCHOT_L

CPU_THERMTRIP_L

CATERR_L, CPU_THERMTRIP_L

Pull Up Resistor 2010 MoW05 Remove

CFG H L

01reserved

reserved reserved

2

NORMAL PEGLANE REVERSAL[0], X16

3

reserved reserved

4

reserved reserved

5

6

7

reserved reserved reserved

8

reserved

9

reserved

10

reserved

11

reserved reserved reserved

12

reserved

13

reserved

14

reserved

15

reserved

CFG_[0..17] HAVE INTERNAL PULL-UPS

1 X 16

2 X 8

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

CPU - MISC

CPU - MISC

CPU - MISC

R244

R244

4.7K-04

4.7K-04

*

*

H_TRST_L

H_TMS

H_TDI

H_TCK

SEL0 SEL1PCIE CONFIG

0111

H61H2-LM5

H61H2-LM5

H61H2-LM5

VTT_SEL <36>

+3VSB

R336

R336

220-04-O

220-04-O

1 2

FP_RST_L

R307 51.1-04-OR307 51.1-04-O

R259 1K-04-OR259 1K-04-O

R286 1K-04-OR286 1K-04-O

R261 51-04R261 51-04

R260 51-04-OR260 51-04-O

reserved

reserved

REVERSE

reserved

reserved

*

*

reserved

reserved

reserved reserved

reserved

reserved

reserved

reserved

FP_RST_L <14,31,39>

RN14 51-8P4R-04-ORN14 51-8P4R-04-O

1 2

3 4

5 6

7 8

Close to CPU

1 2

1 2

1 2

1 2

1 2

DESCRIPTION

reserved

PEOFGSEL[0]

PEOFGSEL[1]

reserved

reserved

reserved

reserved

reserved

reserved

CFG[5:6]:

11=DEFAULT X16,

01=2X8,

10=RESERVED,

00=X8,X4,X4

5 44Friday, March 02, 2012

5 44Friday, March 02, 2012

5 44Friday, March 02, 2012

1

+V_CPUVTT

GND

+V_CPUVTT

V 0.1

V 0.1

V 0.1

+V_1P8_SFR

1 2

R246 2.2K-04R246 2.2K-04

21

GND

D D

VR_HOT_L<37>

DRAM_PWROK<14>

CPU_RST_L<8,39>

CPU_PWROK<14,39>

C C

1 2

R357 10K-04R357 10K-04

SLP3_L

B B

.1U-X7-04C217 .1U-X7-04C217

PROC_SEL

PROC_SEL

B

QN2_B

QN2

QN2

PMBS3904-S

PMBS3904-S

SLP3_L<14,20,22,24,27,29,33,34,35,40>

DRAM_PWROK

+3VSB

R349

R349

10K-04

10K-04

1 2

QN2_C

E C

GND

R262 0-04R262 0-04

R407 120-04R407 120-04

R287 0-04R287 0-04

R306 0-04R306 0-04

1 2

R350 1K-04R350 1K-04

1 2

R356 1K-04R356 1K-04

1 2

R355 1K-04-OR355 1K-04-O

Address:??ch

U1

C377

C377

.1U-X7-04-O

.1U-X7-04-O

2 1

GND

A A

Programmable DIMM_VREF_CPU CIRCUIT

1

2

3

U1

VDD

GND

SCL

AD5247-O

AD5247-O

5

W

SDA

6

A

5

4

DIMM_VREF_CPU_1

SMBDATA_STBYSMBCLK_STBY

Page 6

5

M_DATA_A[0..63]<9>

M_DQS_A_P[0..7]<9>

M_DQS_A_N[0..7]<9>

D D

M_MA_A[0..15]<9>

M_BS_A[0..2]<9>

M_CS_A_L[0..1]<9>

M_CKE_A[0..1]<9>

M_ODT_A[0..1]<9>

M_CLK_A_P[0..1]<9>

M_CLK_A_N[0..1]<9>

M_WE_A_L<9>

M_CAS_A_L<9>

M_RAS_A_L<9>

M_DATA_A[0..63]

M_DQS_A_P[0..7]

M_DQS_A_N[0..7]

M_MA_A[0..15]

M_BS_A[0..2]

M_CS_A_L[0..1]

M_CKE_A[0..1]

M_ODT_A[0..1]

M_CLK_A_P[0..1]

M_CLK_A_N[0..1]

M_WE_A_L

M_CAS_A_L

M_RAS_A_L

DDR3 CH.A

DDR3_DRAMRST_L<9,10>

C C

M_DATA_B[0..63]<10>

M_DQS_B_P[0..7]<10>

M_DQS_B_N[0..7]<10>

M_MA_B[0..15]<10>

M_BS_B[0..2]<10>

M_CS_B_L[0..1]<10>

M_CKE_B[0..1]<10>

M_ODT_B[0..1]<10>

M_CLK_B_P[0..1]<10>

M_CLK_B_N[0..1]<10>

M_WE_B_L<10>

M_CAS_B_L<10>

M_RAS_B_L<10>

DDR3_DRAMRST_L

M_DATA_B[0..63]

M_DQS_B_P[0..7]

M_DQS_B_N[0..7]

M_MA_B[0..15]

M_BS_B[0..2]

M_CS_B_L[0..1]

M_CKE_B[0..1]

M_ODT_B[0..1]

M_CLK_B_P[0..1]

M_CLK_B_N[0..1]

M_WE_B_L

M_CAS_B_L

M_RAS_B_L

DDR3 CH.B

B B

4

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

M_DQS_A_P0

M_DQS_A_P1

M_DQS_A_P2

M_DQS_A_P3

M_DQS_A_P4

M_DQS_A_P5

M_DQS_A_P6

M_DQS_A_P7

M_DQS_A_N0

M_DQS_A_N1

M_DQS_A_N2

M_DQS_A_N3

M_DQS_A_N4

M_DQS_A_N5

M_DQS_A_N6

M_DQS_A_N7

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AU35

AW3 7

AU39

AU36

AW3 5

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AK3

AP3

AW4

AV8

AV37

AP38

AK38

AF38

AK2

AP2

AV4

AW8

AV36

AP39

AK39

AF39

CPU1C

CPU1C

BALLMAP_REV=1.4

BALLMAP_REV=1.4

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_1 0

SA_DQ_1 1

SA_DQ_1 2

SA_DQ_1 3

SA_DQ_1 4

SA_DQ_1 5

SA_DQ_1 6

SA_DQ_1 7

SA_DQ_1 8

SA_DQ_1 9

SA_DQ_2 0

SA_DQ_2 1

SA_DQ_2 2

SA_DQ_2 3

SA_DQ_2 4

SA_DQ_2 5

SA_DQ_2 6

SA_DQ_2 7

SA_DQ_2 8

SA_DQ_2 9

SA_DQ_3 0

SA_DQ_3 1

SA_DQ_3 2

SA_DQ_3 3

SA_DQ_3 4

SA_DQ_3 5

SA_DQ_3 6

SA_DQ_3 7

SA_DQ_3 8

SA_DQ_3 9

SA_DQ_4 0

SA_DQ_4 1

SA_DQ_4 2

SA_DQ_4 3

SA_DQ_4 4

SA_DQ_4 5

SA_DQ_4 6

SA_DQ_4 7

SA_DQ_4 8

SA_DQ_4 9

SA_DQ_5 0

SA_DQ_5 1

SA_DQ_5 2

SA_DQ_5 3

SA_DQ_5 4

SA_DQ_5 5

SA_DQ_5 6

SA_DQ_5 7

SA_DQ_5 8

SA_DQ_5 9

SA_DQ_6 0

SA_DQ_6 1

SA_DQ_6 2

SA_DQ_6 3

SA_DQS_ 0

SA_DQS_ 1

SA_DQS_ 2

SA_DQS_ 3

SA_DQS_ 4

SA_DQS_ 5

SA_DQS_ 6

SA_DQS_ 7

SA_DQS# _0

SA_DQS# _1

SA_DQS# _2

SA_DQS# _3

SA_DQS# _4

SA_DQS# _5

SA_DQS# _6

SA_DQS# _7

SKT_H2_CRB

SKT_H2_CRB

3

Pay Attention to

This Part!

AV27

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_1 0

SA_MA_1 1

SA_MA_1 2

SA_MA_1 3

SA_MA_1 4

SA_MA_1 5

SA_W E#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS#_ 0

SA_CS#_ 1

SA_CS#_ 2

SA_CS#_ 3

SA_CKE_ 0

SA_CKE_ 1

SA_CKE_ 2

SA_CKE_ 3

SA_ODT_ 0

SA_ODT_ 1

SA_ODT_ 2

SA_ODT_ 3

SA_CK_0

SA_CK#_ 0

SA_CK_1

SA_CK#_ 1

SA_CK_2

SA_CK#_ 2

SA_CK_3

SA_CK#_ 3

SM_DRAM RST#

SA_DQS_ 8

SA_DQS# _8

SA_ECC_ CB_0

SA_ECC_ CB_1

SA_ECC_ CB_2

SA_ECC_ CB_3

SA_ECC_ CB_4

SA_ECC_ CB_5

SA_ECC_ CB_6

SA_ECC_ CB_7

DDR_0

DDR_0

3 OF 10

3 OF 10

M_MA_A0

AY24

M_MA_A1

AW2 4

M_MA_A2

AW2 3

M_MA_A3

AV23

M_MA_A4

AT24

M_MA_A5

AT23

M_MA_A6

AU22

M_MA_A7

AV22

M_MA_A8

AT22

M_MA_A9

AV28

M_MA_A10

AU21

M_MA_A11

AT21

M_MA_A12

AW3 2

M_MA_A13

AU20

M_MA_A14

AT20

M_MA_A15

AW2 9

M_WE_A_L

AV30

M_CAS_A_L

AU28

M_RAS_A_L

AY29

M_BS_A0

AW2 8

M_BS_A1

AV20

M_BS_A2

AU29

M_CS_A_L0

AV32

M_CS_A_L1

AW3 0

AU33

AV19

M_CKE_A0

AT19

M_CKE_A1

AU18

AV18

AV31

M_ODT_A0

AU32

M_ODT_A1

AU30

AW3 3

AY25

M_CLK_A_P0

AW2 5

M_CLK_A_N0

AU24

M_CLK_A_P1

AU25

M_CLK_A_N1

AW2 7

AY27

AV26

AW2 6

AW1 8

DDR3_DRAMRST_R_L

AV13

AV12

AU12

AU14

AW1 3

AY13

AU13

AU11

AY12

AW1 2

Desktop dosen't support ECC Desktop dosen't support ECC

1 2

R479 0-04R479 0-04

C428

C428

.1U-X7-04-O

.1U-X7-04-O

For RC Filter

DDR3_DRAMRST_L

2 1

GND

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B13

M_DATA_B9

M_DATA_B11

M_DATA_B15

M_DATA_B12

M_DATA_B8

M_DATA_B14

M_DATA_B10

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B52

M_DATA_B55

M_DATA_B51

M_DATA_B54

M_DATA_B49

M_DATA_B53

M_DATA_B50

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

M_DQS_B_P0

M_DQS_B_P1

M_DQS_B_P2

M_DQS_B_P3

M_DQS_B_P4

M_DQS_B_P5

M_DQS_B_P6

M_DQS_B_P7

M_DQS_B_N0

M_DQS_B_N1

M_DQS_B_N2

M_DQS_B_N3

M_DQS_B_N4

M_DQS_B_N5

M_DQS_B_N6

M_DQS_B_N7

DDR3 CH.A DDR3 CH.B

2

CPU1D

CPU1D

BALLMAP_REV=1.4

AG7

AG8

AJ9

AJ8

AG5

AG6

AJ6

AJ7

AL7

AM7

AM10

AL10

AL6

AM6

AL9

AM9

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AH7

AM8

AR8

AN13

AN29

AP33

AL33

AG35

AH6

AL8

AP8

AN12

AN28

AR33

AM33

AG34

BALLMAP_REV=1.4

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_1 0

SB_DQ_1 1

SB_DQ_1 2

SB_DQ_1 3

SB_DQ_1 4

SB_DQ_1 5

SB_DQ_1 6

SB_DQ_1 7

SB_DQ_1 8

SB_DQ_1 9

SB_DQ_2 0

SB_DQ_2 1

SB_DQ_2 2

SB_DQ_2 3

SB_DQ_2 4

SB_DQ_2 5

SB_DQ_2 6

SB_DQ_2 7

SB_DQ_2 8

SB_DQ_2 9

SB_DQ_3 0

SB_DQ_3 1

SB_DQ_3 2

SB_DQ_3 3

SB_DQ_3 4

SB_DQ_3 5

SB_DQ_3 6

SB_DQ_3 7

SB_DQ_3 8

SB_DQ_3 9

SB_DQ_4 0

SB_DQ_4 1

SB_DQ_4 2

SB_DQ_4 3

SB_DQ_4 4

SB_DQ_4 5

SB_DQ_4 6

SB_DQ_4 7

SB_DQ_4 8

SB_DQ_4 9

SB_DQ_5 0

SB_DQ_5 1

SB_DQ_5 2

SB_DQ_5 3

SB_DQ_5 4

SB_DQ_5 5

SB_DQ_5 6

SB_DQ_5 7

SB_DQ_5 8

SB_DQ_5 9

SB_DQ_6 0

SB_DQ_6 1

SB_DQ_6 2

SB_DQ_6 3

SB_DQS_ 0

SB_DQS_ 1

SB_DQS_ 2

SB_DQS_ 3

SB_DQS_ 4

SB_DQS_ 5

SB_DQS_ 6

SB_DQS_ 7

SB_DQS# _0

SB_DQS# _1

SB_DQS# _2

SB_DQS# _3

SB_DQS# _4

SB_DQS# _5

SB_DQS# _6

SB_DQS# _7

SKT_H2_CRB

SKT_H2_CRB

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_1 0

SB_MA_1 1

SB_MA_1 2

SB_MA_1 3

SB_MA_1 4

SB_MA_1 5

SA_CK[2]

SA_CK[1]

SA_ODT[2 ]

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS#_ 0

SB_CS#_ 1

SB_CS#_ 2

SB_CS#_ 3

SB_CKE_ 0

SB_CKE_ 1

SB_CKE_ 2

SB_CKE_ 3

SB_ODT_ 0

SB_ODT_ 1

SB_ODT_ 2

SB_ODT_ 3

SB_CK_0

SB_CK#_ 0

SB_CK_1

SB_CK#_ 1

SB_CK_2

SB_CK#_ 2

SB_CK_3

SB_CK#_ 3

SB_DQS_ 8

SB_DQS# _8

SB_ECC_ CB_0

SB_ECC_ CB_1

SB_ECC_ CB_2

SB_ECC_ CB_3

SB_ECC_ CB_4

SB_ECC_ CB_5

SB_ECC_ CB_6

SB_ECC_ CB_7

DDR_1

DDR_1

4 OF 10

4 OF 10

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW1 7

AN25

AN26

AL25

AT26

AU16

AY15

AW1 5

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

1

M_MA_B0

M_MA_B1

M_MA_B2

M_MA_B3

M_MA_B4

M_MA_B5

M_MA_B6

M_MA_B7

M_MA_B8

M_MA_B9

M_MA_B10

M_MA_B11

M_MA_B12

M_MA_B13

M_MA_B14

M_MA_B15

M_WE_B_L

M_CAS_B_L

M_RAS_B_L

M_BS_B0

M_BS_B1

M_BS_B2

M_CS_B_L0

M_CS_B_L1

M_CKE_B0

M_CKE_B1

M_ODT_B0

M_ODT_B1

M_CLK_B_P0

M_CLK_B_N0

M_CLK_B_P1

M_CLK_B_N1

A A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

CPU - DDR3

CPU - DDR3

CPU - DDR3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H61H2-LM5

H61H2-LM5

H61H2-LM5

1

6 44Friday, March 02, 2012

6 44Friday, March 02, 2012

6 44Friday, March 02, 2012

V 0.1

V 0.1

V 0.1

Page 7

5

MAX 112A

CPU1F

+VCORE

D D

C C

B B

A A

CPU1F

BALLMAP_REV=1.4

BALLMAP_REV=1.4

A12

VCC_001

A13

VCC_002

A14

VCC_003

A15

VCC_004

A16

VCC_005

A18

VCC_006

A24

VCC_007

A25

VCC_008

A27

VCC_009

A28

VCC_010

B15

VCC_011

B16

VCC_012

B18

VCC_013

B24

VCC_014

B25

VCC_015

B27

VCC_016

B28

VCC_017

B30

VCC_018

B31

VCC_019

B33

VCC_020

B34

VCC_021

C15

VCC_022

C16

VCC_023

C18

VCC_024

C19

VCC_025

C21

VCC_026

C22

VCC_027

C24

VCC_028

C25

VCC_029

C27

VCC_030

C28

VCC_031

C30

VCC_032

C31

VCC_033

C33

VCC_034

C34

VCC_035

C36

VCC_036

D13

VCC_037

D14

VCC_038

D15

VCC_039

D16

VCC_040

D18

VCC_041

D19

VCC_042

D21

VCC_043

D22

VCC_044

D24

VCC_045

D25

VCC_046

D27

VCC_047

D28

VCC_048

D30

VCC_049

D31

VCC_050

D33

VCC_051

D34

VCC_052

D35

VCC_053

D36

VCC_054

E15

VCC_055

E16

VCC_056

E18

VCC_057

E19

VCC_058

E21

VCC_059

E22

VCC_060

E24

VCC_061

E25

VCC_062

E27

VCC_063

E28

VCC_064

E30

VCC_065

E31

VCC_066

E33

VCC_067

E34

VCC_068

E35

VCC_069

F15

VCC_070

F16

VCC_071

F18

VCC_072

F19

VCC_073

F21

VCC_074

F22

VCC_075

F24

VCC_076

F25

VCC_077

F27

VCC_078

F28

VCC_079

F30

VCC_080

F31

VCC_081

SKT_H2_CRB

SKT_H2_CRB

6 OF 10

6 OF 10

5

VCC_082

VCC_083

VCC_084

VCC_085

VCC_086

VCC_087

VCC_088

VCC_089

VCC_090

VCC_091

VCC_092

VCC_093

VCC_094

VCC_095

VCC_096

VCC_097

VCC_098

VCC_099

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

1.05V/1.00V

MAX 8.5A

+V_CPUVTT +VAXG+VCORE +V_1P5_SM

0.925V/0.85V

MAX 8.8A

+V_SA

1.8V

MAX 1A

+V_1P8_SFR

PLACE ALL 0805 CAPS INSIDE CPU SOCKET CAVITY, TOP-SIDE.Total:30PCS.

+V_CPUVTT

21

C361

C361

22U-6V3-08

22U-6V3-08

21

C334

C334

22U-6V3-08

22U-6V3-08

+VCORE

21

21

C304

C304

C309

C309

22U-6V3-08

22U-6V3-08

22U-6V3-08

22U-6V3-08

21

21

C306

C306

22U-6V3-08

22U-6V3-08

C307

C307

22U-6V3-08

22U-6V3-08

M13

A11

A7

AA3

AB8

AF8

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

B9

D10

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

H10

H11

H12

J10

K10

K11

L11

L12

M10

M11

M12

AK11

AK12

21

C333

C333

22U-6V3-08

22U-6V3-08

21

C343

C343

22U-6V3-08

22U-6V3-08

21

CPU1G

CPU1G

VCCIO_34

VCCIO_01

VCCIO_02

VCCIO_03

VCCIO_04

VCCIO_05

VCCIO_06

VCCIO_07

VCCIO_08

VCCIO_09

VCCIO_10

VCCIO_11

VCCIO_12

VCCIO_13

VCCIO_14

VCCIO_15

VCCIO_16

VCCIO_17

VCCIO_18

VCCIO_19

VCCIO_20

VCCIO_21

VCCIO_22

VCCIO_23

VCCIO_24

VCCIO_25

VCCIO_26

VCCIO_27

VCCIO_28

VCCIO_29

VCCIO_30

VCCIO_31

VCCIO_32

VCCIO_33

VCCIO_35

VCCIO_36

VCCIO_37

VCCIO_38

VCCIO_39

VCCIO_40

VCCIO_41

VCCIO_42

VCCIO_43

VCCIO_44

VCCIO_45

VCCSA_0 1

VCCSA_0 2

VCCSA_0 3

VCCSA_0 4

VCCSA_0 5

VCCSA_0 6

VCCSA_0 7

VCCSA_0 8

VCCSA_0 9

VCCSA_1 0

VCCSA_1 1

VCCPLL_ 01

VCCPLL_ 02

SKT_H2_CRB

SKT_H2_CRB

21

C305

C305

22U-6V3-08

22U-6V3-08

4

BALLMAP_REV=1.4

BALLMAP_REV=1.4

21

21

C308

C308

22U-6V3-08

22U-6V3-08

4

C358

C358

22U-6V3-08

22U-6V3-08

C329

C329

22U-6V3-08

22U-6V3-08

GND

21

C301

C301

22U-6V3-08

22U-6V3-08

VDDQ_01

VDDQ_02

VDDQ_04

VDDQ_05

VDDQ_06

VDDQ_07

VDDQ_08

VDDQ_09

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_03

CHS_GND 01

CHS_GND 02

CHS_GND 03

CHS_GND 04

CHS_GND 05

CHS_GND 06

CHS_GND 07

CHS_GND 08

CHS_GND 09

CHS_GND 10

CHS_GND 11

CHS_GND 12

CHS_GND 13

CHS_GND 14

CHS_GND 15

CHS_GND 16

POWER

POWER

7 OF 10

7 OF 10

21

21

GND

21

C239

C239

22U-6V3-08

22U-6V3-08

21

C332

C332

22U-6V3-08

22U-6V3-08

C330

C330

22U-6V3-08

22U-6V3-08

C300

C300

22U-6V3-08

22U-6V3-08

1.5V

MAX 4.5A

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW3 1

AY23

AY26

AY28

AJ20

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

GND

+VAXG

21

C331

C331

22U-6V3-08

22U-6V3-08

+V_1P8_SFR

C354

C354

.1U-X7-04

.1U-X7-04

2 1

21

C238

C238

22U-6V3-08

22U-6V3-08

21

2 1

GND

C312

C312

22U-6V3-08

22U-6V3-08

C351

C351

22U-6V3-08

22U-6V3-08

21

C236

C236

22U-6V3-08

22U-6V3-08

MAX 35A

21

C346

C346

22U-6V3-08

22U-6V3-08

+V_1P5_SM

21

GND

21

GND

3

CPU1H

CPU1H

VBALLMAP_REV=1.4

VBALLMAP_REV=1.4

AB33

VCCAXG_ 01

AB34

VCCAXG_ 02

AB35

VCCAXG_ 03

AB36

VCCAXG_ 04

AB37

VCCAXG_ 05

AB38

VCCAXG_ 06

AB39

VCCAXG_ 07

AB40

VCCAXG_ 08

AC33

VCCAXG_ 09

AC34

VCCAXG_ 10

AC35

VCCAXG_ 11

AC36

VCCAXG_ 12

AC37

VCCAXG_ 13

AC38

VCCAXG_ 14

AC39

VCCAXG_ 15

AC40

VCCAXG_ 16

T33

VCCAXG_ 17

T34

VCCAXG_ 18

T35

VCCAXG_ 19

T36

VCCAXG_ 20

T37

VCCAXG_ 21

T38

VCCAXG_ 22

T39

VCCAXG_ 23

T40

VCCAXG_ 24

U33

VCCAXG_ 25

U34

VCCAXG_ 26

U35

VCCAXG_ 27

U36

VCCAXG_ 28

U37

VCCAXG_ 29

U38

VCCAXG_ 30

U39

VCCAXG_ 31

U40

VCCAXG_ 32

W33

VCCAXG_ 33

W34

VCCAXG_ 34

W35

VCCAXG_ 35

W36

VCCAXG_ 36

W37

VCCAXG_ 37

W38

VCCAXG_ 38

Y33

VCCAXG_ 39

Y34

VCCAXG_ 40

Y35

VCCAXG_ 41

Y36

VCCAXG_ 42

Y37

VCCAXG_ 43

Y38

VCCAXG_ 44

SKT_H2_CRB

SKT_H2_CRB

21

C320

C320

22U-6V3-08

22U-6V3-08

21

C352

C352

C359

C359

22U-6V3-08

22U-6V3-08

22U-6V3-08

22U-6V3-08

C237

C237

22U-6V3-08

22U-6V3-08

3

21

C311

C311

22U-6V3-08

22U-6V3-08

8 OF 10

8 OF 10

21

C360

C360

22U-6V3-08

22U-6V3-08

21

GND

C336

C336

22U-6V3-08

22U-6V3-08

2

1

DECOUPLING & STITCHING CAPS.

+V_CPUVTT

C365

2 1

2 1

2 1

2 1

C365

.1U-X7-04

.1U-X7-04

C350

C350

.1U-X7-04

.1U-X7-04

C246

C246

.1U-X7-04

.1U-X7-04

C268

C268

.1U-X7-04

.1U-X7-04

2 1

2 1

2 1

2 1

C347

C347

.1U-X7-04

.1U-X7-04

C368

C368

.1U-X7-04

.1U-X7-04

C244

C244

.1U-X7-04

.1U-X7-04

C243

C243

.1U-X7-04

.1U-X7-04

2 1

2 1

2 1

2 1

C362

C362

.1U-X7-04

.1U-X7-04

C371

C371

.1U-X7-04

.1U-X7-04

C265

C265

.1U-X7-04

.1U-X7-04

C322

C322

.1U-X7-04

.1U-X7-04

2 1

2 1

2 1

C283

C283

.1U-X7-04

.1U-X7-04

C245

C245

.1U-X7-04

.1U-X7-04

C274

C274

.1U-X7-04

.1U-X7-04

GND

2 1

C279

C279

.1U-X7-04

.1U-X7-04

PLACE NEAR SKT EDGE OUTSIDE CAVITY.

+V_SA+V_CPUVTT

21

GND

C256

C256

22U-6V3-08

22U-6V3-08

21

GND

C287

C287

22U-6V3-08

22U-6V3-08

PLACE ALL 0805 CAPS INSIDE CPU SOCKET CAVITY, BOTTPM-SIDE.Total:25PCS.

+VAXG

21

SC33

SC33

22U-X5-08-X

22U-X5-08-X

21

SC22

SC22

22U-X5-08-X

22U-X5-08-X

1

2

3

GND

+V_CPUVTT

21

SC34

SC34

22U-X5-08-X-O

22U-X5-08-X-O

SC70

SC70

470U-X-O

470U-X-O

POS CAP

21

SC21

SC21

22U-X5-08-X

22U-X5-08-X

21

SC23

SC23

22U-X5-08-X

22U-X5-08-X

21

SC26

SC26

22U-X5-08-X-O

22U-X5-08-X-O

2

21

SC18

SC18

22U-X5-08-X

22U-X5-08-X

GND

21

SC29

SC29

22U-X5-08-X

22U-X5-08-X

GND

21

SC35

SC35

22U-X5-08-X-O

22U-X5-08-X-O

+VCORE

21

SC10

SC10

22U-X5-08-X-O

22U-X5-08-X-O

21

SC15

SC15

22U-6V3-08-X-O

22U-6V3-08-X-O

21

SC68

SC68

22U-X5-08-X-O

22U-X5-08-X-O

21

SC25

SC25

22U-X5-08-X-O

22U-X5-08-X-O

Title

Title

Title

CPU - PWR

CPU - PWR

CPU - PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

21

21

21

21

SC24

SC24

22U-X5-08-X-O

22U-X5-08-X-O

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

21

SC11

SC11

22U-6V3-08-X-O

22U-6V3-08-X-O

21

SC14

SC14

22U-6V3-08-X-O

22U-6V3-08-X-O

21

SC36

SC36

22U-X5-08-X-O

22U-X5-08-X-O

21

SC20

SC20

22U-X5-08-X-O

22U-X5-08-X-O

H61H2-LM5

H61H2-LM5

H61H2-LM5

1

SC16

SC16

22U-6V3-08-X

22U-6V3-08-X

SC9

SC9

22U-X5-08-X

22U-X5-08-X

SC28

SC28

22U-X5-08-X

22U-X5-08-X

21

GND

21

SC12

SC12

22U-6V3-08-X

22U-6V3-08-X

GND

21

SC13

SC13

22U-6V3-08-X

22U-6V3-08-X

GND

21

SC27

SC27

22U-X5-08-X

22U-X5-08-X

GND

SC19

SC19

22U-X5-08-X-O

22U-X5-08-X-O

7 44Friday, March 02, 2012

7 44Friday, March 02, 2012

7 44Friday, March 02, 2012

V 0.1

V 0.1

V 0.1

Page 8

5

CPU1J

CPU1I

CPU1I

BALLMAP_REV=1.4

BALLMAP_REV=1.4

A17

VSS_001

A23

VSS_002

A26

VSS_003

A29

VSS_004

A35

VSS_005

AA33

VSS_006

D D

C C

B B

A A

AA34

AA35

AA36

AA37

AA38

AC1

AC6

AD33

AD36

AD38

AD39

AD40

AD5

AD8

AE33

AE36

AF34

AF36

AF37

AF40

AG36

AH2

AH3

AH33

AH36

AH37

AH38

AH39

AH40

AH5

AH8

AJ12

AJ15

AJ18

AJ21

AJ25

AJ27

AJ36

AK10

AK13

AK14

AK16

AK22

AK28

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK40

AL11

AL14

AL17

AL19

AL24

AL27

AL30

AL36

AM1

AM11

AM14

AM17

AM2

AM21

AM23

AM25

AV39

AA6

AB5

AE3

AF1

AF5

AF6

AF7

AK1

AK4

AK5

AK6

AK7

AK8

AK9

AL5

AJ5

A4

VSS_007

VSS_008

VSS_009

VSS_010

VSS_011

VSS_012

VSS_013

VSS_014

VSS_015

VSS_016

VSS_017

VSS_018

VSS_019

VSS_020

VSS_021

VSS_022

VSS_023

VSS_024

VSS_025

VSS_026

VSS_027

VSS_028

VSS_029

VSS_030

VSS_031

VSS_032

VSS_033

VSS_034

VSS_035

VSS_036

VSS_037

VSS_038

VSS_039

VSS_040

VSS_041

VSS_042

VSS_043

VSS_044

VSS_045

VSS_046

VSS_047

VSS_048

VSS_049

VSS_050

VSS_051

VSS_052

VSS_053

VSS_054

VSS_055

VSS_056

VSS_057

VSS_058

VSS_059

VSS_060

VSS_061

VSS_062

VSS_063

VSS_064

VSS_065

VSS_066

VSS_067

VSS_068

VSS_069

VSS_070

VSS_071

VSS_072

VSS_073

VSS_074

VSS_075

VSS_076

VSS_077

VSS_078

VSS_079

VSS_080

VSS_081

VSS_082

VSS_083

VSS_084

VSS_085

VSS_086

VSS_087

VSS_088

VSS_089

VSS_090

VSS_NCT F_01

VSS_NCT F_02

SKT_H2_CRB

SKT_H2_CRB

9 OF 10

9 OF 10

VSS_091

VSS_092

VSS_093

VSS_094

VSS_095

VSS_096

VSS_097

VSS_098

VSS_099

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

GNDGND GND GND

CPU1J

BALLMAP_REV=1.4

BALLMAP_REV=1.4

AV11

VSS_181

AV14

VSS_182

AV17

VSS_183

AV3

VSS_184

AV35

VSS_185

AV38

VSS_186

AV6

VSS_187

AW1 0

VSS_188

AW1 1

VSS_189

AW1 4

VSS_190

AW1 6

VSS_191

AW3 6

VSS_192

AW6

VSS_193

AY11

VSS_194

AY14

VSS_195

AY18

VSS_196

AY35

VSS_197

AY4

VSS_198

AY6

VSS_199

AY8

VSS_200

B10

VSS_201

B13

VSS_202

B14

VSS_203

B17

VSS_204

B23

VSS_205

B26

VSS_206

B29

VSS_207

B32

VSS_208

B35

VSS_209

B38

VSS_210

B6

VSS_211

C11

VSS_212

C12

VSS_213

C17

VSS_214

C20

VSS_215

C23

VSS_216

C26

VSS_217

C29

VSS_218

C32

VSS_219

C35

VSS_220

C7

VSS_221

C8

VSS_222

D17

VSS_223

D2

VSS_224

D20

VSS_225

D23

VSS_226

D26

VSS_227

D29

VSS_228

D32

VSS_229

D37

VSS_230

D39

VSS_231

D4

VSS_232

D5

VSS_233

D9

VSS_234

E11

VSS_235

E12

VSS_236

E17

VSS_237

E20

VSS_238

E23

VSS_239

E26

VSS_240

E29

VSS_241

E32

VSS_242

E36

VSS_243

E7

VSS_244

E8

VSS_245

F1

VSS_246

F10

VSS_247

F13

VSS_248

F14

VSS_249

F17

VSS_250

F2

VSS_251

F20

VSS_252

F23

VSS_253

F26

VSS_254

F29

VSS_255

F35

VSS_256

F37

VSS_257

F39

VSS_258

F5

VSS_259

F6

VSS_260

F9

VSS_261

G11

VSS_262

G12

VSS_263

G17

VSS_264

G20

VSS_265

G23

VSS_266

G26

VSS_267

G29

VSS_268

G34

VSS_269

G7

VSS_270

AY37

VSS_NCT F_03

B3

VSS_NCT F_04

SKT_H2_CRB

SKT_H2_CRB

4

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

10 of 10

10 of 10

G8

H1

H17

H2

H20

H23

H26

H29

H33

H35

H37

H39

H5

H6

H9

J11

J17

J20

J23

J26

J29

J32

K1

K12

K13

K14

K17

K2

K20

K23

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

PCH_PLTRST_L<14,23,28,29,39>

+3VSB

147

3 4

GND

U3-2

U3-2

74LVC14-O

74LVC14-O

3

R625

R625

10K-04-O

10K-04-O

PCH_PLTRST_L QN5_B

5 6

1 2

C529

C529

R622

R622

.1U-04-O

.1U-04-O

5.1K-04-O

5.1K-04-O

1 2

U3-3

U3-3

147

74LVC14-O

74LVC14-O

147

8 9

B

2 1

GNDGND

U3-4

U3-4

74LVC14-O

74LVC14-O

+3VSB

R593

R593

1K-04-O

1K-04-O

1 2

QN5

QN5

PMBS3904-S-O

PMBS3904-S-O

E C

GND

SIO_PCIRST2_L<29>

QN5_C

147

10 1 1

SIO_PCIRST2_L

+3VSB

147

1 2

GND

U3-5

U3-5

74LVC14-O

74LVC14-O

2

R601 0-04R601 0-04

1 2

U3-1

U3-1

74LVC14-O

74LVC14-O

U3

P/N:02-177-014030 IC TTL.SN74LVC14APW..TSSOP 14P..LEAD-FREE.TI

Close to U3

R608

R608

2K-1-04

2K-1-04

1 2

GND

1.1V

R618

R618

1K-1-04

1K-1-04

1 2

PLTRST_L Driving Circuit

U3-6

U3-6

147

12 1 3

74LVC14-O

74LVC14-O

1

CPU_RST_LCPU_RST_R_L

CPU_RST_L <5,39>

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

CPU - GND, CPU_RST_L

CPU - GND, CPU_RST_L

CPU - GND, CPU_RST_L

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H61H2-LM5

H61H2-LM5

H61H2-LM5

1

8 44Friday, March 02, 2012

8 44Friday, March 02, 2012

8 44Friday, March 02, 2012

V 0.1

V 0.1

V 0.1

Page 9

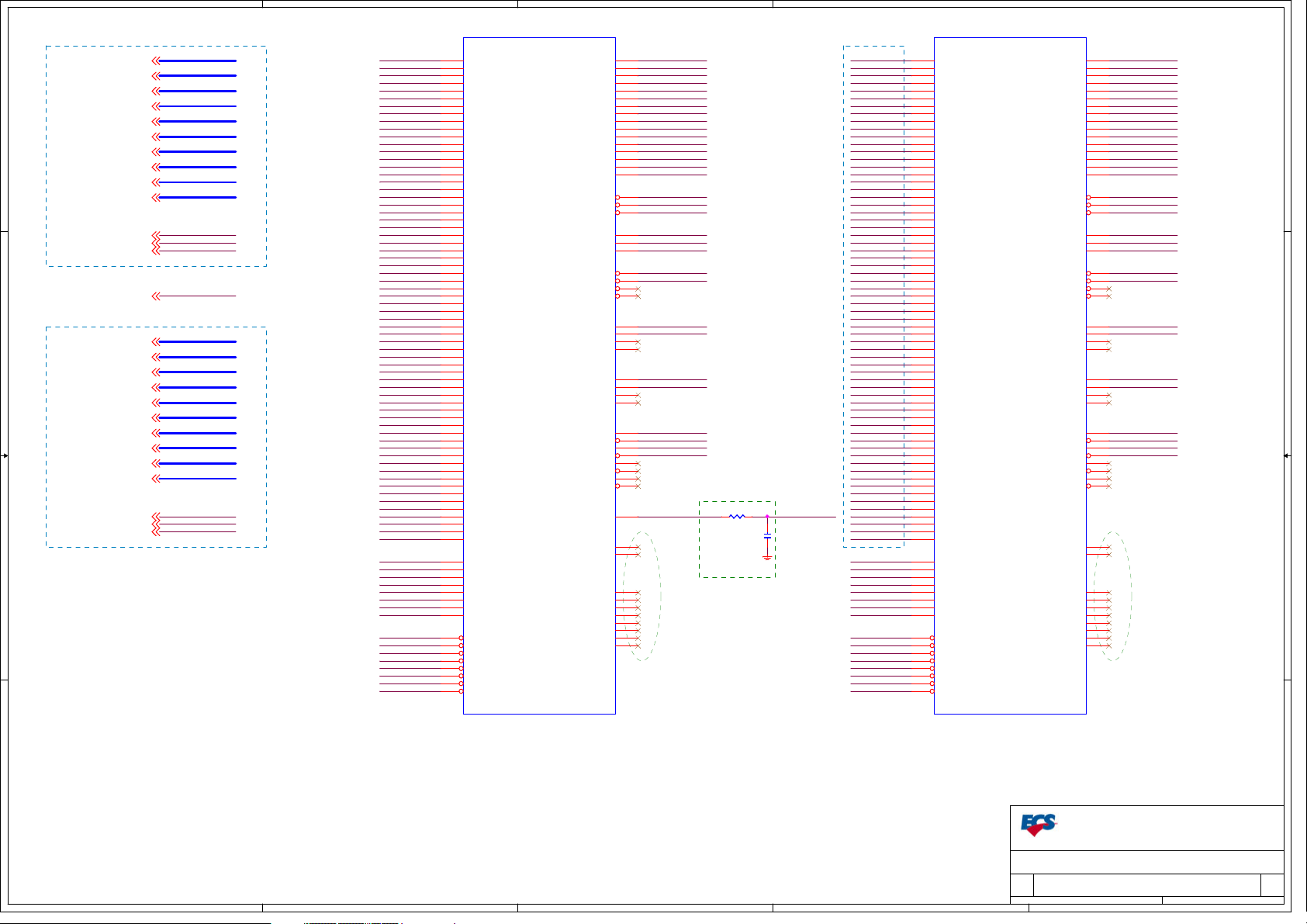

5

M_DQS_A_P[0..7]

M_DQS_A_N[0..7]

Desktop dosen' t

D D

+V_SM_VTT

C C

support ECC

M_DQS_A_P0

M_DQS_A_P1

M_ODT_A0

M_ODT_A1

68

53

167

195

79

FREE49FREE48VTT

CB(0)39CB(1)40CB(2)45CB(3)46CB(4)

NC/TEST4

NC/PAR IN

NC/ERR OUT

VSS

VSS

VSS

VSS

VTT

239

235

232

229

240

120

ODT177ODT0

RSVD

FREE

FREE

198

187

M_DQS_A_N0

158

159

164

165

7

6

16

CB(5)

CB(6)

CB(7)

DQS(0)

DSQ(1)

DQS*(0)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

226

223

220

217

214

211

208

205

202

M_ODT_A[0..1]<6>

M_CS_A_L[0..1]<6>

M_CKE_A[0..1]<6>

M_CLK_A_P[0..1]<6>

M_CLK_A_N[0..1]<6>

M_DQS_A_P2

M_DQS_A_N1

15

25

DSQ*(1)

VSS

VSS

199

166

163

M_DQS_A_P[0..7] <6>

M_DQS_A_N[0..7] <6>

M_DQS_A_P3

M_DQS_A_N2

M_DQS_A_N3

24

34

33

DSQ(2)

DSQ(3)

DSQ*(2)

DSQ*(3)

VSS

VSS

VSS

VSS

VSS

160

157

154

151

148

M_ODT_A[0..1]

M_CS_A_L[0..1]

M_CKE_A[0..1]

M_CLK_A_P[0..1]

M_CLK_A_N[0..1]

M_DQS_A_P4

M_DQS_A_P5

M_DQS_A_N4

M_DQS_A_N5

85

84

94

93

DQS(4)

DQS(5)

DQS*(4)

DQS*(5)

VSS

VSS

VSS

VSS

VSS

VSS

145

142

139

136

133

130

4

The processor memory controller does not

have any DDR3 Data Mask (DM) signals

for either channel. As a result the DM[8:0]

pins of each DDR3 DIMM connector must

be tied directly to ground.

M_DQS_A_N7

M_DQS_A_P6

M_DQS_A_P7

M_DQS_A_N6

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

DSQ(6)

DQS(7)

DQS(8)

DSQ*(6)

DQS*(7)

DQS*(8)

NC/DQS9*

DM0/DQS9

NC/DQS10*

NC/DQS11*

NC/DQS12*

DM1/DQS10

DM2/DQS11

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS98VSS95VSS92VSS89VSS86VSS83VSS80VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS

127

124

121

119

116

113

110

107

104

101

NC/DQS13*

DM3/DQS12

DM4/DQS13

CHANNEL A DIMM

213

NC/DQS14*

DM5/DQS14

+V_1P5_SM

3

M_DATA_A[0..63]

GND

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A0

221

222

230

231

161

162

122

123

DQ(0)3DQ(1)4DQ(2)9DQ(3)10DQ(4)

DQ(5)

NC/DQS15*

NC/DQS16*

DM6/DQS15

NC/DQS17*

DM7/DQS16

DM8/DQS17

VDD

VDD

VDD

VDD

VDD

VDD

2

197

194

191

DIMM_VREF_CA_A<11> M_WE_A_L <6>

DIMM_VREF_DQ_A<11>

VDD

VDD

VDD

186

183

182

179

176

189

+VCC3

M_DATA_A[0..63] <6>

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A6

128

DQ(6)

VDD

173

DIMM_VREF_CA_A

DIMM_VREF_DQ_A

SMB_MEM_CLK

SMB_MEM_DATA

M_DATA_A13

M_DATA_A7

M_DATA_A8

129

12

18

13

131

132

DQ(7)

DQ(8)

DQ(9)

DQ(10)

DQ(11)19DQ(12)

VDD

VDD78VDD75VDD69VDD66VDD65VDD62VDD60VDD57VDDSPD

VDD

72

170

M_BS_A[0..2]<6>

M_DATA_A14

137

DQ(13)

DQ(14)

M_DATA_A15

M_DATA_A16

M_DATA_A17

138

DQ(15)

DQ(16)21DQ(17)22DQ(18)27DQ(19)28DQ(20)

M_BS_A[0..2]

CH.A

DIMM0

DIMM1

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

140

141

DQ(21)

VDD54VDD51VREFCA67VREFDQ

236

L

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

DQ(24)30DQ(25)31DQ(26)36DQ(27)37DQ(28)

SDA

SA1

238

237

GNDGND

SA0SA1

LL

H

M_DATA_A30

149

150

155

DQ(29)

SA0

BA1

BA2

52

117

190

M_BS_A1

M_BS_A2

M_BS_A0

M_DATA_A22

146

147

DQ(22)

DQ(23)

SCL

1

118

M_DATA_A31

156

DQ(30)

BA071CKE1

M_DATA_A32

M_DATA_A33

DQ(31)

DQ(32)81DQ(33)82DQ(34)87DQ(35)88DQ(36)

CKE050S1*76S0*

169

M_CKE_A1

M_CKE_A0

2

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

206

207

DQ(38)

CK1/NU*64CK1/NU63CK0*

DQ(39)

DQ(40)90DQ(41)91DQ(42)96DQ(43)97DQ(44)

185

184A0188A1181

M_DATA_A44

209

CK0

M_MA_A1

M_MA_A0

M_DATA_A34

M_DATA_A35

M_DATA_A36

200

201

DQ(37)

193

M_CS_A_L0

M_CS_A_L1

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

210

215

216

100

105

106

DQ(45)

DQ(46)

DQ(47)

DQ(48)99DQ(49)

DQ(50)

DQ(51)

A261A3

A459A558A6

A756A8

180

178

177A9175

M_MA_A3

M_MA_A2

M_MA_A5

M_MA_A4

M_MA_A8

M_MA_A7

M_MA_A6

M_MA_A[0..15]

M_CLK_A_P0

M_CLK_A_N0

M_CLK_A_P1

M_CLK_A_N1

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

218

219

224

225

108

109

114

115

227

228

233

234

DQ(52)

DQ(53)

DQ(54)

DQ(55)

DQ(56)

DQ(57)

DQ(58)

DQ(59)

DQ(60)

DQ(61)

DQ(62)

DQ(63)

DIMM1DDR3-240P-BL DIMM1DDR3-240P-BL

A10/AP70A1155A12

A13

A14

A15

CAS*74RAS*

WE*

RESET*

172

171

M_MA_A15

M_MA_A14

73

192

168

M_WE_A_L

M_RAS_A_L

M_CAS_A_L

DDR3_DRAMRST_L

M_MA_A[0..15] <6>

174

196

M_MA_A12

M_MA_A13

M_MA_A10

M_MA_A9

M_MA_A11

1

M_RAS_A_L <6>

M_CAS_A_L <6>

DDR3_DRAMRST_L <6,10>

SMBCLK_MAIN<16,28,39>

SMBDATA_MAIN<16,28,39>

SMBCLK_MAIN

SMBDATA_MAIN

close to Dimm slot

B B

A A

For CHANNEL A DIMM1

+V_1P5_SM

C424

C424

C422

C422

.1U-X7-04

.1U-X7-04

.1U-X7-04

.1U-X7-04

2 1

2 1

GND

5

C426

C426

.1U-X7-04

.1U-X7-04

2 1

2 1

C423

C423

.1U-X7-04

.1U-X7-04

+V_SM_VTT +VCC3

C488

2 1

C425

C425

.1U-X7-04

.1U-X7-04

2 1

GND

C488

4.7U-X5-08

4.7U-X5-08

2 1

4

PLACE BETWEEN CHA & CHB.

DO NOT PUNCH VIA.

C495

GND

2 1

C495

.1U-04-O

.1U-04-O

C457

C457

.1U-04

.1U-04

2 1

C471

C471

.1U-04-O

.1U-04-O

1 2

R432 0-04R432 0-04

1 2

R787 0-04R787 0-04

GND GND

12

C436

C436

22P-04-O

22P-04-O

3

SMB_MEM_CLK

SMB_MEM_DATA

12

C438

C438

22P-04-O

22P-04-O

SMB_MEM_CLK <10>

SMB_MEM_DATA <10>

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

DDR3 - CHA DIMM

DDR3 - CHA DIMM

DDR3 - CHA DIMM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom