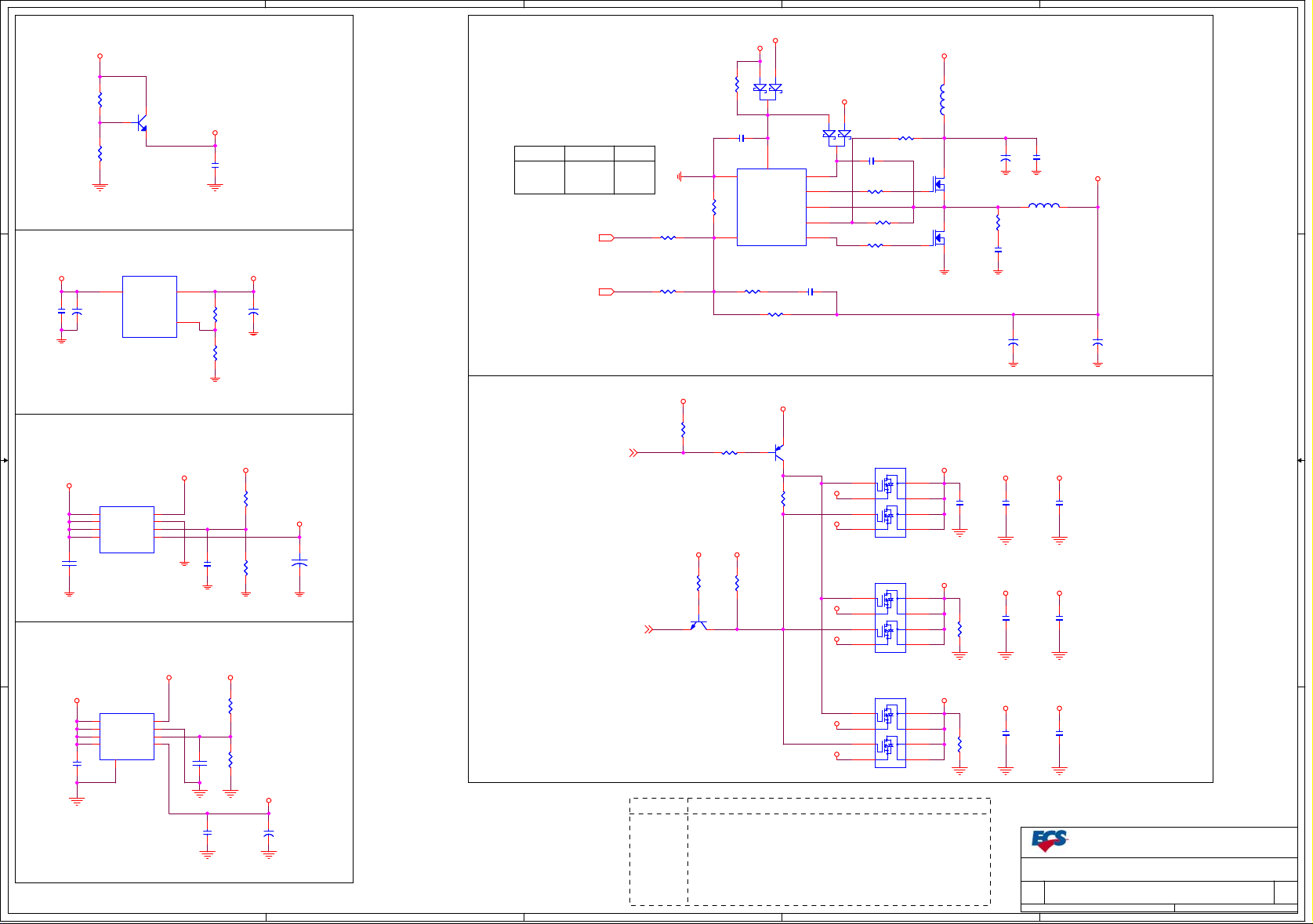

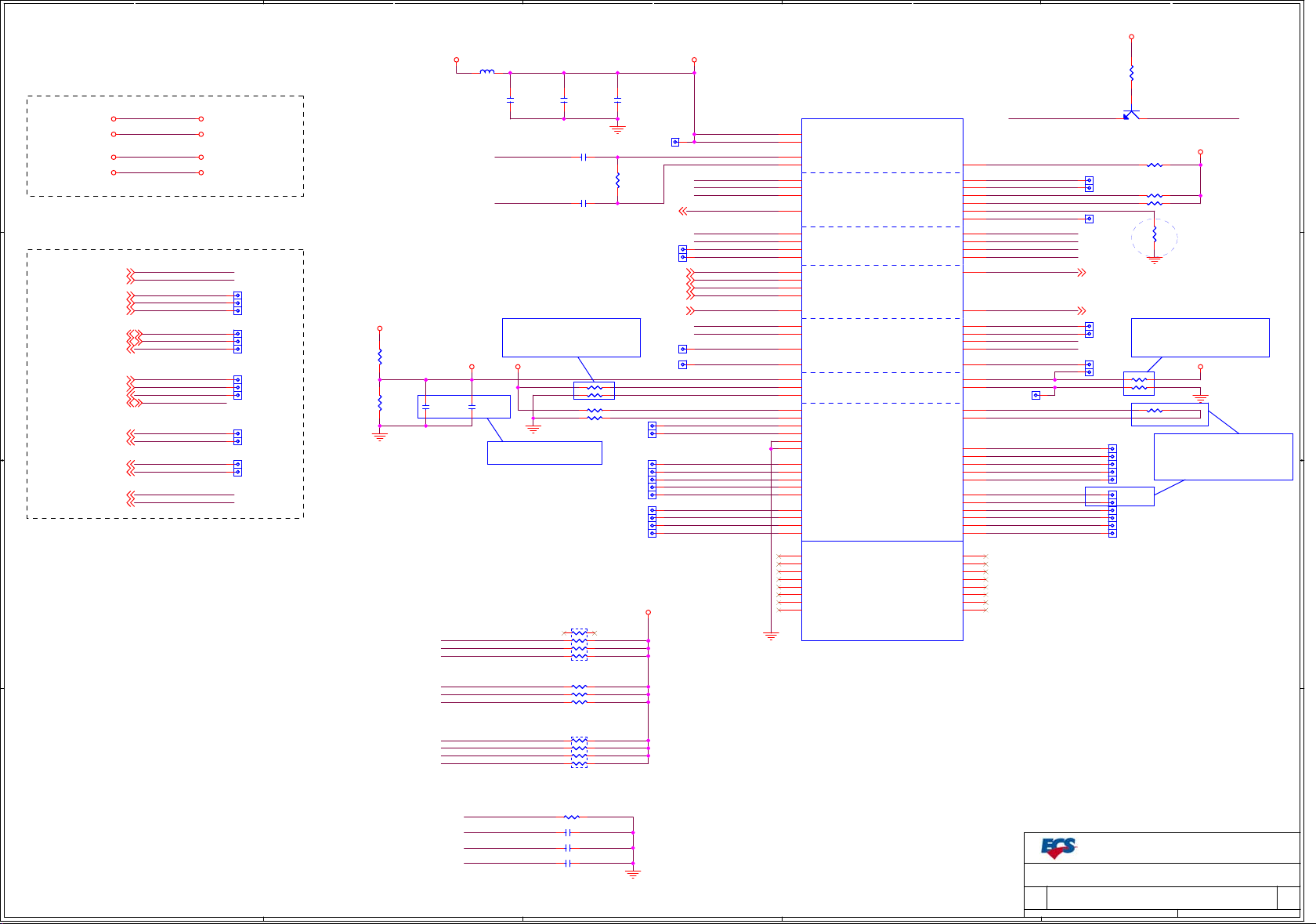

ECS A885GM-M2 Schematics REV 1.0

5

4

3

2

1

D D

A885GM-M2

Rev:1.0

SCHEMATICS TABLE:

Page Index

------- ------------------------

1

COVER PAGE

BLOCK DIADRAM2

CLK GEN

3

4

Power 1(CPU Vcore)

5

Power 2(DC-DC)

C C

B B

10

11

12

13

14

15

16

17

6

Power 3(DC-DC,Power Sequence)

7

AM3 CPU HT & OVERCLOCK

AM3 CPU MEMORY

8

AM3 CPU CONTROL & MISC

9

AM3 CPU PWR & GND

DDR3 DIMM CHANNEL

DDR3 DIMM POWER

NB1(HT Link)

NB3(System)

NB4(Power&GND)

PCI-E Slot(X16,X1)

Page Index

------- ------------------------

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

SB1(PCIE,PCI,CPU)

SB2(ACPI,USB,GPIO,Audio)

SB3(SATA,IDE,HWM,SPI)

SB4(Power,Decoupling)

SB5(Straps)

SIO(IT8721F-DX)

PCI SLOT

IDE, USB, PSKBM, COM

HDMI/DVI, VGA

Front Panel,Fan

LAN( RTL 8111E&8105E )

Audio1(Chip 1705&662)

Audio2(Panel)

Power Delivery Chart (consumption)NB2(PCI-E Link)

Clock Distribution

Power Sequence Distribution

REVISION HISTORY:

IMPORTANT NOTES ABOUT

THIS SCHEMATIC

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

DESIGN NOTE: Example

text for the design note to

A A

show the note inside the

colored box.

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

5

1) DESIGN NOTES in

grey are information

notes.

2) DESIGN NOTES in

yellow are notes of

caution.

3) DESIGN NOTES in

red are critical, and

must be understood and

followed.

Rev Date Notes

------ -------------- ---------------------------------------------------------------------------------

INITIAL RELEASEA

Change from A785GM-M7 V:A

Change to V1.01.0 2010-02-25

1. RN18 pull high to VCC_DUAL_F page 27

2. ER37 change to 11K-1-04 for USB EYE page 19

3. RTC issue fix. C164,C166 change to 27pF. page 20

4. ER41 change to 1.91K-1-04,ER40 change to 1.05K-1-04.R191 change to 19.1K-1-04 for OCP set . page 6

5. R134 change to30k for Vcore NB OCP by vendor. page 4

6. EC46 change to 270U-16D-OS. page 5

7. RGMII GBE LAN isn't used.direct short to GND. page 21

8. USBCLK not connectded by default,del R160,R91. page 19

9. Add D27, is used to prevent the battery runs out for EUP. P18

10. SB change to SB850. P18

3

PCB

PCB

15-R84-011001

15-R84-011001

2009-12-22

4

L1:TOPPCB STACK:

L2:PWR

L3:GND

L4:BOTTOM

2

Elitegroup Computer Systems

Elitegroup Computer Systems

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Cover Page

Cover Page

Cover Page

A885GM-M2

A885GM-M2

A885GM-M2

1

1

1

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

of

1

33Friday, February 26, 2010

1.0

1.0

1.0

5

4

3

2

1

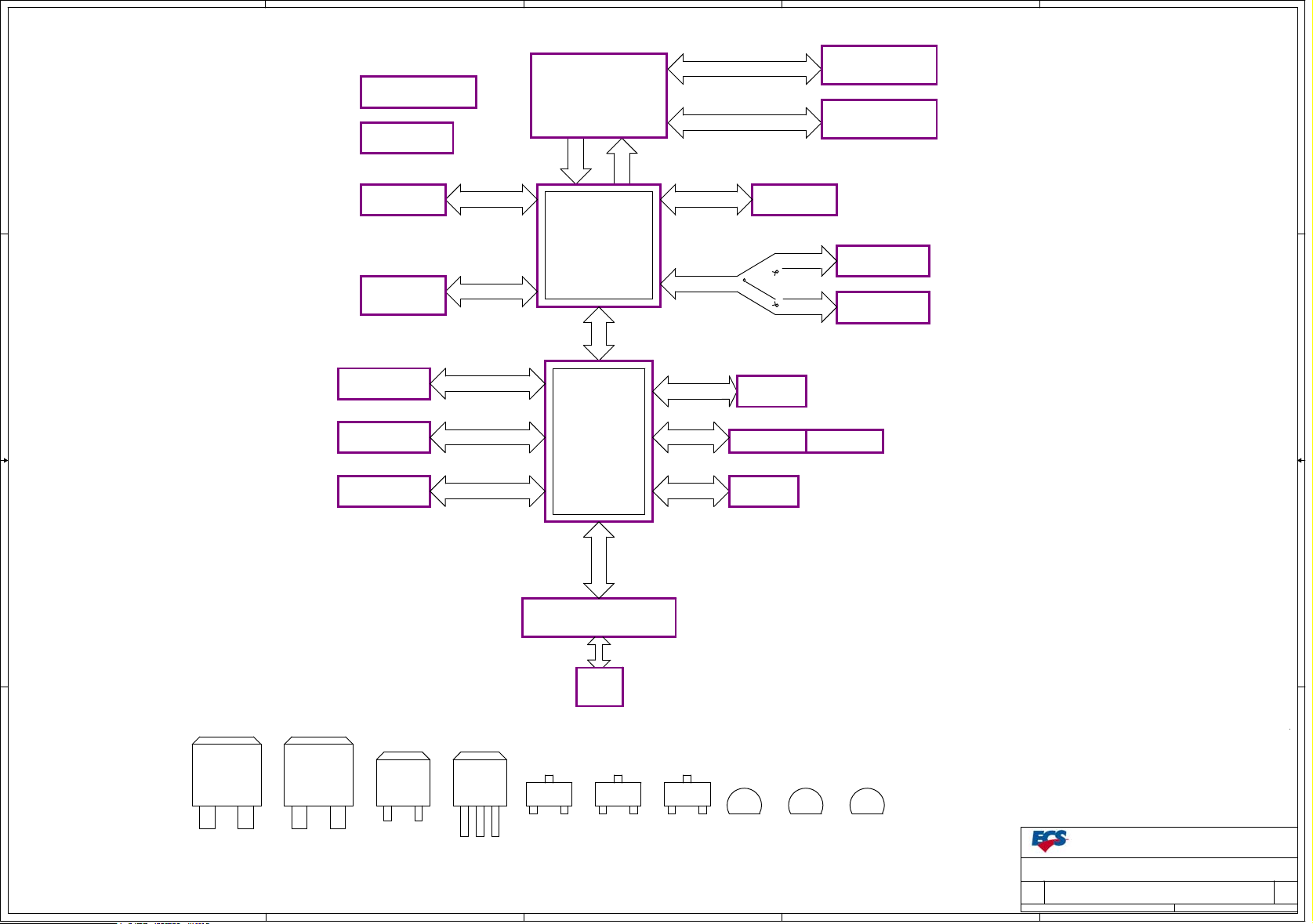

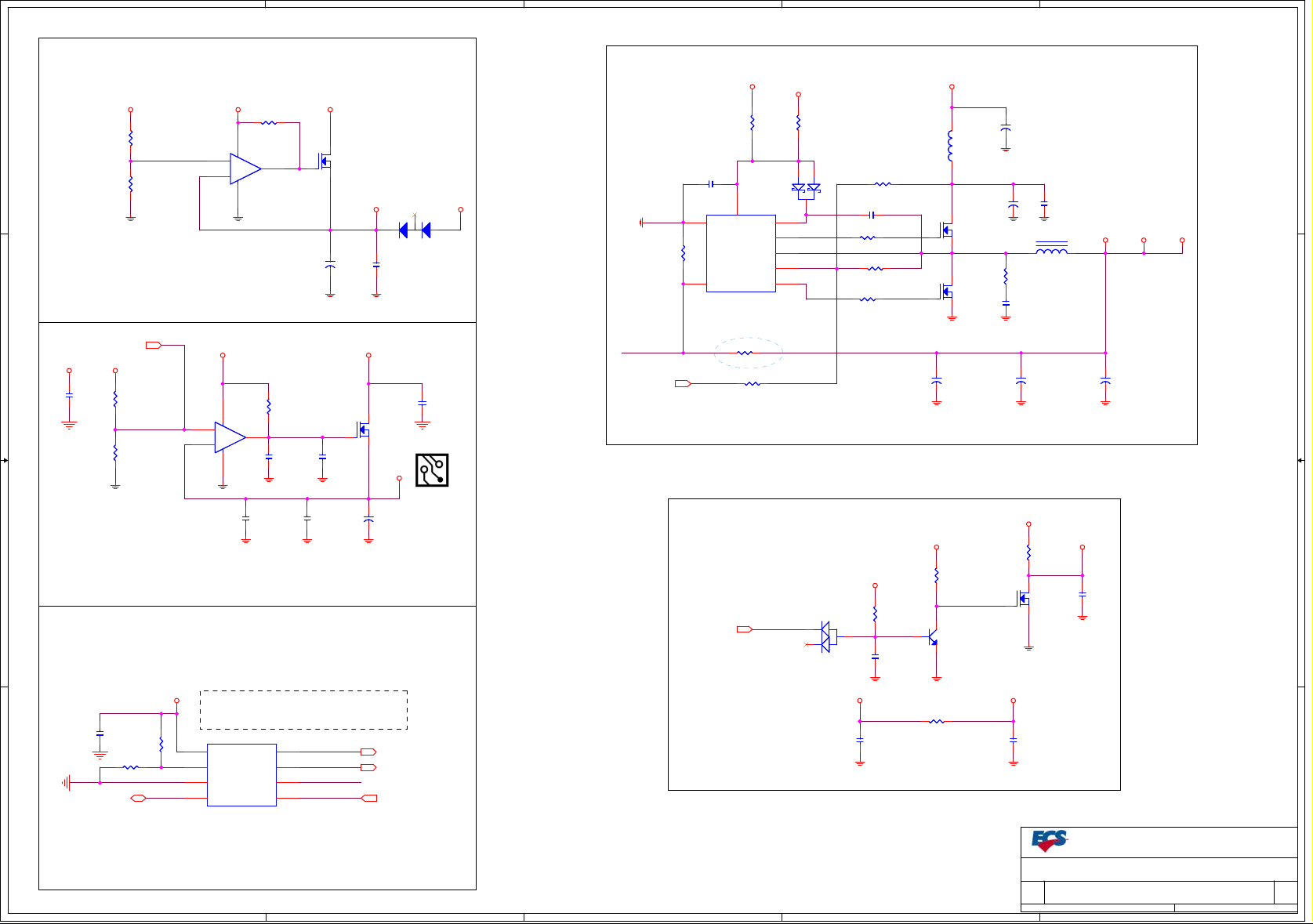

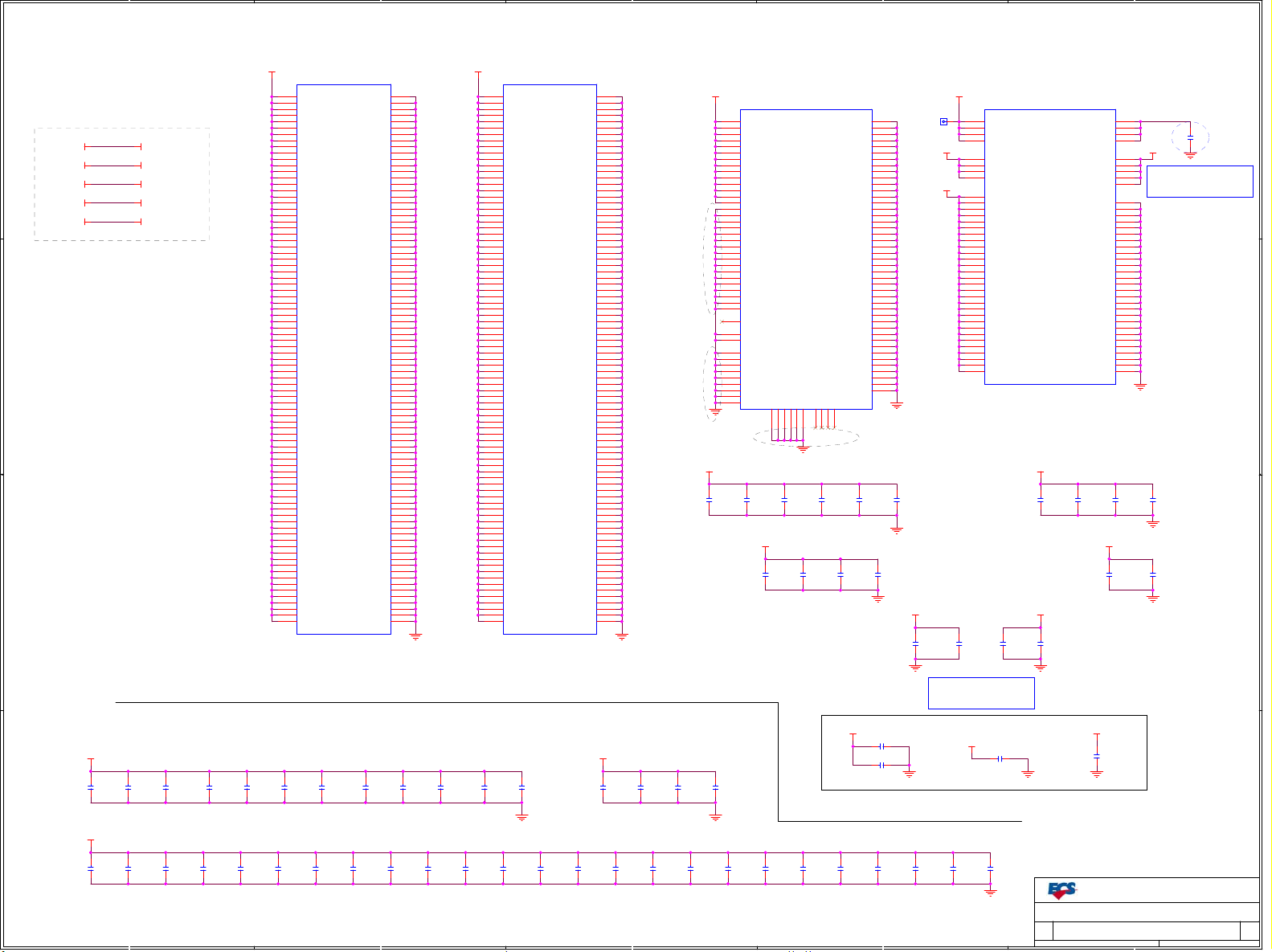

PWM Intersil

RT8861(DCR sense)

D D

Clock Generator

ICS 9LPRS471C

PCIE X 16

HyperTransport

PCIE 16X

LINK

AMD

AM3

AM3 SOCKET

OUT

NB:RS880P

IN

16x16

DDR3 A CHANNEL

Dual Channel

DDR3 B CHANNEL

Unbuffered DDR3

DIMM1

Unbuffered DDR3

DIMM2

VGA

HT LINK0 CPU I/F

Integrated Graphics

LAN

(Atheros 8131M

8132M)

PCIE 1X

1 16X PCIE VIDEO I/F

1 2X PCIE I/F with SB

4 1X PCIE I/F

2CH TMDS

OPTION

DVI CON

HDMI CON

4X ALINK PCIE3.0

C C

14 ports

USB 2.0

SB:ATI SB850

USB2.0*10

PCIE 1X

PCIE X 1*2

SATA*4

AUDIO CODEC

VIA1705

HD AUDIO I/F

AC97 2.3 & Azalia

ATA 66/100/133

Serial ATA

SATA*5

ESATA*1

ACPI 2.0

PCI*1

PCI BUS

LPC 1.1

MII

PCI/PCI Bridge

SPI

BIOS

8M

LPC I/F

B B

ITE SIO 8721F BX

COM

C

B C E

TO-251

HI772(1.4W)

(PNP)

D

G

SOT-23

2N7002

SI2303S

SI2301S

C

E

B

S

SOT-23

2N3904

2N3906

MMBT2907A

3

3

1

SOT-23

BAT54C

3

2

1

2

T0-92

LM431

78L05-DTM3055TL-S

LM432

B

E

C

T0-92

2N2222A

2N2097ABAT54S

B

EC

T0-92

HSD882-D

Elitegroup Computer Systems

Elitegroup Computer Systems

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Elitegroup Computer Systems

Block Diagram

Block Diagram

Block Diagram

A885GM-M2

A885GM-M2

A885GM-M2

2

2

2

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

of

1

33Friday, February 26, 2010

1.0

1.0

1.0

G

TO-263

2SK3296

D

D

G

TO-252

20N03

45N03

FDD6030L

4

S

2

A A

3S

1

TO-263

B55QS03

5

5

4

3

2

1

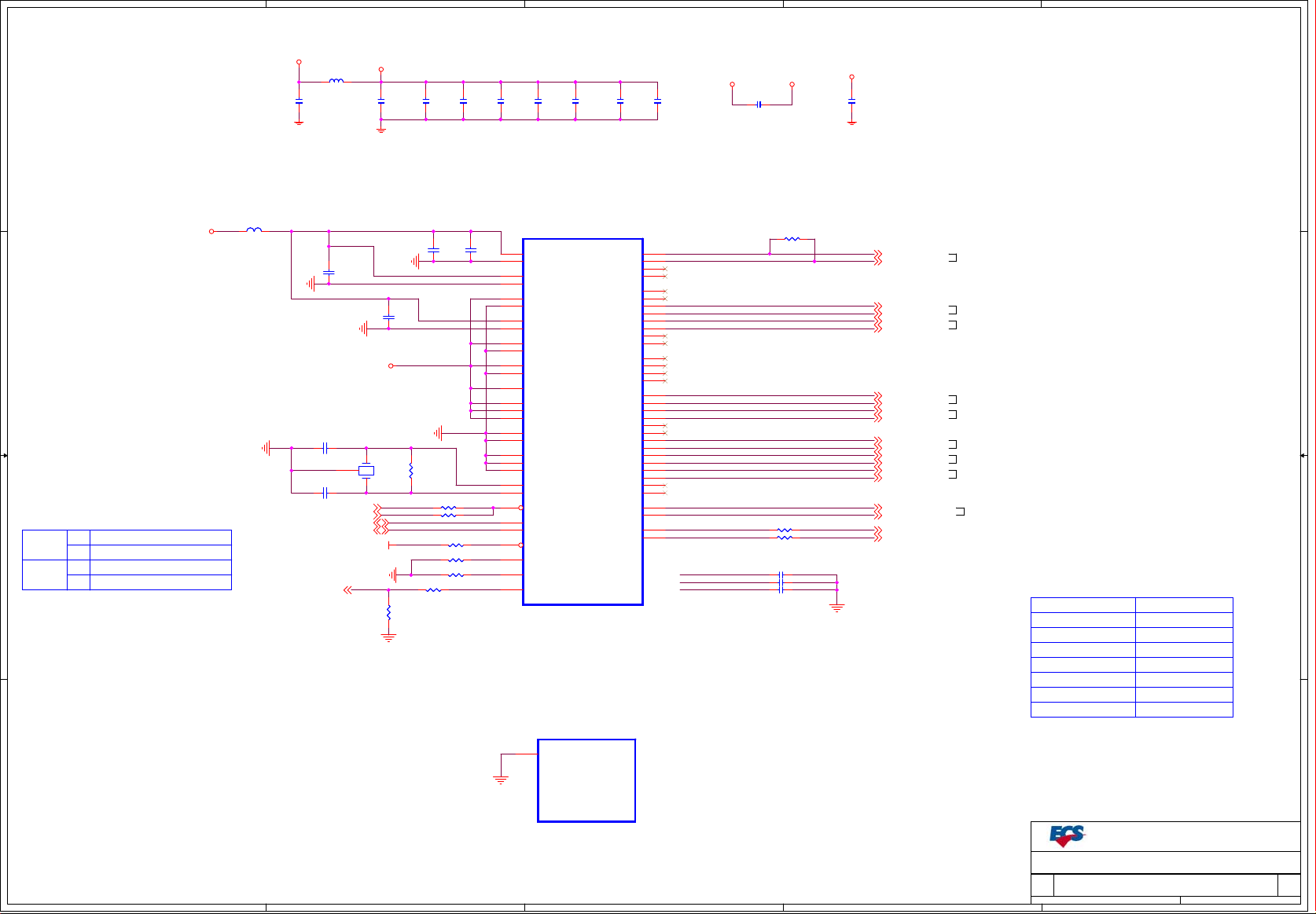

VCC3

C70

C70

10U-08-O

10U-08-O

D D

FB25

FB25

FB-600-08P

FB-600-08P

1 2

CLK_VDD

C76

C76

10U-X5-08

10U-X5-08

C107

C107

.1U-04

.1U-04

1- PLACE ALL SERIAL TERMINATION

RESISTORS CLOSE TO CLOCK GEN

C105

C105

.1U-04

.1U-04

C101

C101

.1U-04

.1U-04

C104

C104

.1U-04-O

.1U-04-O

C100

C100

.1U-04

.1U-04

C81

C81

.1U-04

.1U-04

C95

C95

.1U-04

.1U-04

VCC3 CLK_VDD

C75

C75

.1U-04-O

.1U-04-O

VCC3

C165

C165

.1U-04

.1U-04

For EMI

2- PUT DECOUPLING CAPS CLOSE TO CLOCK GEN POWER PIN

FB26 FB120-06FB26 FB120-06

VCC3

C C

C80 56P-04C80 56P-04

C79 56P-04C79 56P-04

66 MHz 3.3V single ended HTT clock

1

SEL_HTT66

0

100 MHz differential HTT clock

B B

SEL_SATA

* default

*

1

100 MHz non-spreading differential SRC clock

*

100 MHz spreading differential SRC clock

0

OSC_14M_NB15

CLK_VDDA

1U-06

1U-06

C99

C99

CLK_VDDREF

CLK_VDD48

-HW_RST19,27 NBHT_REFCLK_P 15

-PCI_RST18,23,24

SMBCK6,11,17,19,24

CLK_VDD

3

CLK_VDD

1 2

Rb

X2

X2

X-14.318M

X-14.318M

1U-06

1U-06

C90

C90

R81

R81

1M-04-O

1M-04-O

1 2

R87 0-04-SHR87 0-04-SH

R88 0-04-OR88 0-04-O

R86 1K-04R86 1K-04

R83 8.2K-04R83 8.2K-04

R84 8.2K-04R84 8.2K-04

R85 150-1-04R85 150-1-04

1 2

Ra

R82

R82

75-1-04

75-1-04

1 2

MC17

MC17

2.2U-06

2.2U-06

1 2

1 2

1 2

.1U-04

.1U-04

C97

C97

12

12

CLKA

CLKA

44

VDDA

43

GNDA

60

VDDREF

61

GNDREF

39

VDDSATA

42

GNDSATA

64

VDD48

3

GND48

48

VDDCPU

47

GNDCPU

56

VDDHTT

53

GNDHTT

34

VDDATIG

11

VDDSRC1

16

VDDSRC2

25

VDDSB_SRC

28

GNDATIG1

33

GNDATIG2

10

GNDSRC1

17

GNDSRC2

24

GNDSB_SRC

62

X1

63

X2

52

RESTORE#

4

SMBCLK

5

SMBDAT

51

PD#

59

REF0/SEL_HTT66

58

REF1/SEL_SATA

57

REF2

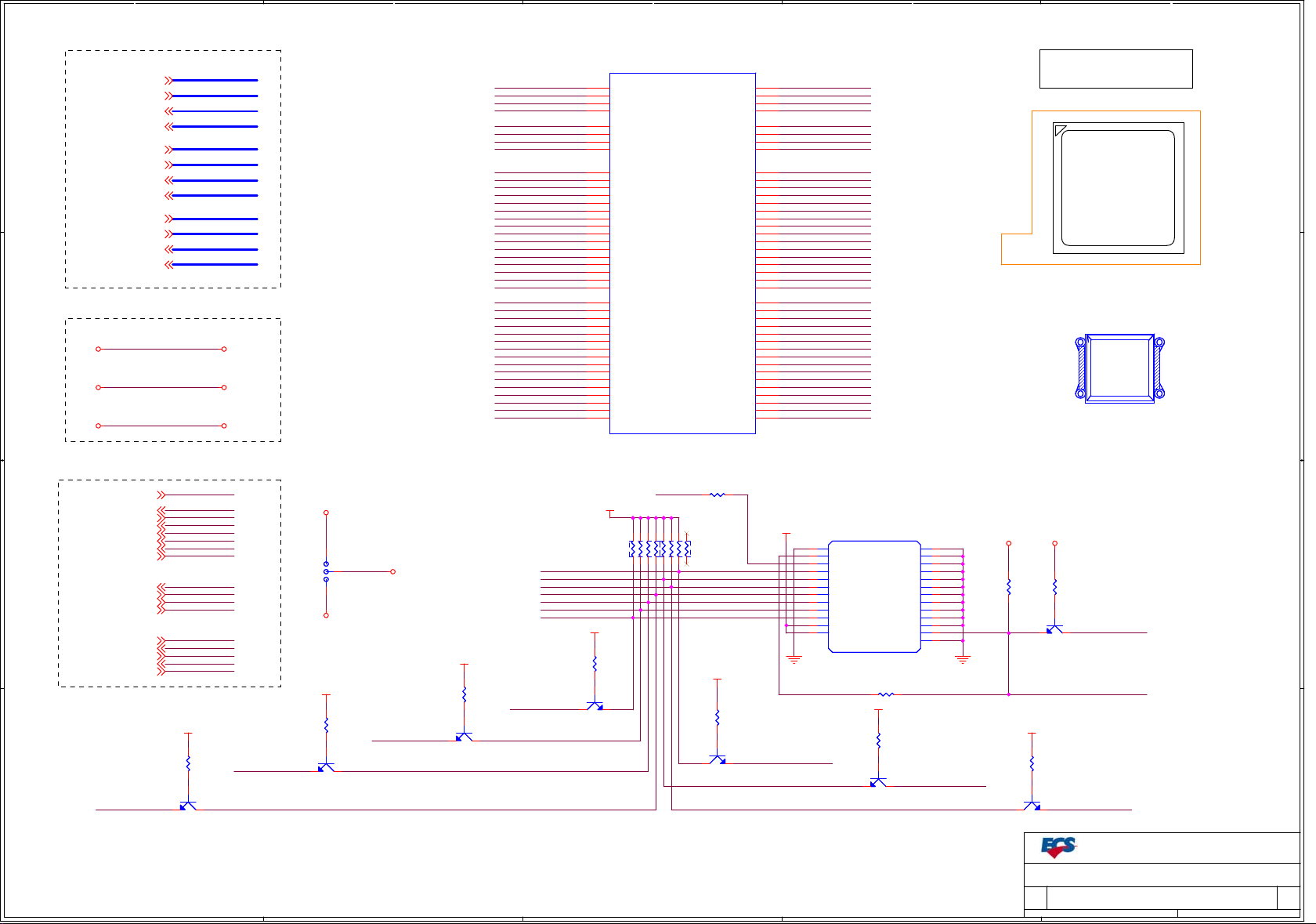

ICS9LPRS471CS

ICS9LPRS471CS

CPUKG0T_LPRS

CPUKG0C_LPRS

CPUKG1T_LPRS

CPUKG1C_LPRS

ATIG0T_LPRS

ATIG0C_LPRS

ATIG1T_LPRS

ATIG1C_LPRS

ATIG2T_LPRS

ATIG2C_LPRS

ATIG3T_LPRS

ATIG3C_LPRS

SB_SRC0T_LPRS

SB_SRC0C_LPRS

SB_SRC1T_LPRS

SB_SRC1C_LPRS

SRC0T_LPRS

SRC0C_LPRS

SRC1T_LPRS

SRC1C_LPRS

SRC2T_LPRS

SRC2C_LPRS

SRC3T_LPRS

SRC3C_LPRS

SRC4T_LPRS

SRC4C_LPRS

SRC5T_LPRS

SRC5C_LPRS

SRC6T/SATAT_LPRS

SRC6C/SATAC_LPRS

HTT0T/66M_LPRS

HTT0C/66M_LPRS

48MHz_0

48MHz_1

50

49

46

45

38

37

36

35

32

31

30

29

27

26

23

22

21

20

19

18

15

14

13

12

9

8

7

6

41

40

55

54

2

1

R_CPUCLK

R_CPUCLK-

R_NBSRC_CLKP

R_NBSRC_CLKN

R_GFX_CLKP

R_GFX_CLKN

R_SBLINK_CLKP

R_SBLINK_CLKN

R_SBSRC_CLKP

R_SBSRC_CLKN

R_GPP_CLK0P

R_GPP_CLK0N

R_GPP_CLK1P

R_GPP_CLK1N

R_LAN_CLKP

R_LAN_CLKN

R_NBHT_REFCLKP

R_NBHT_REFCLKN

SIO_CLOCK_R

48M_USB_R

OSC_14M_NB

CLK_48M_USB

CLK_48M_SIO

R90 261-1-04-OR90 261-1-04-O

1 2

R92 33-04R92 33-04

1 2

R91 33-04-OR91 33-04-O

1 2

CC3 22P-04-OCC3 22P-04-O

CC4 22P-04-OCC4 22P-04-O

CC5 22P-04-OCC5 22P-04-O

CPUCLK 9

CPUCLK- 9

NBSRC_CLKP 15

NBSRC_CLKN 15

GFX_CLKP 17

GFX_CLKN 17

SBLINK_CLKP 15

SBLINK_CLKN 15

SBSRC_CLKP 18

SBSRC_CLKN 18

GPP_CLK0P 17

GPP_CLK0N 17

GPP_CLK1P 17

GPP_CLK1N 17

LAN_CLKP 28

LAN_CLKN 28

NBHT_REFCLK_N 15

CLK_48M_SIO 23SMBDT6,11,17,19,24

CLK_48M_USB 19

RS880 OSC_14M_NB 1.1V Ra/Rb=150R/75R

CLKB

CLKB

THERMAL GND

eGND65

THERMAL GND

65

CPU CLK

NB PCI-E GFX CLK

GFX SLOT

A-Link (NB)

A-Link (SB)

PCI-E 1X SLOT

PCI-E 2X SLOT

LAN CHIP

HT REF CLK

NB CLOCK INPUT TABLE

* RS880 can be used as clock buffer to output two PCIE referecence clocks

By deault, chip will configured as input mode, BIOS can program it to output mode.

Clock chip has internal serial terminations for differencial pairs

NB CLOCKS RS880

HT_REFCLKP

HT_REFCLKN

REFCLK_P 14M SE (1.1V)

GFX_REFCLK 100M DIFF(IN/OUT)*

GPP_REFCLK

GPPSB_REFCLK 100M DIFF

100M DIFF

100M DIFF

VREFREFCLK_N

NC or 100M DIFF OUTPUT

A A

ICS9LPRS471CS

ICS9LPRS471CS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Clock Generator

Clock Generator

Clock Generator

A885GM-M2

A885GM-M2

A885GM-M2

333Friday, February 26, 2010

333Friday, February 26, 2010

333Friday, February 26, 2010

of

of

1

of

1.0

1.0

1.0

5

4

3

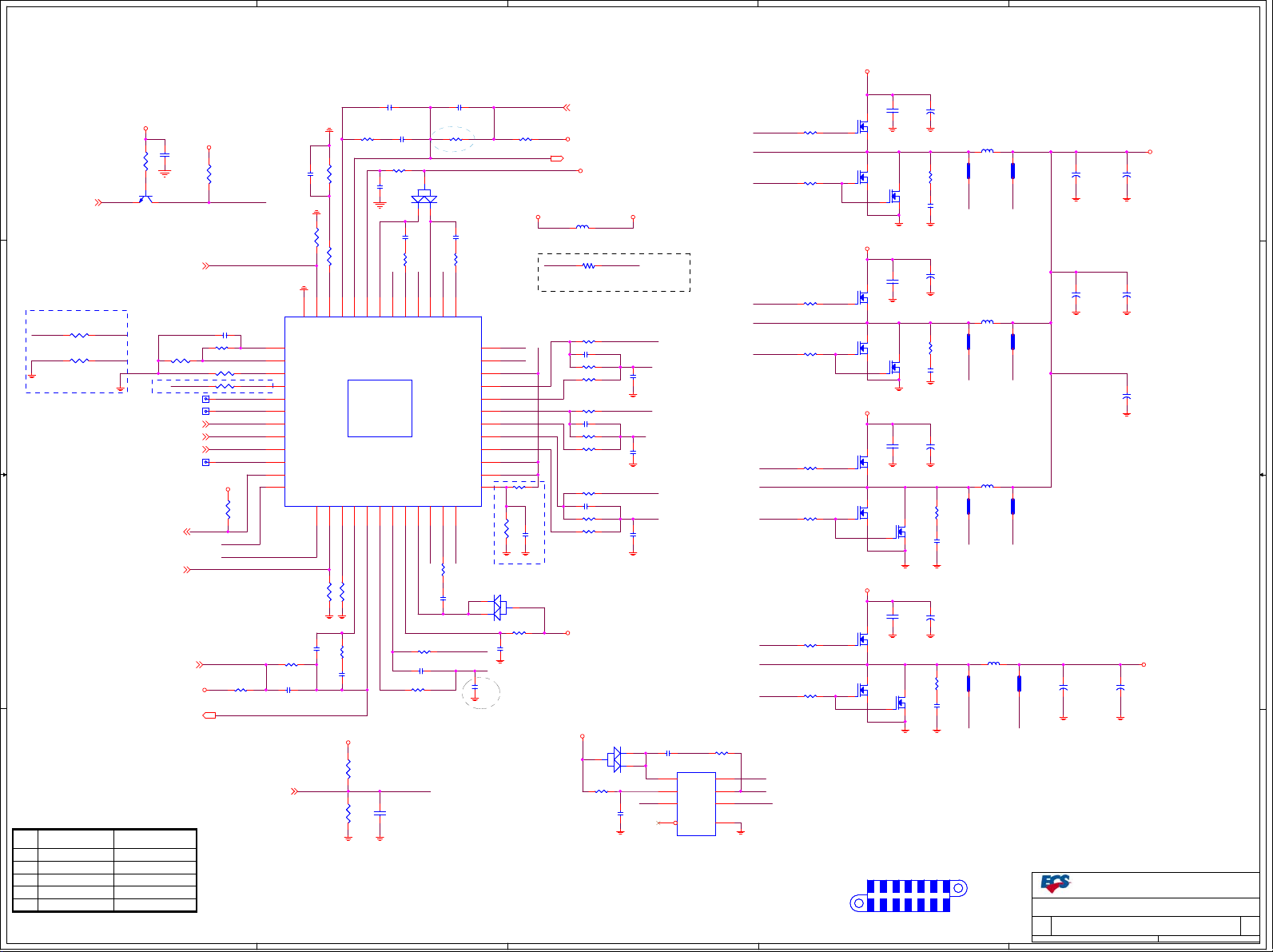

+12V_MOS

2

1

C147 100P-04C147 100P-04

D D

SB_CPUPWRGD9,18

Cc

C C

B B

A A

R137 0-04R137 0-04

R136 0-04-OR136 0-04-O

Co-lay RT8855

close to PWM

BOM Difference

RT8855

RT8855PQV

Ca

R341 1K;R366 NC R341 30K;R366 6.2K

Cb

R367 NC;R368 0ohm R367 0ohm;R368 NC

Cc

R337 33K R337 12K

Cd

1.1VSB

R159

R159

4.7K-04

4.7K-04

E C

Q3 2N3904-SQ3 2N3904-S

ADJ1ADJ2

ADJ1

Next Version RT8861 Value

CPU_VDDNB_FB-9

RT8861(new)

RT8861PQV

Default

5

12

B

CPU_COREFB-9

PG_VCORE23

CPU_VDDNB_FB9

MC32

MC32

1U-06

1U-06

R142 75K-1-04R142 75K-1-04

ADJ1

STP59STP59

STP60STP60

CPU_SVC9

CPU_SVD9

CPU_PVEN9

STP61STP61

CPU_VDDNB

I_VDDNB6

VCC3

12

R146

R146

10K-04

10K-04

VRM_PWROK

CPU_COREFB-

C130 1U-16V-08C130 1U-16V-08

R149 15K-1-04-OR149 15K-1-04-O

R138 51K-04R138 51K-04

R135 12K-1-04R135 12K-1-04

H_VID5

1

H_VID4

1

H_VID0

1

VCC3

R129

R129

4.7K-04

4.7K-04

EN_8855

VRM_PWROK

ΔV = - ΔI * R

R147 100-04R147 100-04

A5VCC

EN_VCORE23

PWM1

PWM1

RT8861GQW

RT8861GQW

24

10

2

Cd

14

46

45

44

43

42

41

47

48

R151 1K-04R151 1K-04

C150 .01U-04-OC150 .01U-04-O

C153 .1U-04C153 .1U-04

49

GND

5VCC

OFS

RT

IMAX

VID[5]

VID[4]

VID[3]/SVC

VID[2]/SVD

VID[1]/PVI

VID[0]/VFIXEN

VDDPWRGD

ENABLE

R139 100-04R139 100-04

3

FBRTN

PWROK

1

C154

C154

33P-04

33P-04

R154 220-1-04R154 220-1-04

T_ADJ ADJ2

R141 330-1-04R141 330-1-04

9

ADJ

FBRTN_NB

4

R140 100-04R140 100-04

R143

R143

C146

C146

6800P-04

6800P-04

15K-1-04

15K-1-04

R110 2.2-06R110 2.2-06

C129

C129

1U-16V-08

1U-16V-08

UG1

35

31

11

12

34

FB

COMP

UG[1]

12VCC

BOOT[1]

Ca

GND

GND

RT8861

RT8861

CSN_NB8CSP_NB

COMP_NB6FB_NB

IMAX_NB

7

5

13

R134 30K-1-04R134 30K-1-04

R152

R152

4.7K-04

4.7K-04

C151

C151

.01U-04

.01U-04

+12V_4P

12

R122

R122

10K-04

10K-04

EN_8855EN_VCORE PHASE3

12

12

R127

R127

MC30

MC30

2.7K-04

2.7K-04

1U-06-O

1U-06-O

4

3

1

2

C128

C128

.1U-16VX7-04

.1U-16VX7-04

R109

R109

0-06

0-06

PHASE1

LG1

27

33

32

LG[1]

BOOT[2]

PHASE[1]

12VCC_NB

UG_NB

BOOT_NB

40

37

36

NB_UG

R148 1K-1-04R148 1K-1-04

C152 1U-16VX-06C152 1U-16VX-06

R153 220-1-04R153 220-1-04

C148 1000P-04-OC148 1000P-04-O

R144 1.5K-04R144 1.5K-04

D16

D16

BAT54A-S

BAT54A-S

C126

C126

.1U-16VX7-04

.1U-16VX7-04

R108

R108

0-06

0-06

PHASE2

UG2

28

29

UG[2]

PHASE[2]

LG[2]

PWM3

PWM4

ISP[1]

ISN[1]

ISP[2]

ISN[2]

ISP[3]

ISN[3]

ISP[4]

ISN[4]

ENPS

PHASE_NB

LG_NB

38

39

NB_LG

NB_PHASE

R115

R115

0-06

0-06

C127

C127

.1U-16VX7-04

.1U-16VX7-04

NB_DPHASE

NB_ISN

CPU_COREFB+

R145 100-04R145 100-04

ΔV = - ΔI * R

T_ADJ

Location of Vcore

LG2

30

26

25

16

15

18

17

20

19

22

21

23

Next Version RT8861 Value

D15

D15

1

2

BAT54A-S

BAT54A-S

C155

C155

.1U-04

.1U-04

改善

偵測偏高問題

PWM3

R120

R120

Cb

R107 6.2K-04R107 6.2K-04

R114 2.2-06R114 2.2-06

C136

C136

1U-16V-08

1U-16V-08

OCP

3

30K-1-04

30K-1-04

C125

C125

100P-04-O

100P-04-O

A5VCC

CPU_COREFB+ 9

VCORE

I_VCORE 6

+12V_4P

08-413-604322

08-413-604097

2 1

L5 RCK-0.6UDL5 RCK-0.6UD

RT2

RT2

NTC-10K-1-06

NTC-10K-1-06

R131 1K-1-04R131 1K-1-04

C141 1U-16VX-06C141 1U-16VX-06

R132 3K-04-OR132 3K-04-O

R133 470-1-04R133 470-1-04

R125 1K-1-04R125 1K-1-04

C137 1U-16VX-06C137 1U-16VX-06

R123 3K-04-OR123 3K-04-O

R128 470-1-04R128 470-1-04

R113 1K-1-04R113 1K-1-04

C134 1U-16VX-06C134 1U-16VX-06

R118 3K-04-OR118 3K-04-O

R121 470-1-04R121 470-1-04

+12V_4P

+12V_4P

3

R99

R99

2.2-06

2.2-06

+12V_MOS+12V_4P

ADJ2

DPHASE1

ISN1

C143

C143

.1U-04

.1U-04

DPHASE2

ISN2

C140

C140

.1U-04

.1U-04

DPHASE3

ISN3

C132

C132

.1U-04

.1U-04

D13

D13

1

2

BAT54A-S

BAT54A-S

PWM3

C113 1U-16V-08C113 1U-16V-08

3

C109 .1U-16VX7-04C109 .1U-16VX7-04

PWM2

PWM2

1

BST

4

VCC

2

IN

3

NC

RT9619APSS

RT9619APSS

R97 0-06R97 0-06

DRVH

SW

DRVL

PGND

MN4

MN4

DS

MN252-9MS

R60 0-06R60 0-06

R70 0-06R70 0-06

R62 0-06R62 0-06

R71 0-06R71 0-06

R59 0-06R59 0-06

R69 0-06R69 0-06

R63 0-06R63 0-06

R73 0-06R73 0-06

MN252-9MS

G

G

MN5

MN5

MN252-9MS

MN252-9MS

G

G

MN3

MN3

MN252-9MS

MN252-9MS

G

G

MN6

MN6

MN252-9MS

MN252-9MS

G

G

DS

MN8

MN8

MN252-6MS

MN252-6MS

+12V_MOS

DS

DS

MN10

MN10

MN252-6MS

MN252-6MS

+12V_MOS

DS

DS

MN7

MN7

MN252-6MS

MN252-6MS

+12V_MOS

DS

DS

MN13

MN13

MN252-6MS

MN252-6MS

NB_MOS

NB_MOS

G

G

UG1

PHASE1

LG1

UG2

PHASE2

LG2

UG3

PHASE3

LG3

NB_UG

NB_PHASE

NB_LG

UG3

8

7

LG3

5

6

C56

C56

10U-16V-08

10U-16V-08

DS

MN9

MN9

MN252-6MS

MN252-6MS

C62

C62

10U-16V-08

10U-16V-08

DS

MN11

MN11

MN252-6MS

MN252-6MS

C55

C55

10U-16V-08

10U-16V-08

G

C57

C57

10U-16V-08

10U-16V-08

G

20-120-011930

20-120-011930

2

12

change to OS-CON.

R76

R76

1-08

1-08

C73

C73

.01U-04

.01U-04

12

R77

R77

1-08

1-08

C74

C74

.01U-04

.01U-04

12

DS

MN12

MN12

MN252-6MS

MN252-6MS

12

DS

MN14

MN14

MN252-6MS

MN252-6MS

EC14

EC14

270U-16D-OS

270U-16D-OS

L7 PIND-0.6UDL7 PIND-0.6UD

SU6

SU6

Short PAD

Short PAD

1 2

DPHASE1

EC15

EC15

270U-16D-OS

270U-16D-OS

L8 PIND-0.6UDL8 PIND-0.6UD

SU3

SU3

Short PAD

Short PAD

1 2

EC16

EC16

270U-16D-OS

270U-16D-OS

L6 PIND-0.6UDL6 PIND-0.6UD

R75

R75

SU5

SU5

Short PAD

Short PAD

1-08

1-08

1 2

C72

C72

.01U-04

.01U-04

DPHASE3 DPHASE2

EC24

EC24

270U-16D-OS-O

270U-16D-OS-O

L9 PIND-0.6UDL9 PIND-0.6UD

SU4

SU4

R74

R74

Short PAD

Short PAD

1-08

1-08

1 2

C71

C71

.01U-04

.01U-04

NB_DPHASE

21

SU10

SU10

Short PAD

Short PAD

1 2

ISN1

21

SU7

SU7

Short PAD

Short PAD

1 2

ISN2ISN3

21

SU9

SU9

Short PAD

Short PAD

1 2

12

EC30

EC30

820U-2.5D-OS-6.3

820U-2.5D-OS-6.3

12

EC28

EC28

820U-2.5D-OS-6.3

820U-2.5D-OS-6.3

VCORE

12

EC29

EC29

820U-2.5D-OS-6.3

820U-2.5D-OS-6.3

12

EC27

EC27

820U-2.5D-OS-6.3

820U-2.5D-OS-6.3

12

EC26

EC26

820U-2.5D-OS-6.3

820U-2.5D-OS-6.3

04-737-827691

Vcore MOS change to H1L2

820uF footprint change to 6.3mm

21

12

SU8

SU8

Short PAD

Short PAD

EC32

EC32

820U-2.5D-OS-6.3-O

1 2

NB_ISN

820U-2.5D-OS-6.3-O

Elitegroup Computer Systems

Elitegroup Computer Systems

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Power (CPU Vcore RT8861)

Power (CPU Vcore RT8861)

Power (CPU Vcore RT8861)

CPU_VDDNB

12

EC31

EC31

820U-2.5D-OS-6.3

820U-2.5D-OS-6.3

A885GM-M2

A885GM-M2

A885GM-M2

1

1.0

1.0

4

4

4

1.0

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

5

3VSB_IO

5VSB_ATX

3VSB IO Max=25mA

Vo=Vin*Rb/(Rt+Rb)-0.7

B

Default = 3.161V

QN7

QN7

2N3904-S

2N3904-S

E C

3VSB_IO

2 1

MC48

MC48

1U-06-O

1U-06-O

12

ER45

ER45

63.4-1-04

63.4-1-04

Rt

D D

Rb

12

ER44

ER44

215-1-04

215-1-04

3VSB

5VSB

MC16

MC16

1U-06-O

1U-06-O

C C

12

EC21

EC21

100U-16DE

100U-16DE

U10 ADJ1086-SU10 ADJ1086-S

INIOUT

ADJ

O

A

Vo=1.25(1+Rb/Rt)

AMS1086(SOT223)=1.5A

12

12

ER14

ER14

180-1-04

180-1-04

ER13

ER13

300-1-04

300-1-04

3VSB

12

EC23

EC23

100U-16DE

100U-16DE

1.1VSB

BC70

BC70

.1U-04-O

.1U-04-O

2 1

3VSB

12

ER35

ER35

7.5K-1-04

7.5K-1-04

12

ER36

ER36

4.02K-1-04

4.02K-1-04

1.1VSB

+

+

EC37

EC37

100U-16DE

100U-16DE

GND

VOUT

3VSB

1

VIN

2

3

4

3VSB

U14 9173P-SU14 9173P-S

8

Vcntl

7

Vcntl

6

REFEN

Vcntl

5

Vcntl

12

MC31

MC31

1U-06

1U-06

B B

DDRVTT

DDRREF

BC88

BC88

12

.1U-04-O

.1U-04-O

12

V_DIMM

MC47

MC47

10U-08

10U-08

ER43

ER43

10K-1-04

10K-1-04

1 2

ER42

ER42

10K-1-04

10K-1-04

1 2

DDR_VTT

12

EC44

EC44

1000U-6V3LD8H11E

1000U-6V3LD8H11E

V_DIMM

3VSB

U18 9173DPSP-SU18 9173DPSP-S

8

Vcntl

7

Vcntl

6

Vcntl

5

Vcntl

12

MC50

MC50

1U-06

1U-06

A A

9

G

GND

REFEN

VOUT

1

VIN

2

3

4

5

4

SIO_GP25 V_DIMM

V_DIMM voltage :1.6V----2.1V

4

SIO_GP24

1

0

1

0

1

1

0

0

GP2523

GP2423

VDIMM_EN23

ATX_PWRGD23,27

3

1.6V

1.8V

1.9V

2.1V

1 2

ER48 4.02K-1-04ER48 4.02K-1-04

1 2

ER49 2.67K-1-04ER49 2.67K-1-04

VDIMM_EN

ATX_PWRGD

DUALSW_P

DUALSW_N

5V_DUAL

VDIMM

3

ER46

ER46

976-1-04

976-1-04

5VSB

12

R220

R220

4.7K-04

4.7K-04

R221 10K-04R221 10K-04

3VSB +12V

R215

R215

10K-04

10K-04

1 2

B

E C

Q5 2N3904-SQ5 2N3904-S

S5

0

0

5VSB

0

X

X

5VSB

R246

R246

1-06-O

1-06-O

1 2

BC92

BC92

.1U-16VX7-04

.1U-16VX7-04

3

GND

12

6

FB

RT8105GS

RT8105GS

R241

R241

1 2

1K-04-O

1K-04-O

12

R227

R227

4.7K-04

4.7K-04

1 2

DUALSW_N

enter S0

0

1

5VSB

12V

VCC5

V

+12V

1

2

D26

D26

BAT54C-S

BAT54C-S

3

BAT54C-S

BAT54C-S

5

U19

U19

BOOT

VCC

UGATE

PHASE

COMP/OCSET

LGATE

4700P-04-O

4700P-04-O

1 2

ER47 1K-1-04ER47 1K-1-04

5VSB

EC

Q6

B

2N3906-SQ62N3906-S

DUALSW_P

12

S0

1

1

12V

12V

VCC5

V

D25

D25

1

2

8

7

4

C228

C228

R222

R222

10K-04

10K-04

enter S3

1

0

0

0

5VSB

V

5VSB

1

2

3

.1U-16VX7-04

.1U-16VX7-04

R238

R238

1 2

0-06

0-06

DIMM_PHASE

R237 22K-1-04R237 22K-1-04

R242

R242

1 2

0-06

0-06

When Vgs=12V,Tj=100C;Rdson =16mΩ , ocp=30A

Iocp=(40uA*Rocset-0.4) / Rdson of Lowside mos

For DIMM PWM

G2

G2

G2

4

5VSB

VCC

S2

S2

S2

3

G1

G1

G1

2

S1

S1

S1

1

AO4609-S

AO4609-S

For USB connector

G2

G2

G2

4

5VSB

VCC

S2

S2

S2

3

G1

G1

G1

2

S1

S1

S1

1

AO4609-S

AO4609-S

For USB Header

G2

G2

G2

4

5VSB

VCC

S2

S2

S2

3

G1

G1

G1

2

S1

S1

S1

1

AO4609-S

AO4609-S

exit S3

1

1

12V

12V

VCC5

V

C221

C221

U17

U17

U7

U7

U16

U16

R236

R236

24K-06-O

24K-06-O

D_HG

12

D_LG

D2

D2

P

P

D2

D2

D1

D1

N

N

D1

D1

D2

D2

P

P

D2

D2

D1

D1

N

N

D1

D1

D2

D2

P

P

D2

D2

D1

D1

N

N

D1

D1

enter S5

2

5V_DUAL

12

G

G

5V_DUAL

D2

5

D2

6

D1

7

D1

8

VCC_DUAL_R

D2

5

D2

6

D1

7

D1

8

VCC_DUAL_F

D2

5

D2

6

D1

7

D1

8

0

1

5VSB

12V

VCC5

V

2

L11

L11

FB-160-D

FB-160-D

1 2

5VIN_DIMM

270U-16D-OS

270U-16D-OS

DS

MN21

MN21

MN252-20MS

MN252-20MS

DS

MN20

MN20

MN252-20MS

MN252-20MS

2 1

1 2

1 2

EC46

EC46

BC90

BC90

.1U-04-O

.1U-04-O

R50

R50

1K-04-O

1K-04-O

R155

R155

1K-04-O

1K-04-O

S5

0

0

5VSB

0

0

X

1

V_DIMM

12

MC49

MC49

10U-08

10U-08

V_DIMM

1pcs DDR3@3A

@MAX=9A , Pulse=16A

12

EC43

EC43

1000U-6V3LD8H11E

1000U-6V3LD8H11E

PIND1.5UD-20A

PIND1.5UD-20A

1 2

R239

R239

2.2-06

2.2-06

1 2

C229

C229

4700P-04

4700P-04

12

EC45

EC45

1000U-6V3LD8H11E

1000U-6V3LD8H11E

L12

L12

5V_DUAL

5VSB

5VSB

5VSB

VCC

BC89

BC89

.1U-04-O

.1U-04-O

2 1

BC32

BC32

.1U-04-O

.1U-04-O

2 1

BC71

BC71

.1U-04-O

.1U-04-O

2 1

C219

C219

.1U-04

.1U-04

2 1

VCC

BC31

BC31

.1U-04

.1U-04

2 1

VCC

BC72

BC72

.1U-04-O

.1U-04-O

2 1

Elitegroup Computer Systems

Elitegroup Computer Systems

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Power A(DC to DC)

Power A(DC to DC)

Power A(DC to DC)

A885GM-M2

A885GM-M2

A885GM-M2

5

5

5

1

1.0

1.0

1.0

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

5

4

3

2

1

VCC1.8

VCC_NB

+12V

1 2

PWM3

PWM3

BOOT

UGATE

PHASE

LGATE

R192

R192

1-06-O

1-06-O

D21

D21

BAT54C-S

BAT54C-S

1

2

8

7

4

VCC

1 2

2

VCC12_EN

1

3

1 2

R193 24K-06-OR193 24K-06-O

.1U-16VX7-04BC84 .1U-16VX7-04BC84

HG_NB

1 2

R188 1-06R188 1-06

PHASE_NB

12

R191 19.1K-1-04R191 19.1K-1-04

LG_NB

12

R187 1-06R187 1-06

When Vgs=12V ,Id=20A, Tj=100C; Rdsmax=1.4Rds(on),

Rdson =9mΩ , ocp=40A

Iocp=(40uA*Rocset-0.4) / Rdson of Lowside mos

12

EC19

EC19

R47

R47

4.7K-04-O

4.7K-04-O

C156

C156

1000P-04-O

1000P-04-O

VCC3

MN2

MN2

DS

P3055LDG-S

P3055LDG-S

G

VCC1.8

12

C60

C60

.1U-04-O

.1U-04-O

D8

BAV99-SD8BAV99-S

VCC3

ER41

ER41

1.91K-1-04

1.91K-1-04

For EMI

BC83

BC83

.1U-16VX7-04

.1U-16VX7-04

3

12

6

R195

R195

10-06

10-06

GND

COMP/OCSET

FB

RT8105GS

RT8105GS

5

VCC

VCC25A

I_NBVCORE

ΔV = - ΔI * R

EN_VCC1223

HW default :VCC_NB = 1.2V

1 2

ER40 1.05K-1-04ER40 1.05K-1-04

1 2

R196 0-04-SHR196 0-04-SH

C50

C50

1000P-04-O

1000P-04-O

2 1

VCC3+12V

12

MC5

MC5

10U-08-O

DS

MN16

MN16

2N7002-S

2N7002-S

G

10U-08-O

Near CPU.

VCC25A

3VSB

D D

C C

21

C43

C43

1U-06-O

1U-06-O

12

ER12

ER12

1.5K-1-04

1.5K-1-04

VREF18

12

ER11

ER11

1.8K-1-04

1.8K-1-04

EN_VCC25A23

3VSB3VSB

ER6

ER6

3.24K-1-04

3.24K-1-04

1 2

ER7

ER7

10K-1-04

10K-1-04

1 2

5

6

+

+

-

-

3

2

84

+12V

84

+

+

-

-

U8B

U8B

OP358-S

OP358-S

R48 4.7K-04-OR48 4.7K-04-O

U8A

U8A

OP358-S

OP358-S

1

1000U-6V3LD8H11E

1000U-6V3LD8H11E

1 2

7

2 1

VCC3

1 2

DS

G

DS

G

12

EC34

EC34

1000U-6V3LD8H11E

1000U-6V3LD8H11E

LL1

LL1

FB-160-D

FB-160-D

3VIN_VCCNB

EC41

EC41

560U-6.3D-OS

560U-6.3D-OS

MN18

MN18

MN252-9MS

MN252-9MS

MN17

MN17

MN252-6MS

MN252-6MS

12

EC36

EC36

470U-6V3D6.3H11E

470U-6V3D6.3H11E

12

1 2

PIND1.5UD-20A

PIND1.5UD-20A

R166

R166

2.2-06

2.2-06

1 2

BC81

BC81

4700P-04

4700P-04

12

EC42

EC42

1000U-6V3LD8H11E

1000U-6V3LD8H11E

MC41

MC41

10U-08

10U-08

L10

L10

VCC_NB

@MAX=13A

12

EC33

EC33

1000U-6V3LD8H11E

1000U-6V3LD8H11E

VDDHT

VCC_SB

12

EC39

C51

C138

C138

1000P-04-O

1000P-04-O

2 1

B B

uP6262的電流輸出與ΔVout的關系如下:

選取從uP6262輸出的方向為正,

則VCORE,VCC_NB及VDIMM的ΔVout為:

ΔVout = -Ic * RFB;

5VSB

Chip Address: 0x60

C157

C157

R161

R161

.1U-04

.1U-04

2 1

10K-04

10K-04

1 2

R164 16.9K-04-OR164 16.9K-04-O

A A

SMBDT3,11,17,19,24

5

Address 4 Voltage Range = 77~100%VCC

U15

U15

1

VCC

1 2

2

3

4

BUS_SEL

GND

SDA

UP6262

UP6262

OUT1

OUT2

OUT3

SCL

C51

1000P-04-O

1000P-04-O

2 1

8

7

I_NBVCORE

6

5

OUT1..3,W/S=10/15

EC39

100U-16DE

100U-16DE

UP6262

I_VCORE 4

I_VDDNB 4

SMBCK 3,11,17,19,24

4

3VSB

R225

1 2

C212

C212

1U-06

1U-06

C224

C224

.1U-04-O

.1U-04-O

R225

10K-04

10K-04

1 2

Q18

Q18

B

2N3904-S

2N3904-S

E C

1 2

R226 0-08-OR226 0-08-O

Co-lay for +1.5V

V_DIMM

R235

R235

D24

D24

10K-04

1

2

BAT54A-S

BAT54A-S

10K-04

3

+1.5V V_DIMM

21

-SLP3

-SLP319,23

Sideport memory power Sequence

3

2

+12V

R231

R231

47K-04

47K-04

G

21

12V_Gate

1 2

MN19

MN19

2N7002-S

2N7002-S

21

C220

C220

1U-06-O

1U-06-O

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

A885GM-M2

A885GM-M2

A885GM-M2

633Friday, February 26, 2010

633Friday, February 26, 2010

633Friday, February 26, 2010

1

DS

C211

C211

1U-06

1U-06

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Power B(DC to DC),PWR Sequence&good

Power B(DC to DC),PWR Sequence&good

Power B(DC to DC),PWR Sequence&good

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

1.0

1.0

1.0

of

of

of

A

B

C

D

E

HyperTransport

CPUA

HT_CLKIN_H[0..1]13

HT_CLKIN_L[0..1]13

V_DIMM

VCC1.8

HT_CLKOUT_H[0..1]13

HT_CLKOUT_L[0..1]13

HT_CTLOUT_H[0..1]13

HT_CTLOUT_L[0..1]13

HT_CADIN_H[0..15]13

HT_CADIN_L[0..15]13

HT_CADOUT_H[0..15]13

HT_CADOUT_L[0..15]13

HT_CTLIN_H[0..1]13

HT_CTLIN_L[0..1]13

SB_PWRGD19

CPU_DBREQ_9

CPU_DBRDY9

CPU_TRST-9

CPU_TDO9

LDT_RST-9,15,18

IMC_CRST_19

IMC_DBREQ_19

IMC_DBRDY19

IMC_TCK19

IMC_TMS

CPU_TCK9

CPU_TMS9

CPU_TDI9

IMC_TDI19

IMC_TRST_19

IMC_TDO19

IMC_TMS19

4 4

3 3

2 2

1 1

HT_CLKIN_H[0..1]

HT_CLKIN_L[0..1]

HT_CLKOUT_H[0..1]

HT_CLKOUT_L[0..1]

HT_CTLIN_H[0..1]

HT_CTLIN_L[0..1]

HT_CTLOUT_H[0..1]

HT_CTLOUT_L[0..1]

HT_CADIN_H[0..15]

HT_CADIN_L[0..15]

HT_CADOUT_H[0..15]

HT_CADOUT_L[0..15]

1.5V

1.8V

3.3V

SB_PWRGD

CPU_DBREQ_

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRSTCPU_TDO

IMC_TDI

IMC_TRST_

IMC_TDO

IMC_TMS

LDT_RSTIMC_CRST_

IMC_DBREQ_

IMC_DBRDY

IMC_TCK

JT_GATE

12

R275

R275

10K-04

10K-04

B

E C

Q15 2N3904-SQ15 2N3904-S

V_DIMM

VCC1.8

VCC3VCC3

IMC_TDO

V_DIMM

13

RJ6

RJ6

2

0-04(1-2)

0-04(1-2)

VCC1.8

JT_GATE

12

R276

R276

10K-04

10K-04

B

E C

Q16 2N3904-SQ16 2N3904-S

JT_GATE

IMC_TRST_

JT_GATE

12

R274

R274

10K-04

10K-04

B

E C

Q14 2N3904-SQ14 2N3904-S

HT_CLKIN_H1

HT_CLKIN_L1

HT_CLKIN_H0

HT_CLKIN_L0

HT_CTLIN_H1

HT_CTLIN_L1

HT_CTLIN_H0

HT_CTLIN_L0

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

IMC_TDI

CPU_DBREQ_

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRSTCPU_TDO

Q17 2N3904-SQ17 2N3904-S

CPUA

N6

L0_CLKIN_H1

P6

L0_CLKIN_L1

N3

L0_CLKIN_H0

N2

L0_CLKIN_L0

V4

L0_CTLIN_H1

V5

L0_CTLIN_L1

U1

L0_CTLIN_H0

V1

L0_CTLIN_L0

U6

L0_CADIN_H15

V6

L0_CADIN_L15

T4

L0_CADIN_H14

T5

L0_CADIN_L14

R6

L0_CADIN_H13

T6

L0_CADIN_L13

P4

L0_CADIN_H12

P5

L0_CADIN_L12

M4

L0_CADIN_H11

M5

L0_CADIN_L11

L6

L0_CADIN_H10

M6

L0_CADIN_L10

K4

L0_CADIN_H9

K5

L0_CADIN_L9

J6

L0_CADIN_H8

K6

L0_CADIN_L8

U3

L0_CADIN_H7

U2

L0_CADIN_L7

R1

L0_CADIN_H6

T1

L0_CADIN_L6

R3

L0_CADIN_H5

R2

L0_CADIN_L5

N1

L0_CADIN_H4

P1

L0_CADIN_L4

L1

L0_CADIN_H3

M1

L0_CADIN_L3

L3

L0_CADIN_H2

L2

L0_CADIN_L2

J1

L0_CADIN_H1

K1

L0_CADIN_L1

J3

L0_CADIN_H0

J2

L0_CADIN_L0

V_DIMM

RN22

RN22

4.7K-8P4R-06-O

4.7K-8P4R-06-O

JT_GATE

12

R277

R277

10K-04

10K-04

B

EC

1 2

3 4

5 6

SB_PWRGD

1 2

3 4

5 6

7 8

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

HT LINK

HT LINK

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

ZIF-941P-S

ZIF-941P-S

R273

R273

0-04-O

0-04-O

1 2

RN21

RN21

4.7K-8P4R-06

4.7K-8P4R-06

7 8

JT_GATE

12

R262

R262

10K-04

10K-04

B

EC

Q12 2N3904-SQ12 2N3904-S

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_CLKOUT_H1

HT_CLKOUT_L1

HT_CLKOUT_H0

HT_CLKOUT_L0

HT_CTLOUT_H1

HT_CTLOUT_L1

HT_CTLOUT_H0

HT_CTLOUT_L0

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

Over Clocking

V_DIMM

HDT Connector

1

3

5

7

9

11

13

15

17

19

21

23

Use buffered reset

IMC_DBREQ_

SJ1

SJ1

KEY

KEY

ASP-68200-07-O

ASP-68200-07-O

R270 0-04-OR270 0-04-O

1 2

JT_GATE

12

R260

R260

10K-04

10K-04

B

E C

Q10 2N3904-SQ10 2N3904-S

2

4

6

8

10

12

14

16

18

20

22

24

26

IMC_DBRDY

Q11 2N3904-SQ11 2N3904-S

Please use 1mm pad size,

place all ELT test pads

on bottom side only.

A1

AL1

CPU(104) 30-430-020513

CPU(104) 30-430-020513

VCC1.8

VCC3

12

12

R263

R263

R271

R271

10K-04

10K-04

4.7K-04

4.7K-04

B

E C

Q13 2N3904-SQ13 2N3904-S

JT_GATE

12

R261

R261

10K-04

10K-04

B

EC

AM3

Top View

CPU-R1

CPU-R1

LDT_RST-

IMC_CRST_

IMC_TCK

A31

AL31

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

CPU HT & DEBUG

CPU HT & DEBUG

CPU HT & DEBUG

A885GM-M2

A885GM-M2

A885GM-M2

E

1.0

1.0

7

7

7

1.0

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

of

33Friday, February 26, 2010

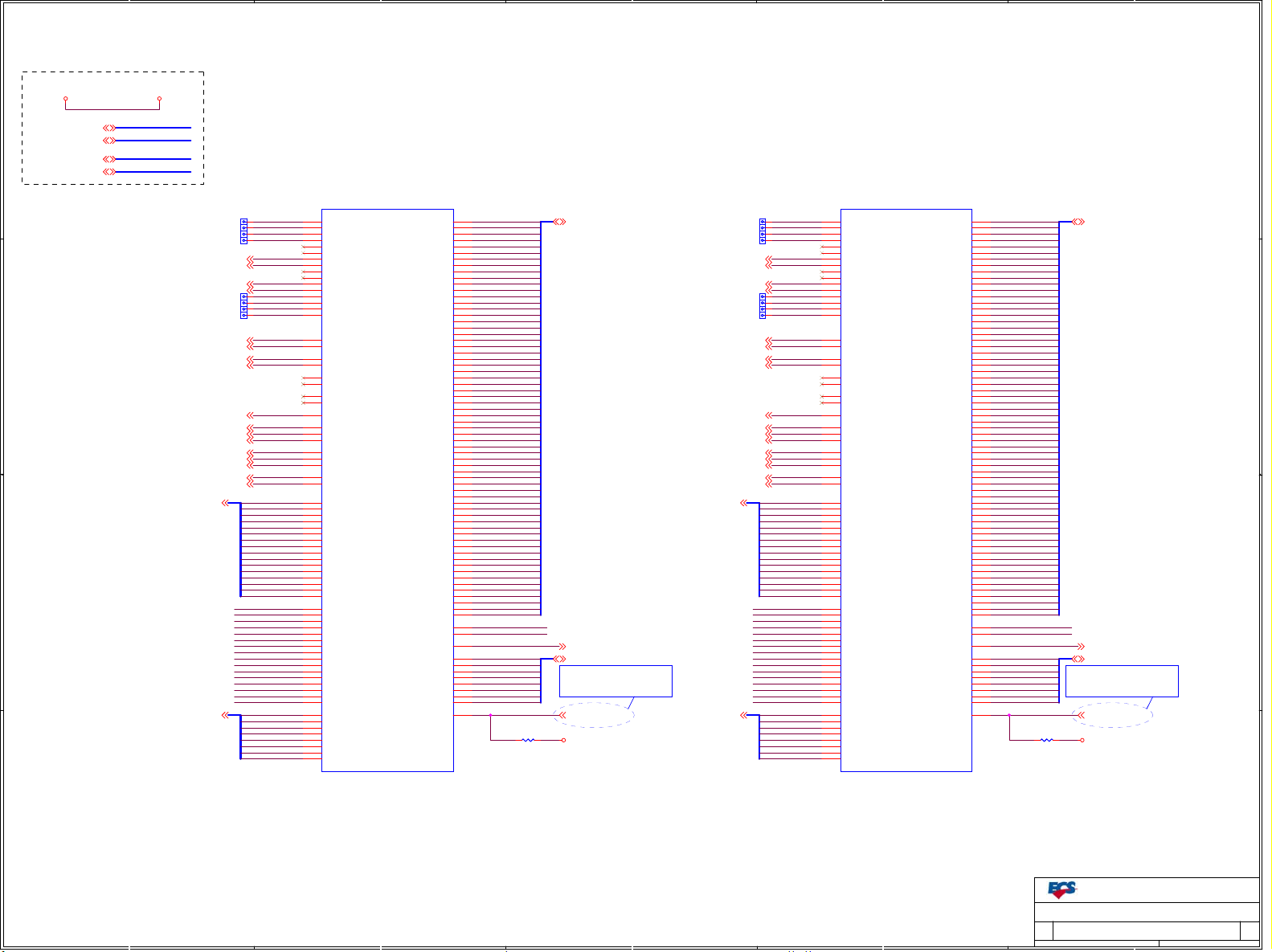

A

CPU_VDDIO_SUSV_DIMM

1.5V

4 4

MEM_MA_DQS_H[8..0]11

MEM_MA_DQS_L[8..0]11

MEM_MB_DQS_H[8..0]11

MEM_MB_DQS_L[8..0]11

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_L[8..0]

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_L[8..0]

B

C

D

E

CPU Memory

DDR3 Memory Interface A DDR3 Memory Interface B

CPUC

AJ19

AK19

AL19

AL18

AE30

AC31

AF31

AD29

AE29

AB31

AG31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

U31

U30

W29

W28

Y31

Y30

V31

W31

A18

A19

C19

D19

B19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

CPUC

MB_CLK_H7

MB_CLK_L7

MB_CLK_H6

MB_CLK_L6

MB_CLK_H5

MB_CLK_L5

MB_CLK_H4

MB_CLK_L4

MB_CLK_H3

MB_CLK_L3

MB_CLK_H2

MB_CLK_L2

MB_CLK_H1

MB_CLK_L1

MB_CLK_H0

MB_CLK_L0

MB0_CS_L1

MB0_CS_L0

MB0_ODT1

MB0_ODT0

MB1_CS_L1

MB1_CS_L0

MB1_ODT1

MB1_ODT0

MB_RESET_L

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MEM CHB

MEM CHB

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

ZIF-941P-S

ZIF-941P-S

MEM_MB_DATA63

AH13

MEM_MB_DATA62

AL13

MEM_MB_DATA61

AL15

MEM_MB_DATA60

AJ15

MEM_MB_DATA59

AF13

MEM_MB_DATA58

AG13

MEM_MB_DATA57

AL14

MEM_MB_DATA56

AK15

MEM_MB_DATA55

AL16

MEM_MB_DATA54

AL17

MEM_MB_DATA53

AK21

MEM_MB_DATA52

AL21

MEM_MB_DATA51

AH15

MEM_MB_DATA50

AJ16

MEM_MB_DATA49

AH19

MEM_MB_DATA48

AL20

MEM_MB_DATA47

AJ22

MEM_MB_DATA46

AL22

MEM_MB_DATA45

AL24

MEM_MB_DATA44

AK25

MEM_MB_DATA43

AJ21

MEM_MB_DATA42

AH21

MEM_MB_DATA41

AH23

MEM_MB_DATA40

AJ24

MEM_MB_DATA39

AL27

MEM_MB_DATA38

AK27

MEM_MB_DATA37

AH31

MEM_MB_DATA36

AG30

MEM_MB_DATA35

AL25

MEM_MB_DATA34

AL26

MEM_MB_DATA33

AJ30

MEM_MB_DATA32

AJ31

MEM_MB_DATA31

E31

MEM_MB_DATA30

E30

MEM_MB_DATA29

B27

MEM_MB_DATA28

A27

MEM_MB_DATA27

F29

MEM_MB_DATA26

F31

MEM_MB_DATA25

A29

MEM_MB_DATA24

A28

MEM_MB_DATA23

A25

MEM_MB_DATA22

A24

MEM_MB_DATA21

C22

MEM_MB_DATA20

D21

MEM_MB_DATA19

A26

MEM_MB_DATA18

B25

MEM_MB_DATA17

B23

MEM_MB_DATA16

A22

MEM_MB_DATA15

B21

MEM_MB_DATA14

A20

MEM_MB_DATA13

C16

MEM_MB_DATA12

D15

MEM_MB_DATA11

C21

MEM_MB_DATA10

A21

MEM_MB_DATA9

A17

MEM_MB_DATA8

A16

MEM_MB_DATA7

B15

MEM_MB_DATA6

A14

MEM_MB_DATA5

E13

MEM_MB_DATA4

F13

MEM_MB_DATA3

C15

MEM_MB_DATA2

A15

MEM_MB_DATA1

A13

MEM_MB_DATA0

D13

MEM_MB_DQS_H8

J31

MEM_MB_DQS_L8

J30

J29

MEM_MB_CHECK7

K29

MEM_MB_CHECK6

K31

MEM_MB_CHECK5

G30

MEM_MB_CHECK4

G29

MEM_MB_CHECK3

L29

MEM_MB_CHECK2

L28

MEM_MB_CHECK1

H31

MEM_MB_CHECK0

G31

V29

EVENT pins are for future AM3r2

1 2

R281 1K-04R281 1K-04

MEM_MB_DM8 11

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

MEM_MB_EVENT_L 11

CPU_VDDIO_SUSCPU_VDDIO_SUS

CPUB

CPUB

STP47STP47

STP51STP51

STP48STP48

STP46STP46

MEM_MA0_CLK0_P11

MEM_MA0_CLK0_N11 MEM_MB0_CLK0_N11

MEM_MA0_CLK1_P11

MEM_MA0_CLK1_N11

STP45STP45

STP50STP50

STP49STP49

STP52STP52

MEM_MA0_CS_L111

3 3

2 2

MEM_MA0_CS_L011

MEM_MA0_ODT111 MEM_MB0_ODT111

MEM_MA0_ODT011

MEM_MA_RESET-11 MEM_MB_RESET-11

MEM_MA_CAS-11

MEM_MA_WE-11

MEM_MA_RAS-11

MEM_MA_BANK211

MEM_MA_BANK111

MEM_MA_BANK011

MEM_MA_CKE011

MEM_MA_ADD[15..0]11

MEM_MA_DM[7..0]11

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6 MEM_MB_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

AE20

AE19

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

U27

U26

V27

W27

W26

W25

U24

V24

G19

H19

G20

G21

E20

N25

Y27

L27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

MA_CLK_H7

MA_CLK_L7

MA_CLK_H6

MA_CLK_L6

MA_CLK_H5

MA_CLK_L5

MA_CLK_H4

MA_CLK_L4

MA_CLK_H3

MA_CLK_L3

MA_CLK_H2

MA_CLK_L2

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA1_ODT1

MA1_ODT0

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MEM CHA

MEM CHA

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

ZIF-941P-S

ZIF-941P-S

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

J25

MEM_MA_CHECK7

K25

J26

MEM_MA_CHECK5

G28

MEM_MA_CHECK4

G27

MEM_MA_CHECK3

L24

MEM_MA_CHECK2

K27

MEM_MA_CHECK1MEM_MA_DQS_H0

H29

MEM_MA_CHECK0

H27

W30

EVENT pins are for future AM3r2

1 2

R280 1K-04R280 1K-04

MEM_MA_DATA[63..0] 11 MEM_MB_DATA[63..0] 11

MEM_MB_ADD[15..0]11

MEM_MA_DM8 11

MEM_MA_CHECK[7..0] 11 MEM_MB_CHECK[7..0] 11

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

MEM_MA_EVENT_L 11

STP14STP14

STP15STP15

STP16STP16

STP11STP11

MEM_MB0_CLK0_P11

MEM_MB0_CLK1_P11

MEM_MB0_CLK1_N11

STP12STP12

STP13STP13

STP17STP17

STP18STP18

MEM_MB0_CS_L111

MEM_MB0_CS_L011

MEM_MB0_ODT011

MEM_MB_CAS-11

MEM_MB_WE-11

MEM_MB_RAS-11

MEM_MB_BANK211

MEM_MB_BANK111

MEM_MB_BANK011

MEM_MB_CKE111MEM_MA_CKE111

MEM_MB_CKE011

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3MEM_MA_CHECK6

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM[7..0]11

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

1 1

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

Elitegroup Computer Systems

AM3 CPU MEMORY

AM3 CPU MEMORY

AM3 CPU MEMORY

A885GM-M2

A885GM-M2

A885GM-M2

E

8

8

8

of

of

of

1.0

1.0

1.0

33Friday, February 26, 2010

33Friday, February 26, 2010

33Friday, February 26, 2010

A

4 4

3 3

2 2

VCC25A VCC25A

VCC3 VCC3

V_DIMM CPU_VDDIO_SUS

VDDHT

CPUCLK3

CPUCLK-3

SB_CPUPWRGD4,18

LDT_STOP-15,18

LDT_RST-7,15,18

CPU_PVEN4

CPU_SVD4

CPU_SVC4

CPU_THERMDC15,23

CPU_THERMDA23

CPU_THERMTRIP_L19

-CPU_PROCHOT18

CPU_COREFB+4

CPU_COREFB-4

CPU_VDDNB_FB4

CPU_VDDNB_FB-4

SB_CPU_SIC19

SB_CPU_SID19

2.5V

3.3V

1.5V

1.2V

CPU_CLKP

CPU_CLKN

CPU_PWRGD

LDT_STOPLDT_RST-

CPU_PVEN

CPU_SVD

CPU_SVC CPU_VDDNB_FB_L

CPU_THERMDC

CPU_THERMDA

CPU_THERMTRIP_L

CPU_PROCHOT_L_15

CPU_VDD_FB_H

CPU_VDD_FB_L

CPU_VDDNB_FB_H

CPU_VDDNB_FB_L

CPU_SIC

CPU_SID

CPU_VDDHT

STP10STP10

TP39TP39

TP37TP37

TP32TP32

TP29TP29

TP35TP35

STP43STP43

STP40STP40

TP17TP17

STP25STP25

STP24STP24

STP27STP27

B

VCC25A

FB40

FB40

FB120-08

FB120-08

1 2

Layout: Place as close as

possible to CPU socket.

a,Rshunt near CPU pin<600mil

b,Cseries as a pair within 25mil

c,Cseries to CPU pin trace length<1250mil

d,12:4:6:4:12(1080 for 93ohm)

CPU_VDDIO_SUS

12

R267

R267

15-1-06

15-1-06

0.25W

12

R266

R266

15-1-06

15-1-06

12mil(width):20mil(spacing)

CPU_M_VREF_SUS CPU_VDDIO_SUS

C251

C251

C250

C250

1000P-04

1000P-04

.1U-04

.1U-04

2 1

2 1

Layout: Place within 500

mils of the CPU socket.

LDT_RSTLDT_STOPCPU_PWRGD

C

a,20mil(width):20mil(spacing)

b,reference to GND

C249

C249

10U-08

10U-08

2 1

CPU_CLKP

CPU_CLKN CPU_SVD

Layout: Keep trace to resistors

less than 1" from CPU pins.

C252

C252

.22U-06

.22U-06

21

21

1 2

1 2

1 2

1 2

2

4

6

8

2 1

12

CPU_PRESENT_L19

TP45TP45

TP43TP43

STP32STP32

STP37STP37

STP39STP39

STP31STP31

STP42STP42

STP30STP30

STP33STP33

STP35STP35

STP34STP34

2 1

C235 3900P-04C235 3900P-04

C234 3900P-04C234 3900P-04

R269 39.2-1-04R269 39.2-1-04

R272 39.2-1-04R272 39.2-1-04

R264 511-1-04R264 511-1-04

R265 511-1-04R265 511-1-04

RN19 300-8P4R-06RN19 300-8P4R-06

1

3

5

7

CPU_VDDA_RUN

2.5V@0.25A

C253

C253

3300P-04

3300P-04

TP51TP51

R252

R252

169-1-04

169-1-04

STP54STP54

STP58STP58

CPU_TDI7

CPU_TRST-7

CPU_TCK7

CPU_TMS7

CPU_DBREQ_7

TP15TP15

STP44STP44

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_H_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST7_ANALOG_T

CPU_TEST6_DIECRACKMON

CPU_TEST3_GATE0

CPU_TEST2_DRAIN0

CPU_VDDIO_SUS

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_PWRGD

LDT_STOPLDT_RST-

CPU_PRESENT_L

CPU_SIC

CPU_SID

CPU_SA0

CPU_ALERT_

CPU_VDD_FB_H

CPU_VDD_FB_L

CPU_VDDIO_PWRGD

CPU_VTT_SUS_SENSE

CPU_M_ZN

CPU_M_ZP

C10

D10

AK6

AK4

AL10

AJ10

AH10

AH11

AJ11

AH9

AH7

C18

C20

G24

G25

H25

A8

B8

C9

D8

C7

AL3

AL6

AL4

AL9

A5

G2

G1

F3

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

E5

AJ5

AJ6

F2

L25

L26

CPUD

CPUD

VDDA_1

VDDA_2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

SA0

ALERT_L

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

M_VDDIO_PWRGD

VDDR_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST3

TEST2

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

INT. MISC.

INT. MISC.

RSVD6

RSVD7

RSVD8

MISC.

MISC.

D

CORE_TYPE

VID5

VID4

SVC/VID3

SVD/VID2

PVIEN/VID1

VID0

THERMDC

THERMDA

THERMTRIP_L

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

ZIF-941P-S

ZIF-941P-S

CPU_CORE_TYPE_L

G5

CPU_VID5

D2

CPU_VID4

D1

CPU_SVC

C1

E3

CPU_PVEN

E2

CPU_VID0

E1

CPU_THERMDC

AG9

CPU_THERMDA

AG8

CPU_THERMTRIP_L_15

AK7

CPU_PROCHOT_L_15

AL7

CPU_TDO

AK10

CPU_DBRDY

B6

CPU_VDDIO_FB_H

AK11

CPU_VDDIO_FB_L

AL11

CPU_VDDNB_FB_H

G4

G3

CPU_PSI-

F1

CPU_HTREF1CPU_M_VREF

V8

CPU_HTREF0

V7

STP9STP9

CPU_TEST29_H_FBCLKOUT_H

C11

CPU_TEST29_L_FBCLKOUT_L

D11

CPU_TEST24_SCANCLK1

AK8

CPU_TEST23_TSTUPD

AH8

CPU_TEST22_SCANSHIFTEN

AJ9

CPU_TEST21_SCANEN

AL8

CPU_TEST20_SCANCLK2

AJ8

CPU_TEST28_H_PLLCHRZ_H

J10

CPU_TEST28_L_PLLCHRZ_L

H9

CPU_TEST27_SINGLECHAIN

AK9

CPU_TEST26_BURNIN_L

AK5

CPU_TEST10_ANALOGOUT

G7

CPU_TEST8_DIG_T

D4

L30

L31

AD25

AE24

AE25

AJ18

AJ20

AK3

E

CPU_VDDIO_SUS

12

R259

R259

10K-04

10K-04

B

CPU_THERMTRIP_L_15 CPU_THERMTRIP_L

E C

Q9 2N3904-SQ9 2N3904-S

R251 1K-04R251 1K-04

1 2

TP28TP28

TP34TP34

R250 1K-04R250 1K-04

1 2

R249 1K-04R249 1K-04

1 2

TP33TP33

1 2

CPU_TDO 7

CPU_DBRDY 7

STP56STP56

STP57STP57

STP53STP53

STP29STP29

R255 44.2-1-04R255 44.2-1-04

R253 44.2-1-04R253 44.2-1-04

For AM3 CPU

Layout: Keep CPU_HTREF0,1

less than 1.5" from in length.

1 2

1 2

1 2

R268 80.6-1-04R268 80.6-1-04

TP47TP47

TP19TP19

TP50TP50

TP48TP48STP26STP26

TP46TP46

STP41STP41

STP38STP38

TP49TP49

STP55STP55

STP36STP36

STP28STP28

CPU_VDDIO_SUS

R248

R248

300-04

300-04

CPU_VDDHT

Layout: Route as 80 ohms diff

impedance (4/5mil).Keep trace

to resistor < 1" from CPU pins.

CPU_PRESENT_L

CPU_SIC

CPU_SID

CPU_TEST27_SINGLECHAIN

CPU_THERMTRIP_L_15

CPU_PROCHOT_L_15

CPU_TEST26_BURNIN_L

1 1

A

B

CPU_SA0

CPU_PWRGD

LDT_STOP-

LDT_RST-

R254 10K-04R254 10K-04

1 2

R258 10K-04R258 10K-04

1 2

R257 10K-04R257 10K-04

1 2

RN20 300-8P4R-06RN20 300-8P4R-06

1

2

3

4

5

6

7

8

R256 0-04R256 0-04

1 2

C248 180P-04C248 180P-04

C247 180P-04C247 180P-04

C246 180P-04C246 180P-04

21

21

21

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

C

D

Date: Sheet

AM3 CPU CONTROL&MISC

AM3 CPU CONTROL&MISC

AM3 CPU CONTROL&MISC

A885GM-M2

A885GM-M2

A885GM-M2

9

9

9

of

of

E

of

1.0

1.0

1.0

33Friday, February 26, 2010

33Friday, February 26, 2010

33Friday, February 26, 2010

A

B

C

D

E

CPU_VDD_RUN CPU_VDD_RUN

4 4

VCORE

V_DIMM

CPU_VDDNB

VDDHT

VDDHT

3 3

2 2

CPU_VDD_RUN

CPU_VDDIO_SUS

CPU_VDDNB_RUN

CPU_VDDR

CPU_VDDHT

CPUE

CPUE

B3

VDD_1

C2

VDD_2

C4

VDD_3

D3

VDD_4

D5

VDD_5

E4

VDD_6

E6

VDD_7

F5

VDD_8

F7

VDD_9

G6

VDD_10

G8

VDD_11

H7

VDD_12

H11

VDD_13

H23

VDD_14

J8

VDD_15

J12

VDD_16

J14

VDD_17

J16

VDD_18

J18

VDD_19

J20

VDD_20

J22

VDD_21

J24

VDD_22

K7

VDD_23

K9

VDD_24

K11

VDD_25

K13

VDD_26

K15

VDD_27

K17

VDD_28

K19

VDD_29

K21

VDD_30

K23

VDD_31

L4

VDD_32

L5

VDD_33

L8

VDD_34

L10

VDD_35

L12

VDD_36

L14

VDD_37

L16

VDD_38

L18

VDD_39

L20

VDD_40

L22

VDD_41

M2

VDD_42

M3

VDD_43

M7

VDD_44

M9

VDD_45

M11

VDD_46

M13

VDD_47

M15

VDD_48

M17

VDD_49

M19

VDD_50

M21

VDD_51

M23

VDD_52

N8

VDD_53

N10

VDD_54

N12

VDD_55

N14

VDD_56

N16

VDD_57

N18

VDD_58

N20

VDD_59

N22

VDD_60

P7

VDD_61

P9

VDD_62

P11

VDD_63

P13

VDD_64

P15

VDD_65

P17

VDD_66

P19

VDD_67

P21

VDD_68

P23

VDD_69

R4

VDD_70

R5

VDD_71

R8

VDD_72

R10

VDD_73

R12

VDD_74

R14

VDD_75

R16

VDD_76

R18

VDD_77

R20

VDD_78

R22

VDD_79

T2

VDD_80

T3

VDD_81

T7

VDD_82

T9

VDD_83

T11

VDD_84

T13

VDD_85

A3

VSS_1

A7

VSS_2

A9

VSS_3

A11

VSS_4

B4

VSS_5

B9

VSS_6

B11

VSS_7

B14

VSS_8

B16

VSS_9

B18

VSS_10

B20

VSS_11

B22

VSS_12

B24

VSS_13

B26

VSS_14

B28

VSS_15

B30

VSS_16

C3

VSS_17

D14

VSS_18

D16

VSS_19

D18

VSS_20

D20

VSS_21

D22

VSS_22

D24

VSS_23

D26

VSS_24

D28

VSS_25

D30

VSS_26

E11

VSS_27

F4

VSS_28

F14

VSS_29

F16

VSS_30

F18

VSS_31

F20

VSS_32

F22

VSS_33

F24

VSS_34

F26

VSS_35

F28

VSS_36

F30

VSS_37

G9

VSS_38

G11

VSS_39

H8

VSS_40

H10

VSS_41

H12

VSS_42

H14

VSS_43

H16

VSS_44

H18

VSS_45

H24

VSS_46

H26

VSS_47

H28

VSS_48

H30

VSS_49

J4

VSS_50

POWER/GND1

POWER/GND1

J5

VSS_51

J7

VSS_52

J9

VSS_53

J11

VSS_54

J13

VSS_55

J15

VSS_56

J17

VSS_57

J19

VSS_58

J21

VSS_59

J23

VSS_60

K2

VSS_61

K3

VSS_62

K8

VSS_63

K10

VSS_64

K12

VSS_65

K14

VSS_66

K16

VSS_67

K18

VSS_68

K20

VSS_69

K22

VSS_70

K24

VSS_71

K26

VSS_72

K28

VSS_73

K30

VSS_74

L7

VSS_75

L9

VSS_76

L11

VSS_77

L13

VSS_78

L15

VSS_79

L17

VSS_80

L19

VSS_81

L21

VSS_82

L23

VSS_83

M8

VSS_84

M10

VSS_85

ZIF-941P-S

ZIF-941P-S

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AE10

AE12

AF11

CPUF

CPUF

T15

VDD_86

T17

VDD_87

T19

VDD_88

T21

VDD_89

T23

VDD_90

U8

VDD_91

U10

VDD_92

U12

VDD_93

U14

VDD_94

U16

VDD_95

U18

VDD_96

U20

VDD_97

U22

VDD_98

V9

VDD_99

V11

VDD_100

V13

VDD_101

V15

VDD_102

V17

VDD_103

V19

VDD_104

V21

VDD_105

V23

VDD_106

W4

VDD_107

W5

VDD_108

W8

VDD_109

W10

VDD_110

W12

VDD_111

W14

VDD_112

W16

VDD_113

W18

VDD_114

W20

VDD_115

W22

VDD_116

Y2

VDD_117

Y3

VDD_118

Y7

VDD_119

Y9

VDD_120

Y11

VDD_121

Y13

VDD_122

Y15

VDD_123

Y17

VDD_124

Y19

VDD_125

Y21

VDD_126

Y23

VDD_127

AA8

VDD_128

VDD_129

VDD_130

VDD_131

VDD_132

VDD_133

VDD_134

POWER/GND2

POWER/GND2

VDD_135

AB7

VDD_136

AB9

VDD_137

VDD_138

VDD_139

VDD_140

VDD_141

VDD_142

VDD_143

VDD_144

AC4

VDD_145

AC5

VDD_146

AC8

VDD_147

VDD_148

VDD_149

VDD_150

VDD_151

VDD_152

VDD_153

VDD_154

AD2

VDD_155

AD3

VDD_156

AD7

VDD_157

AD9

VDD_158

VDD_159

VDD_160

VDD_161

VDD_162

AF7

VDD_163

AF9

VDD_164

VDD_165

AG4

VDD_166

AG5

VDD_167

AG7

VDD_168

AH2

VDD_169

AH3

VDD_170

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

ZIF-941P-S

ZIF-941P-S

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20