Page 1

5

4

3

2

1

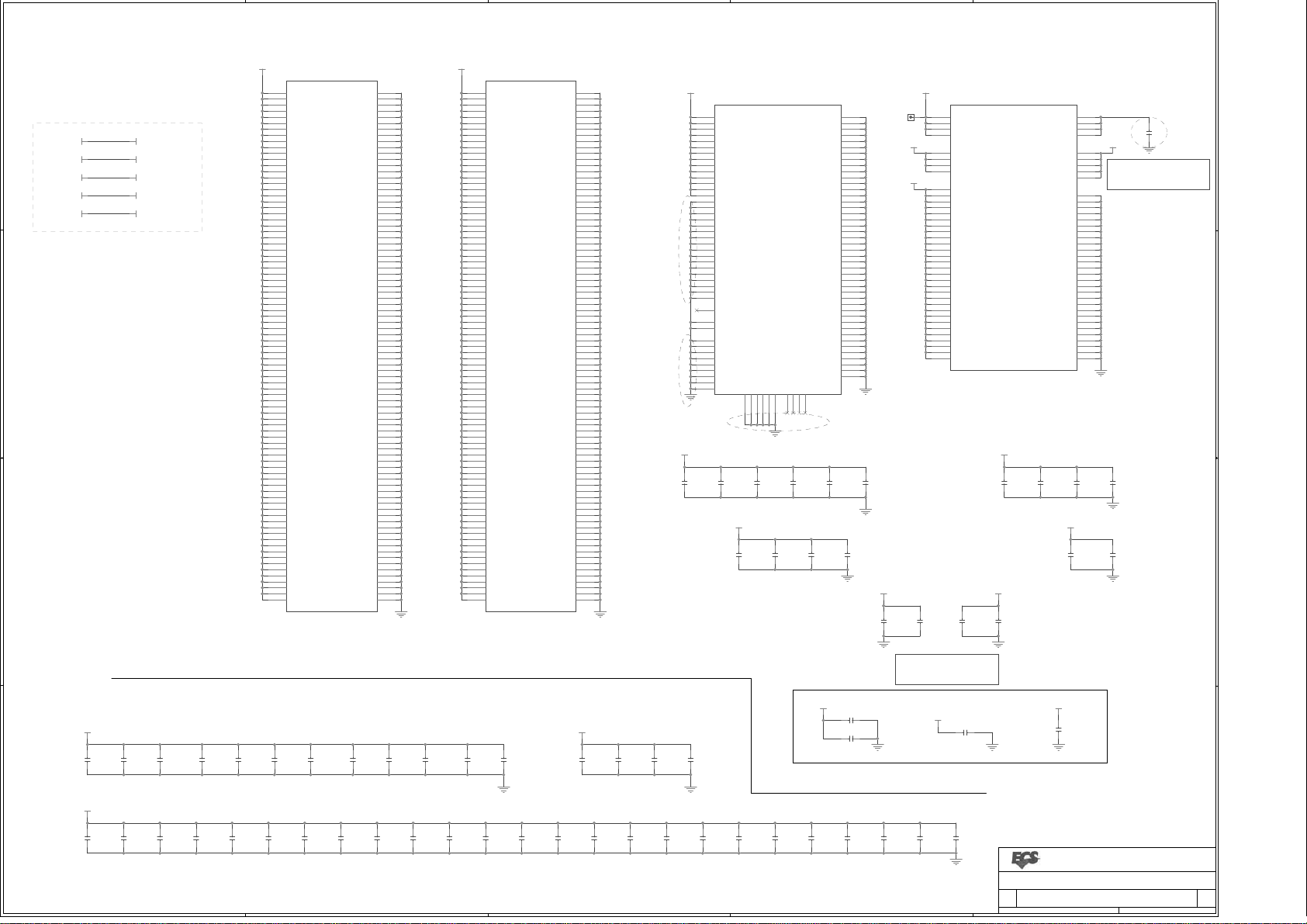

A785GM-M7

D D

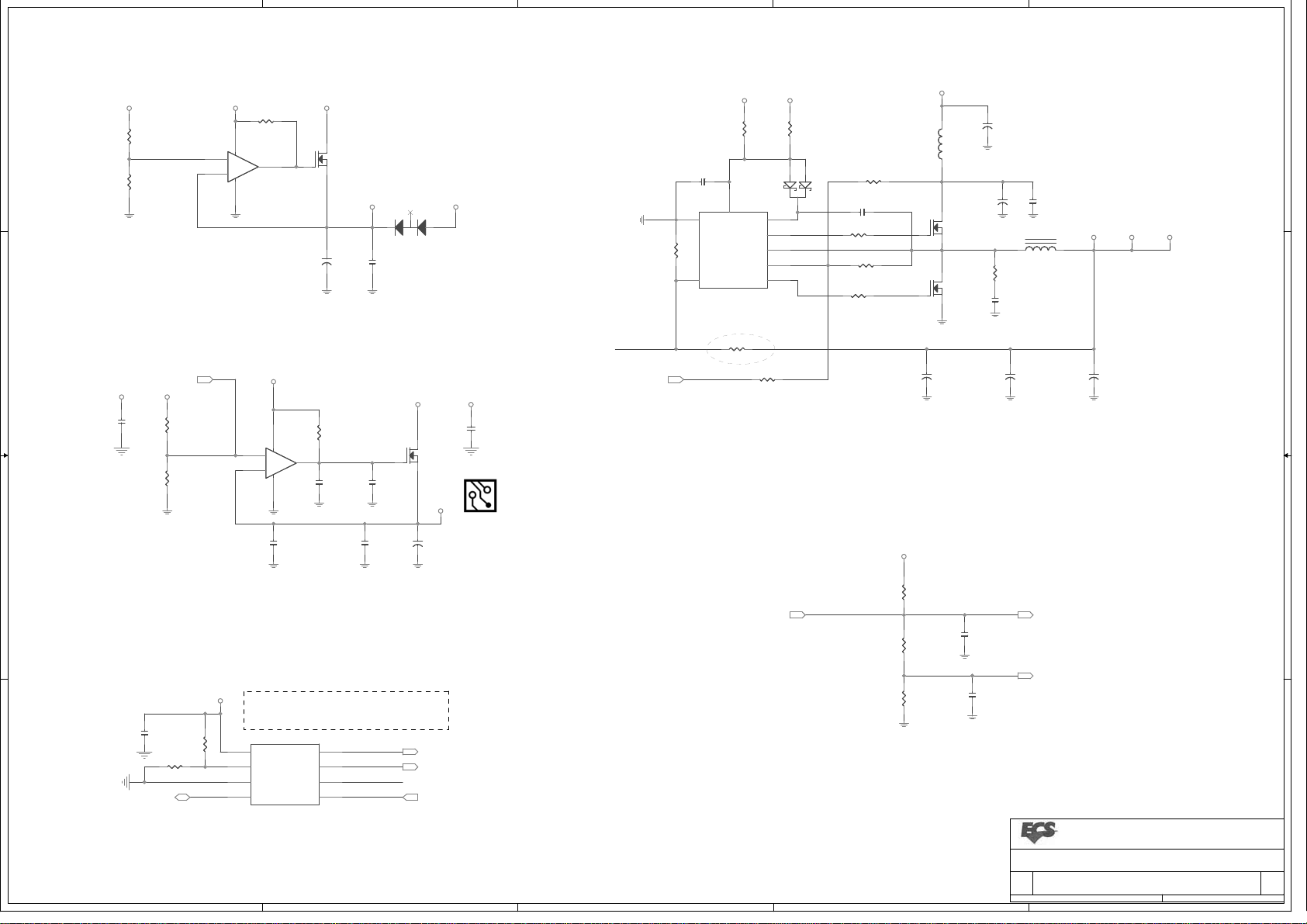

SCHEMATICS TABLE:

Page Index

------- ------------------------

1

COVER PAGE

BLOCK DIADRAM2

CLK GEN

3

4

Power 1(CPU Vcore)

5

Power 2(DC-DC)

C C

B B

10

11

12

13

14

15

16

17

6

Power 3(DC-DC,Power Sequence)

7

AM3 CPU HT & OVERCLOCK

AM3 CPU MEMORY

8

AM3 CPU CONTROL & MISC

9

AM3 CPU PWR & GND

DDR3 DIMM CHANNEL

DDR3 DIMM POWER

NB1(HT Link)

NB3(System)

NB4(Power&GND)

PCI-E Slot(X16,X1)

Page Index

------- ------------------------

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

SB1(PCIE,PCI,CPU)

SB2(ACPI,USB,GPIO,Audio)

SB3(SATA,IDE,HWM,SPI)

SB4(Power,Decoupling)

SB5(Straps)

SIO(IT8726F-S/FX)

PCI1,PCI2

IDE, USB, PSKBM, COM

HDMI/DVI, VGA

Front Panel,Fan

LAN( Atheros 8131M/8132M )

Audio1(Chip 1705&662)

Audio2(Panel)

Power Delivery Chart (consumption)NB2(PCI-E Link)

Clock Distribution

Power Sequence Distribution

REVISION HISTORY:

Rev Date Notes

------ -------------- ---------------------------------------------------------------------------------

2.0 2010-01-06

Rev:2.0

2009-09-04

2009-11-061.0

INITIAL RELEASEA

Change from A785GM-M5 V:A

1.Delete LPT and IR.

2.Add one front USB header F_USB3.

3.Change the USB connector power.

4.Add CPU Over Clocking circuit.

5.Add UP6262 for CPU and NB to enhance the voltage.

6.VRM chipset change RT8855 to RT8861.

7.Change to support AM3 CPU and DDR3.

8.Add a HDMI connector.

1.Modify CPU VRM circuit according to the manufacturer's recommendations.

2.Modify VCC_DUAL power.

1.Modify CPU VRM circuit RT8861 Colay RT8855.

IMPORTANT NOTES ABOUT

THIS SCHEMATIC

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

DESIGN NOTE: Example

text for the design note to

A A

show the note inside the

colored box.

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

5

1) DESIGN NOTES in

grey are information

notes.

2) DESIGN NOTES in

yellow are notes of

caution.

3) DESIGN NOTES in

red are critical, and

must be understood and

followed.

PCB

PCB

15-R56-010010

15-R56-010010

L1:TOPPCB STACK:

L2:PWR

L3:GND

L4:BOTTOM

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Cover Page

Cover Page

Cover Page

A785GM-M7

A785GM-M7

A785GM-M7

1

1

1

of

33Thursday, January 07, 2010

of

33Thursday, January 07, 2010

of

1

33Thursday, January 07, 2010

2.0

2.0

2.0

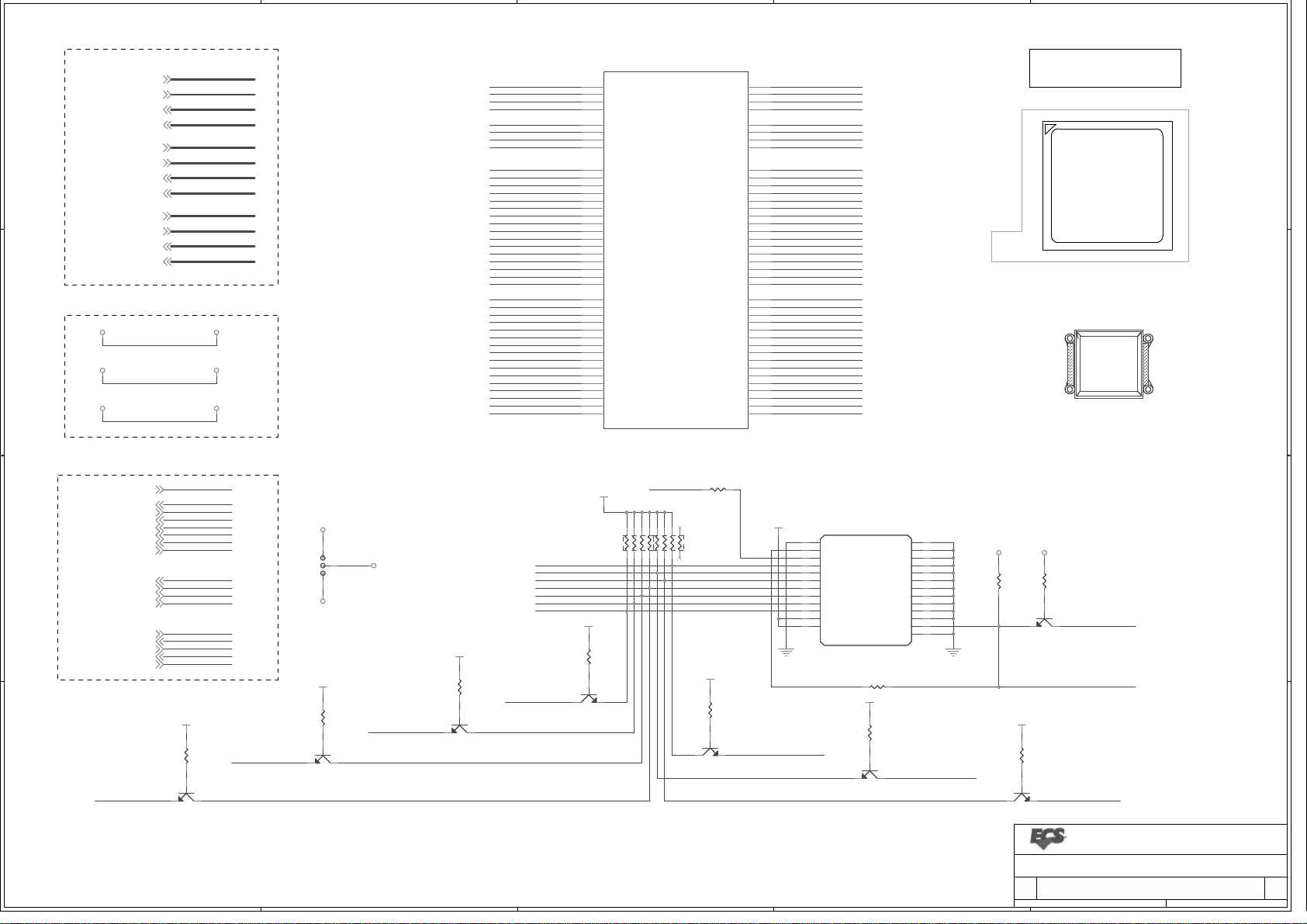

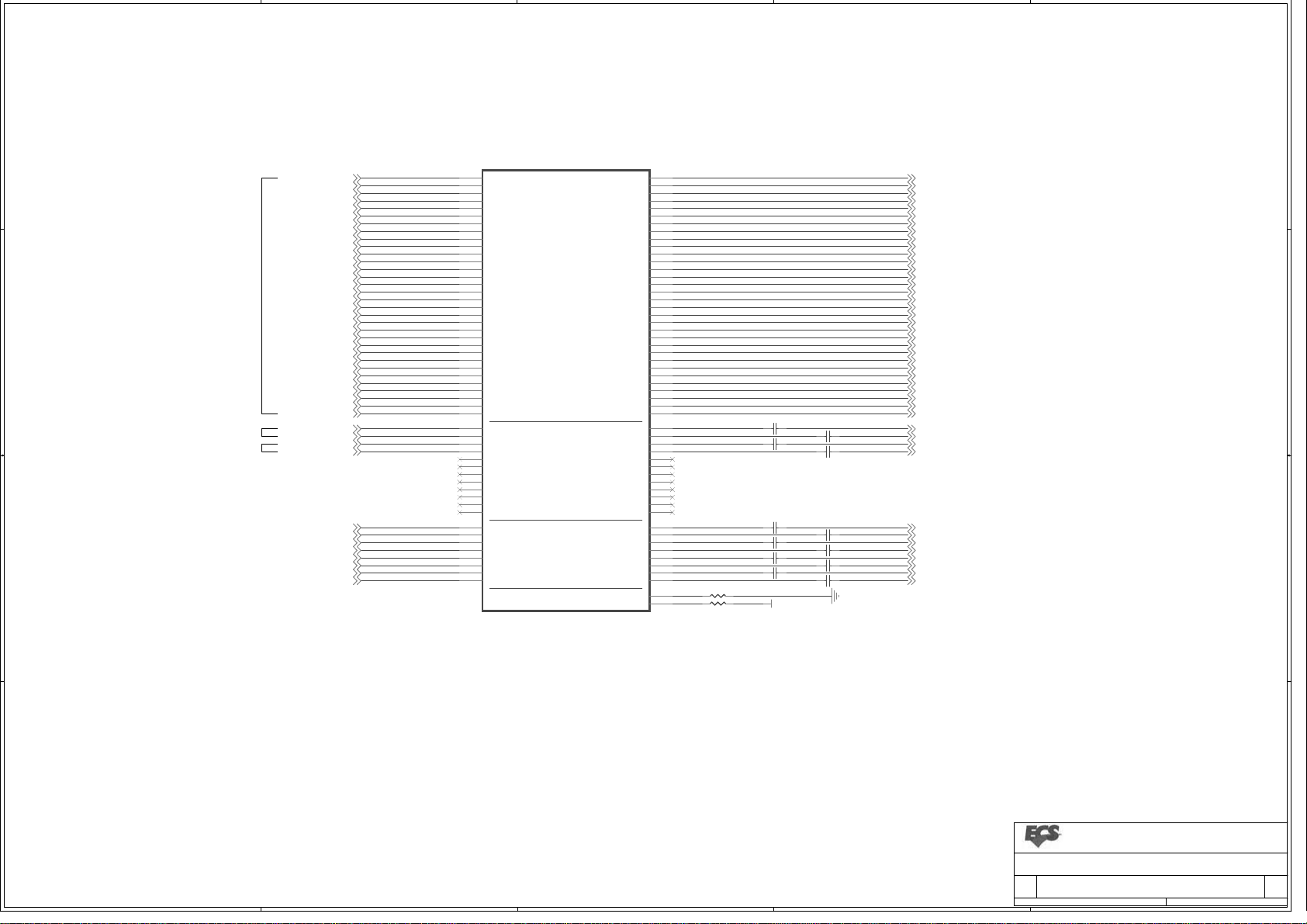

Page 2

5

4

3

2

1

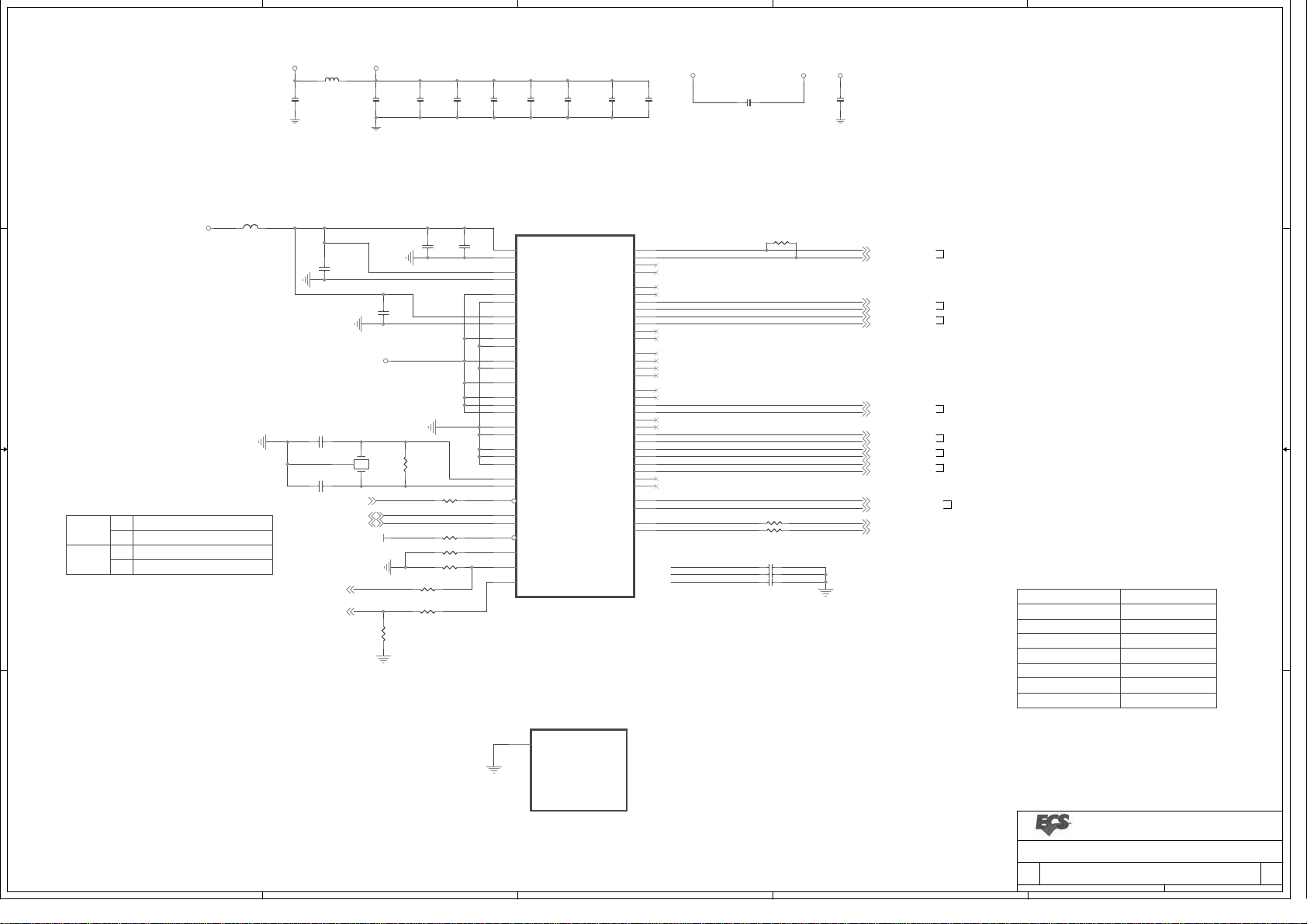

PWM Intersil

RT8861(DCR sense)

D D

Clock Generator

ICS 9LPRS471C

PCIE X 16

HyperTransport

PCIE 16X

LINK

AMD

AM3

AM3 SOCKET

OUT

NB:RS880

IN

16x16

DDR3 A CHANNEL

Dual Channel

DDR3 B CHANNEL

Unbuffered DDR3

DIMM1

Unbuffered DDR3

DIMM2

VGA

HT LINK0 CPU I/F

PCIE X 1

LAN

(Atheros 8131M

8132M)

PCIE 1X

PCIE 1X

Integrated Graphics

1 16X PCIE VIDEO I/F

1 2X PCIE I/F with SB

4 1X PCIE I/F

2CH TMDS

DVI CON

OPTION

HDMI CON

4X ALINK

C C

10 ports

USB 2.0

SB:ATI SB710

USB2.0*10

ATA66/100/133

IDE*1

SATA*4

AUDIO CODEC

VIA1705

HD AUDIO I/F

AC97 2.3 & Azalia

ATA 66/100/133

Serial ATA

SATA*6

ACPI 2.0

PCI*2

PCI BUS

LPC 1.1

MII

PCI/PCI Bridge

SPI

BIOS

8M

LPC I/F

B B

ITE SIO 8726F/IX

COM

2

A A

3S

1

TO-263

B55QS03

5

G

TO-263

2SK3296

D

D

G

TO-252

20N03

45N03

FDD6030L

4

S

C

B C E

TO-251

HI772(1.4W)

(PNP)

D

G

SOT-23

2N7002

SI2303S

SI2301S

C

B

SOT-23

2N3904

2N3906

MMBT2907A

E

S

3

3

1

SOT-23

BAT54C

3

2

1

2

T0-92

LM431

78L05-DTM3055TL-S

LM432

B

E

C

T0-92

2N2222A

2N2097ABAT54S

B

EC

T0-92

HSD882-D

Elitegroup Computer Systems

Elitegroup Computer Systems

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Elitegroup Computer Systems

Block Diagram

Block Diagram

Block Diagram

A785GM-M7

A785GM-M7

A785GM-M7

2

2

2

of

33Thursday, January 07, 2010

of

33Thursday, January 07, 2010

of

1

33Thursday, January 07, 2010

2.0

2.0

2.0

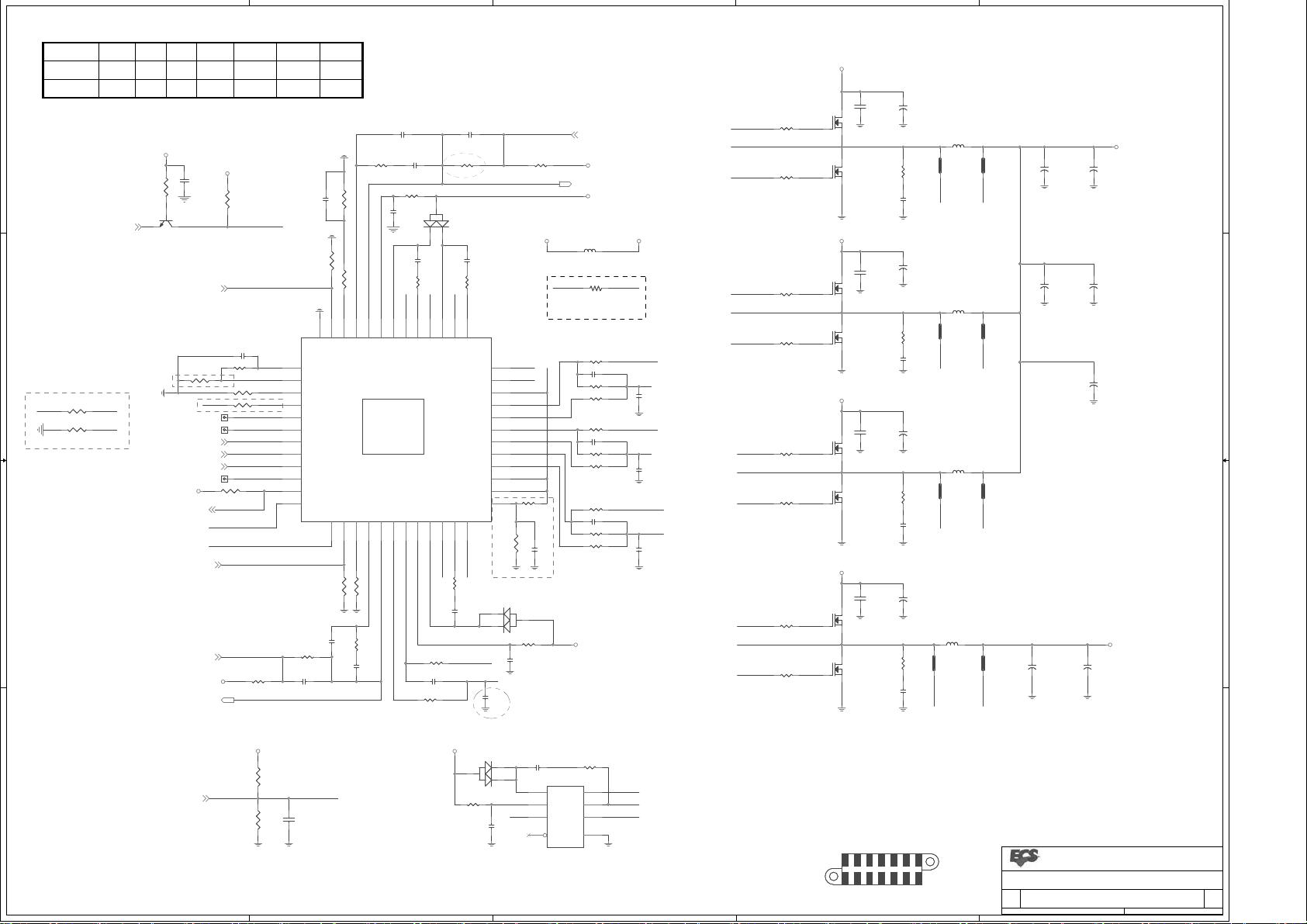

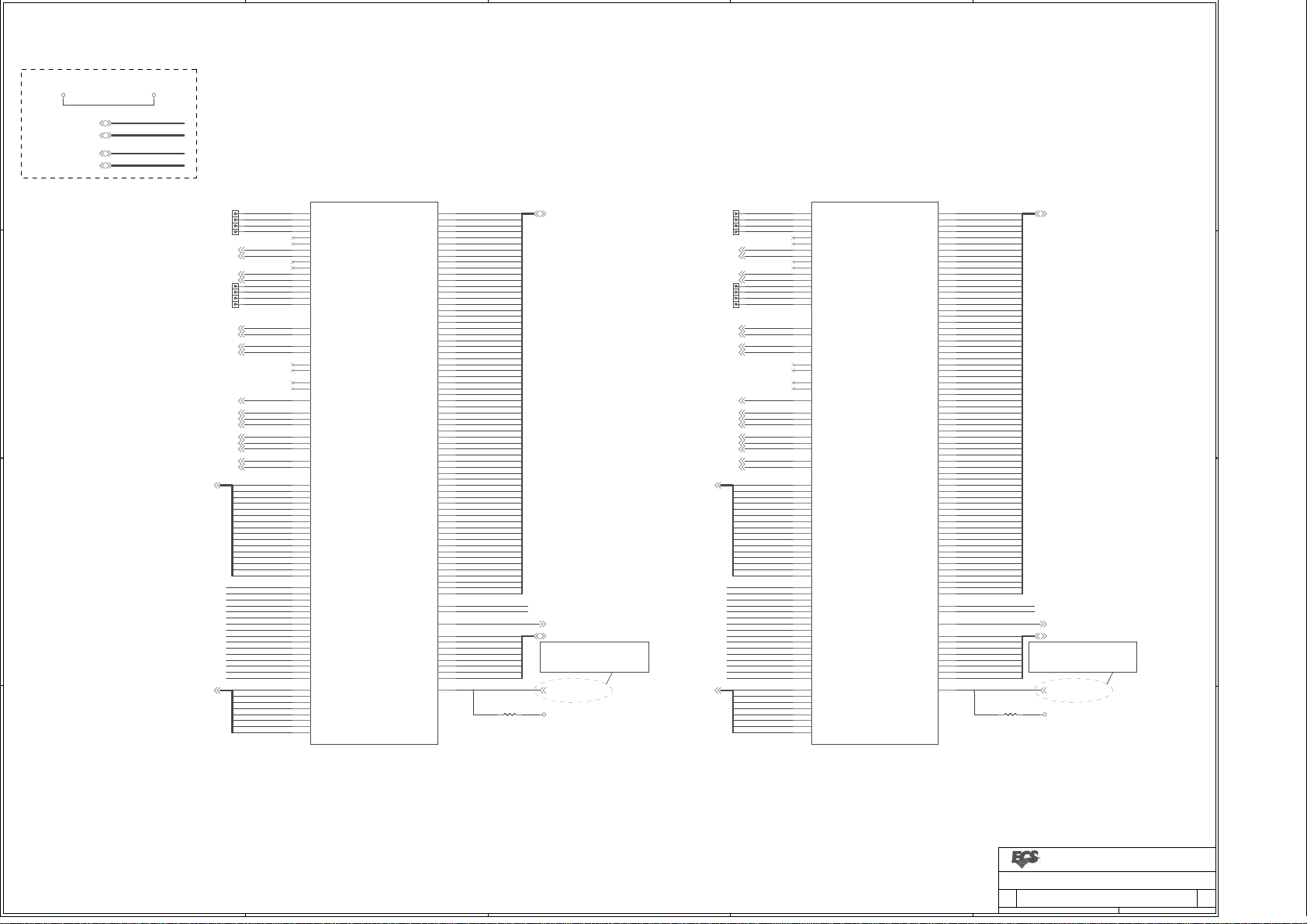

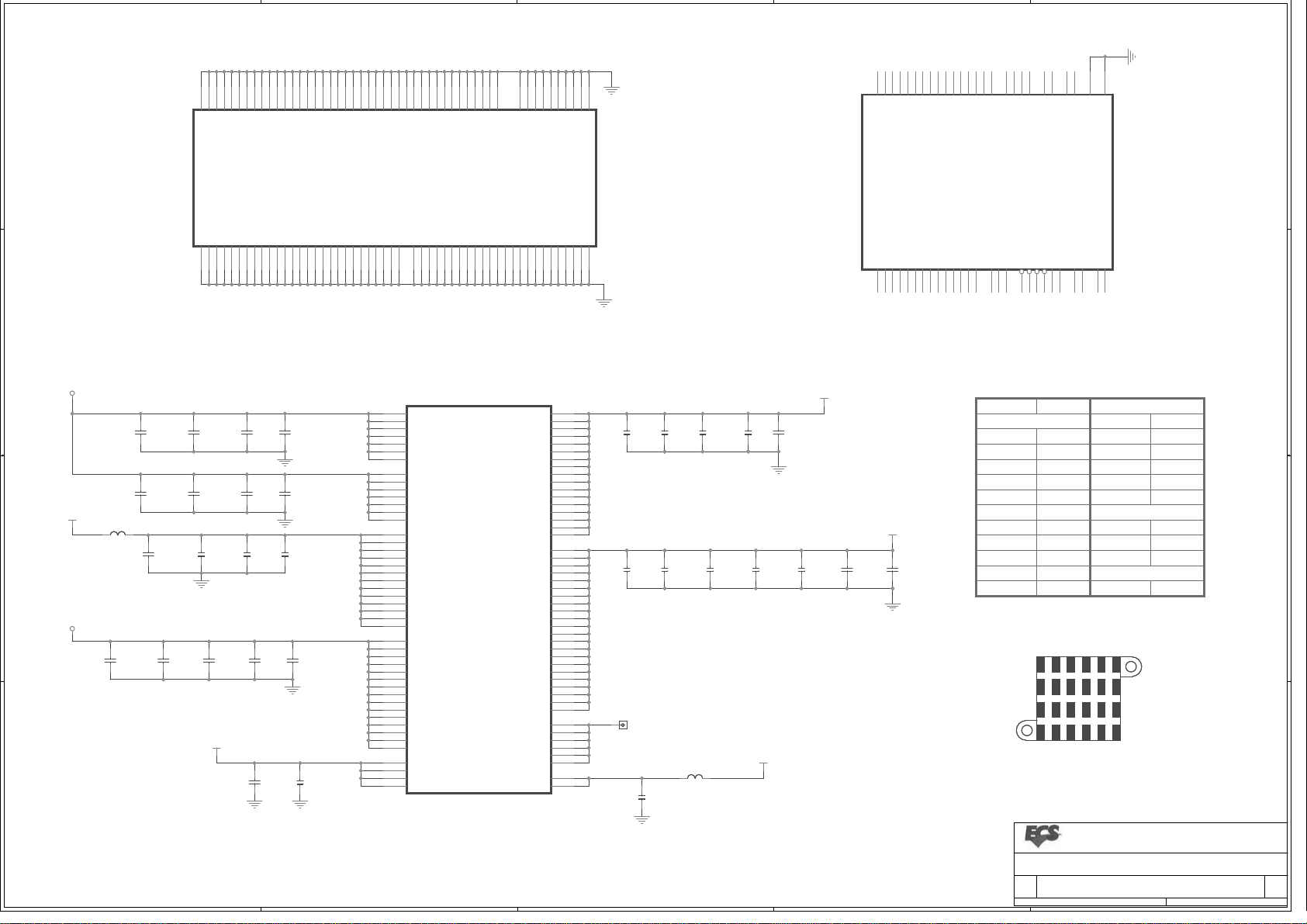

Page 3

5

VCC3 CLK_VDD

FB33

FB33

FB-600-08P

FB-600-08P

1 2

C121

C121

10U-08-O

10U-08-O

D D

4

C100

C100

10U-X5-08

10U-X5-08

C145

C145

.1U-04

.1U-04

1- PLACE ALL SERIAL TERMINATION

RESISTORS CLOSE TO CLOCK GEN

C146

C146

.1U-04

.1U-04

C140

C140

.1U-04

.1U-04

C142

C142

.1U-04-O

.1U-04-O

C138

C138

.1U-04

.1U-04

C125

C125

.1U-04

.1U-04

3

VCC3 CLK_VDD VCC3

C131

C131

.1U-04

.1U-04

C122

C122

.1U-04-O

.1U-04-O

C128

C128

.1U-04

.1U-04

2

For EMI

1

2- PUT DECOUPLING CAPS CLOSE TO CLOCK GEN POWER PIN

FB37 FB120-06FB37 FB120-06

VCC3

C C

C106 56P-04C106 56P-04

C105 56P-04C105 56P-04

66 MHz 3.3V single ended HTT clock

1

SEL_HTT66

0

100 MHz differential HTT clock

*

1

B B

SEL_SATA

* default

100 MHz non-spreading differential SRC clock

*

0

100 MHz spreading differential SRC clock

OSC_14M_SB18

OSC_14M_NB15

CLK_VDDA

1U-06

1U-06

C123

C123

CLK_VDDREF

CLK_VDD48

1U-06

1U-06

C129

C129

CLK_VDD

R99

R99

X2

X2

1M-04-O

3

1 2

-HW_RST19,23,27 NBHT_REFCLK_P 15

SMBCK6,11,17,19,24

CLK_VDD

Rb

1M-04-O

X-14.318M

X-14.318M

1 2

R114 1K-04R114 1K-04

R111 8.2K-04R111 8.2K-04

R112 8.2K-04R112 8.2K-04

R119 33-04R119 33-04

1 2

R113 150-1-04R113 150-1-04

1 2

Ra

R85

R85

75-1-04

75-1-04

1 2

MC21

MC21

2.2U-06

2.2U-06

1 2

R88 0-04-SHR88 0-04-SH

1 2

12

12

.1U-04

.1U-04

C133

C133

CLK1A

CLK1A

44

VDDA

43

GNDA

60

VDDREF

61

GNDREF

39

VDDSATA

42

GNDSATA

64

VDD48

3

GND48

48

VDDCPU

47

GNDCPU

56

VDDHTT

53

GNDHTT

34

VDDATIG

11

VDDSRC1

16

VDDSRC2

25

VDDSB_SRC

28

GNDATIG1

33

GNDATIG2

10

GNDSRC1

17

GNDSRC2

24

GNDSB_SRC

62

X1

63

X2

52

RESTORE#

4

SMBCLK

5

SMBDAT

51

PD#

59

REF0/SEL_HTT66

58

REF1/SEL_SATA

57

REF2

ICS9LPRS471CS

ICS9LPRS471CS

CPUKG0T_LPRS

CPUKG0C_LPRS

CPUKG1T_LPRS

CPUKG1C_LPRS

ATIG0T_LPRS

ATIG0C_LPRS

ATIG1T_LPRS

ATIG1C_LPRS

ATIG2T_LPRS

ATIG2C_LPRS

ATIG3T_LPRS

ATIG3C_LPRS

SB_SRC0T_LPRS

SB_SRC0C_LPRS

SB_SRC1T_LPRS

SB_SRC1C_LPRS

SRC0T_LPRS

SRC0C_LPRS

SRC1T_LPRS

SRC1C_LPRS

SRC2T_LPRS

SRC2C_LPRS

SRC3T_LPRS

SRC3C_LPRS

SRC4T_LPRS

SRC4C_LPRS

SRC5T_LPRS

SRC5C_LPRS

SRC6T/SATAT_LPRS

SRC6C/SATAC_LPRS

HTT0T/66M_LPRS

HTT0C/66M_LPRS

48MHz_0

48MHz_1

50

49

46

45

38

37

36

35

32

31

30

29

27

26

23

22

21

20

19

18

15

14

13

12

9

8

7

6

41

40

55

54

2

1

R_CPUCLK

R_CPUCLK-

R_NBSRC_CLKP

R_NBSRC_CLKN

R_GFX_CLKP

R_GFX_CLKN

R_GPP_CLK0P

R_GPP_CLK0N

R_LAN_CLKP

R_LAN_CLKN

R_SBLINK_CLKP

R_SBLINK_CLKN

R_SBSRC_CLKP

R_SBSRC_CLKN

R_NBHT_REFCLKP

R_NBHT_REFCLKN

SIO_CLOCK_R

48M_USB_R

OSC_14M_NB

CLK_48M_USB

CLK_48M_SIO

R105 261-1-04-OR105 261-1-04-O

1 2

R117 33-04R117 33-04

1 2

R116 33-04R116 33-04

1 2

CC4 22P-04-OCC4 22P-04-O

CC5 22P-04-OCC5 22P-04-O

CC6 22P-04-OCC6 22P-04-O

CPUCLK 9

CPUCLK- 9

NBSRC_CLKP 15

NBSRC_CLKN 15

GFX_CLKP 17

GFX_CLKN 17

GPP_CLK0P 17

GPP_CLK0N 17

LAN_CLKP 28

LAN_CLKN 28

SBLINK_CLKP 15

SBLINK_CLKN 15

SBSRC_CLKP 18

SBSRC_CLKN 18

NBHT_REFCLK_N 15

CLK_48M_SIO 23SMBDT6,11,17,19,24

CLK_48M_USB 19

RS880 OSC_14M_NB 1.1V Ra/Rb=150R/75R

CLK1B

CLK1B

THERMAL GND

eGND65

THERMAL GND

65

CPU CLK

NB PCI-E GFX CLK

GFX SLOT

PCI-E 1X SLOT

LAN CHIP

A-Link (NB)

A-Link (SB)

HT REF CLK

NB CLOCK INPUT TABLE

* RS880 can be used as clock buffer to output two PCIE referecence clocks

By deault, chip will configured as input mode, BIOS can program it to output mode.

Clock chip has internal serial terminations for differencial pairs

NB CLOCKS RS880

HT_REFCLKP

HT_REFCLKN

REFCLK_P 14M SE (1.1V)

GFX_REFCLK 100M DIFF(IN/OUT)*

GPP_REFCLK

GPPSB_REFCLK 100M DIFF

100M DIFF

100M DIFF

VREFREFCLK_N

NC or 100M DIFF OUTPUT

A A

ICS9LPRS471CS

ICS9LPRS471CS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Clock Generator

Clock Generator

Clock Generator

A785GM-M7

A785GM-M7

A785GM-M7

333Thursday, January 07, 2010

333Thursday, January 07, 2010

333Thursday, January 07, 2010

of

of

1

of

2.0

2.0

2.0

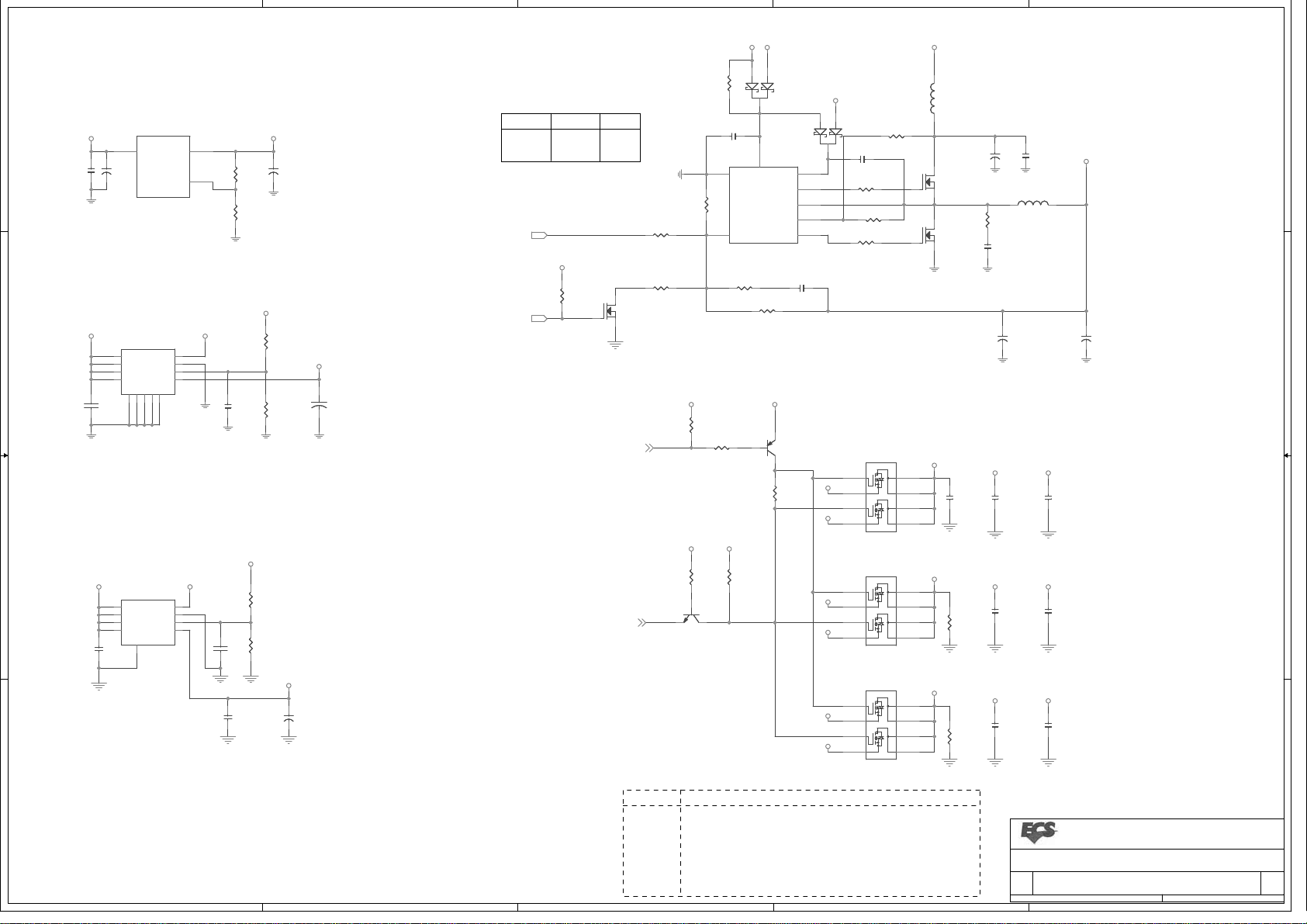

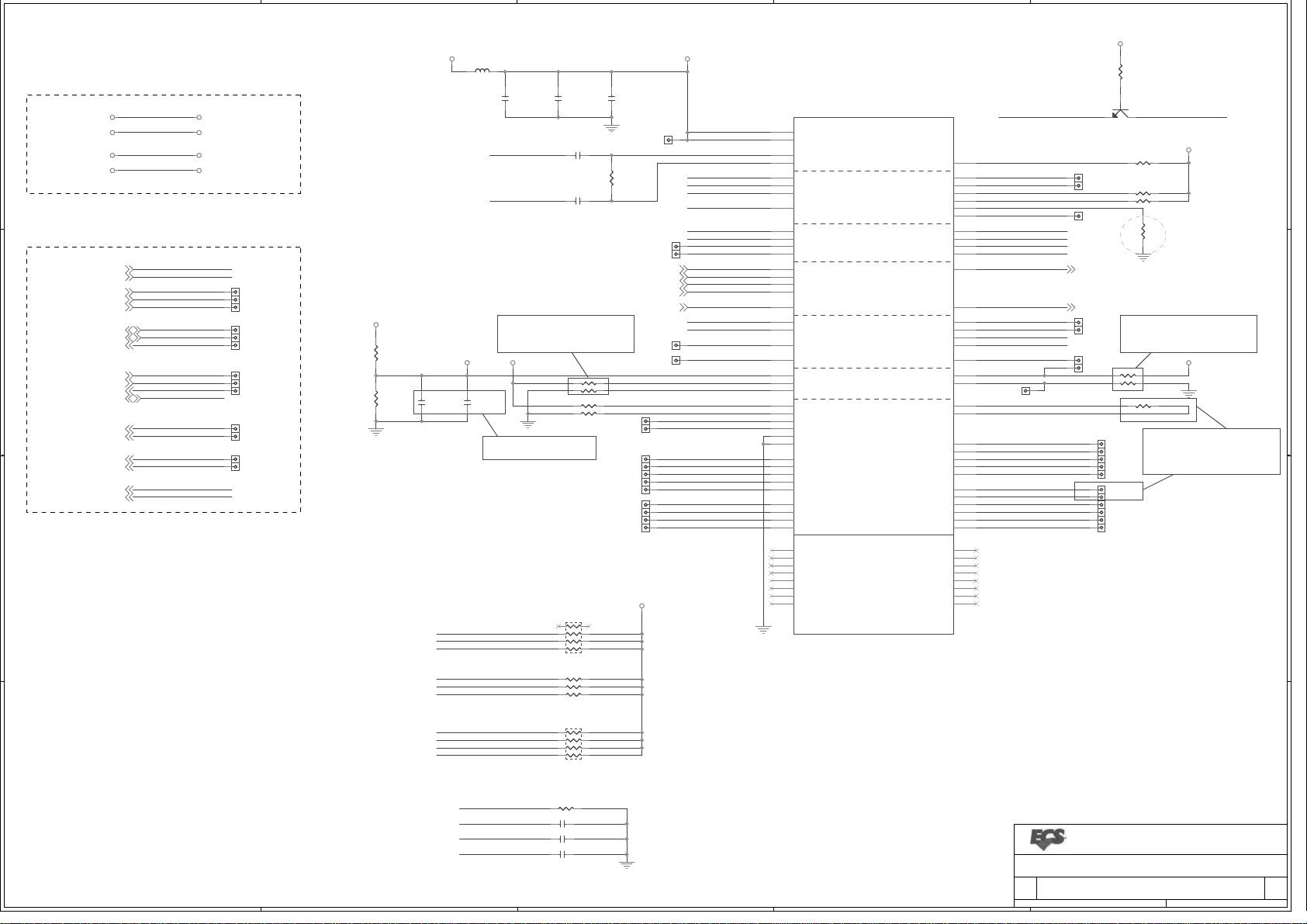

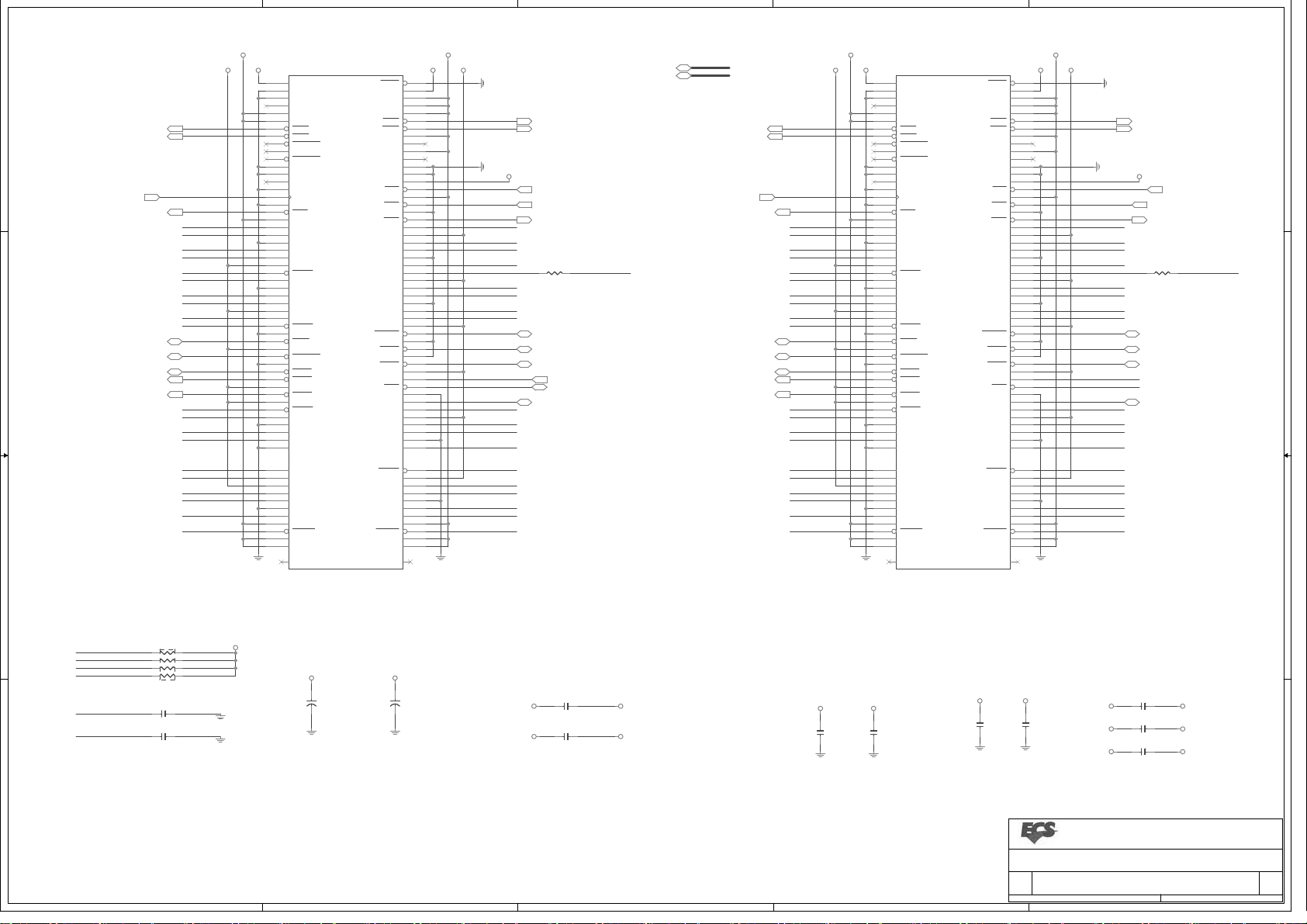

Page 4

5

4

3

2

1

0-04

12

B

CPU_COREFB-9

PG_VCORE23

CPU_VDDNB_FB-9

CPU_VDDNB_FB9

Rb

NC

MC51

MC51

1U-06

1U-06

Rc

R331 75K-04R331 75K-04

Rd

CPU_SVC9

CPU_SVD9

CPU_PVEN9

VCC3

CPU_VDDNB

I_VDDNB6

Offset

Rc

75K-04

75K-04

VCC3

12

R345

R345

10K-04

10K-04

C362 1U-16V-08C362 1U-16V-08

R328 15K-1-04-OR328 15K-1-04-O

R334 51K-04R334 51K-04

ADJ1

R337 36K-1-04R337 36K-1-04

TP5TP5

1

TP6TP6

1

TP7TP7

1

R344 4.7K-04R344 4.7K-04

EN_8855

VRM_PWROK

R358 100-04R358 100-04

Rd Re

36K-1-04

12K-1-04

VRM_PWROK

CPU_COREFB-

A5VCC

H_VID5

H_VID4

H_VID0

ɴ9 ɴ,5

Rf

1K-04

30K-1-04NC6.2K-04

C356 .1U-04C356 .1U-04

R323 100-04R323 100-04

PWM1

PWM1

RT8855PQV

RT8855PQV

49

24

5VCC

10

OFS

2

RT

14

IMAX

46

VID[5]

45

VID[4]

44

VID[3]/SVC

43

VID[2]/SVD

42

VID[1]/PVI

41

VID[0]/VFIXEN

47

VDDPWRGD

48

ENABLE

R356 1K-04R356 1K-04

C376 .01U-04-OC376 .01U-04-O

3

GND

FBRTN

PWROK

1

C371

C371

33P-04

33P-04

15K-1-04

15K-1-04

R319 220-1-04R319 220-1-04

T_ADJ ADJ

R324 330-1-04R324 330-1-04

12

9

11

FB

ADJ

COMP

RT8855

RT8855

COMP_NB6FB_NB

FBRTN_NB

IMAX_NB

4

13

R352 36K-1-04R352 36K-1-04

R351 100-04R351 100-04

R355

R355

4.7K-04

4.7K-04

C375

C375

.01U-04

.01U-04

C352 100P-04C352 100P-04

R315

R315

31

12VCC

Ca

GND

GND

5

C354

C354

6800P-04

6800P-04

R320 2.2-06R320 2.2-06

C357

C357

1U-16V-08

1U-16V-08

UG1

34

35

UG[1]

BOOT[1]

CSN_NB8CSP_NB

7

3

1

2

C359

C359

.1U-16VX7-04

.1U-16VX7-04

R325

R325

0-06

0-06

PHASE1

LG1

32

27

33

LG[1]

BOOT[2]

PHASE[1]

12VCC_NB

UG_NB37BOOT_NB

40

36

NB_UG

R354 1K-1-04R354 1K-1-04

C374 1U-16VX-06C374 1U-16VX-06

R359 220-1-04R359 220-1-04

C353 1000P-04C353 1000P-04

R316 1.5K-04R316 1.5K-04

D18

D18

BAT54A-S

BAT54A-S

C360

C360

.1U-16VX7-04

.1U-16VX7-04

R326

R326

0-06

0-06

PHASE2

UG2

28

29

UG[2]

PHASE[2]

PWM3

PWM4

ISP[1]

ISN[1]

ISP[2]

ISN[2]

ISP[3]

ISN[3]

ISP[4]

ISN[4]

ENPS

PHASE_NB

LG_NB

38

39

NB_LG

NB_PHASE

R350

R350

0-06

0-06

C370

C370

.1U-16VX7-04

.1U-16VX7-04

NB_DPHASE

NB_ISN

090831 V1.0

ɴ9 ɴ,5

LG[2]

1

2

C380

C380

.1U-04

.1U-04

30

26

25

16

15

18

17

20

19

22

21

23

Rf

D19

D19

BAT54A-S

BAT54A-S

ޏ

OCP

ೠྒྷೣംᠲ

CPU_COREFB+

R317 100-04R317 100-04

LG2

PWM3

R341

R341

1K-04

1K-04

Re

C381

C381

100P-04-O

100P-04-O

R366 6.2K-04-OR366 6.2K-04-O

3

R353 2.2-06R353 2.2-06

C372

C372

1U-16V-08

1U-16V-08

Location of Vcore

A5VCC

CPU_COREFB+ 9

VCORE

I_VCORE 6

+12V_4P

2 1

L7 RCK-0.9UDL7 RCK-0.9UD

RT2

RT2

NTC-10K-1-06

NTC-10K-1-06

R330 1K-1-04R330 1K-1-04

C350 1U-16VX-06C350 1U-16VX-06

R332 3K-04-OR332 3K-04-O

R336 470-1-04R336 470-1-04

R338 1K-1-04R338 1K-1-04

C351 1U-16VX-06C351 1U-16VX-06

R339 3K-04-OR339 3K-04-O

R340 470-1-04R340 470-1-04

R342 1K-1-04R342 1K-1-04

C367 1U-16VX-06C367 1U-16VX-06

R346 3K-04-OR346 3K-04-O

R347 470-1-04R347 470-1-04

+12V_4P

ADJT_ADJ

+12V_MOS+12V_4P

DPHASE1

ISN1

C363

C363

.1U-04

.1U-04

DPHASE2

ISN2

C365

C365

.1U-04

.1U-04

DPHASE3

ISN3

C368

C368

.1U-04

.1U-04

UG1

PHASE1

LG1

UG2

PHASE2

LG2

NB_UG

NB_PHASE

NB_LG

UG3

PHASE3

LG3

R318 0-06R318 0-06

R322 0-06R322 0-06

R329 0-06R329 0-06

R333 0-06R333 0-06

R343 0-06R343 0-06

R349 0-06R349 0-06

R357 0-06R357 0-06

R361 0-06R361 0-06

MN4

MN4

MN252-9MS

MN252-9MS

G

G

MN5

MN5

MN252-9MS

MN252-9MS

G

G

MN6

MN6

MN252-9MS

MN252-9MS

G

G

MN27

MN27

MN252-9MS

MN252-9MS

G

G

+12V_MOS

DS

DS

MN8

MN8

MN252-6MS

MN252-6MS

+12V_MOS

DS

DS

MN9

MN9

MN252-6MS

MN252-6MS

+12V_MOS

DS

DS

MN7

MN7

MN252-6MS

MN252-6MS

+12V_MOS

DS

DS

MN28

MN28

MN252-6MS

MN252-6MS

C355

C355

10U-16V-08

10U-16V-08

C361

C361

10U-16V-08

10U-16V-08

C366

C366

10U-16V-08

10U-16V-08

C373

C373

10U-16V-08

10U-16V-08

12

EC23

EC23

270U-16D-OS

270U-16D-OS

change to OS-CON.

L8 PIND-0.6UDL8 PIND-0.6UD

R321

R321

1-08

1-08

C358

C358

.01U-04

.01U-04

12

EC24

EC24

270U-16D-OS

270U-16D-OS

L9 PIND-0.6UDL9 PIND-0.6UD

R335

R335

1-08

1-08

C364

C364

.01U-04

.01U-04

12

EC25

EC25

270U-16D-OS

270U-16D-OS

L10 PIND-0.6UDL10 PIND-0.6UD

R348

R348

1-08

1-08

C369

C369

.01U-04

.01U-04

12

EC27

EC27

270U-16D-OS-O

270U-16D-OS-O

L18 PIND-0.6UDL18 PIND-0.6UD

R360

R360

1-08

1-08

1 2

C378

C378

.01U-04

.01U-04

NB_DPHASE

SU5

SU5

Short PAD

Short PAD

1 2

DPHASE1

SU6

SU6

Short PAD

Short PAD

1 2

SU7

SU7

Short PAD

Short PAD

1 2

DPHASE3 DPHASE2

SU8

SU8

Short PAD

Short PAD

21

SU9

SU9

Short PAD

Short PAD

1 2

ISN1

21

SU10

SU10

Short PAD

Short PAD

1 2

ISN2ISN3

21

SU11

SU11

Short PAD

Short PAD

1 2

21

SU12

SU12

Short PAD

Short PAD

1 2

NB_ISN

12

EC40

EC40

820U-2.5D-OS

820U-2.5D-OS

12

EC36

EC36

820U-2.5D-OS

820U-2.5D-OS

12

EC69

EC69

820U-2.5D-OS-O

820U-2.5D-OS-O

12

EC38

EC38

820U-2.5D-OS

820U-2.5D-OS

12

EC37

EC37

820U-2.5D-OS

820U-2.5D-OS

12

EC35

EC35

820U-2.5D-OS

820U-2.5D-OS

12

EC68

EC68

820U-2.5D-OS

820U-2.5D-OS

VCORE

CPU_VDDNB

BOM Difference

Ra

SB_CPUPWRGD9,18

Ra

Rb

Ca

RT8855 NC

RT8861

ADJ1ADJ

ADJ1

0-04

1.2VSB

R238

R238

4.7K-04

4.7K-04

E C

Q18 2N3904-SQ18 2N3904-S

Location

RT8855

RT8861

D D

C C

R32 0-04-OR32 0-04-O

R33 0-04R33 0-04

B B

+12V_4P

12

R362

R362

10K-04

10K-04

A A

EN_VCORE23

5

12

R365

R365

2.7K-04

2.7K-04

12

EN_8855EN_VCORE

MC56

MC56

1U-06-O

1U-06-O

4

+12V_4P

D20

D20

3

BAT54A-S

BAT54A-S

R364

R364

2.2-06

2.2-06

C379 1U-16V-08C379 1U-16V-08

1

C377 .1U-16VX7-04C377 .1U-16VX7-04

2

PWM3

PWM2

PWM2

1

BST

4

VCC

2

IN

3

NC

RT9619APSS

RT9619APSS

R363 0-06R363 0-06

DRVH

SW

DRVL

PGND

UG3

8

PHASE3

7

LG3

5

6

MOS_HK

MOS_HK

Title

Title

20-120-011930

20-120-011930

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Power (CPU Vcore RT8855)

Power (CPU Vcore RT8855)

Power (CPU Vcore RT8855)

A785GM-M7

A785GM-M7

A785GM-M7

1

4

4

4

of

33Thursday, January 07, 2010

of

33Thursday, January 07, 2010

of

33Thursday, January 07, 2010

2.0

2.0

2.0

Page 5

5

4

3

2

1

+12V

5VSB

1

2

D15

3

5

VCC

COMP/OCSET

R251

R251

1 2

ER65 1K-1-04ER65 1K-1-04

B

12

R250

R250

4.7K-04

4.7K-04

D15

BAT54C-S

BAT54C-S

BOOT

UGATE

PHASE

LGATE

5VSB

EC

DUALSW_P

12

D14

D14

BAT54C-S

BAT54C-S

U14

U14

1

2

8

7

4

C332

C332

4700P-04-O

4700P-04-O

Q13

Q13

2N3906-S

2N3906-S

R272

R272

10K-04

10K-04

5VSB

1

2

3

.1U-16VX7-04

.1U-16VX7-04

R235

R235

1 2

0-06

0-06

DIMM_PHASE

R244 22K-1-04R244 22K-1-04

R234

R234

1 2

0-06

0-06

Rdson =16mȍ , ocp=30A

Iocp=(40uA*Rocset-0.4) / Rdson of Lowside mos

5V_DUAL

For DIMM PWM

G2

G2

G2

4

5VSB

5VSB

5VSB

S2

S2

S2

3

G1

G1

G1

2

VCC

S1

S1

S1

1

AO4609-S

AO4609-S

For USB connector

G2

G2

G2

4

S2

S2

S2

3

G1

G1

G1

2

VCC

S1

S1

S1

1

AO4609-S

AO4609-S

For USB Header

G2

G2

G2

4

S2

S2

S2

3

G1

G1

G1

2

VCC

S1

S1

S1

1

AO4609-S

AO4609-S

R241

R241

1-06-O

1-06-O

1 2

ADJ

3VSB

O

A

12

12

ER36

ER36

180-1-04

180-1-04

ER37

ER37

300-1-04

300-1-04

3VSB

12

EC32

EC32

100U-16DE

100U-16DE

D D

MC19

MC19

1U-06-O

1U-06-O

5VSB

12

EC41

EC41

100U-16DE

100U-16DE

U9 ADJ1086-SU9 ADJ1086-S

INIOUT

Vo=1.25(1+Rb/Rt)

SIO_GP55 V_DIMM

V_DIMM voltage :1.6V----2.1V

AMS1086(SOT223)=1.5A

SIO_GP46

10

01

GP5523

00

11

1.6V

1.8V

1.9V

2.1V

1 2

ER64 4.02K-1-04ER64 4.02K-1-04

ER66

ER66

1K-1-04

1K-1-04

BC47

BC47

.1U-16VX7-04

.1U-16VX7-04

3

12

6

GND

FB

RT9214PS-S

RT9214PS-S

5VSB

12

R264

R264

4.7K-04

4.7K-04

G

ATX_PWRGD23,27

2 1

DDRREF

BC50

BC50

12

.1U-04-O

.1U-04-O

12

BC49

BC49

.1U-04-O

.1U-04-O

V_DIMM

MC64

MC64

10U-08

10U-08

3VSB

ER61

ER61

10K-1-04

10K-1-04

1 2

ER60

ER60

10K-1-04

10K-1-04

1 2

12

ER52

ER52

6.98K-1-04

6.98K-1-04

12

ER53

ER53

4.02K-1-04

4.02K-1-04

DDR_VTT

1.2VSB

+

+

12

EC56

EC56

1000U-6V3LD8H11E

1000U-6V3LD8H11E

EC48

EC48

100U-16DE

100U-16DE

GP4623

1.2VSB

3VSB 3VSB

MC41

MC41

12

3VSB

12

U10 9173P-SU10 9173P-S

8

Vcntl

7

Vcntl

6

REFEN

Vcntl

5

Vcntl

G9G10G11G12G

U15 9173DPSP-SU15 9173DPSP-S

8

Vcntl

7

Vcntl

6

REFEN

Vcntl

5

Vcntl

G

9

1

VIN

2

GND

3

4

VOUT

13

DDRVTT

V_DIMM

1

VIN

2

GND

3

4

VOUT

C C

MC30

MC30

1U-06-O

1U-06-O

B B

1U-06

1U-06

ER69 2.67K-1-04ER69 2.67K-1-04

DS

MN19

MN19

2N7002-S

2N7002-S

-SUSC_S523

1 2

R270

R270

10K-04

10K-04

E C

Q14 2N3904-SQ14 2N3904-S

5VSB

12

R227

R227

4.7K-04

4.7K-04

R222 10K-04R222 10K-04

3VSB +12V

1 2

B

1 2

1K-04-O

1K-04-O

1 2

DUALSW_N

C310

C310

U6

U6

U7

U7

U8

U8

R248

R248

24K-06-O

24K-06-O

D_HG

12

D_LG

D2

D2

P

P

D2

D2

D1

D1

N

N

D1

D1

D2

D2

P

P

D2

D2

D1

D1

N

N

D1

D1

D2

D2

P

P

D2

D2

D1

D1

N

N

D1

D1

5V_DUAL

12

G

G

5V_DUAL

D2

5

D2

6

D1

7

D1

8

VCC_DUAL_R

D2

5

D2

6

D1

7

D1

8

VCC_DUAL_F

D2

5

D2

6

D1

7

D1

8

L11

L11

FB-160-D

FB-160-D

1 2

5VIN_DIMM

EC60

EC60

560U-6.3D-OS

560U-6.3D-OS

DS

MN13

MN13

MN252-20MS

MN252-20MS

DS

MN15

MN15

MN252-20MS

MN252-20MS

BC58

BC58

.1U-04-O

.1U-04-O

2 1

R35

R35

1K-04-O

1K-04-O

1 2

R261

R261

1K-04-O

1K-04-O

1 2

12

PIND1.5UD-20A

PIND1.5UD-20A

1 2

R249

R249

2.2-06

2.2-06

1 2

C337

C337

4700P-04

4700P-04

12

EC59

EC59

1000U-6V3LD8H11E

1000U-6V3LD8H11E

5VSB

BC56

BC56

.1U-04-O

.1U-04-O

2 1

5VSB

BC31

BC31

.1U-04-O

.1U-04-O

2 1

5VSB

BC57

BC57

.1U-04-O

.1U-04-O

2 1

MC54

MC54

10U-08

10U-08

L12

L12

VCC

VCC

VCC

V_DIMM

V_DIMM

1pcs DDR3@3A

@MAX=9A Δ Pulse=16A

12

EC57

EC57

1000U-6V3LD8H11E

1000U-6V3LD8H11E

C78

C78

.1U-04

.1U-04

2 1

BC30

BC30

.1U-04

.1U-04

2 1

BC55

BC55

.1U-04-O

.1U-04-O

2 1

A A

-SUSC_S5

ATX_PWRGD

DUALSW_P

DUALSW_N

5V_DUAL

VDIMM

5

4

3

S5

0

0

5VSB

0

X

X

enter S0

0

1

5VSB

12V

VCC5

V

S0

1

1

12V

12V

VCC5

V

enter S3

exit S3

1

0

0

0

5VSB

V

1

1

12V

12V

VCC5

V

enter S5

0

1

5VSB

12V

VCC5

V

2

S5

0

0

5VSB

0

0

X

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Power A(DC to DC)

Power A(DC to DC)

Power A(DC to DC)

A785GM-M7

A785GM-M7

A785GM-M7

5

5

5

of

33Thursday, January 07, 2010

of

33Thursday, January 07, 2010

of

1

33Thursday, January 07, 2010

2.0

2.0

2.0

Page 6

5

4

3

2

1

+12V

1 2

PWM3

PWM3

BOOT

UGATE

PHASE

LGATE

R269

R269

D11

D11

BAT54C-S

BAT54C-S

1-06

1-06

1

2

8

7

4

VCC

1 2

2

VCC12_EN

1

3

1 2

R273 24K-06-OR273 24K-06-O

.1U-16VX7-04BC94 .1U-16VX7-04BC94

HG_NB

1 2

R267 1-06R267 1-06

PHASE_NB

12

R245 22K-1-04R245 22K-1-04

LG_NB

12

R268 1-06R268 1-06

3VSB

D D

12

ER23

ER23

1.5K-1-04

1.5K-1-04

12

ER22

ER22

1.8K-1-04

1.8K-1-04

VREF18

+12V

R90 4.7K-04-OR90 4.7K-04-O

84

3

+

+

2

-

-

U4A

U4A

OP358-S

OP358-S

1

1000U-6V3LD8H11E

1000U-6V3LD8H11E

VCC3

12

MN3

MN3

DS

P3055LDG-S

P3055LDG-S

G

12

EC22

EC22

VCC1.8

VCC1.8

C136

C136

.1U-04-O

.1U-04-O

D7

BAV99-SD7BAV99-S

VCC3

ER67

ER67

976-1-04

976-1-04

For EMI

BC93

BC93

.1U-16VX7-04

.1U-16VX7-04

3

12

6

RT9214PS-S

RT9214PS-S

R265

R265

10-06-O

10-06-O

GND

COMP/OCSET

FB

5

VCC

VCC3

12

LL1

LL1

EC49

EC49

470U-6V3D6.3H11E

470U-6V3D6.3H11E

FB-160-D

FB-160-D

1 2

3VIN_VCCNB

12

EC53

EC53

560U-6.3D-OS

560U-6.3D-OS

DS

MN16

MN16

MN251-6MD

MN251-6MD

G

DS

MN17

MN17

1 2

MN251-6MD

MN251-6MD

G

1 2

PIND1.5UD-20A

PIND1.5UD-20A

R266

R266

2.2-06

2.2-06

BC91

BC91

4700P-04

4700P-04

MC55

MC55

10U-08

10U-08

L13

L13

VCC_NB

VCC_NB

@MAX=13A

VDDHT

VCC_SB

Rdson =15mȍ , ocp=32A

C C

EN_VCC25A23

3VSB

3VSB

21

B B

A A

C74

C74

1U-06-O

1U-06-O

1 2

1 2

C262

C262

.1U-04

.1U-04

2 1

10K-04

10K-04

1 2

R207 16.9K-04-OR207 16.9K-04-O

SMBDT3,11,17,19,24

5

ER21

ER21

3.24K-1-04

3.24K-1-04

ER24

ER24

10K-1-04

10K-1-04

uP6262ሽᙁנፖǻVoutᣂߓڕՀ:

ᙇ࠷ൕuP6262ᙁנֱٻإ,

ঞVCORE,VCC_NB֗VDIMMǻVout:

ǻVout = -Ic * RFB;

5VSB

R198

R198

1 2

+12V

5

+

+

6

-

-

Chip Address: 0x60

Address 4 Voltage Range = 77~100%VCC

U20

U20

1

VCC

2

BUS_SEL

3

GND

4

SDA

UP6262

UP6262

84

U4B

U4B

OP358-S

OP358-S

C15

C15

1000P-04-O

1000P-04-O

2 1

VCC25A

R259

R259

4.7K-04-O

4.7K-04-O

1 2

7

C13

C13

1000P-04-O

1000P-04-O

2 1

8

OUT1

7

OUT2

6

OUT3

5

SCL

OUT1..3,W/S=10/15

2 1

C39

C39

1000P-04-O

1000P-04-O

2 1

I_NBVCORE

G

C14

C14

1000P-04-O

1000P-04-O

4

VCC3

VCC3

12

MC65

MC65

10U-08-O

DS

MN10

MN10

2N7002-S

2N7002-S

VCC25A

12

EC43

EC43

100U-16DE

100U-16DE

I_VCORE 4

I_VDDNB 4

SMBCK 3,11,17,19,24

10U-08-O

Near CPU.

I_NBVCORE

EN_VCC1223

3

ɴ9 ɴ,5

1 2

ER62 499-1-04ER62 499-1-04

1 2

R118 0-04-SHR118 0-04-SH

ASIC_CPUPWRGD7,19,23

Iocp=(40uA*Rocset-0.4) / Rdson of Lowside mos

12

EC44

EC44

1000U-6V3LD8H11E

1000U-6V3LD8H11E

HW default :VCC_NB = 1.2V

5VSB

SB&NB PWRGOOD

R92

R92

4.7K-04

4.7K-04

2

1 2

1 2

1 2

R93

R93

3.6K-04

3.6K-04

R84

R84

4.7K-04

4.7K-04

ASIC_CPUPWRGD

12

EC55

EC55

1000U-6V3LD8H11E

1000U-6V3LD8H11E

C89

C89

.1U-04

.1U-04

C96

C96

.1U-04-O

.1U-04-O

SB_PWRGD 7,19,23

NB_PWRGD_1.8V 15

Title

Title

Title

Power B(DC to DC),PWR Sequence&good

Power B(DC to DC),PWR Sequence&good

Power B(DC to DC),PWR Sequence&good

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

12

EC47

EC47

1000U-6V3LD8H11E

1000U-6V3LD8H11E

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

A785GM-M7

A785GM-M7

A785GM-M7

1

2.0

2.0

633Thursday, January 07, 2010

633Thursday, January 07, 2010

633Thursday, January 07, 2010

2.0

of

of

of

Page 7

A

B

C

D

E

HyperTransport

CPUA

HT_CLKIN_H[0..1]13

HT_CLKIN_L[0..1]13

4 4

3 3

2 2

1 1

HT_CLKOUT_H[0..1]13

HT_CLKOUT_L[0..1]13

HT_CTLOUT_H[0..1]13

HT_CTLOUT_L[0..1]13

HT_CADIN_H[0..15]13

HT_CADIN_L[0..15]13

HT_CADOUT_H[0..15]13

HT_CADOUT_L[0..15]13

V_DIMM

VCC1.8

IMC_TMS

HT_CTLIN_H[0..1]13

HT_CTLIN_L[0..1]13

SB_PWRGD6,19,23

CPU_DBREQ_9

CPU_DBRDY9

CPU_TCK9

CPU_TMS9

CPU_TDI9

CPU_TRST-9

CPU_TDO9

IMC_TDI19

IMC_TRST_19

IMC_TDO19

IMC_TMS19

LDT_RST-9,15,18

IMC_CRST_19

IMC_DBREQ_19

IMC_DBRDY19

IMC_TCK19

HT_CLKIN_H[0..1]

HT_CLKIN_L[0..1]

HT_CLKOUT_H[0..1]

HT_CLKOUT_L[0..1]

HT_CTLIN_H[0..1]

HT_CTLIN_L[0..1]

HT_CTLOUT_H[0..1]

HT_CTLOUT_L[0..1]

HT_CADIN_H[0..15]

HT_CADIN_L[0..15]

HT_CADOUT_H[0..15]

HT_CADOUT_L[0..15]

NB_PWRGD

CPU_DBREQ_

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRSTCPU_TDO

IMC_TDI

IMC_TRST_

IMC_TDO

IMC_TMS

LDT_RSTIMC_CRST_

IMC_DBREQ_

IMC_DBRDY

IMC_TCK

JT_GATE

12

M_R31

M_R31

10K-04

10K-04

B

E C

V_DIMM

VCC1.8

1.5V

M_QN6 2N3904-SM_QN6 2N3904-S

HT_CLKIN_H1

HT_CLKIN_L1

HT_CLKIN_H0

HT_CLKIN_L0

HT_CTLIN_H1

HT_CTLIN_L1

HT_CTLIN_H0

HT_CTLIN_L0

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

M_R35

M_R35

10K-04

10K-04

HT_CADIN_H0

HT_CADIN_L0

IMC_TDI

CPU_DBREQ_

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRSTCPU_TDO

M_QN9 2N3904-SM_QN9 2N3904-S

VCC3VCC3

V_DIMM

13

RJ7(1-2)

RJ7(1-2)

2

JT_GATE

0-04

0-04

VCC1.8

JT_GATE

12

B

E C

M_QN8 2N3904-SM_QN8 2N3904-S

IMC_TDO

JT_GATE

12

M_R33

M_R33

10K-04

10K-04

B

E C

M_QN7 2N3904-SM_QN7 2N3904-S

IMC_TRST_

CPUA

N6

L0_CLKIN_H1

P6

L0_CLKIN_L1

N3

L0_CLKIN_H0

N2

L0_CLKIN_L0

V4

L0_CTLIN_H1

V5

L0_CTLIN_L1

U1

L0_CTLIN_H0

V1

L0_CTLIN_L0

U6

L0_CADIN_H15

V6

L0_CADIN_L15

T4

L0_CADIN_H14

T5

L0_CADIN_L14

R6

L0_CADIN_H13

T6

L0_CADIN_L13

P4

L0_CADIN_H12

P5

L0_CADIN_L12

M4

L0_CADIN_H11

M5

L0_CADIN_L11

L6

L0_CADIN_H10

M6

L0_CADIN_L10

K4

L0_CADIN_H9

K5

L0_CADIN_L9

J6

L0_CADIN_H8

K6

L0_CADIN_L8

U3

L0_CADIN_H7

U2

L0_CADIN_L7

R1

L0_CADIN_H6

T1

L0_CADIN_L6

R3

L0_CADIN_H5

R2

L0_CADIN_L5

N1

L0_CADIN_H4

P1

L0_CADIN_L4

L1

L0_CADIN_H3

M1

L0_CADIN_L3

L3

L0_CADIN_H2

L2

L0_CADIN_L2

J1

L0_CADIN_H1

K1

L0_CADIN_L1

J3

L0_CADIN_H0

J2

L0_CADIN_L0

V_DIMM

M_RN3

M_RN3

4.7K-8P4R-06-O

4.7K-8P4R-06-O

JT_GATE

12

M_R37

M_R37

10K-04

10K-04

B

EC

1 2

3 4

5 6

NB_PWRGD

1 2

3 4

5 6

7 8

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

HT LINK

HT LINK

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

ZIF-941P-S

ZIF-941P-S

M_R16

M_R16

0-04-O

0-04-O

1 2

M_RN2

M_RN2

4.7K-8P4R-06

4.7K-8P4R-06

7 8

JT_GATE

12

M_R22

M_R22

10K-04

10K-04

B

EC

M_QN3 2N3904-SM_QN3 2N3904-S

HT_CLKOUT_H1

AD5

HT_CLKOUT_L1

AD4

HT_CLKOUT_H0

AD1

HT_CLKOUT_L0

AC1

HT_CTLOUT_H1

Y6

HT_CTLOUT_L1

W6

HT_CTLOUT_H0

W2

HT_CTLOUT_L0

W3

HT_CADOUT_H15

Y5

HT_CADOUT_L15

Y4

HT_CADOUT_H14

AB6

HT_CADOUT_L14

AA6

HT_CADOUT_H13

AB5

HT_CADOUT_L13

AB4

HT_CADOUT_H12

AD6

HT_CADOUT_L12

AC6

HT_CADOUT_H11

AF6

HT_CADOUT_L11

AE6

HT_CADOUT_H10

AF5

HT_CADOUT_L10

AF4

HT_CADOUT_H9

AH6

HT_CADOUT_L9

AG6

HT_CADOUT_H8

AH5

HT_CADOUT_L8

AH4

HT_CADOUT_H7

Y1

HT_CADOUT_L7

W1

HT_CADOUT_H6

AA2

HT_CADOUT_L6

AA3

HT_CADOUT_H5

AB1

HT_CADOUT_L5

AA1

HT_CADOUT_H4

AC2

HT_CADOUT_L4

AC3

HT_CADOUT_H3

AE2

HT_CADOUT_L3

AE3

HT_CADOUT_H2

AF1

HT_CADOUT_L2

AE1

HT_CADOUT_H1

AG2

HT_CADOUT_L1

AG3

HT_CADOUT_H0

AH1

HT_CADOUT_L0

AG1

Over Clocking

V_DIMM

HDT Connector

1

3

5

7

9

11

13

15

17

19

21

23

KEY

KEY

Use buffered reset

IMC_DBREQ_

ASP-68200-07-O

ASP-68200-07-O

M_R13 0-04-OM_R13 0-04-O

E C

M_QN4 2N3904-SM_QN4 2N3904-S

SJ1

SJ1

1 2

JT_GATE

12

B

M_R26

M_R26

10K-04

10K-04

2

4

6

8

10

12

14

16

18

20

22

24

26

IMC_DBRDY

M_QN5 2N3904-SM_QN5 2N3904-S

Please use 1mm pad size,

place all ELT test pads

on bottom side only.

A1

AL1

CPU(104) 30-430-020513

CPU(104) 30-430-020513

VCC1.8

VCC3

12

12

M_R14

M_R14

M_R30

M_R30

10K-04

10K-04

4.7K-04

4.7K-04

B

E C

M_QN2 2N3904-SM_QN2 2N3904-S

JT_GATE

12

M_R27

M_R27

10K-04

10K-04

B

EC

AM3

Top View

CPU-R1

CPU-R1

LDT_RST-

IMC_CRST_

IMC_TCK

A31

AL31

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

CPU HT & DEBUG

CPU HT & DEBUG

CPU HT & DEBUG

A785GM-M7

A785GM-M7

A785GM-M7

E

2.0

2.0

7

7

7

2.0

of

33Thursday, January 07, 2010

of

33Thursday, January 07, 2010

of

33Thursday, January 07, 2010

Page 8

A

CPU_VDDIO_SUSV_DIMM

1.5V

4 4

MEM_MA_DQS_H[8..0]11

MEM_MA_DQS_L[8..0]11

MEM_MB_DQS_H[8..0]11

MEM_MB_DQS_L[8..0]11

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_L[8..0]

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_L[8..0]

B

C

D

E

CPU Memory

DDR3 Memory Interface A DDR3 Memory Interface B

CPUC

AJ19

AK19

AL19

AL18

AE30

AC31

AF31

AD29

AE29

AB31

AG31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

U31

U30

W29

W28

Y31

Y30

V31

W31

A18

A19

C19

D19

B19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

CPUC

MB_CLK_H7

MB_CLK_L7

MB_CLK_H6

MB_CLK_L6

MB_CLK_H5

MB_CLK_L5

MB_CLK_H4

MB_CLK_L4

MB_CLK_H3

MB_CLK_L3

MB_CLK_H2

MB_CLK_L2

MB_CLK_H1

MB_CLK_L1

MB_CLK_H0

MB_CLK_L0

MB0_CS_L1

MB0_CS_L0

MB0_ODT1

MB0_ODT0

MB1_CS_L1

MB1_CS_L0

MB1_ODT1

MB1_ODT0

MB_RESET_L

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MEM CHB

MEM CHB

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

ZIF-941P-S

ZIF-941P-S

MEM_MB_DATA63

AH13

MEM_MB_DATA62

AL13

MEM_MB_DATA61

AL15

MEM_MB_DATA60

AJ15

MEM_MB_DATA59

AF13

MEM_MB_DATA58

AG13

MEM_MB_DATA57

AL14

MEM_MB_DATA56

AK15

MEM_MB_DATA55

AL16

MEM_MB_DATA54

AL17

MEM_MB_DATA53

AK21

MEM_MB_DATA52

AL21

MEM_MB_DATA51

AH15

MEM_MB_DATA50

AJ16

MEM_MB_DATA49

AH19

MEM_MB_DATA48

AL20

MEM_MB_DATA47

AJ22

MEM_MB_DATA46

AL22

MEM_MB_DATA45

AL24

MEM_MB_DATA44

AK25

MEM_MB_DATA43

AJ21

MEM_MB_DATA42

AH21

MEM_MB_DATA41

AH23

MEM_MB_DATA40

AJ24

MEM_MB_DATA39

AL27

MEM_MB_DATA38

AK27

MEM_MB_DATA37

AH31

MEM_MB_DATA36

AG30

MEM_MB_DATA35

AL25

MEM_MB_DATA34

AL26

MEM_MB_DATA33

AJ30

MEM_MB_DATA32

AJ31

MEM_MB_DATA31

E31

MEM_MB_DATA30

E30

MEM_MB_DATA29

B27

MEM_MB_DATA28

A27

MEM_MB_DATA27

F29

MEM_MB_DATA26

F31

MEM_MB_DATA25

A29

MEM_MB_DATA24

A28

MEM_MB_DATA23

A25

MEM_MB_DATA22

A24

MEM_MB_DATA21

C22

MEM_MB_DATA20

D21

MEM_MB_DATA19

A26

MEM_MB_DATA18

B25

MEM_MB_DATA17

B23

MEM_MB_DATA16

A22

MEM_MB_DATA15

B21

MEM_MB_DATA14

A20

MEM_MB_DATA13

C16

MEM_MB_DATA12

D15

MEM_MB_DATA11

C21

MEM_MB_DATA10

A21

MEM_MB_DATA9

A17

MEM_MB_DATA8

A16

MEM_MB_DATA7

B15

MEM_MB_DATA6

A14

MEM_MB_DATA5

E13

MEM_MB_DATA4

F13

MEM_MB_DATA3

C15

MEM_MB_DATA2

A15

MEM_MB_DATA1

A13

MEM_MB_DATA0

D13

MEM_MB_DQS_H8

J31

MEM_MB_DQS_L8

J30

J29

MEM_MB_CHECK7

K29

MEM_MB_CHECK6

K31

MEM_MB_CHECK5

G30

MEM_MB_CHECK4

G29

MEM_MB_CHECK3

L29

MEM_MB_CHECK2

L28

MEM_MB_CHECK1

H31

MEM_MB_CHECK0

G31

V29

EVENT pins are for future AM3r2

1 2

M_R42 300-04M_R42 300-04

MEM_MB_DM8 11

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

MEM_MB_EVENT_L 11

CPU_VDDIO_SUSCPU_VDDIO_SUS

CPUB

CPUB

M_STP27M_STP27

M_STP25M_STP25

M_STP24M_STP24

M_STP23M_STP23

MEM_MA0_CLK0_P11

MEM_MA0_CLK0_N11 MEM_MB0_CLK0_N11

MEM_MA0_CLK1_P11

MEM_MA0_CLK1_N11

M_STP22M_STP22

M_STP26M_STP26

M_STP28M_STP28

M_STP29M_STP29

MEM_MA0_CS_L111

3 3

2 2

MEM_MA0_CS_L011

MEM_MA0_ODT111 MEM_MB0_ODT111

MEM_MA0_ODT011

MEM_MA_RESET-11 MEM_MB_RESET-11

MEM_MA_CAS-11

MEM_MA_WE-11

MEM_MA_RAS-11

MEM_MA_BANK211

MEM_MA_BANK111

MEM_MA_BANK011

MEM_MA_CKE011

MEM_MA_ADD[15..0]11

MEM_MA_DM[7..0]11

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6 MEM_MB_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

AE20

AE19

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

U27

U26

V27

W27

W26

W25

U24

V24

G19

H19

G20

G21

E20

N25

Y27

L27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

MA_CLK_H7

MA_CLK_L7

MA_CLK_H6

MA_CLK_L6

MA_CLK_H5

MA_CLK_L5

MA_CLK_H4

MA_CLK_L4

MA_CLK_H3

MA_CLK_L3

MA_CLK_H2

MA_CLK_L2

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA1_ODT1

MA1_ODT0

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MEM CHA

MEM CHA

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

ZIF-941P-S

ZIF-941P-S

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

J25

MEM_MA_CHECK7

K25

J26

MEM_MA_CHECK5

G28

MEM_MA_CHECK4

G27

MEM_MA_CHECK3

L24

MEM_MA_CHECK2

K27

MEM_MA_CHECK1MEM_MA_DQS_H0

H29

MEM_MA_CHECK0

H27

W30

EVENT pins are for future AM3r2

1 2

M_R41 300-04M_R41 300-04

MEM_MA_DATA[63..0] 11 MEM_MB_DATA[63..0] 11

MEM_MB_ADD[15..0]11

MEM_MA_DM8 11

MEM_MA_CHECK[7..0] 11 MEM_MB_CHECK[7..0] 11

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

MEM_MA_EVENT_L 11

STP14STP14

STP15STP15

STP16STP16

STP19STP19

MEM_MB0_CLK0_P11

MEM_MB0_CLK1_P11

MEM_MB0_CLK1_N11

STP10STP10

STP11STP11

STP12STP12

STP13STP13

MEM_MB0_CS_L111

MEM_MB0_CS_L011

MEM_MB0_ODT011

MEM_MB_CAS-11

MEM_MB_WE-11

MEM_MB_RAS-11

MEM_MB_BANK211

MEM_MB_BANK111

MEM_MB_BANK011

MEM_MB_CKE111MEM_MA_CKE111

MEM_MB_CKE011

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3MEM_MA_CHECK6

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM[7..0]11

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

1 1

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

Elitegroup Computer Systems

AM3 CPU MEMORY

AM3 CPU MEMORY

AM3 CPU MEMORY

A785GM-M7

A785GM-M7

A785GM-M7

E

8

8

8

of

of

of

2.0

2.0

2.0

33Thursday, January 07, 2010

33Thursday, January 07, 2010

33Thursday, January 07, 2010

Page 9

A

B

C

D

E

VCC25A

M_FB1

M_FB1

FB120-08

FB120-08

1 2

Layout: Place as close as

4 4

3 3

2 2

VCC25A VCC25A

VCC3 VCC3

V_DIMM CPU_VDDIO_SUS

VDDHT

CPUCLK3

CPUCLK-3

SB_CPUPWRGD4,18

LDT_STOP-15,18

LDT_RST-7,15,18

CPU_PVEN4

CPU_SVD4

CPU_SVC4

CPU_THERMDC15,23

CPU_THERMDA23

-CPU_THERMTRIP19

-CPU_PROCHOT18

CPU_COREFB+4

CPU_COREFB-4

CPU_VDDNB_FB4

CPU_VDDNB_FB-4

SB_CPU_SIC19

SB_CPU_SID19

1.5V

1.2V

CPU_CLKP

CPU_CLKN

CPU_PWRGD

LDT_STOPLDT_RST-

CPU_PVEN

CPU_SVD

CPU_SVC CPU_VDDNB_FB_L

CPU_THERMDC

CPU_THERMDA

CPU_THERMTRIP_L

CPU_PROCHOT_L_15

CPU_VDD_FB_H

CPU_VDD_FB_L

CPU_VDDNB_FB_H

CPU_VDDNB_FB_L

CPU_SIC

CPU_SID

CPU_VDDHT

STP9STP9

M_TP2M_TP2

M_TP14M_TP14

M_TP8M_TP8

M_TP37M_TP37

M_TP38M_TP38

M_STP20M_STP20

M_STP18M_STP18

TP9TP9

M_STP1M_STP1

M_STP2M_STP2

M_STP5M_STP5

possible to CPU socket.

a,Rshunt near CPU pin<600mil

b,Cseries as a pair within 25mil

c,Cseries to CPU pin trace length<1250mil

d,12:4:6:4:12(1080 for 93ohm)

CPU_VDDIO_SUS

12

M_R18

M_R18

15-1-06

12

15-1-06

0.25W

M_R17

M_R17

15-1-06

15-1-06

CPU_M_VREF_SUS CPU_VDDIO_SUS

M_C19

M_C19

M_C18

M_C18

1000P-04

1000P-04

.1U-04

.1U-04

2 1

2 1

12mil(width):20mil(spacing)

LDT_RSTLDT_STOPCPU_PWRGD

a,20mil(width):20mil(spacing)

b,reference to GND

M_C21

M_C21

10U-08

10U-08

2 1

CPU_CLKP

CPU_CLKN CPU_SVD

Layout: Keep trace to resistors

less than 1" from CPU pins.

Layout: Place within 500

mils of the CPU socket.

M_C20

M_C20

.22U-06

.22U-06

21

21

1 2

1 2

1 2

1 2

2

4

6

8

2 1

12

M_TP19M_TP19

M_TP18M_TP18

M_STP8M_STP8

M_STP13M_STP13

M_STP19M_STP19

M_STP4M_STP4

M_STP12M_STP12

M_STP9M_STP9

M_STP7M_STP7

M_STP14M_STP14

M_STP10M_STP10

2 1

M_C14 3900P-04M_C14 3900P-04

M_C16 3900P-04M_C16 3900P-04

M_R19 39.2-1-04M_R19 39.2-1-04

M_R21 39.2-1-04M_R21 39.2-1-04

M_R11 511-1-04M_R11 511-1-04

M_R12 511-1-04M_R12 511-1-04

M_RN4 300-8P4R-06M_RN4 300-8P4R-06

1

3

5

7

CPU_VDDA_RUN

2.5V@0.25A

M_C22

M_C22

3300P-04

3300P-04

M_TP25M_TP25

M_R10

M_R10

169-1-04

169-1-04

M_TP13M_TP13

M_TP36M_TP36

CPU_TDI7

CPU_TRST-7

CPU_TCK7

CPU_TMS7

CPU_DBREQ_7

TP11TP11

M_STP21M_STP21

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_H_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST7_ANALOG_T

CPU_TEST6_DIECRACKMON

CPU_TEST3_GATE0

CPU_TEST2_DRAIN0

CPU_VDDIO_SUS

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_PWRGD

LDT_STOPLDT_RST-

CPU_PRESENT_L_15

CPU_SIC

CPU_SID

CPU_SA0

CPU_ALERT_

CPU_VDD_FB_H

CPU_VDD_FB_L

CPU_VDDIO_PWRGD

CPU_VTT_SUS_SENSE

CPU_M_ZN

CPU_M_ZP

C10

D10

AK6

AK4

AL10

AJ10

AH10

AH11

AJ11

AH9

AH7

C18

C20

G24

G25

H25

A8

B8

C9

D8

C7

AL3

AL6

AL4

AL9

A5

G2

G1

F3

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

E5

AJ5

AJ6

F2

L25

L26

CPUD

CPUD

VDDA_1

VDDA_2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

SA0

ALERT_L

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

M_VDDIO_PWRGD

VDDR_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST3

TEST2

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

INT. MISC.

INT. MISC.

RSVD6

RSVD7

RSVD8

MISC.

MISC.

CORE_TYPE

VID5

VID4

SVC/VID3

SVD/VID2

PVIEN/VID1

VID0

THERMDC

THERMDA

THERMTRIP_L

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

ZIF-941P-S

ZIF-941P-S

G5

D2

D1

C1

E3

E2

E1

AG9

AG8

AK7

AL7

AK10

B6

AK11

AL11

G4

G3

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

L30

L31

AD25

AE24

AE25

AJ18

AJ20

AK3

CPU_THERMTRIP_L_15 CPU_THERMTRIP_L

CPU_CORE_TYPE_L

CPU_VID5

CPU_VID4

CPU_SVC

CPU_PVEN

CPU_VID0

CPU_THERMDC

CPU_THERMDA

CPU_THERMTRIP_L_15

CPU_PROCHOT_L_15

CPU_TDO

CPU_DBRDY

CPU_VDDIO_FB_H

CPU_VDDIO_FB_L

CPU_VDDNB_FB_H

CPU_PSICPU_HTREF1CPU_M_VREF

CPU_HTREF0

STP24STP24

CPU_TEST29_H_FBCLKOUT_H

CPU_TEST29_L_FBCLKOUT_L

CPU_TEST24_SCANCLK1

CPU_TEST23_TSTUPD

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST28_H_PLLCHRZ_H

CPU_TEST28_L_PLLCHRZ_L

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN_L

CPU_TEST10_ANALOGOUT

CPU_TEST8_DIG_T

CPU_VDDIO_SUS

12

M_R15

M_R15

10K-04

10K-04

B

E C

M_QN1 2N3904-SM_QN1 2N3904-S

M_R3 1K-04M_R3 1K-04

1 2

M_TP10M_TP10

M_TP9M_TP9

M_R5 1K-04M_R5 1K-04

1 2

M_R4 1K-04M_R4 1K-04

1 2

M_TP7M_TP7

1 2

CPU_TDO 7

CPU_DBRDY 7

M_TP26M_TP26

M_TP27M_TP27

M_TP1M_TP1

M_STP30M_STP30

M_R2 44.2-1-04M_R2 44.2-1-04

M_R1 44.2-1-04M_R1 44.2-1-04

For AM3 CPU

Layout: Keep CPU_HTREF0,1

less than 1.5" from in length.

1 2

1 2

1 2

M_R20 80.6-1-04M_R20 80.6-1-04

M_TP20M_TP20

TP10TP10

M_TP22M_TP22

M_TP21M_TP21M_STP3M_STP3

M_TP16M_TP16

M_STP17M_STP17

M_STP16M_STP16

M_TP23M_TP23

M_TP15M_TP15

M_STP15M_STP15

M_STP6M_STP6

CPU_VDDIO_SUS

M_R47

M_R47

300-04

300-04

CPU_VDDHT

Layout: Route as 80 ohms diff

impedance (4/5mil).Keep trace

to resistor < 1" from CPU pins.

CPU_PRESENT_L_15

CPU_SIC

CPU_SID

CPU_TEST27_SINGLECHAIN

CPU_THERMTRIP_L_15

CPU_PROCHOT_L_15

CPU_TEST26_BURNIN_L

1 1

A

B

CPU_SA0

CPU_PWRGD

LDT_STOPLDT_RST-

M_R7 10K-04M_R7 10K-04

1 2

M_R8 10K-04M_R8 10K-04

1 2

M_R9 10K-04M_R9 10K-04

1 2

M_RN1 300-8P4R-06M_RN1 300-8P4R-06

1

2

3

4

5

6

7

8

M_R6 0-04M_R6 0-04

1 2

M_C33 180P-04M_C33 180P-04

M_C31 180P-04M_C31 180P-04

M_C32 180P-04M_C32 180P-04

21

21

21

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

C

D

Date: Sheet

AM3 CPU CONTROL&MISC

AM3 CPU CONTROL&MISC

AM3 CPU CONTROL&MISC

A785GM-M7

A785GM-M7

A785GM-M7

9

9

9

of

of

E

of

2.0

2.0

2.0

33Thursday, January 07, 2010

33Thursday, January 07, 2010

33Thursday, January 07, 2010

Page 10

A

B

C

D

E

CPU_VDD_RUN CPU_VDD_RUN

4 4

VCORE

V_DIMM

CPU_VDDNB

VDDHT

VDDHT

3 3

2 2

CPU_VDD_RUN

CPU_VDDIO_SUS

CPU_VDDNB_RUN

CPU_VDDR

CPU_VDDHT

CPUE

CPUE

B3

VDD_1

C2

VDD_2

C4

VDD_3

D3

VDD_4

D5

VDD_5

E4

VDD_6

E6

VDD_7

F5

VDD_8

F7

VDD_9

G6

VDD_10

G8

VDD_11

H7

VDD_12

H11

VDD_13

H23

VDD_14

J8

VDD_15

J12

VDD_16

J14

VDD_17

J16

VDD_18

J18

VDD_19

J20

VDD_20

J22

VDD_21

J24

VDD_22

K7

VDD_23

K9

VDD_24

K11

VDD_25

K13

VDD_26

K15

VDD_27

K17

VDD_28

K19

VDD_29

K21

VDD_30

K23

VDD_31

L4

VDD_32

L5

VDD_33

L8

VDD_34

L10

VDD_35

L12

VDD_36

L14

VDD_37

L16

VDD_38

L18

VDD_39

L20

VDD_40

L22

VDD_41

M2

VDD_42

M3

VDD_43

M7

VDD_44

M9

VDD_45

M11

VDD_46

M13

VDD_47

M15

VDD_48

M17

VDD_49

M19

VDD_50

M21

VDD_51

M23

VDD_52

N8

VDD_53

N10

VDD_54

N12

VDD_55

N14

VDD_56

N16

VDD_57

N18

VDD_58

N20

VDD_59

N22

VDD_60

P7

VDD_61

P9

VDD_62

P11

VDD_63

P13

VDD_64

P15

VDD_65

P17

VDD_66

P19

VDD_67

P21

VDD_68

P23

VDD_69

R4

VDD_70

R5

VDD_71

R8

VDD_72

R10

VDD_73

R12

VDD_74

R14

VDD_75

R16

VDD_76

R18

VDD_77

R20

VDD_78

R22

VDD_79

T2

VDD_80

T3

VDD_81

T7

VDD_82

T9

VDD_83

T11

VDD_84

T13

VDD_85

A3

VSS_1

A7

VSS_2

A9

VSS_3

A11

VSS_4

B4

VSS_5

B9

VSS_6

B11

VSS_7

B14

VSS_8

B16

VSS_9

B18

VSS_10

B20

VSS_11

B22

VSS_12

B24

VSS_13

B26

VSS_14

B28

VSS_15

B30

VSS_16

C3

VSS_17

D14

VSS_18

D16

VSS_19

D18

VSS_20

D20

VSS_21

D22

VSS_22

D24

VSS_23

D26

VSS_24

D28

VSS_25

D30

VSS_26

E11

VSS_27

F4

VSS_28

F14

VSS_29

F16

VSS_30

F18

VSS_31

F20

VSS_32

F22

VSS_33

F24

VSS_34

F26

VSS_35

F28

VSS_36

F30

VSS_37

G9

VSS_38

G11

VSS_39

H8

VSS_40

H10

VSS_41

H12

VSS_42

H14

VSS_43

H16

VSS_44

H18

VSS_45

H24

VSS_46

H26

VSS_47

H28

VSS_48

H30

VSS_49

J4

VSS_50

POWER/GND1

POWER/GND1

J5

VSS_51

J7

VSS_52

J9

VSS_53

J11

VSS_54

J13

VSS_55

J15

VSS_56

J17

VSS_57

J19

VSS_58

J21

VSS_59

J23

VSS_60

K2

VSS_61

K3

VSS_62

K8

VSS_63

K10

VSS_64

K12

VSS_65

K14

VSS_66

K16

VSS_67

K18

VSS_68

K20

VSS_69

K22

VSS_70

K24

VSS_71

K26

VSS_72

K28

VSS_73

K30

VSS_74

L7

VSS_75

L9

VSS_76

L11

VSS_77

L13

VSS_78

L15

VSS_79

L17

VSS_80

L19

VSS_81

L21

VSS_82

L23

VSS_83

M8

VSS_84

M10

VSS_85

ZIF-941P-S

ZIF-941P-S

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AE10

AE12

AF11

CPUF

CPUF

T15

VDD_86

T17

VDD_87

T19

VDD_88

T21

VDD_89

T23

VDD_90

U8

VDD_91

U10

VDD_92

U12

VDD_93

U14

VDD_94

U16

VDD_95

U18

VDD_96

U20

VDD_97

U22

VDD_98

V9

VDD_99

V11

VDD_100

V13

VDD_101

V15

VDD_102

V17

VDD_103

V19

VDD_104

V21

VDD_105

V23

VDD_106

W4

VDD_107

W5

VDD_108

W8

VDD_109

W10

VDD_110

W12

VDD_111

W14

VDD_112

W16

VDD_113

W18

VDD_114

W20

VDD_115

W22

VDD_116

Y2

VDD_117

Y3

VDD_118

Y7

VDD_119

Y9

VDD_120

Y11

VDD_121

Y13

VDD_122

Y15

VDD_123

Y17

VDD_124

Y19

VDD_125

Y21

VDD_126

Y23

VDD_127

AA8

VDD_128

VDD_129

VDD_130

VDD_131

VDD_132

VDD_133

VDD_134

POWER/GND2

POWER/GND2

VDD_135

AB7

VDD_136

AB9

VDD_137

VDD_138

VDD_139

VDD_140

VDD_141

VDD_142

VDD_143

VDD_144

AC4

VDD_145

AC5

VDD_146

AC8

VDD_147

VDD_148

VDD_149

VDD_150

VDD_151

VDD_152

VDD_153

VDD_154

AD2

VDD_155

AD3

VDD_156

AD7

VDD_157

AD9

VDD_158

VDD_159

VDD_160

VDD_161

VDD_162

AF7

VDD_163

AF9

VDD_164

VDD_165

AG4

VDD_166

AG5

VDD_167

AG7

VDD_168

AH2

VDD_169

AH3

VDD_170

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

ZIF-941P-S

ZIF-941P-S

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W7

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

Y14

Y16

Y18

Y20

Y22

AA4

AA5

AA7

AA9

CPU_VDDNB_RUN CPU_VDDHT

A4

A6

B5

B7

C6

C8

D7

D9

E8

E10

F9

F11

G10

G12

MT1

MT2

MT3

MT4

MT5

MT6

MT7

MT8

MT9

MT10

MT11

MT12

MT13

MT14

MT15

MT16

MT17

B2

H20

AE7

MT18

MT19

MT20

MT21

MT22

MT23

MT24

MT25

MT26

CPU_VDDNB_RUN

M_C10

M_C10

.01U-04

.01U-04

2 1

Processor Power and Ground

CPUG

CPUG

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5