Page 1

1

2

3

4

5

6

7

8

BOM P/N:89-200-A39000

Rev: A 15-A39-010000

A A

730S A

Revision History :

B B

C C

Rev: 1.0 15-A39-010100

Rev: 1.1 15-A39-010200

BOM P/N:89-200-A39100

BOM P/N:89-200-A39200

Page Index

01. Cover Sheet

02. Block Diagram

03. CPU

04. CPU

05. CPU

06. 730S-1 (MEMORY/HOST INTERFACE)

07. 730S-2 (PCI/IDE/INTERFACE)

08. 730S-3 (VGA/AGP INTERFACE)

09. 730S-4 (SOUTH BRIDGE)

10. 730S-5 (POWER)

11. Hardware Trap

12. CLOCK GENERATOR

13. DIMM1/2

14. AGP

15. VGA

16. PCI1/2

17. PCI3/4

18. PCI5/AT123S

19. IDE CONNECTORS

20. USB1/2

21. AC'97 CODEC(ALC201A)

22. AUDIO INTERFACE

23. AMR/USB3

24. RTC

25. PS2 KB/MS

26. ITE8705/SIS950

27. Wake Up Event/FDC/SIR

28. COM1/2 / PARALLEL PORT

29. HM/FAN

30. Panel

31. ROM

32.STR/VCC3_DUAL/SB1.8V/SB3V

33.VDDQ/VCC1.8V/OVP circuit

34.ATX

35.PWM

36. RTL8100/B (LOM)

SIGNATURE

DESUGNER

D D

LAYOUT

Steven

DREAM'S

DATE

09/05/'2001

Elitegroup Computer Systems

CHECK

APPROVAL

1

Steven

2

09/05/'2001

3

Title

Cover Sheet

Size Document Number Rev

Custom

4

5

6

Date: Sheet of

7

1 36Wednesday, September 05, 2001

8

1.1730SA

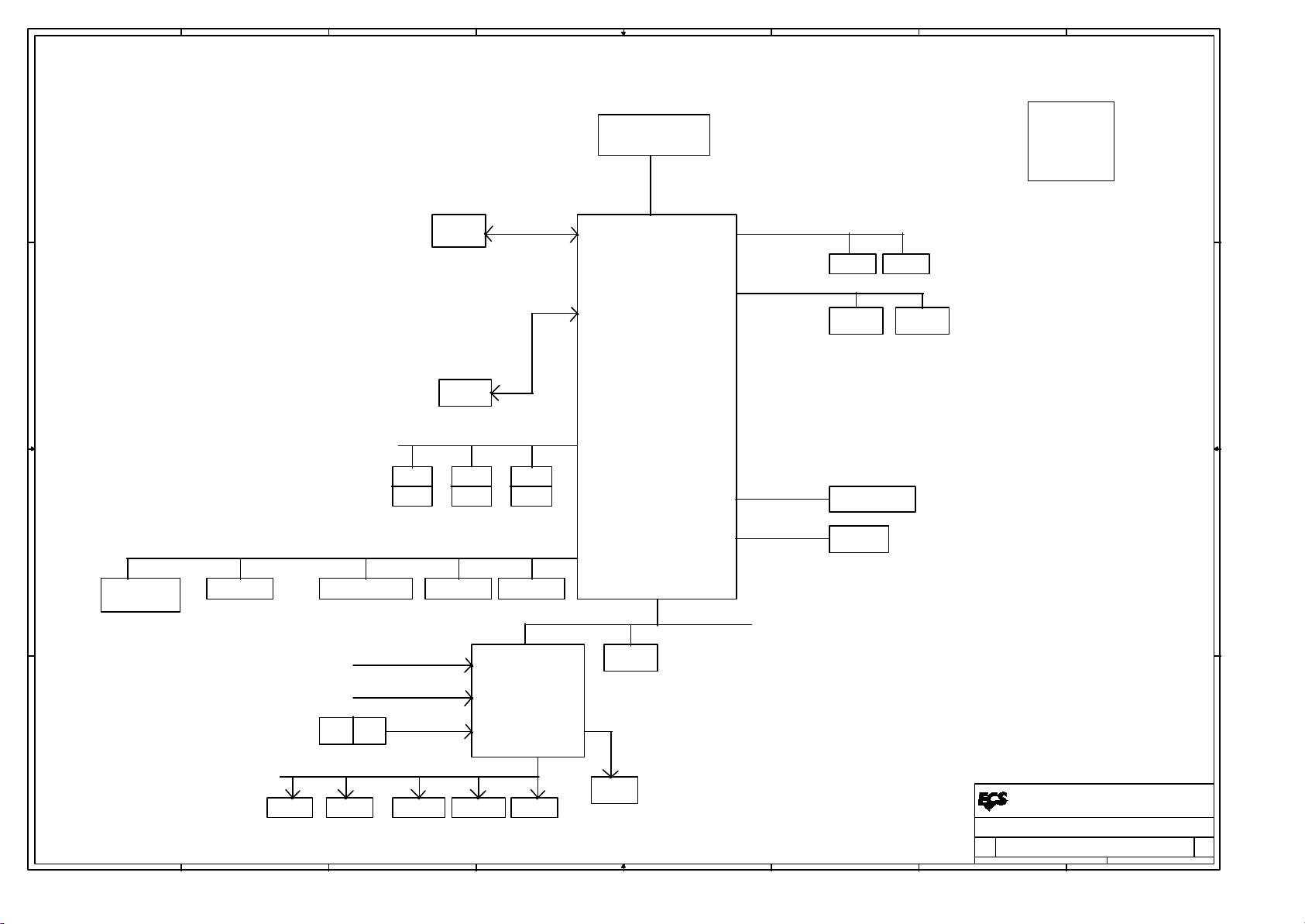

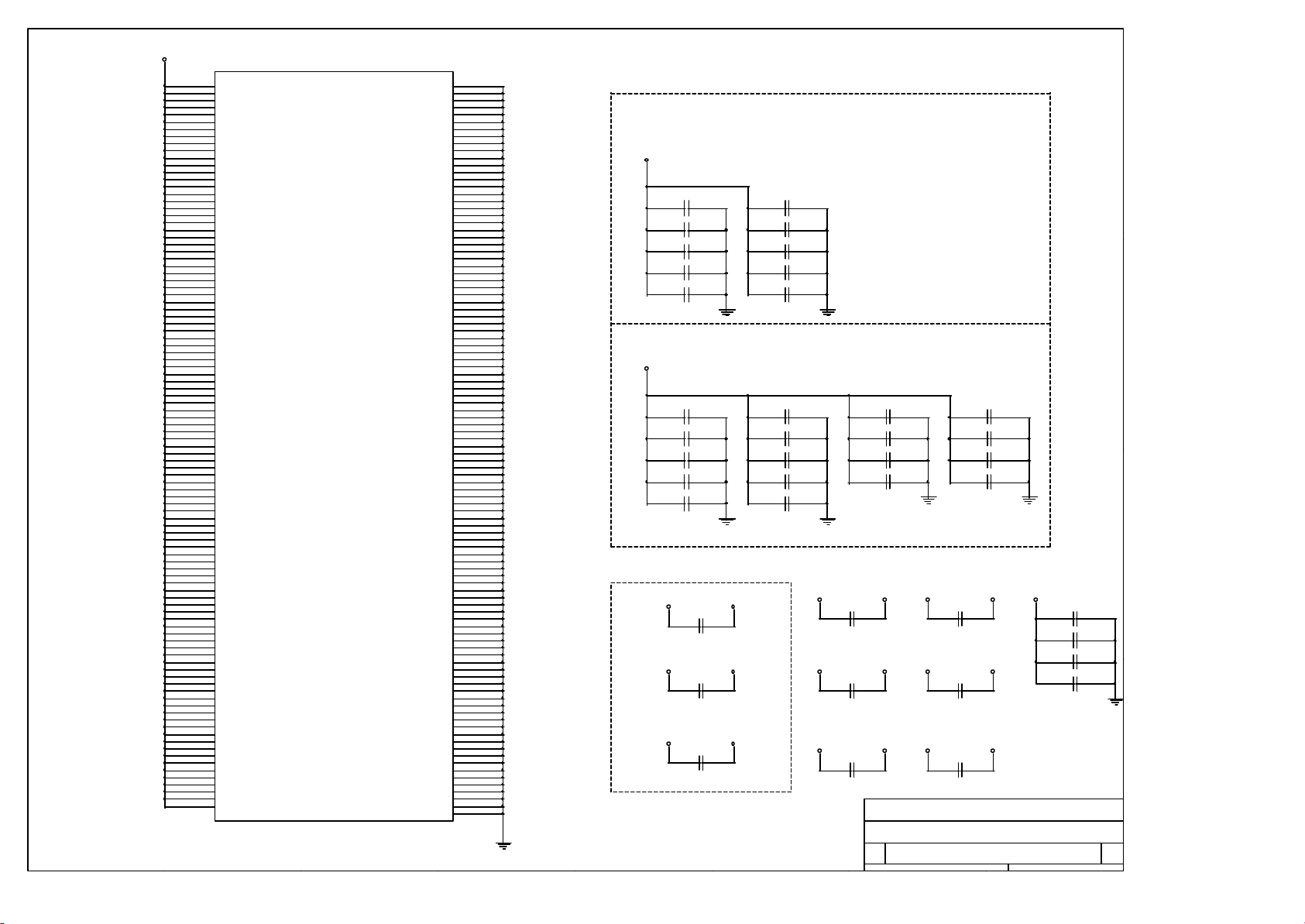

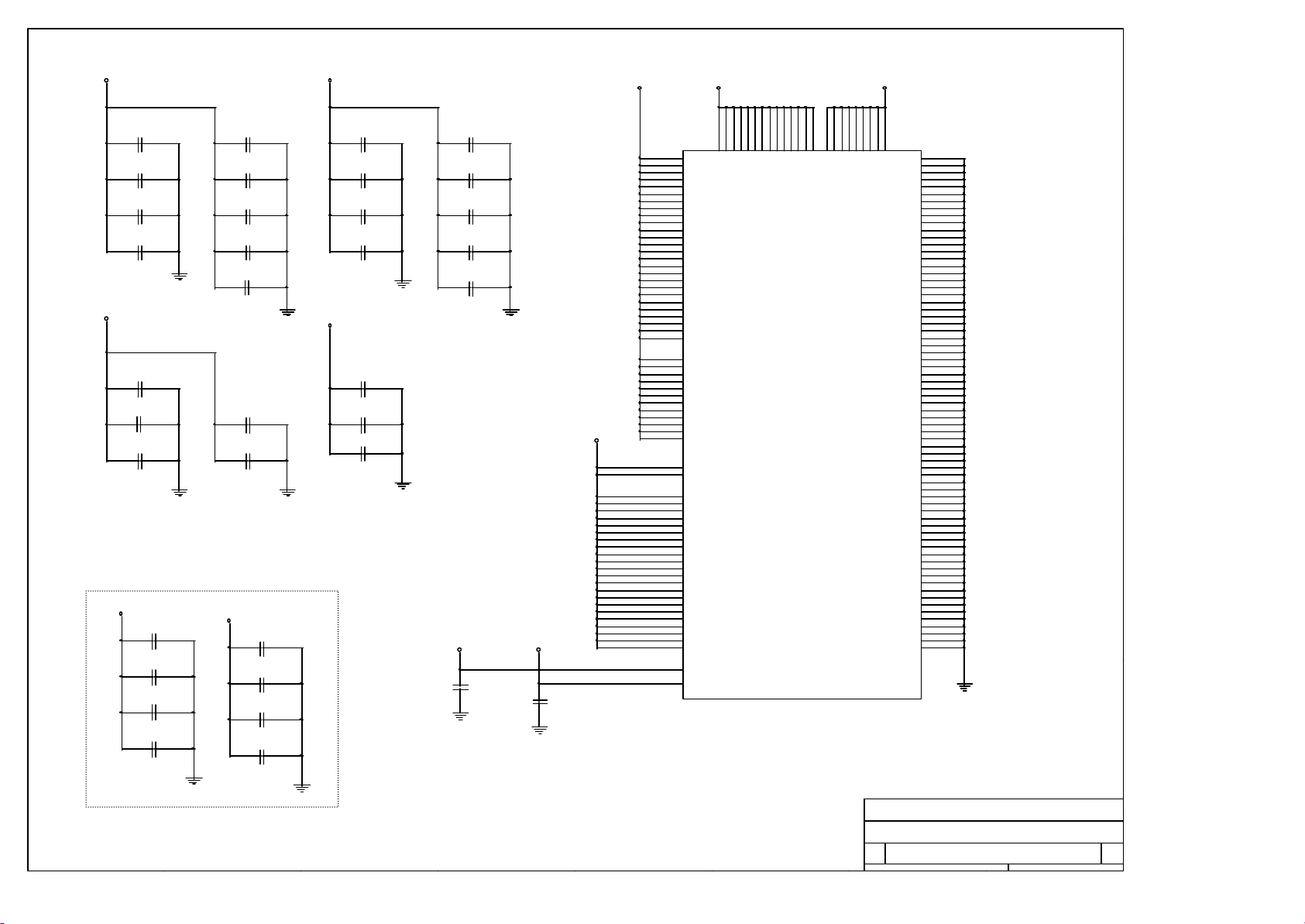

Page 2

1

2

3

4

5

6

7

8

System Block Diagram

A A

Socket A

Clock

Gen.

P.3,4,5

P.12

CRT

P.15

DIMM 1 DIMM 2

P.13 P.13

1. PLL2.5V=VCC5->PLL2.5V Page4

2. VCC2.5V=VCC5->VCC2.5V Page11

3. RTCVDD=SB5V->RTCVDD Page24

4. SB1.8V=SB5V->SB1.8V Page32

5. SB3V=SB5V->SB3V Page32

6. V_DIMM Page32

IDE 1

(ATA-100) (ATA-100)

B B

IDE 2

P.19P.19

7. VDDQ Page33

8. VCC1.8V Page33

9. VCC_CORE Page35

SiS730S

AGP

P.14

P.20P.20

USB 2

USB 3USB 5

USB 0

USB 1

P.23

Hardware Traps

P.11

KEYBOARD

/MOUSE

P.25

P.16P.17P.23

P.6,7,8,9,10

USB 4

C C

AC'97

CODEC(ALC100P)

AMR PCI SLOT3/4 PCI SLOT1/2

PCI

SLOT5/AT123S

P.18

P.21

1.KLOCK->NB pinB9(KLOCK#)

2.CPUSTP->NB pinB12(GPIO7)

3.remove reset->NB pinD13(GPIO0)

(EN-RSTSW)

4.CNR_DWEN->NB pinE16(GPIO1)

5.select ICS or Winbond clock gen->NB

pinA12(GPIO2)

730S power consumption

VCC3->340.18mA

"1"=ICS , "0"=Winbond

VCC1.8->1653.7mA

VCC_CORE->60mA

SB1.8V->10mA

SB3.3V->69.4mA

VOLTAGE MONITOR

P.29

TEMPERATURE MONITOR

P.29

FAN1 FAN2

FAN CONTROL

P.29

D D

LPC SUPER I/O

SIS950(ITE 8705)

P.26

LPC

ROM

optional

S0

正常 工作(系統

S1 STOPCLK

Full Run)

拉下

S2 Deep sleep(

S3 STR

S4 STD

S5

正常關機

目前沒有使用到

)

Legacy

GPIOs

P.9

1

2

SIR

P.27 P.28 P.28 P.27

SERIAL PARALLEL FLOPPY

3

P.31

4

5

6

ROM

Elitegroup Computer Systems

Title

Block Diagram

Size Document Number Rev

730SA

Custom

Date: Sheet of

7

2 36Wednesday, September 05, 2001

8

1.1

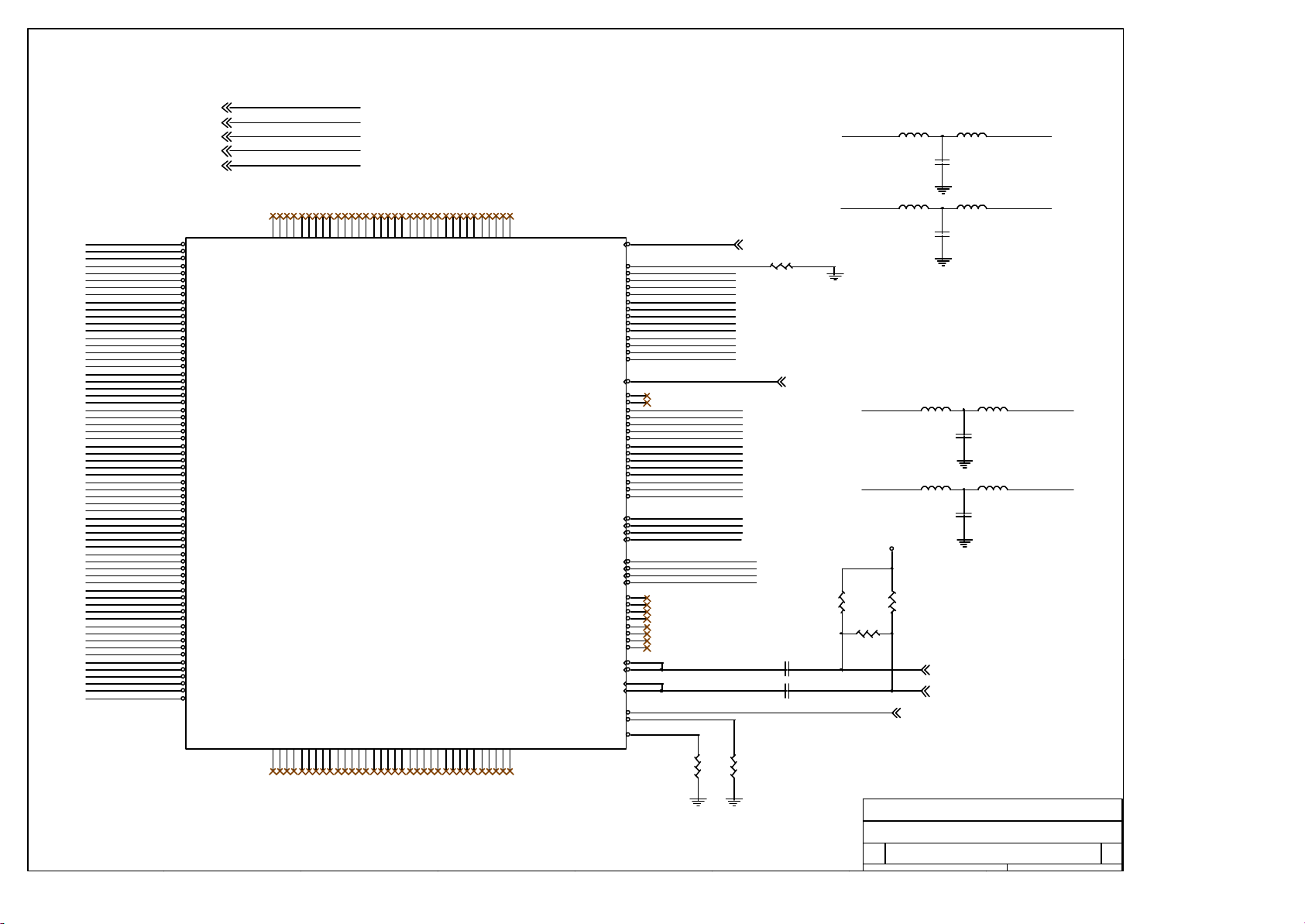

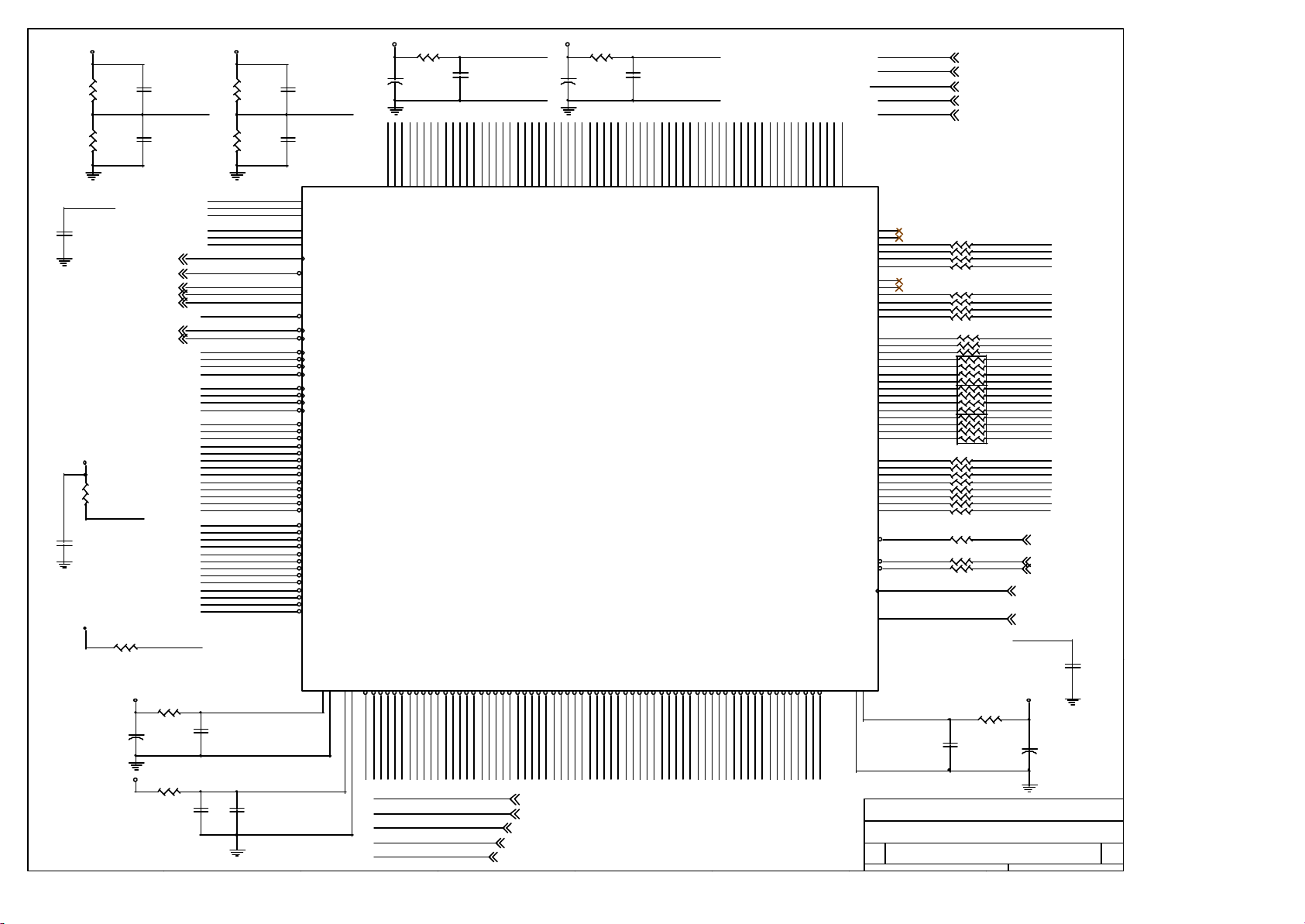

Page 3

8

7

6

5

4

3

2

1

SDATAINCLK-[0..3]<6>

SDATAOUTCLK-[0..3]<6>

D D

SDATA-0

SDATA-1

SDATA-2

SDATA-3 SADDIN-1

SDATA-4 SADDIN-2

SDATA-5 SADDIN-3

SDATA-6 SADDIN-4

SDATA-7 SADDIN-5

SDATA-8 SADDIN-6

SDATA-9 SADDIN-7

SDATA-10 SADDIN-8

SDATA-11 SADDIN-9

SDATA-12 SADDIN-10

SDATA-13 SADDIN-11

SDATA-14 SADDIN-12

C C

B B

SDATA-15 SADDIN-13

SDATA-16 SADDIN-14

SDATA-17

SDATA-18

SDATA-19 SADDOUTCLKSDATA-20

SDATA-21

SDATA-22

SDATA-23 SADDOUT-2

SDATA-24 SADDOUT-3

SDATA-25 SADDOUT-4

SDATA-26 SADDOUT-5

SDATA-27 SADDOUT-6

SDATA-28 SADDOUT-7

SDATA-29 SADDOUT-8

SDATA-30 SADDOUT-9

SDATA-31 SADDOUT-10

SDATA-32 SADDOUT-11

SDATA-33 SADDOUT-12

SDATA-34 SADDOUT-13

SDATA-35 SADDOUT-14

SDATA-36

SDATA-37

SDATA-38

SDATA-39

SDATA-40

SDATA-41

SDATA-42

SDATA-43

SDATA-44 SDATAOUTCLK-0

SDATA-45 SDATAOUTCLK-1

SDATA-46 SDATAOUTCLK-2

SDATA-47 SDATAOUTCLK-3

SDATA-48

SDATA-49

SDATA-50

SDATA-51

SDATA-52

SDATA-53

SDATA-54

SDATA-55

SDATA-56

SDATA-57

SDATA-58

SDATA-59

SDATA-60

SDATA-61

SDATA-62

SDATA-63

SADDOUT-[2..14]<6>

AC33

AC37

AC35

AA35

W37

W35

AA33

AE37

AA37

SADDIN-[2..14]<6>

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

A13

C9

C21

A21

E19

C19

C17

A11

A17

A15

SDATA-[0..63]<6>

E9

A9

SYSDATA#0

SYSDATA#1

SYSDATA#2

SYSDATA#3

SYSDATA#4

SYSDATA#5

SYSDATA#6

SYSDATA#7

SYSDATA#8

SYSDATA#9

SYSDATA#10

SYSDATA#11

SYSDATA#12

SYSDATA#13

SYSDATA#14

SYSDATA#15

SYSDATA#16

SYSDATA#17

SYSDATA#18

SYSDATA#19

SYSDATA#20

SYSDATA#21

SYSDATA#22

SYSDATA#23

SYSDATA#24

SYSDATA#25

SYSDATA#26

SYSDATA#27

SYSDATA#28

SYSDATA#29

SYSDATA#30

SYSDATA#31

SYSDATA#32

SYSDATA#33

SYSDATA#34

SYSDATA#35

SYSDATA#36

SYSDATA#37

SYSDATA#38

SYSDATA#39

SYSDATA#40

SYSDATA#41

SYSDATA#42

SYSDATA#43

SYSDATA#44

SYSDATA#45

SYSDATA#46

SYSDATA#47

SYSDATA#48

SYSDATA#49

SYSDATA#50

SYSDATA#51

SYSDATA#52

SYSDATA#53

SYSDATA#54

SYSDATA#55

SYSDATA#56

SYSDATA#57

SYSDATA#58

SYSDATA#59

SYSDATA#60

SYSDATA#61

SYSDATA#62

SYSDATA#63

A A

SDATAINCLK-[0..3]

SDATAOUTCLK-[0..3]

SADDIN-[2..14]

SADDOUT-[2..14]

SDATA-[0..63]

F8

F30

G11

NC1

NC2

NC3

NC35

NC36

NC37

AE31

AF6

AF8

G13

AF10

G19

NC4

NC38

AF28

G21

NC5

NC39

AF30

G27

NC6

NC40

AF32

G29

NC7

NC41

AG5

G31H6H8

NC8

NC9

NC42

NC43

AG19

AG21

NC10

NC44

AG23

H10

NC11

NC45

AG25

H28

NC12

NC46

AH8

NC13

NC47

H30

H32J5J31K8K30

NC14

NC15

NC48

NC49

AH30

AJ7

AJ9

NC16

NC50

AJ11

NC17

NC51

AJ15

NC18

NC52

AJ17

L31

N31

Q31S7S31U7U31W7W31Y5Y31

NC19

NC20

NC21

NC22

NC23

NC24

NC53

NC54

NC55

NC56

NC57

NC58

AJ19

AJ27

AJ29

AK8

AL7

L45

R40

60.4-1-06

R58

301-1-06

VCC_CORE

10nH-06

L47

10nH-06

R39

60.4-1-06

SDATAINVAL- <6>

SDATAIN-0

AA31

AC31

AD8

AD30

NC25

NC26

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC62

AM8

NC63

AN7

NC64

AN9

NC65

AN11

NC66

AN25

NC67

AN27

NC68

NC59

NC60

NC61

AL9

AL11

AL25

AL27

U4A

SYSADDINCLK#

SYSADDIN#1

SYSADDIN#2

SYSADDIN#3

SYSADDIN#4

SYSADDIN#5

SYSADDIN#6

SYSADDIN#7

SYSADDIN#8

SYSADDIN#9

SYSADDIN#10

SYSADDIN#11

SYSADDIN#12

SYSADDIN#13

SYSADDIN#14

SYSADDOUTCLK#

SYSADDOUT#0

SYSADDOUT#1

SYSADDOUT#2

SYSADDOUT#3

SYSADDOUT#4

SYSADDOUT#5

SYSADDOUT#6

SYSADDOUT#7

SYSADDOUT#8

SYSADDOUT#9

SYSADDOUT#10

SYSADDOUT#11

SYSADDOUT#12

SYSADDOUT#13

SYSADDOUT#14

SYSDATAINCLK#0

SYSDATAINCLK#1

SYSDATAINCLK#2

SYSDATAINCLK#3

SYSDATAOUTCLK#0

SYSDATAOUTCLK#1

SYSDATAOUTCLK#2

SYSDATAOUTCLK#3

SYSCHECK#0

SYSCHECK#1

SYSCHECK#2

SYSCHECK#3

SYSCHECK#4

SYSCHECK#5

SYSCHECK#6

SYSCHECK#7

RSTCLK#

CLKIN#

RSTCLK

CLKIN

SDATAIN_VALID#

SDATAOUT_VALID#

SYSFILLVALID#

ZIF-462P-AMP

AJ33

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

E3

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

W33

J35

E27

E15

AE35

C37

A33

C11

U37

Y33

L35

E33

E25

A31

C13

A19

AL19

AL17

AN19

AN17

AN33

AL31

AJ31

SADDINCLK-

SDATAIN-0

SDATAIN-1

SDATAIN-2

SDATAIN-3

SDATAINVAL-

R87

270-06

SADDINCLK- <6>

R89

270-06

SADDOUTCLK- <6>

C24 .1U-06

C23 .1U-06

R88

270-06

L51

10nH-06

L53

10nH-06

CPUCLK- <12>

CPUCLK <12>

L46

10nH-06

C131

5P-06

L48

10nH-06

C132

5P-06

L52

10nH-06

C134

5P-06

L54

10nH-06

C135

5P-06

SDATAINCLK-0

SDATAINCLK-1SDATAIN-1

SDATAINCLK-2SDATAIN-2

SDATAINCLK-3SDATAIN-3

Title

SOCKETA-1

Size Document Number Rev

730SA 1.1

Date: Sheet of

8

7

6

5

4

3

2

3 36Wednesday, September 05, 2001

1

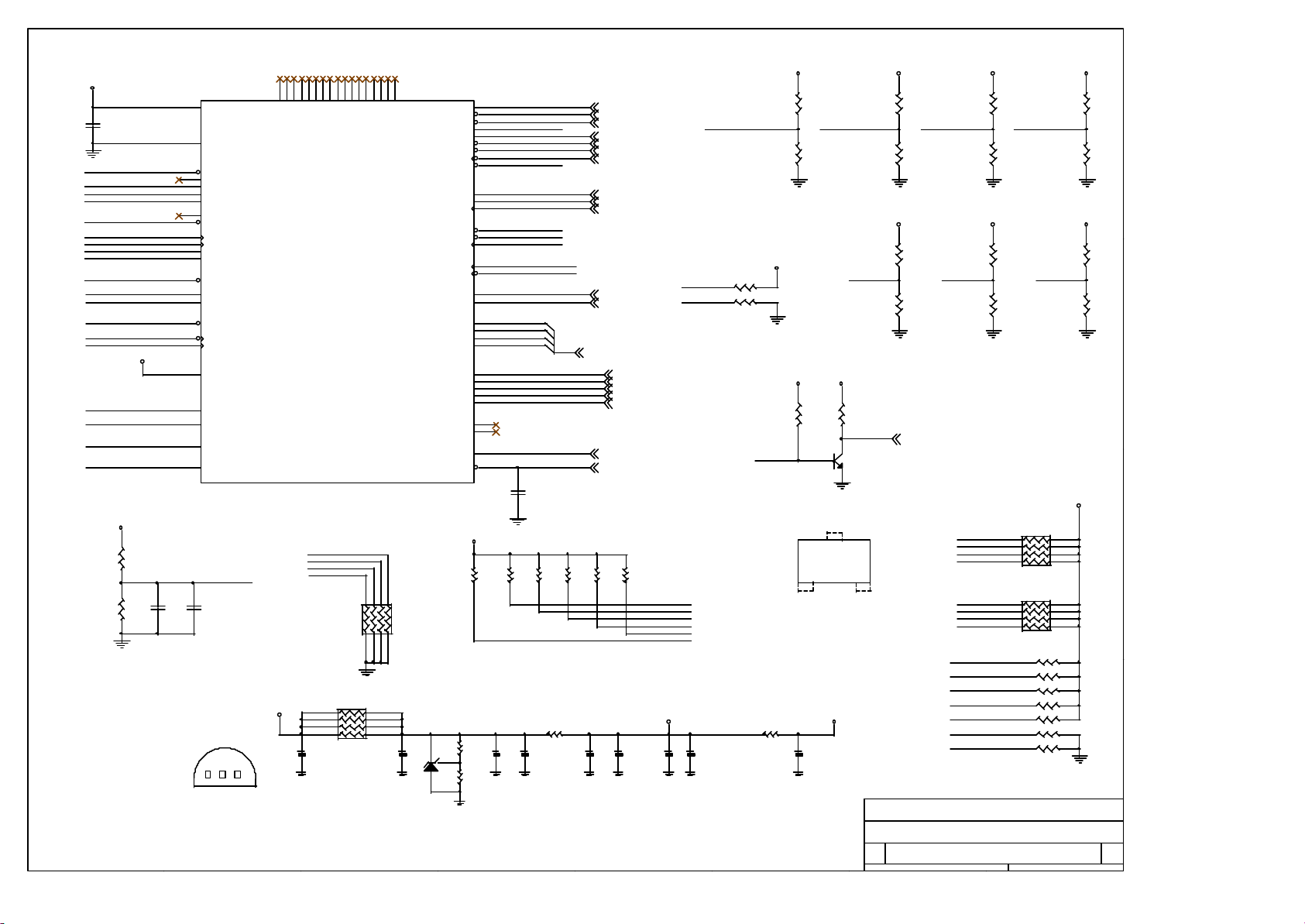

Page 4

8

7

6

5

4

3

2

1

VCC_CORE

VCC_Z

MC2

1US

D D

C C

B B

VSS_Z

P_TRSTP_TDI

P_TCK

P_TMS

DBREQSCANCLK1

SCANCLK2

SCANSHIFTEN

SCANINTEVAL

PLLTESTPLLMON1 COREFB-

PLLMON2 COREFB+

PLLBYPASS- FID0

PLLBYPASSCLK- FID2

PLLBYPASSCLK FID3

VCCA_PLL

ZP

ZN

VREFSYS

SYSVREFMODE CPURST-

VCC_CORE

R104

100-1-06

R105

100-1-06

BC26

.33U-25V

AN13

AL13

AJ25

AL15

AN15

AJ23

AC7

AE7

U3

U5

U1

Q1

Q3

AA1

AA3

S1

S5

Q5

S3

AC3

AE5

AC5

W5

AA5

VCC_Z

VSS_Z

TRST#

TDO

TDI

TCK

TMS

DBRDY

DBREQ#

SCANCLK1

SCANCLK2

SCANSHIFTEN

SCANINTEVAL

PLLTEST#

PLLMON1

PLLMON2

PLLBYPASS#

PLLBYPASSCLK#

PLLBYPASSCLK

VCCA

ZP

ZN

VREFSYS

SYSVREFMODE

VREFSYS

BC27

.047U-06

A A

G7G9G15

G17

G23

G25N7Q7Y7AA7

AG7

AG9

AG15

AG17

AG27

AG29

AG31

KEY1

KEY2

KEY3

KEY4

KEY5

KEY6

KEY7

KEY8

KEY9

KEY10

KEY11

KEY12

KEY13

KEY14

KEY15

KEY16

KEY17

SCANCLK2

SCANINTEVAL

SCANCLK1

SCANSHIFTEN

RN5

270-8P4R

1 8

2 7

3 6

4 5

RN1

C3

100-8P4R

1 8

2 7

3 6

4 5

C6

39P-06

VCC5

CAREF

1 2 3

TL-431

TOP VIEW (DIP)

8

7

6

U200B

NMI

SMI#

A20M#

FERR

INTR

INIT#

IGNNE#

STPCLK#

FLUSH#

CONNECT

PROCRDY

CLKFWDRESET

PIC#1

PIC#0

PICCLK

K7CLKOUT

K7CLKOUT#

COREFB-

COREFB+

FID0

FID1

FID2

FID3

VID0

VID1

VID2

VID3

VID4

AMDPIN

ANALOG

PWROK

RESET#

ZIF-462P-AMP-O

VCC_CORE

(2.5V Output)

D3

139P-06

LM431

DIP

2 3

0-06

R23

0-06-O

NMI

AN3

SMI-

AN5

A20M-

AE1

FERR PLLBYPASSCLK- PLLBYPASSCLK K7CLKOUT K7CLKOUT-

AG1

INTR

AL1

INIT-

AJ3

IGNNE-

AJ1

STPCLK-

AC1

FLUSH-

AL3

CONNECT

AL23

PROCRDY

AN23

CLKFWDRST

AJ21

PICD1-

N5

PICD0-

N3

PICCLK

N1

K7CLKOUT

AL21

K7CLKOUT-

AN21

AG13

AG11

W1

FID1

W3

Y1

Y3

VID0

L1

VID1

L3

VID2

L5

VID3

L7

VID4

J7

AH6

AJ13

BC6

.1U-06-O

R47

510-06

PWRGOOD

R48

510-06

AE3

AG3

R45

510-06

NMI <9>

SMI- <9>

A20M- <9>

INTR <9>

INIT- <9>

IGNNE- <9>

STPCLK- <9>

CONNECT <6>

PROCRDY <6>

CLKFWDRST <6>

COREFB- <35>

COREFB+ <35>

FID[0..3] <11>

PWRGOOD <34>

CPURST- <9>

R46

510-06

VID0 <35>

VID1 <35>

VID2 <35>

VID3 <35>

VID4 <35>

R65

510-06

R64

510-06

P_TCK

P_TMS

P_TDI

P_TRSTPLLTESTDBREQ-

COREFB+

COREFB-

To NB pinAJ23

VCCA_PLL PLL2.5V

.1U-06-O

BC7R22

C21

39P-06

C22

39P-06

C15

39P-06-O

R34 0-06

C5

39P-06

C20

39P-06-O

for_EMI

5

4

VCC_CORE VCC_CORE

R59

100-06

R41

100-06

VCC_CORE

R280

10K-06-O

R291

10K-06-O

R63

680-06

FERR

1

B

R55 10-06

C16

39P-06

3

R60

100-06

R42

100-06

R152

330-06

PICD1- PICD0- PICCLK

R147

1K-06

VCC3VCC_CORE

R44

4.7K-06

3

1

2

2N3904-S

C

3

2N3904

NPN

To PWROK

circuit

FERR- <9>

Q13

2

E

Title

SOCKETA-2

Size Document Number Rev

730SA 1.1

B

Date: Sheet of

2

VCC_CORE VCC_CORE

R56

100-06

R37

100-06

VCC3VCC3 VCC3

R153

330-06

R148

1K-06

CPURSTINITSMINMI

INTR

IGNNEA20MSTPCLK-

FLUSHPLLBYPASSPLLMON1

PLLMON2

ZN

ZP

SYSVREFMODE

RN2

1 8

2 7

3 6

4 5

680-8P4R

RN4

1 8

2 7

3 6

4 5

680-8P4R

R62 680-06

R90 680-06

R61 56-06

R43 56-06

R28 47-1-06

R26 40.2-1-06

R27 270-06

4 36Wednesday, September 05, 2001

1

VCC_CORE

R57

100-06

R38

100-06

R154

330-06

R149

1K-06

Page 5

8

VCC_CORE

D D

C C

B B

A A

8

AB32

AB34

AB36

AF14

AF18

AF22

AF26

AF34

AF36

AH10

AH14

AH18

AH22

AH26

AK10

AK14

AK18

AK22

AK26

AK30

AK34

AK36

AM10

AM14

AM18

AM22

AM26

AM30

AM34

AD2

AD4

AD6

AH2

AH4

AJ5

AL5

AM2

B12

B16

B20

B24

B28

B32

B36

D12

D16

D2

D20

D24

D28

D32

D4

D8

F12

F16

F20

F24

F28

F32

F34

F36

H12

H16

H2

H20

H24

H4

K32

K34

K36

M2

M4

M6

M8

P30

P32

P34

P36

R2

R4

R6

R8

T30

T32

T34

T36

X30

X32

X34

X36

Z2

Z4

Z6

Z8

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

B4

VCC_CORE46

B8

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

V2

VCC_CORE90

V4

VCC_CORE91

V6

VCC_CORE92

V8

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

7

7

6

U300C

AB2AB30

VSS1VCC_CORE1

AB4

VSS2

AB6

VSS3

AB8

VSS4

AD32

VSS5

AD34

VSS6

AD36

VSS7

AF12

VSS8

AF16

VSS9

AF2

VSS10

AF20

VSS11

AF24

VSS12

AF4

VSS13

AH12

VSS14

AH16

VSS15

AH20

VSS16

AH24

VSS17

AH28

VSS18

AH32

VSS19

AH34

VSS20

AH36

VSS21

AK12

VSS22

AK16

VSS23

AK2

VSS24

AK20

VSS25

AK24

VSS26

AK28

VSS27

AK32

VSS28

AK4

VSS29

AK6

VSS30

AM12

VSS31

AM16

VSS32

AM20

VSS33

AM24

VSS34

AM28

VSS35

AM32

VSS36

AM36

VSS37

AM4

VSS38

AM6

VSS39

B10

VSS40

B14

VSS41

B18

VSS42

B2

VSS43

B22

VSS44

B26

VSS45

B30

VSS46

B34

VSS47

B6

VSS48

D10

VSS49

D14

VSS50

D18

VSS51

D22

VSS52

D26

VSS53

D30

VSS54

D34

VSS55

D36

VSS56

D6

VSS57

F10

VSS58

F14

VSS59

F18

VSS60

F2

VSS61

F22

VSS62

F26

VSS63

F4

VSS64

F6

VSS65

H14

VSS66

H18

VSS67

H22

VSS68

H26

VSS69

H34

VSS70

H36

VSS71

K2

VSS72

K4

VSS73

K6

VSS74

M30

VSS75

M32

VSS76

M34

VSS77

M36

VSS78

P2

VSS79

P4

VSS80

P6

VSS81

P8

VSS82

R30

VSS83

R32

VSS84

R34

VSS85

R36

VSS86

T2

VSS87

T4

VSS88

T6

VSS89

T8

VSS90

V30

VSS91

V32

VSS92

V34

VSS93

V36

VSS94

X2

VSS95

X4

VSS96

X6

VSS97

X8

VSS98

Z30

VSS99

Z32

VSS100

Z34

VSS101

Z36

VSS102

ZIF-462P-AMP-O

6

5

4

Bulk Decoupling

OSCON Capacitors

VCC_CORE

3

2

1

1206 Package

CB7 4.7U-16V-12-O

CB2 4.7U-16V-12-O

CB1 4.7U-16V-12-O

CB3 4.7U-16V-12-O

CB4 4.7U-16V-12-O

High Frequency Decoupling

0603 Package

VCC_CORE

BC14 .1U-06 BC22 .1U-06 BC23 .1U-06

BC32 .1U-06

BC18 .1U-06 BC37 .1U-06

V_CORE<->VCC3 Power Island 2-3cm 放置1

VCC_CORE

VCC_CORE

VCC_CORE

5

4

C60

33P-06

C59

33P-06

C66

33P-06

CB5 4.7U-16V-12-O

CB9 4.7U-16V-12-O

CB8 4.7U-16V-12-O

CB10 4.7U-16V-12-O

CB6 4.7U-16V-12-O

VCC3

VCC3

VCC3

BC36 .1U-06

BC43 .1U-06BC42 .1U-06

BC17 .1U-06BC16 .1U-06

顆電容

3

VCC_CORE

VCC_CORE

VCC_CORE

BC33 .1U-06

BC40 .1U-06

BC44 .1U-06

BC46 .1U-06

BC41 .1U-06

BC45 .1U-06

BC15 .1U-06

for EMI solution

VCC5

C13

33P-06

C7

33P-06

C14

33P-06

VCC_CORE

VCC5

VCC_CORE

VCC5

VCC_CORE

Title

SOCKETA-3

Size Document Number Rev

730SA 1.1

B

Date: Sheet of

2

C26

33P-06

C1

33P-06

C25

33P-06

VCC5

VCC5

VCC5

VCC_CORE

BC65 .1U-06

BC4 .1U-06

BC62 .1U-06

BC9 .1U-06

PLACE USB SIGNAL

AROUND

5 36Wednesday, September 05, 2001

1

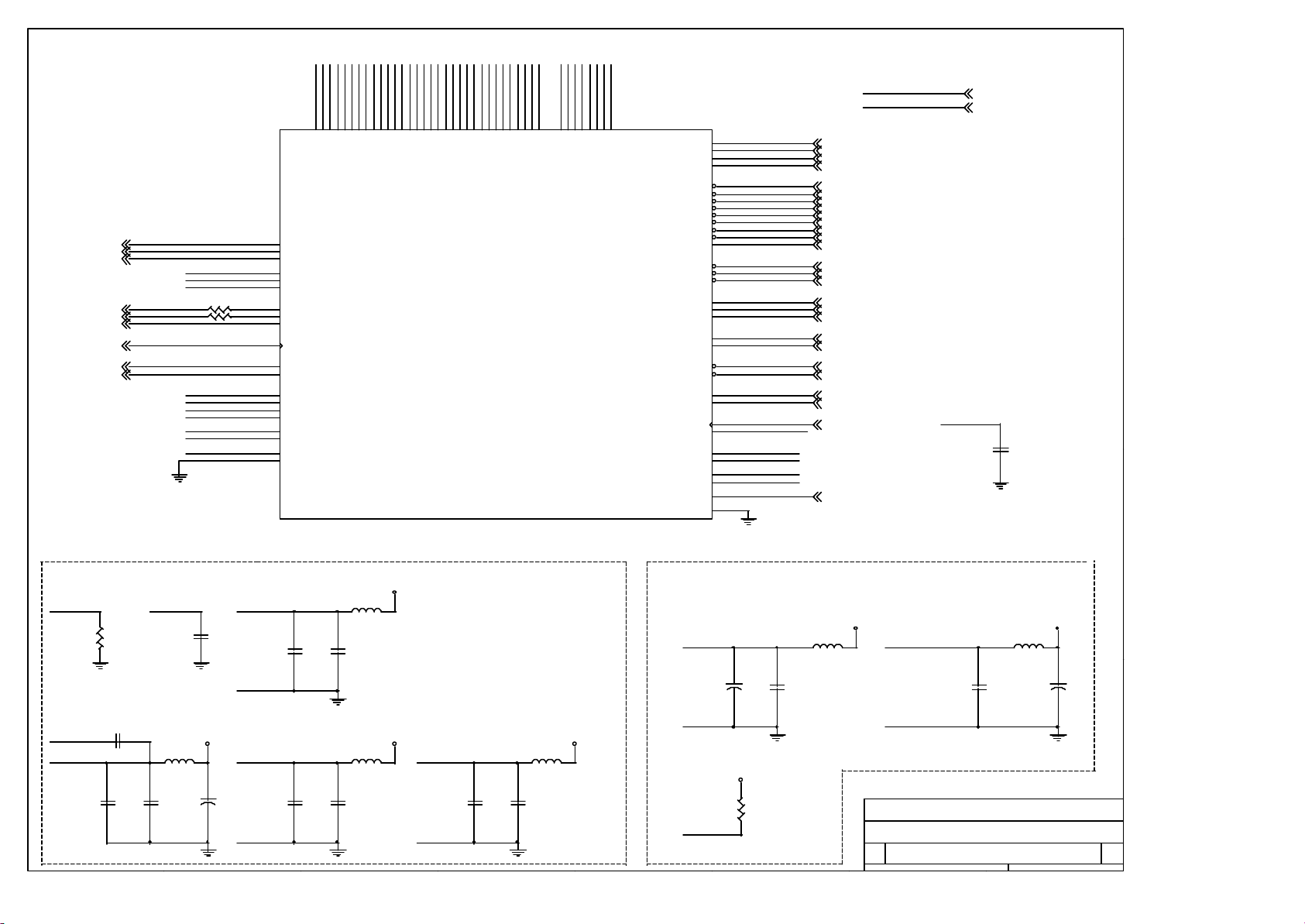

Page 6

8

VCC_CORE VCC_CORE

R151

100-1-06

80.6/1% 80.6/1%

R166

D D

100-1-06

BC60

.01U-06

HSTLREFA HSTLREFB

BC63

.01U-06

7

R174

100-1-06

R163

100-1-06

BC75

.01U-06

BC67

.01U-06

VCC1.8V VCC1.8V

6

R165 0-06

TC23

+

100U-25E

MD63 SDATA-60

MD62 SDATA-59

MD61 SDATA-58

MD60 SDATA-57

MD59 SDATA-56

MD58 SDATA-55

MD57 SDATA-54

MD56 SDATA-53

MD55 SDATA-52

MD54 SDATA-51

5

VDDREFA VDDREFB

BC70

.1U-06

VSSREFA VSSREFB

MD53 SDATA-50

MD52 SDATA-49

MD51 SDATA-48

MD50 SDATA-47

MD49 SDATA-46

MD48 SDATA-45

MD47 SDATA-44

MD46 SDATA-43

MD45 SDATA-42

MD44 SDATA-41

MD43 SDATA-40

MD42 SDATA-39

MD41 SDATA-38

MD40 SDATA-37

MD39 SDATA-36

R164 0-06

TC22

+

100U-25E

MD38 SDATA-35

MD37 SDATA-34

MD36 SDATA-33

MD35 SDATA-32

MD34 SDATA-31

MD33 SDATA-30

MD32 SDATA-29

MD31 SDATA-28

MD30 SDATA-27

MD29 SDATA-26

4

BC68

.1U-06

MD28 SDATA-25

MD27 SDATA-24

MD26 SDATA-23

MD25 SDATA-22

MD24 SDATA-21

MD23 SDATA-20

MD22 SDATA-19

MD21 SDATA-18

MD20 SDATA-17

MD19 SDATA-16

MD18 SDATA-15

MD17 SDATA-14

MD16 SDATA-13

MD15 SDATA-12

MD14 SDATA-11

MD13 SDATA-10

MD12 SDATA-9

MD11 SDATA-8

3

MD10 SDATA-7

MD9 SDATA-6

MD8 SDATA-5

MD7 SDATA-4

MD6 SDATA-3

MD5 SDATA-2

MD4 SDATA-1

MD3 SDATA-0

MD2

MD1

MD0

MD[0..63]

MA[0..14]

CSA-[0..3]

CSB-[0..3]

DQM[0..7]

2

1

MD[0..63] <11,13>

MA[0..14] <13>

CSA-[0..3] <13>

CSB-[0..3] <13>

DQM[0..7] <13>

U26

V29

V28

V26

W29

W28

W26

Y28

Y26

AA28

AA27

AB29

AB27

AB25

AC29

AC27

AG23

AJ23

AG22

AJ22

AH21

AE22

AF20

AH20

AG19

AJ19

AG18

AE21

AH17

AF21

AG16

AD20

V24

U25

W25

V27

V25

Y25

W27

Y29

Y27

AA29

Y24

AA26

AB28

AB26

AA25

AC28

AF23

AH23

AF22

AH22

AG21

AJ21

AE20

AG20

AJ20

AH19

AF18

AH18

VDDREFA

730SCCLK

C62

10P-06-O

730SCCLK<12>

SDATAINVAL-<3>

PROCRDY<4>

CONNECT<4>

CLKFWDRST<4>

SADDINCLK-<3>

SADDOUTCLK-<3>

C C

Close to SiS730

VCC_CORE

R157

60.4-1-06

730SCCLK

從

BC57

.1U-06

NB 730SCCLK

處拉回

B B

VCC_CORE

A A

R173

60.4-1-06

VCC3

+

S2KCOMP

R185

150-06

TC26

100U-25E

8

VSSREFA

HSTLREFA

VDDREFB

VSSREFB

HSTLREFB

730SCCLK CSA-1

SDATAINVALPROCRDY

CONNECT

CLKFWDRST

S2KCOMP

SADDINCLK-

SADDOUTCLK- MA14

SDATAOUTCLK-0 MA12

SDATAOUTCLK-1 MA11

SDATAOUTCLK-2 MA10

SDATAOUTCLK-3 MA9

SDATAINCLK-0 MA7

SDATAINCLK-1 MA6

SDATAINCLK-2 MA5

SDATAINCLK-3 MA4

SADDIN-2 MA2

SADDIN-3 MA1

SADDIN-4 MA0

SADDIN-5

SADDIN-6

SADDIN-7

SADDIN-8

SADDIN-9

SADDIN-10

SADDIN-11

SADDIN-12

SADDIN-13

SADDIN-14

SADDOUT-2

SADDOUT-3

SADDOUT-4 RAMWSADDOUT-5

SADDOUT-6

SADDOUT-7 SRASSADDOUT-8 SCASSADDOUT-9

SADDOUT-10

SADDOUT-11 730SDCLK

SADDOUT-12

SADDOUT-13

SADDOUT-14

2.5V~2.9V

BC78

.1U-06

R158

BC72

BC64

0-06

.1U-06

.01U-06

7

CPUPHYAVDD

CPUPHYAVSS

CPUAVDD

L26

M26

M24

C23

D24

D23

T26

D22

D19

D20

D21

B19

B20

T27

E24

F29

H26

P29

C25

G27

H27

M27

B22

A22

C21

A23

F22

E23

E22

A21

B21

C22

C19

C20

A20

P27

P28

R26

R28

R29

U29

R27

T29

R24

R25

T28

U28

U27

VDDREFA

VSSREFA

HSTLREFA

VDDREFB

VSSREFB

HSTLREFB

CPUCLK

SDATAINVAL#

PROCRDY

CONNECT

CLKFWDRST

S2KCOMP

SADDINCLK#

SADDOUTCLK#

SDATAOUTCLK#0

SDATAOUTCLK#1

SDATAOUTCLK#2

SDATAOUTCLK#3

SDATAINCLK#0

SDATAINCLK#1

SDATAINCLK#2

SDATAINCLK#3

SADDIN#2

SADDIN#3

SADDIN#4

SADDIN#5

SADDIN#6

SADDIN#7

SADDIN#8

SADDIN#9

SADDIN#10

SADDIN#11

SADDIN#12

SADDIN#13

SADDIN#14

SADDOUT#2

SADDOUT#3

SADDOUT#4

SADDOUT#5

SADDOUT#6

SADDOUT#7

SADDOUT#8

SADDOUT#9

SADDOUT#10

SADDOUT#11

SADDOUT#12

SADDOUT#13

SADDOUT#14

CPUPHYAVDD

CPUPHYAVSS

E18

D18

CPUAVDD

CPUAVSS

T24

T25

MD63

MD62

SDATA#63

SDATA#62

SDATA#61

SDATA#60

SDATA#59

N29

M28

N25

M29

L27

L28

SDATA-63

SDATA-62

SDATA-61

SDATA-[0..63]

SADDIN-[2..14]

SADDOUT-[2..14]

SDATAINCLK-[0..3]

SDATAOUTCLK-[0..3]

6

MD61

MD60

MD59

SDATA#58

SDATA#57

SDATA#56

L29

K27

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MEMORY

730S-1

HOST

SDATA#55

SDATA#54

SDATA#53

SDATA#52

SDATA#51

SDATA#50

SDATA#49

SDATA#48

SDATA#47

SDATA#46

SDATA#45

SDATA#44

SDATA#43

SDATA#42

SDATA#41

SDATA#40

SDATA#39

SDATA#38

P24

P25

N27

P26

M25

N26

N28

L25

K29

K25

J28

J29

H28

SDATAINCLK-[0..3] <3>

SDATAOUTCLK-[0..3] <3>

5

SDATA#37

H29

G28

G29

K28

J27

K26

K24

SDATA-[0..63] <3>

SADDIN-[2..14] <3>

SADDOUT-[2..14] <3>

MD39

MD38

MD37

SDATA#36

SDATA#35

SDATA#34

J25

J26

H24

MD36

MD35

MD34

SDATA#33

SDATA#32

SDATA#31

H25

G26

MD33

MD32

SDATA#30

SDATA#29

G25

F25

MD31

SDATA#28

F26

F28

MD30

MD29

MD28

SDATA#27

SDATA#26

SDATA#25

F27

E26

E27

4

MD27

MD26

MD25

SDATA#24

SDATA#23

SDATA#22

E29

E28

MD24

MD23

SDATA#21

SDATA#20

D27

D28

MD22

MD21

SDATA#19

SDATA#18

D29

C28

MD20

MD19

SDATA#17

SDATA#16

C29

B28

MD18

MD17

SDATA#15

SDATA#14

C27

B24

MD16

SDATA#13

C24

E25

MD15

MD14

MD13

SDATA#12

SDATA#11

SDATA#10

A24

F24

B23

MD12

MD11

SDATA#9

SDATA#8

D25

B27

MD9

MD10

SDATA#7

SDATA#6

A27

C26

3

MD8

MD7

SDATA#5

SDATA#4

B26

B25

MD6

MD5

SDATA#3

SDATA#2

A26

D26

AJ18

AJ17

MD4

MD3

SDATA#0

SDATA#1

A25

U5A

AF16

AF17

MD2

MD1

MD0

AH25

CSA#[5]

AG25

CSA#[4]

AF25

CSA#[3]

AJ26

CSA#[2]

AH26

CSA#[1]

AE24

CSA#[0]

AE27

CSB#[5]

AE28

CSB#[4]

AB24

CSB#[3]

AE29

CSB#[2]

AD25

CSB#[1]

AD26

CSB#[0]

AC25

MA[14]

AE26

MA[13]

AE25

MA[12]

AF29

MA[11]

AF28

MA[10]

AF27

MA[9]

AF26

MA[8]

AG29

MA[7]

AD24

MA[6]

AG28

MA[5]

AH28

MA[4]

AG27

MA[3]

AH27

MA[2]

AJ27

MA[1]

AG26

MA[0]

AD29

DQM[7]

AD27

DQM[6]

AE23

DQM[5]

AH24

DQM[4]

AC26

DQM[3]

AD28

DQM[2]

AF24

DQM[1]

AG24

DQM[0]

AJ24

WE#

AJ25

SRAS#

AD22

SCAS#

AG17

SDCLK

C6

CKE

SDAVSS

SDAVDD

AE19

AF19

SIS730S

Title

730S-1 (HOST/MEMORY)

Size Document Number Rev

730SA 1.1

B

Date: Sheet of

8P4R

1 <-> 8

2 <-> 7

3 <-> 6

4 <-> 5

RN22B 10-8P4R2 7

RN22A 10-8P4R1 8

RN22C 10-8P4R3 6

RN22D 10-8P4R

4 5

RN17C 10-8P4R3 6

RN17D 10-8P4R

4 5

RN17A 10-8P4R1 8

RN17B 10-8P4R2 7

R162

R168 10-06

R167 10-06

1 8

RN18

2 7

10-8P4R

3 6

4 5

1 8

RN20

2 7

3 6

10-8P4R

4 5

1 8

RN21

2 7

3 6

10-8P4R

4 5

RN16B 10-8P4R2 7

RN16D 10-8P4R4 5

RN23A 10-8P4R1 8

RN23C 10-8P4R

3 6

RN16A 10-8P4R1 8

RN16C 10-8P4R3 6

RN23B 10-8P4R2 7

RN23D 10-8P4R4 5

10-06

R187

R188 10-06

R189

10-06

730SCKE

R204

0-06

BC82

.1U-06

10-06

CSA-3

CSA-2

CSA-0

CSB-3

CSB-2

CSB-1

CSB-0

MA13

MA8

MA3

DQM7

DQM6

DQM5

DQM4

DQM3

DQM2

DQM1

DQM0

RAMW- <13>

SRAS- <13>

SCAS- <13>

730SDCLK <12>

730SCKE <32>

730SDCLK

VCC3VCC3

+

2

TC30

100U-25E

6 36Wednesday, September 05, 2001

1

8P4R

1 <-> 8

2 <-> 7

3 <-> 6

4 <-> 5

C77

10P-06-O

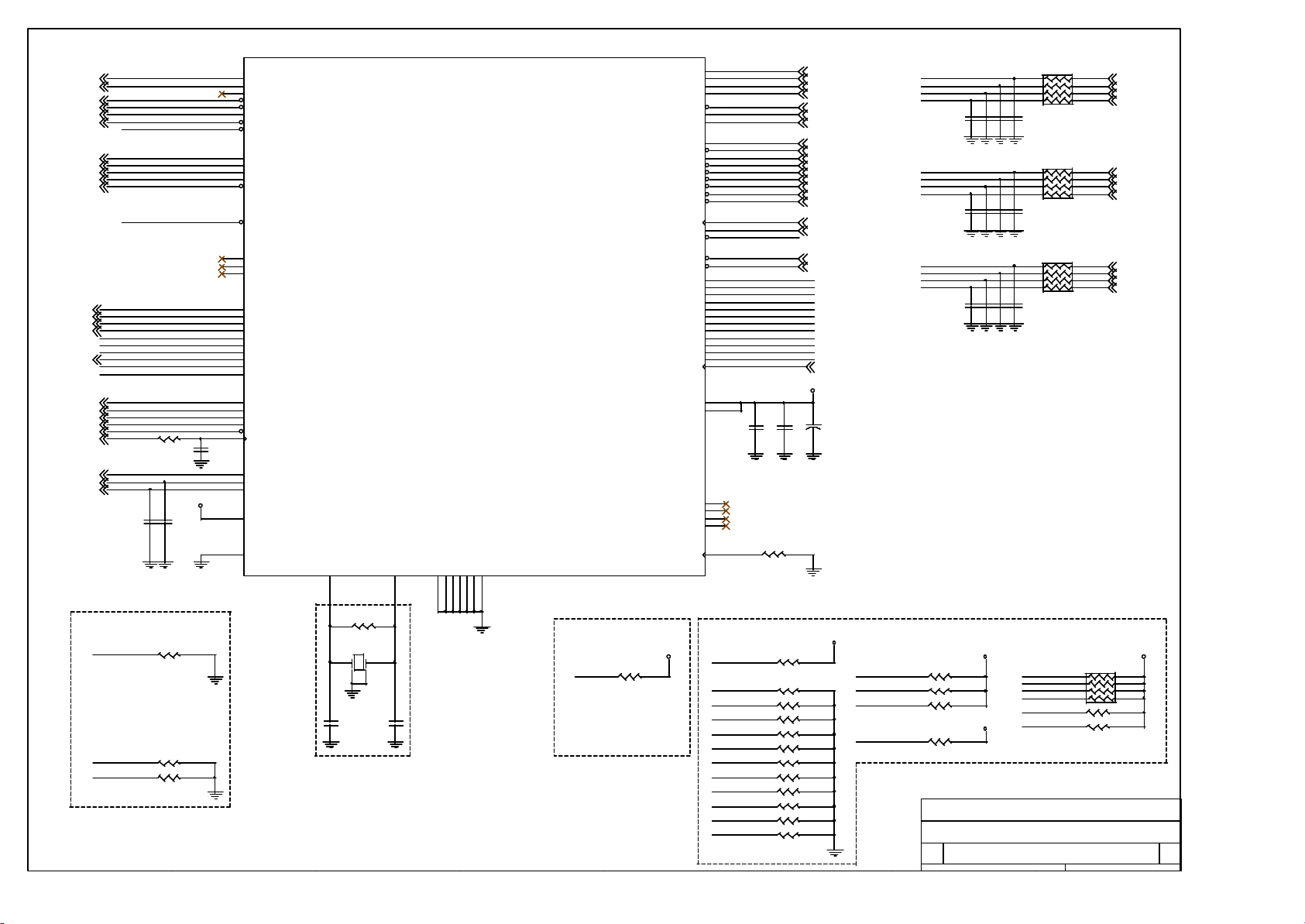

Page 7

8

AD[0..31]<16,17,18,36>

AD[0..31]

7

6

AD31 IDEDB0

AD30 IDEDB1

AD29 IDEDB2

AD28 IDEDB3

AD27 IDEDB4

AD26 IDEDB5

AD25 IDEDB6

AD24 IDEDB7

AD23 IDEDB8

AD22 IDEDB9

AD21 IDEDB10

AD20 IDEDB11

5

AD19 IDEDB12

AD18 IDEDB13

AD17 IDEDB14

AD16 IDEDB15

AD15

AD14 IDEDA0

AD13 IDEDA1

AD12 IDEDA2

AD11 IDEDA3

AD10 IDEDA4

AD9 IDEDA5

AD8 IDEDA6

AD7 IDEDA7

AD6 IDEDA8

AD5 IDEDA9

AD4 IDEDA10

AD3 IDEDA11

AD2 IDEDA12

AD1 IDEDA13

4

AD0 IDEDA14

IDEAVDD

3

1 2

FB-31-08

MC5

1US

2

VCC1.8V

L30

1

D D

U500B

AD18N4AE18

H6E4H5E3E2E1J5F4F3K6F2K5F1G3G2L5J2J1N6K4K3K2N5K1L2P6L1M4M3M2M1

AD9

AD31

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AD22

AD21

AD20

AD19

AD18

AD17

AD16

IDB10

AG12

IDB11

AJ12

IDB12

AF13

IDB13

AH13

IDB14

AJ13

AD15

IDB15

AH8

PREQ-2<16,36>

PREQ-1<16>

PREQ-0<16>

PGNT-2<16,36>

PGNT-1<16>

PGNT-0<16>

C C

FRAME-<16,17,18,36>

DEVSEL-<16,17,18,36>

730SPCLK<12>

PCIRST-<14,16,17,18,19,26,36>

730SPCLK

PREQ-2 ICHRDYA

PREQ-1 IDEREQA

PREQ-0 IDEIRQA

PGNT-2

PGNT-1 IDACK-A

PGNT-0

C/BE-3

C/BE-3<16,17,18,36>

C/BE-2 IDECS-A1

C/BE-2<16,17,18,36>

C/BE-1 IDECS-A0

C/BE-1<16,17,18,36>

C/BE-0

C/BE-0<16,17,18,36>

INT-A

INT-A<14,16,17,18>

INT-B ICHRDYB

INT-B<14,16,17,18>

INT-C IDEREQB

INT-C<16,17,18>

INT-D IDEIRQB

INT-D<16,17,18,36>

FRAMEIRDY- IDEIOR-B

IRDY-<16,17,18,36>

TRDY- IDEIOW-B

TRDY-<16,17,18,36>

STOP- IDACK-B

STOP-<16,17,18,36>

SERR- IDESAB2

SERR-<16,17,18,36>

PAR IDESAB1

PAR<16,17,18,36>

DEVSEL- IDESAB0

730SPCLK IDECS-B0

PCIRST-

C80

10P-06-O

R221

10-06

AJ16

F15

E12

G5

C1

F5

D1

G4

D2

J4

G1

J3

L3

N3

N2

N1

H4

H3

L4

H1

M5

H2

P_REQ#[2]

P_REQ#[1]

P_REQ#[0]

P_GNT#[2]

P_GNT#[1]

P_GNT#[0]

P_C/BE#[3]

P_C/BE#[2]

P_C/BE#[1]

P_C/BE#[0]

INTA#

INTB#

INTC#

INTD#

P_FRAME#

P_IRDY#

P_TRDY#

P_STOP#

P_SERR#

P_PAR

P_DEVSEL#

PCICLK

PCIRST#

PCI

IDB0

IDB1

IDB2

AE15

AG13

AD15

730S-2

IDB3

IDB4

IDB5

IDB6

IDB7

IDB8

AF12

AE14

AG11

AD14

AF11

AH11

IDB9

AJ11

AH12

AD14

IDA0

AE10

AD13

IDA1

AE8

AD12

IDA2

AH7

AD11

IDA3

AD10

IDE

IDA4

IDA5

AD10

AJ6

AE9

AD8

IDA6

AF6

P5

AD7

IDA7

AG6

AD0

AD6

AD5

AD4

AD3

AD2

AD1

IDEAVSS

IDEAVDD

IDA8

IDA9

IDA10

IDA11

IDA12

IDA13

IDA14

AH6

IDA15

AF7

AG7

AJ7

AF8

AG8

AE11

IDEDA15

ICHRDYA

IDREQ[A]

IIRQA

CBLIDA

IIOR#[A]

IIOW#[A]

IDACK#[A]

IDSAA[2]

IDSAA[1]

IDSAA[0]

IDECSA#[1]

IDECSA#[0]

ICHRDYB

IDREQ[B]

IIRQB

CBLIDB

IIOR#[B]

IIOW#[B]

IDACK#[B]

IDSAB[2]

IDSAB[1]

IDSAB[0]

IDECSB#[1]

IDECSB#[0]

SIS730S-O

AG9

AF9

AJ9

AH10

AH9

AJ8

AD12

AG10

AE12

AF10

AJ10

AE13

AH14

AE16

AE17

AH16

AG14

AF14

AJ14

AH15

AF15

AG15

AJ15

AD16

CBLIDA

IDEIOR-A

IDEIOW-A

IDESAA2

IDESAA1

IDESAA0

CBLIDB

IDECS-B1

ICHRDYA <19>

IDEREQA <19>

IDEIRQA <19>

CBLIDA <19>

IDEIOR-A <19>

IDEIOW-A <19>

IDACK-A <19>

IDESAA[0..2]

IDECS-A[0..1]

ICHRDYB <19>

IDEREQB <19>

IDEIRQB <19>

CBLIDB <19>

IDEIOR-B <19>

IDEIOW-B <19>

IDACK-B <19>

IDESAB[0..2]

IDECS-B[0..1]

IDESAA[0..2] <19>

IDECS-A[0..1] <19>

IDESAB[0..2] <19>

IDECS-B[0..1] <19>

B B

INT-[A..D] ASSIGNMENT

INT-A

->

PCI SLOT1-INT-D, PCI SLOT2-INT-C

PCI SLOT3-INT-B, PCI SLOT4-INT-A

SiS301-INT-A

INT-B

->

PCI SLOT1-INT-A, PCI SLOT2-INT-D

PCI SLOT3-INT-C, PCI SLOT4-INT-B

INT-C

->

PCI SLOT1-INT-B, PCI SLOT2-INT-A

PCI SLOT3-INT-D, PCI SLOT4-INT-C

INT-D

->

PCI SLOT1-INT-C, PCI SLOT2-INT-B

A A

8

PCI SLOT3-INT-A, PCI SLOT4-INT-D

7

INT-D

INT-C

INT-A

INT-B

6

RN49

1 8

2 7

3 6

4 5

8.2K-8P4R

VCC3

5

4

3

IDEDA[0..15]

IDEDB[0..15]

Title

730S-2 (PCI/IDE)

Size Document Number Rev

730SA 1.1

B

Date: Sheet of

2

IDEDA[0..15] <19>

IDEDB[0..15] <19>

7 36Wednesday, September 05, 2001

1

Page 8

8

D D

ROUT APAR

ROUT<15>

GOUT

GOUT<15>

BOUT

BOUT<15>

VSYNC ST1

VSYNC<15>

HSYNC<15>

SSYNC<14>

C C

VOSCI<12>

DDC1DATA<15>

DDC1CLK<15>

R195 33-06

HSYNC ST2

R197 33-06

SSYNC

VOSCI ADSTB1

DDC1DATA ADSTB-0

DDC1CLK ADSTB-1

7

AAD0

AG1

A_AD0

A15

ROUT

A16

GOUT

B15

730SRSET PIPE730SVREF WBF730SCOMP

DCLKAVDD SBSTB

DCLKAVSS SBSTBECLKAVDD

ECLKAVSS

DACAVDDB AGPRCOMP

DACAVSSB

DACAVDDC AGPAVDDA

DACAVSSC

F18

E17

E19

D16

C16

B17

D12

B16

A17

E15

E14

F14

E13

D14

D15

C14

C15

BOUT

VRSET

VVREF

VCOMP

VSYNC

HSYNC

SSYNC

VOSCI

DDC1DATA

DDC1CLK

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

DACAVDDB

DACAVSSB

DACAVDDC

DACAVSSC

AF3

AAD1

A_AD1

AF2

AAD2

A_AD2

AF1

AAD3

A_AD3

AE4

AAD4

A_AD4

AE3

AAD5

A_AD5

AE2

AAD6

A_AD6

AE1

6

AAD7

A_AD7

AAD8

AD3

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AD2

AD1

AC5

AC4

AC3

AC2

AB6

AA2

AA1Y5Y4Y3Y2Y1W4W1V5V4V3V2V1U4U3R3R2R1T3T2T1

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16/B5

A_AD17/B2

A_AD18/B3

A_AD19/B0

730S-3

VGA/AGP

AAD20

AAD21

AAD22

A_AD20/B1

A_AD21/R1

AAD23

AAD24

A_AD22/R2

A_AD23/R3

A_AD24/R4

5

AAD25

AAD26

AAD27

A_AD25/R5

A_AD26/R6

A_AD27/R7

AAD28

AAD29

AAD30

A_AD28/G2

A_AD29/G0

A_AD30/G1

AAD31

A_AD31/G3

SBA0

SBA1

SBA2

SBA3

R4

SBA3/G7

SBA0/VBBLANK#

SBA2/DDC2CLK

SBA1/DDC2DATA

SIS730S

SBA4

SBA5

SBA4/G6

SBA6

U1

SBA5/G5

SBA6/G4

SBA7

SBA7

4

U5C

A_C/BE0

A_C/BE1

B4/A_C/BE2

R0/A_C/BE3

VBCAD/A_REQ#

B7/A_FRAME#

A_TRDY#

B6/A_IRDY#

A_STOP#

A_DEVSEL#

A_SERR#

VGCLK/A_GNT#

A_PAR

VBHCLK/RBF#

VBCTL1/PIPE#

VBCTL0/WBF#

VBHSYNC/ST0

VBVSYNC/ST1

VBCLK/ST2

AD_STB0

AD_STB1

AD_STB0#

AD_STB1#

SB_STB

SB_STB#

AGPCLK

AGPRCOMP

AGPAVDDA

AGPAVSSA

AGPAVDDB

AGPAVSSB

AGPVREF

AGPVSSREF

ACBE-0

AG2

ACBE-1

AC1

ACBE-2

AA3

ACBE-3

U2

AREQ-

R6

AFRAME-

AB2

ATRDY-

AB3

AIRDY-

W5

ASTOP-

AB5

ADEVSEL-

AB4

ASERR-

AA5

AGNT-

T6

Y6

RBF-

P4

P3

P2

ST0

U5

P1

R5

ADSTB0

AD4

W2

AD5

W3

T5

T4

730ACLK

AH3

AB1

AE6

AGPAVSSA

AD6

AGPAVDDB

AD8

AGPAVSSB

AE7

AA4

V6

3

AAD[0..31]

SBA[0..7]

ACBE-0 <14>

ACBE-1 <14>

ACBE-2 <14>

ACBE-3 <14>

AREQ- <14>

AFRAME- <14>

ATRDY- <14>

AIRDY- <14>

ASTOP- <14>

ADEVSEL- <14>

ASERR- <14>

AGNT- <14>

APAR <14>

RBF- <14>

PIPE- <14>

WBF- <14>

ST0 <14>

ST1 <14>

ST2 <14>

ADSTB0 <14>

ADSTB1 <14>

ADSTB-0 <14>

ADSTB-1 <14>

SBSTB <14>

SBSTB- <14>

730ACLK <12>

AGPREF <14>

2

AAD[0..31] <14>

SBA[0..7] <14>

730ACLK

C101

10P-06-O

1

PLACE THESE CIRCUITS CLOSE TO SiS 730S

B B

VCC3

730SRSET 730SVREF ECLKAVDD

R186

140-1-06

730SCOMP

DACAVDDC DACAVDDB DCLKAVDD

A A

MC4

1US

BC84

.01U-06

1 2

FB-120-08

MC3

1US

8

BC79

.1U-06

ECLKAVSS

VCC3

L26

TC32

+

100U-25E

DACAVSSB

BC87

.01U-06

BC88

.01U-06

7

L28

1 2

FB-120-08

BC89

.1U-06

VCC3 VCC3

L29

1 2

FB-120-08

BC90

.1U-06

DCLKAVSS

BC86

.01U-06

6

BC85

.1U-06

5

L27

1 2

FB-120-08

PLACE THESE CIRCUITS CLOSE TO SiS 730S

BC117

.1U-06

3

L33

1 2

FB-120-08

AGPAVDDA AGPAVDDB

BC116

.01U-06

AGPAVSSA

VDDQ

R288

60.4-1-06

AGPRCOMP

4

VCC3 VCC3

AGPAVSSB

Title

730S-3 (VGA/DFP)

Size Document Number Rev

730SA 1.1

B

Date: Sheet of

2

BC122

.1U-06

L35

1 2

FB-120-08

TC43

100U-25E

+

8 36Wednesday, September 05, 2001

1

Page 9

8

PME-

KBDAT

KBCLK

PMDAT

PMCLK

KLOCK-

TXD0

TXD1

TXD2

RXER

TXCLK

COL

CRS

GPIO7

MDC

RXCLK

SDATI1

SDATI0

AUXOK

BATOK

PWRGD

BC96

.1U-06

SPKR

PSON-

EXTSMIPWRBTNRING

PMETHERM-

ENTEST

R307

0-06

C84

100P-06

RTCVDD

SPKR<30>

PSON-<34>

EXTSMI-<30>

PWRBTN-<30>

,16,17,18,26,36>

RING<27>

D D

KBDAT<25>

KBCLK<25>

PMDAT<25>

PMCLK<25>

KLOCK-<30>

PREQ-3<16,18>

PGNT-3<16,18>

EN_RSTSW<30>

CNR_DWEN

C C

GPIO7<35>

SDATI1<23>

SDATI0<21,23>

SDATO<21,23>

SYNC<21,23>

AC_RST-<23,31>

BIT_CLK<21,23>

AUXOK<24>

BATOK<24>

PWRGD<30,34>

B B

C79

10P-06-O

7

C13

SPK

B8

PSON#

E8

ACPILED

B13

EXTSMI#

F8

PWRBTN#

D8

RING

C8

PME#

A13

THERM#

A8

KBDAT/G10

E9

KBCLK/G11

D9

PMDAT/G12

C9

PMCLK/G13/GREEN

B9

KLOCK#/G14/TXD3

M6

ENTEST

AF4

NC1

AH2

NC2

D13

G0/PREQ#3/TXD0

E16

G1/PGNT#3/TXD1

A12

G2/LDRQ1/TXD2

E10

G3/RXER

C11

G4/TXCLK

D11

G5/COL

A7

G6/CRS

B12

G7/SPDIF/GREEN#

A9

G8/MDC

A10

G9/RXCLK

B11

AC_SDIN[1]

F12

AC_SDIN[0]

A14

AC_SDOUT

F16

AC_SYNC

A11

AC_RESET#

B14

AC_BIT_CLK

C7

AUXOK

D6

BATOK

E6

PWROK

A6

RTCVDD

A5

RTCVSS

ACPI

KBC

GPIO

AC'97

RTC

OSC32KHI

B5

6

730S-4

OSC32KHO

VSSA

VSSB

VSSC

VSSD

VSSE

VSSF

B6

F13

VSSG

F17

N24

U24

AD17

AD13

U6

5

U5D

LPC

CPU

SMB

USB

4

LAD0

LAD1

LAD2

LAD3

LDRQ#

LFRAME#

SIRQ

SMI#

INTR

A20M#

INIT#

IGNNE#

FERR#

STPCLK#

CPURST#

SMBCLK

SMBDAT

SMBALT#/G15/TXE

OC0#/RXDVNC0

OC1#/MDIO

UV0+

UV0-

UV1+

UV1-

UV2+

UV2-

UV3+

UV3-

UV4+

UV4-

UV5+

UV5-

USBCLK48M

USBVDD

USBVDD

3

LAD0

AJ4

LAD1

AH4

LAD2

AF5

LAD3

AG5

LDRQ-

AH5

LFRAME-

AE5

SIRQ

AJ5

NMI

E21

NMI

SMI-

C17

INTR

A19

A20M-

D17

INIT-

E20

IGNNE-

C18

FERR-

B18

STPCLK-

A18

CPURST-

F20

SMBCLK

AJ3

SMBDAT

AG4

TXEN

F10

OC0-

E7AG3

OC1-

B7

USBP0+

D3

USBP0-

D4

USBP1+

C2

USBP1-

C3

USBP2+

F6

USBP2-

E5

USBP3+

A4

USBP3-

A3

USBP4+

C4

USBP4-

B4

USBP5+

D5

USBP5-

C5

UCLK48M

C12

B3

B2

BC115

.1U-06

LAD0 <26>

LAD1 <26>

LAD2 <26>

LAD3 <26>

LDRQ- <26>

LFRAME- <26>

SIRQ <26>

NMI <4>

SMI- <4>

INTR <4>

A20M- <4>

INIT- <4>

IGNNE- <4>

FERR- <4>

STPCLK- <4>

CPURST- <4>

SMBCLK <12,13>

SMBDAT <12,13>

OC0- <20>

OC1- <20,23>

SB3V

MC22

1US

UCLK48M <12>

12

TC37

10U-25SE

USBP0+

USBP0-

USBP1+

USBP1-

USBP2USBP2+

USBP3-

USBP3+

USBP4USBP4+

USBP5+

USBP5-

C97

22P-06

C91

100P-06

C86

22P-06

2

C98

100P-06 C99

C90

22P-06 C96

C85

100P-06 C87

22P-06

100P-06

100P-06

1 8

2 7

3 6

4 5

C100

100P-06

1 8

2 7

3 6

4 5

C95

22P-06

1 8

2 7

3 6

4 5

C88

22P-06

RN28

27-8P4R

RN27

27-8P4R

RN25

27-8P4R

1

UV0+ <23>

UV0- <23>

UV1+ <23>

UV1- <23>

UV2- <14,20>

UV2+ <14,20>

UV3- <20>

UV3+ <20>

UV4- <20>

UV4+ <20>

UV5+ <20>

UV5- <20>

MII

D10

RXD[0]

C10

RXD[1]

B10

RXD[2]

E11

RXD[3]

R493

LAN25MCLK

SIS730S

D7

10K-06

X-32.768K-CY

1 2

3 4

C94

10P-06

R271

10M-06

Y2

C89

10P-06

CLK select

TXD2

GPIO2

1->ICS94208EF

0->W83194BR-730

6

5

R220

4.7K-06-O

VCC3

GPIO7

R9

TXD0

R454

TXD1

R196 10K-06-O

TXD2

R223

RXER

R239

TXCLK

R235 10K-06-O

COL

R236

CRS

R260 10K-06-O

MDC

R241

RXCLK

R240

KLOCK-

R431 10K-06-O

TXEN

R237

4

4.7K-06

10K-06-O

10K-06-O

10K-06-O

10K-06-O

10K-06-O

10K-06-O

10K-06-O

VCC3

THERMSMBDAT

SMBCLK

PME-

R222 4.7K-06

R70

R77 4.7K-06

R444 4.7K-06

Title

Size Document Number Rev

Date: Sheet of

3

VCC3

LAD3

LAD2

SB3V

LAD1

LAD0

LDRQSIRQ

4.7K-06

730S-4 (SOUTH BRIDGE)

730SA 1.1

RN41

4.7K-8P4R

1 8

2 7

3 6

4 5

R400 4.7K-06

R397

2

VCC3

4.7K-06

9 36Wednesday, September 05, 2001

1

NEDD NOT to place

near to 730S

ENTEST

AC'97 Pull-Down

In order to stabilize

730S AC,97 controller

pull-down resistors on

SDATI1 and SDATI0 can

not be removed.

SDATI1

A A

SDATI0

8

R317

4.7K-06

R342 100K-06

R343 100K-06

Place close to SiS730S

7

Page 10

8

7

6

5

4

3

2

1

VCC3

D D

MC15

1US

BC148

.1U-06

BC139

.1U-06

BC92

.1U-06

VCC1.8V

MC23

MC26

BC91

.1U-06

BC160

.1U-06

BC175

.1U-06

1US

1US

C C

MC16

1US

MC14

1US

MC10

1US

BC132

.1U-06

BC133

.1U-06

B B

Under NB

VCC1.8V

MC44

1US

MC43

1US

MC40

1US

MC42

A A

1US

VCC3

MC45

1US

MC46

1US

MC39

1US

MC41

1US

VDDQ

VCC_CORE

BC106

.1U-06

BC107

.1U-06

BC108

.1U-06

BC130

.1U-06

BC71

.1U-06

BC66

.1U-06

BC69

.1U-06

BC109

.1U-06

BC110

.1U-06

BC111

.1U-06

BC143

.1U-06

MC30

1US

SB3V SB1.8V

MC9

1US

MC17

1US

VCC1.8V

VCC3 VDDQ

J9

OVDD

J11

OVDD

J12

OVDD

K8

OVDD

K9

OVDD

M9

OVDD

AA11

OVDD

AA12

OVDD

AA13

OVDD

AB12

OVDD

H17

OVDD

U21

OVDD

U22

OVDD

V21

OVDD

V22

OVDD

W21

OVDD

W22

OVDD

Y21

OVDD

AA18

OVDD

AA19

OVDD

AB21

OVDD

AA20

OVDD

AA22

OVDD

AB19

OVDD

AB22

OVDD

AB10

PVDD

AB11

PVDD

H11

PVDD

H12

PVDD

L8

PVDD

M8

PVDD

H18

PVDD

AB18

PVDD

AB20

PVDD

AB13

PVDD

Y22

PVDD

T22

PVDD

J18

S2KPVDD

N22

S2KPVDD

J20

IVDD

AA10

IVDD

U9

IVDD

N9

IVDD

L9

IVDD

J10

IVDD

H13

IVDD

AB14

IVDD

H16

IVDD

AA14

IVDD

J16

IVDD

J17

IVDD

J13

IVDD

J19

IVDD

K21

IVDD

L21

IVDD

M21

IVDD

N21

IVDD

T21

IVDD

AA21

IVDD

AA17

IVDD

AB17

IVDD

H9

AUX3.3V

J8

AUX1.8V

N8P8P9U8V8V9W8W9Y8Y9AA8

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

730S-5

POWER

VDDQ

AA9

VDDQ

AB8

VDDQ

AB9

VDDQ

VDDQ

H19

H21

S2KOVDD

H22

J21

S2KOVDD

S2KOVDD

S2KOVDD

H20

J22

S2KOVDD

VCC_CORE

K22

L22

M22

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

SIS730S

VSSQOVDD

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

VSSD

U5E

P11H10

P12

P13

U11

U12

U13

R11

R12

R13

T11

T12

T13

V12

V13

W17

W16

V18

P16

P17

R16

R17

R18

R19

T16

T17

T18

T19

U16

U17

U18

U19

V16

V17

U15

VSS

V14

VSS

N13

VSS

U14

VSS

W15

VSS

L13

VSS

L14

VSS

L15

VSS

L16

VSS

L17

VSS

M12

VSS

M13

VSS

M14

VSS

M15

VSS

M16

VSS

M17

VSS

M18

VSS

N11

VSS

N12

VSS

N14

VSS

N15

VSS

W13

VSS

T15

VSS

N16

VSS

N17

VSS

N18

VSS

N19

VSS

P14

VSS

P15

VSS

P18

VSS

P19

VSS

R14

VSS

R15

VSS

T14

VSS

V15

VSS

W14

VSS

Title

730S-5 (POWER)

Size Document Number Rev

730SA 1.1

B

Date: Sheet of

8

7

6

5

4

3

2

10 36Wednesday, September 05, 2001

1

Page 11

8

MD63: SIP mode

1:Debug Mode

0:Production Mode

MD62: PCI Clock PLL Enable

1:Disable

0:Enable

MD61: SDRAM Clock DLL Enable

D D

C C

1:Disable

0:Enable

MD60: CPU Clock DLL Enable

1:Disable

0:Enable

MD[59..58]: DLL ER[1..0]

MD[57..56]: PLL ER[1..0]

MD54: AGP PLL Enable

MD53: Clock Forward Offset

0:Delay 1000ps

1:No Delay

MD45: IDE Clock Control

1:PLL By-pass

0:From the PLL clock

MD[44..42]: TCLK Delay

MD41: Receiver Delay Enable

1:NB forward clock delay mode

0:Processor forward clock delay mode

MD40: Enable/Disable Auto Reset Function

1:Disable

0:Enable

MD38: VGA Interrupt Function

1:Enable

0:Disable

MD37: Enable External CLock Generator

MD35: VGA Multi-Function Select

MD34: Enable Multi-Function

MD32: PAL/NTSC Select

1:PAL

0:NTSC

MD36 MD33: Function

0 0 Enable Frame Buffer Cache

0 1 Enable SiS301 Video Bridge

1 0 Enable other Panel Link Chip

1 1 Enable other TV-OUT Encoder

*These H/W traps have internal pull-down resistors.

MD[31..29]: Reserved/SysDCDelay(DL)

B B

MD[28..26]: Reserved/SysAddRecMuxPreload(AM)

MD25: PPMODE (S2K I/O buffer mode control

*

1:Push/Pull--SocketA

0:Open Drain--SlotA

MD24: PUE(Internal Pull-up Resistor Enable)

1:Turn off the internal pull-up resistors

0:Normal open drain internal resistor pull-up scheme

MD23 MD22: S2K bus length/NBDataInitCnt(DIC)

0 0 Shor t

0 1

1 0

1 1 Long

A A

MD21 MD20: System clock speed/NBSysDCOutDelay(DCO)

0 0 100MH z

0 1 66MH z

1 0 90MH z

1 1 133Mh z

(Recommend value is 0)

(Default 00)

(Default 00)

--Depends on SIP mode

1:Debug Mode--SysDCDelay(DL)

0:Production Mode--Reserved

(Recommend value is 0)

--Depends on SIP mode

1:Debug Mode--SysAddRecMuxPreload(AM)

0:Production Mode--Reserved

(Recommend value is 0)

--Depends on SIP mode

1:Debug Mode--NBDataInitCnt(DIC)

0:Production Mode--S2K bus length

--Depends on SIP mode

1:Debug Mode--NBSysDCOutDelay(DCO)

0:Production Mode--System clock speed

8

7

MD[0..63]

MD[0..63]<6,13>

7

6

MD55

R108 4.7K-06-O

MD54

R110

MD53

MD45

MD44

MD43

MD42

MD41

MD40

MD38

MD46

*

MD36 ENEXTPL

MD35

MD34

MD33 ENVB

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

*

MD24

MD23

MD22

MD21

MD20

4.7K-06-O

R111

4.7K-06-O

R177 4.7K-06-O

R192 4.7K-06-O

R199 4.7K-06-O

R169

4.7K-06-O

R198

4.7K-06-O

R206 4.7K-06-O

R225 4.7K-06-O

R178 4.7K-06

R266

4.7K-06-O

R265 4.7K-06-O

R276 4.7K-06-O

R83 4.7K-06-O

R92

4.7K-06-O

R93 4.7K-06-O

R91

4.7K-06-O

R98 4.7K-06-O

R97

4.7K-06-O

R99

4.7K-06

R106 4.7K-06-O

R107

4.7K-06-O

R112 4.7K-06-O

R109

4.7K-06-O

R116

4.7K-06-O

6

5

VCC3

VCC3

R250

4.7K-06-O

R279

4.7K-06-O

VCC3

MD15: Receive clock delay control mode

1:Use hardware trap value (MD[14..11])

0:Use DLL control value

MD[14..11]: Receive Forward Clock Delay Control

MD[10..9]: SLEW (Output Slew Rate Control Value)

*

MD8: S2K Output Buffer Driving Strength Control Mode

*

0: Use conpensation logic control value

1: Use hardware-trap value(MD[3..0] and MD[7..4])

MD[7..4]: S2K Output Buffer NMOS Driving Strength Control value

*

MD[3..0]: S2K Output Buffer PMOS Driving Strength Control value

*

5

FOR SOCKETA

MD16

MD17

MD18

MD19

R249

4.7K-06-O

R277

4.7K-06-O

0000:minimum delay

1111:maximum delay

00:minimum slew rate

11:maximum slew rate

0000:minimum driving strength

1111:maximum driving strength

1111:minimum driving strength

0000:maximum driving strength

4

R119

4.7K-06

R121

4.7K-06

R120

4.7K-06

R115

4.7K-06

ENEXTPL <14>

4

R139

R145

4.7K-06

4.7K-06

R124

4.7K-06

R117

4.7K-06

2N7002

1

G

MD[19..16]: CPU clock divider/NBSysDCInDelay(DCI)

11.0

ENVB <14>

VCC5 VCC2.5V

R146 120-06

R150 120-06

TC20

+

100U-25E

11.5

12.0

12.5

5.0

5.5

6.0

6.5

7.0

7.5

8.0

8.5

9.0

9.5

10.0

10.5

D12

LM431

DIP

1

2 3

1 2 3

TL-431

TOP VIEW (DIP)

VCC2.5VVCC3

3

R144

10K-06

R140

10K-06

32

32

32

32

3

Q30

PH2N7002-S

1

Q29

PH2N7002-S

1

Q28

PH2N7002-S

1

Q27

PH2N7002-S

1

D

R122

10K-06

N-CH

2

S

--Depends on SIP mode

1:Debug Mode--NBSysDCInDelay(DCI)

0:Production Mode--CPU clock divider

MD19 MD18 MD17 MD16

(FID2) (FID0)(FID1)(FID3)

0 0 0 0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

*

*

BC56

680P-06

*

*

*

*

CAREF

Title

VID/FID

Size Document Number Rev

730SA 1.1

B

Date: Sheet of

3

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

2

R141

10K-06

2

R123

10K-06

FID0

FID1

FID2

FID3

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

R175

4.7K-06-O

R176

4.7K-06-O

R191 4.7K-06-O

R190

4.7K-06-O

R170 4.7K-06-O

R200

4.7K-06-O

R205

4.7K-06

R208 4.7K-06

R207

4.7K-06-O

R224 4.7K-06

R226

4.7K-06

R251

4.7K-06-O

R268 4.7K-06

R267

4.7K-06

R278 4.7K-06-O

R264

4.7K-06-O

1

TO CPU

FID[0..3] <4>

VCC3

MD[0..7] -> 6C

MD[0..7] -> 5D

11 36Wednesday, September 05, 2001

1

Page 12

1

2

3

4

5

6

7

8

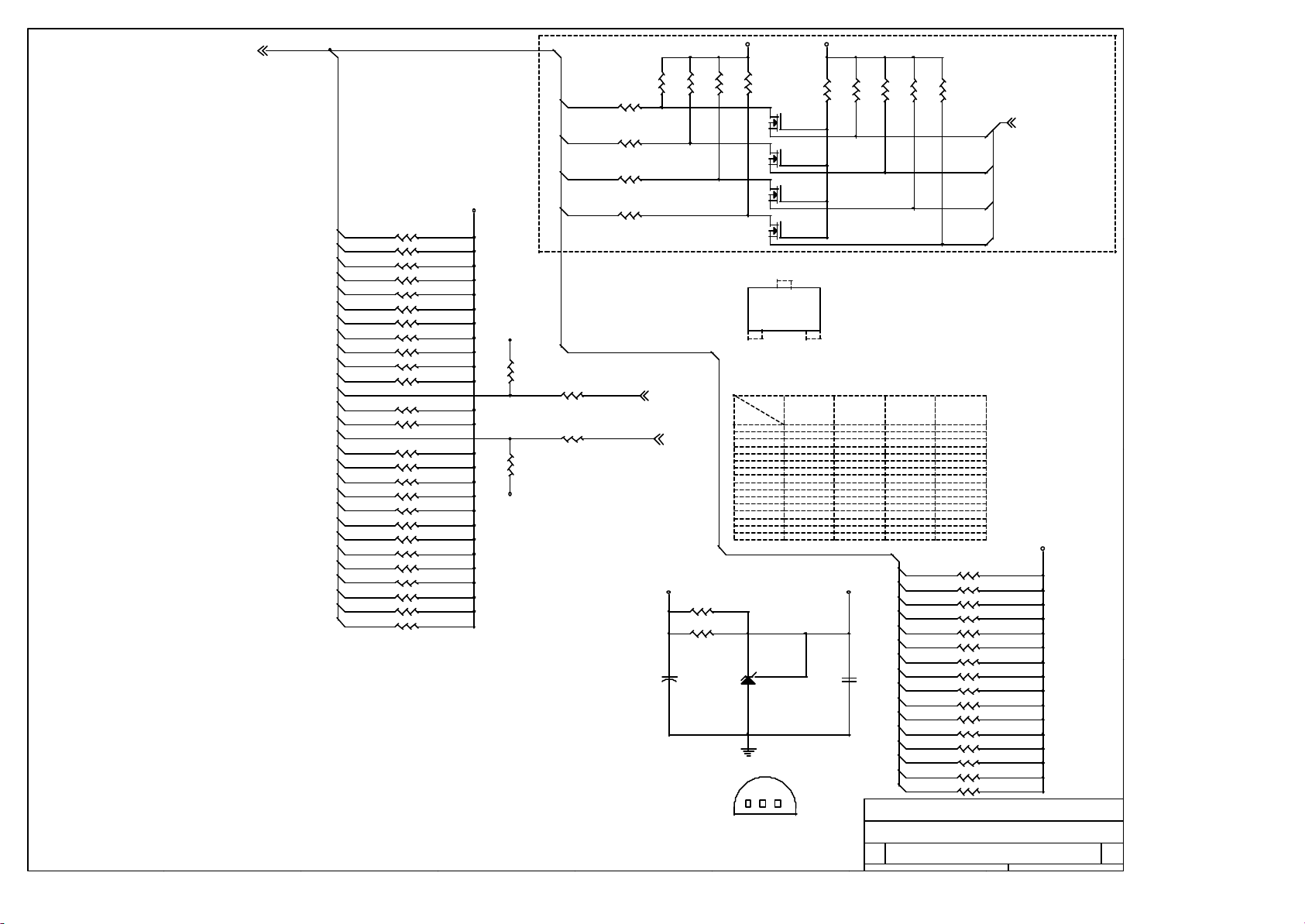

Clock Generator

A A

VCC3

L13

FB-31-08

VCC3

L15

FB-31-08

TC11

+

100U-25E

BC34

.1U-06

VCC3_CLK PCICLK2

TC16

B B

+

100U-25E

BC49

.1U-06

BC50

.1U-06

BC51

.1U-06

BC52

.1U-06

SMBDAT<9,13>

SMBCLK<9,13>

BC31

BC30

.1U-06

BC29

.1U-06

.1U-06

SMBDAT

SMBCLK 730SDCLK

VCC3

TC19

+

C57

C C

100U-25E

470P-06

BC39

.01U-06

(5 OPTIONS)

1: ICS94208EF (ICS) ICS9248AF-136

2: W83194BR-730 (Winbond)

3: ICW247 (IC Works)

4: C9730 (IMI)

5: FS6221-01 (AMI)

CLK1

ICS94208EF

48

VDDCPU

BC28

.1U-06

44

GNDCPU

1 10

VDDREF PCICLK2

7

VDDPCI

22

VDD48

43

VDDSDR

35

VDDSDR

25

VDDSDR

15

VDDAGP

4

GNDREF

14

GNDPCI

19

GND48

29

GNDSDR

32

GNDSDR

39

GNDSDR

18

GNDAGP

23

SDATA

24

SCLK

X1

5

Y1

X-14.318M

C45

10P-06

^CPUCS_C1

^CPUC0

^CPUT0

AGPCLK1

AGPCLK0

PCICLK5

PCICLK4

PCICLK3

*FS2/PCICLK1

*FS1/PCICLK_F

FS3/*REF0

AGPSEL/*REF1

*MODE/24_48MHZ

48MHZ/FS0

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

PD#/SDRAM8

SDRSTP#/SDRAM9

PCISTP#/SDRAM10

CPUSTP#/SDRAM11

SDRAM12

X2

6

C44

10P-06

45

47

46

17

16

13

12

11

FS2 LANPCLK

9

FS1

8

FS3 VOSCI

3

2

AGPSEL

MODE SIO48M

21

20

FS0 UCLK48M

42

41

40

38

37

36

34

33

31

30

28

27

26

R100 0-06

R102 10-06

R101 10-06

R132 22-06

R131 22-06

R533 33-06

RN13C 33-8P4R3 6

R130 33-06

R510 33-06

1 8

RN13A 33-8P4R

RN13B 33-8P4R2 7

R494 33-06

RN13D 33-8P4R4 5

R495 33-06

R126 22-06

R134 22-06

R133 22-06

RN9

1 8

2 7

3 6

22-8P4R

4 5

1 8

RN10

2 7

3 6

4 5

22-8P4R

R103

22-06

730SCCLK

CPUCLK

CPUCLK-

AGPCLK

730ACLK

AT123SCLK

PCICLK1

SIOPCLK

PCICLK4

PCLCLK3

730SPCLK

PCICLK5

SDCLK0

SDCLK1

SDCLK2

SDCLK3

SDCLK4

SDCLK5

SDCLK6

SDCLK7

730SCCLK <6>

CPUCLK <3>

CPUCLK- <3>

AGPCLK <14>

730ACLK <8>

AT123SCLK <18>

PCICLK1 <16>

SIOPCLK <26>

PCICLK4 <17>

PCICLK3 <17>

PCICLK2 <16>

LANPCLK <36>

730SPCLK <7>

PCICLK5 <18>

VOSCI <8>

SIO48M <26>

UCLK48M <9>

SDCLK0 <13>

SDCLK1 <13>

SDCLK2 <13>

SDCLK3 <13>

SDCLK4 <13>

SDCLK5 <13>

SDCLK6 <13>

SDCLK7 <13>

730SDCLK <6>

TO SiS950

By-Pass Capacitors

Place near to the Clock Generator

AT123SCLK

730SCCLK

CPUCLKCPUCLK

AGPCLK

730ACLK

LANPCLK

730SDCLK

PCICLK4PCICLK5

12

C137

10P-06-O

UCLK48M

VOSCI

730SPCLK

PCICLK1

PCICLK2

SIOPCLK

12

C54

10P-06-O

SDCLK0

SDCLK1

SDCLK2

SDCLK3

12

C37

10P-06-O

C291

C31 10P-06-O

C33 10P-06-O

C55 10P-06-O

C288 10P-06-O

C42 10P-06-O

12

C138

10P-06-O

12

12

C51

C52

10P-06-O

10P-06-O

12

10P-06-O

10P-06-O

C32 10P-06-O

C46 10P-06-O

12

C53

10P-06-O

12

C50

10P-06-O

C36

12

12

C35

10P-06-O

SIO48MPCICLK3

C49

10P-06-O

12

C47

10P-06-O

12

C34

10P-06-O

12

C56

10P-06-O

SiS 730S CLOCK

100

133

150

66.6

112

100

124

100

133

150

166

165

166

90

48

60

PCISDRAM

(MHz)(MHz)(MHz)

33.3

33.3

30

33.3

33.6

31.3

31

33.3

33.3

30

33.3

33

33.3

30

32

30

NOTE:

PCICLK<34.5MHz

2

AGPCLK (MHz)

AGPSEL=0 AGPSEL=1

66.6

66.6

60

66.6

67.2

62.5

62

66.6

66.6

60

66.6

66

66.6

60

64

60

50

50

50

50

56

50

46.5

50

50

50

55.6

55

55.6

45

48

45

3

0

CPUFS0FS1FS2FS3

0

0

0

*

0

0

0

0

0

0

0

0

1

*

1

1

1

1

D D

1

1

1

0

0

1

0

1

1

0

1

0

1

1

1

1

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

1

100

1

100

0

100

1

100

0

112

1

125

0

124

1

133

0

133

1

150

0

111

1

110

0

166

1

90

0

48

1

45

VCC3

Freqyency Selection

R125 4.7K-06-O

R142 4.7K-06-O

R128 4.7K-06-O

R129 4.7K-06-O

R127 4.7K-06-O

R143 4.7K-06-O

4

AGPSEL

FS0

FS1

FS2

FS3

MODE

5

SDCLK4

SDCLK5

SDCLK6

SDCLK7

12

12

12

6

C41

10P-06-O

C40

10P-06-O

12

C39

C38

10P-06-O

10P-06-O

Title

Clock Generators (5 Options)

Size Document Number Rev

730SA 1.1

Custom

Date: Sheet of

7

12 36Wednesday, September 05, 2001

8

Page 13

8

MD[0..63]<6,11>

MA[0..14]<6>

DQM[0..7]<6>

D D

V_DIMM

C C

B B

DIMM DECOUPLING

place around DIMM1,2

LED-RD

BC11

.1U-06

BC20

.1U-06

BC47

.1U-06

BC58

.1U-06

BC76

.1U-06

BC93

.1U-06

RAMW-<6>

SDCLK0<12>

SDCLK1<12>

SDCLK2<12>

SDCLK3<12>

SMBCLK<9,12>

SMBDAT<9,12>

SRAS-<6>

SCAS-<6>

CKE0<32>

CKE1<32>

BC10

.1U-06

BC19

.1U-06

BC38

.1U-06

BC54

.1U-06

BC55

.1U-06

BC81

.1U-06

V_DIMM

12

R29

330-06

LED1

1 2

INDICATE STABDBY POWER

7

MD[0..63]

MA[0..14]

DQM[0..7]

DIMM DECOUPLING

MA0 MA0

MA1 MD0 MA1 MD0

MA2 MD1 MA2 MD1

MA3 MD2 MA3 MD2

MA4 MD3 MA4 MD3

MA5 MD4 MA5 MD4

MA6 MD5 MA6 MD5

MA7 MD6 MA7 MD6

MA8 MD7 MA8 MD7

MA9 MA9

MA10 MD8 MA10 MD8

MA13 MD9 MA13 MD9

MA14 MD10 MA14 MD10

MA11 MD12 MA11 MD12

R137

0-06

SRAS- MD34 SRAS- MD34

SCAS- MD35 SCAS- MD35

RAMW- MD41 RAMW- MD41

SDCLK0

SDCLK1

SDCLK2

SDCLK3

SMBCLK MD51 SMBCLK MD51

SMBDAT MD52 SMBDAT MD52

MA12 MD13 MA12 MD13

DQM0 MD17 DQM0 MD17

DQM1 MD18 DQM1 MD18

DQM2 MD19 DQM2 MD19

DQM3 MD20 DQM3 MD20

DQM4 MD21 DQM4 MD21

DQM5 MD22 DQM5 MD22

DQM6 MD23 DQM6 MD23

DQM7 DQM7

CSA-0 MD37 CSA-2 MD37

CSA-1 MD38 CSA-3 MD38

CSB-0 MD39 CSB-2 MD39

CSB-1 CSB-3

CKE0

CKE1

6

V_DIMM V_DIMM

TC27

+

100U-25E

33

117

34

118

35

119

36

120

37

121

38

123

126

122

39

132

28

29

46

47

112

113

130

131

21

22

52

53

105

106

136

137

115

111

30

114

45

129

27

48

42

125

79

163

128

63

83

82

165

166

167

147

24

25

50

31

44

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]/AP

A[11]

A[12]

BA[0]

BA[1]

A[13]

DQM[0]

DQM[1]

DQM[2]

DQM[3]

DQM[4]

DQM[5]

DQM[6]

DQM[7]

CB[0]

CB[1]

CB[2]

CB[3]

CB[4]

CB[5]

CB[6]

CB[7]

SRAS#

SCAS#

S#[0]

S#[1]

S#[2]

S#[3]

WE0#

WE2#

CK[0]

CK[1]

CK[2]

CK[3]

CKE[0]

CKE[1]

SCL

SDA

SA[0]

SA[1]

SA[2]

REOE/NC

NC

NC

NC

NC/OE#0

NC/OE#2

NCNCNC

616280

VCC3

VCC3

VCC3

addr =

1010000b

VSS

NC

1

12

108

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VSS

VSS

VSS

VSS

VSS

VSS

43647896116

68

543223

1029084735949414026186

VCC3

VSS

110

VCC3

VSS

85

124

VCC3

VSS

133

VCC3

VSS

107

143

VCC3

VSS

157

VCC3

VSS

127

168

VCC3

VSS

138

5

VCC3

VSS

148

WP/NC

DQ[10]

DQ[11]

DQ[12]

DQ[13]

DQ[14]

DQ[15]

DQ[16]

DQ[17]

DQ[18]

DQ[19]

DQ[20]

DQ[21]

DQ[22]

DQ[23]

DQ[24]

DQ[25]

DQ[26]

DQ[27]

DQ[28]

DQ[29]

DQ[30]

DQ[31]

DQ[32]

DQ[33]

DQ[34]

DQ[35]

DQ[36]

DQ[37]

DQ[38]

DQ[39]

DQ[40]

DQ[41]

DQ[42]

DQ[43]

DQ[44]

DQ[45]

DQ[46]

DQ[47]

DQ[48]

DQ[49]

DQ[50]

DQ[51]

DQ[52]

DQ[53]

DQ[54]

DQ[55]

DQ[56]

DQ[57]

DQ[58]

DQ[59]

DQ[60]

DQ[61]

DQ[62]

DQ[63]

VSS

152

DQ[0]

DQ[1]

DQ[2]

DQ[3]

DQ[4]

DQ[5]

DQ[6]

DQ[7]

DQ[8]

DQ[9]

VSS

4

V_DIMM V_DIMM

DIMM1

R81

2.2K-06

81

2

3

4

5

7

8

9

10

164

NC

11

13

14

MD11 MD11

15

NC

NC

NC

NC

NC

NC

VSS

162

16

17

MD14 MD14

19

MD15 MD15

20

51

MD16 MD16

55

56

57

58

60

65

66

67

146

MD24 MD24

69

MD25 MD25

70

MD26 MD26

71

MD27 MD27

72

MD28 MD28

74

MD29 MD29

75

MD30 MD30

76

MD31 MD31

77

145

MD32 MD32

86

MD33 MD33

87

88

89

MD36 MD36

91

92

93

94

135

MD40 MD40

95

97

MD42 MD42

98

MD43 MD43

99

MD44 SDCLK4 MD44

100

MD45 MD45

101

MD46 SDCLK6 MD46

103

MD47 SDCLK7 MD47

104

134

MD48 CKE3 MD48

139

MD49 MD49

140

MD50 MD50

141

142

144

MD53 MD53

149

MD54 MD54

150

MD55 MD55

151

109

MD56 MD56

153

MD57 MD57

154

MD58 MD58

155

MD59 MD59

156

MD60 MD60

158

MD61 MD61

159

MD62 MD62

160

MD63 MD63

161

DIMM-168P1R-FOX

SDCLK4<12>

SDCLK5<12>

SDCLK6<12>

SDCLK7<12>

CKE2<32>

CKE3<32>

R84

8.2K-06

R138

0-06

V_DIMM

SDCLK5

CKE2

3

VCC3

VCC3

33

A[0]

117

A[1]

34

A[2]

118

A[3]

35

A[4]

119

A[5]

36

A[6]

120

A[7]

37

A[8]

121

A[9]

38

A[10]/AP

123

A[11]

126

A[12]

122

BA[0]

39

BA[1]

132

A[13]

28

DQM[0]

29

DQM[1]

46

DQM[2]

47

DQM[3]

112

DQM[4]

113

DQM[5]

130

DQM[6]

131

DQM[7]

21

CB[0]

22

CB[1]

52

CB[2]