Page 1

®

FT 3120®/ FT 3150

Smart Transceiver Data Book

@®

005-0139-01D

Page 2

Echelon, LON, LONWORKS, Neuron, 3120, 3150, LonTalk, NodeBuilder, LNS,

LonMaker, i.LON, and the Echelon logo are trademarks of Echelon Corporation

registered in the United States and other countries.

Other brand and product names are trademarks or registered trademarks of their

respective holders.

Smart Transceivers, Neuron Chips, and other OEM Products were not designed

for use in equipment or systems which involve danger to human health or safety

or a risk of property damage and Echelon assumes no responsibility or liability

for use of the Smart Transceivers or Neuron Chips in such applications.

Parts manufactured by vendors other than Echelon and referenced in this

document have been described for illustrative purposes only, and may not have

been tested by Echelon. It is the responsibility of the customer to determine the

suitability of these parts for each application

ECHELON MAKES AND YOU RECEIVE NO WARRANTIES OR

CONDITIONS, EXPRESS, IMPLIED, STATUTORY OR IN ANY

COMMUNICATION WITH YOU, AND ECHELON SPECIFICALLY

DISCLAIMS ANY IMPLIED WARRANTY OF MERCHANTABILITY OR

FITNESS FOR A PARTICULAR PURPOSE.

No part of this publication may be reproduced, stored in a retrieval system, or

transmitted, in any form or by any means, electronic, mechanical, photocopying,

recording, or otherwise, without the prior written permission of Echelon

Corporation.

.

Printed in the United States of America.

Copyright ©2002-2006 by Echelon Corporation.

Echelon Corporation

www.echelon.com

Page 3

Table of Contents

Chapter 1 - Introduction ......................................................................................1

Introduction .......................................................................................................2

Audience ...........................................................................................................2

Product Overview .............................................................................................2

Free Topology Technology Overview ..............................................................4

Related Documentation .....................................................................................5

Chapter 2 - Hardware Resources ........................................................................7

Overview ...........................................................................................................8

Neuron Processor Architecture .........................................................................8

Memory Allocation .........................................................................................13

FT 3120 Smart Transceiver ......................................................................13

FT 3150 Smart Transceiver ......................................................................13

EEPROM ..................................................................................................14

Static RAM ...............................................................................................16

Preprogrammed ROM ...............................................................................16

External Memory of the FT 3150 Smart Transceiver ...............................16

Input/Output ...................................................................................................17

Eleven Bidirectional I/O Pins ...................................................................17

Two 16-Bit Timer/Counters ......................................................................17

Clock Input .....................................................................................................18

Clock Generation ......................................................................................18

Additional Functions .......................................................................................19

Reset Function ..........................................................................................19

RESET Pin ................................................................................................20

Power Up Sequence ............................................................................20

Software Controlled Reset ..................................................................21

Watchdog Timer .................................................................................21

LVI Considerations .............................................................................21

Reset Processes and Timing .....................................................................22

SERVICE

Integrity Mechanisms .....................................................................................28

Memory Integrity Using Checksums ........................................................28

Reboot and Integrity Options Word ..........................................................29

Reset Processing .......................................................................................30

Signatures ..................................................................................................30

Pin ...........................................................................................27

Chapter 3 - Input/Output Interfaces ................................................................31

Overview .........................................................................................................32

Hardware Considerations ................................................................................33

I/O Timing Issues ............................................................................................37

Scheduler-Related I/O Timing Information ..............................................38

Firmware and Hardware-Related I/O Timing Information .......................39

FT 3120 / 3150 Smart Tranceiver Data Book i

Page 4

Table of Contents

Direct I/O Objects ..........................................................................................40

Bit Input/Output ........................................................................................40

Byte Input/Output .....................................................................................41

Leveldetect Input ......................................................................................43

Nibble Input/Output ..................................................................................44

Parallel I/O Objects ........................................................................................45

Muxbus Input/Output ................................................................................45

Parallel Input/Output .................................................................................46

Master/Slave A Mode .........................................................................47

Slave B Mode ......................................................................................51

Token Passing .....................................................................................52

Handshaking .......................................................................................53

Data Transferring ................................................................................54

Serial I/O Objects ...........................................................................................57

Bitshift Input/Output .................................................................................57

I2C Input/Output .......................................................................................59

Magcard Input ...........................................................................................60

Magtrack1 Input ........................................................................................62

Neurowire (SPI Interface) Input/Output Object .......................................63

Neurowire Master Mode .....................................................................63

Neurowire Slave Mode .......................................................................64

Serial Input/Output ...................................................................................66

Touch Input/Output ...................................................................................67

Wiegand Input ...........................................................................................69

Timer/Counter Input Objects ..........................................................................70

Dualslope Input .........................................................................................71

Edgelog Input ............................................................................................72

Infrared Input ............................................................................................73

Ontime Input .............................................................................................74

Period Input ...............................................................................................75

Pulsecount Input .......................................................................................77

Quadrature Input .......................................................................................78

Totalcount Input ........................................................................................79

Timer/Counter Output Objects .......................................................................80

Edgedivide Output ....................................................................................80

Frequency Output .....................................................................................81

Oneshot Output .........................................................................................83

Pulsecount Output .....................................................................................84

Pulsewidth Output .....................................................................................85

Triac Output ..............................................................................................86

Triggered Count Output ............................................................................87

Notes ..............................................................................................................88

ii FT 3120 / 3150 Smart Tranceiver Data Book

Page 5

Chapter 4 - Hardware Design Considerations .................................................91

Introduction .....................................................................................................92

Quick Start for Users Familiar With The FTT-10A Transceiver ...................92

Interface Between Smart Transceivers and the Network ................................93

PC Board Layout Guidelines ..........................................................................95

EMI Design Issues ..........................................................................................98

ESD Design Issues ........................................................................................101

Lightening Protection ...................................................................................102

Building Entrance Protection ..................................................................102

Network Line Protection .........................................................................102

Shield Protection .....................................................................................103

Suggested Gas Discharge Arresters ........................................................103

EN 61000-4 Electromagnetic Compatibility (EMC) Testing .......................104

Chapter 5 - Network Cabling and Connections .............................................109

Network Connection .....................................................................................110

Network Topology Overview .......................................................................110

System Performance and Cable Selection ....................................................111

System Specifications .............................................................................112

Transmission Specifications ...................................................................112

Cable Termination and Shield Grounding ....................................................113

Free Topology Network Segment ...........................................................113

Doubly Terminated Bus Topology Segment ..........................................113

Grounding Shielded Twisted Pair Cable ................................................114

Chapter 6 - Programming Considerations .....................................................115

Application Program Development and Export ............................................116

LonBuilder Developers Kit ...........................................................................116

Development Hardware Setup ................................................................116

Release Hardware Setup .........................................................................118

NodeBuilder Development Tool ...................................................................118

Development Hardware Setup ................................................................118

Release Hardware Setup .........................................................................119

Appendix A - FT Smart Transceiver Design Checklist .................................121

Introduction ...................................................................................................122

Device Checklist ...........................................................................................122

Appendix B - Qualified TP/FT-10 Cable Specifications and Sources ..........125

Introduction ...................................................................................................126

Qualified Cables ...........................................................................................126

Category 5 Cable Specifications .............................................................126

NEMA Level IV Cable Specifications ...................................................126

16AWG/1.3mm “Generic” Cable Specifications ...................................128

FT 3120 / 3150 Smart Tranceiver Data Book iii

Page 6

Table of Contents

Appendix C - Design and Handling Guidelines .............................................129

Application Considerations ...........................................................................130

Termination of Unused Pins ...................................................................130

Avoidance of Damaging Conditions .......................................................130

Power Supply, Ground, and Noise Considerations .................................132

Decoupling Capacitors ............................................................................133

Board Soldering Considerations ...................................................................134

Soldering Through-hole Parts (FT-X1) ..................................................134

Soldering Surface Mount (SMT) Parts (Free Topology Transceivers) ..135

Handling Precautions and Electrostatic Discharge .......................................135

Electrostatic Discharge ...........................................................................138

Recommended Reading ..........................................................................139

Power Distribution and Decoupling Capacitors ...........................................139

Recommended Bypass Capacitor Placement ................................................140

Appendix D - Reference Design Schematics and Layout ...............................141

Mini Evaluation Kit Board ............................................................................142

FT 3150 Evaluatin Board Core......................................................................143

FT 3150 Evaluation Board Peripheral Circuitry............................................144

FT 3150 Evaluation Board Composite Top Layer.........................................145

FT 3150 Evaluation Board Top Layer...........................................................146

FT 3150 Evaluation Board Internal Ground Layer........................................147

FT 3150 Evaluation Board Internal Power Layer..........................................148

FT 3150 Evaluation Board Bottom Layer .....................................................149

FT 3150 Evaluation Board Composite Bottom Layer ...................................150

iv FT 3120 / 3150 Smart Tranceiver Data Book

Page 7

1

Introduction

FT 3120 / FT 3150 Smart Transceiver Data Book 1

Page 8

Chapter 1 - Introduction

Introduction

This manual provides detailed technical specifications on the electrical interfaces, mechanical interfaces, and

®

operating environment characteristics for the FT 3120

guidelines for migrating applications to an FT Smart Transceiver-based device using a LonBuilder

®

NodeBuilder

In some cases, vendor sources are included in this manual to simplify the task of integrating FT Smart Transceivers

with application electronics.

There is a list of related documentation at the end of this chapter in the section Related Documentation. The

documents listed in that section can be found on the Echelon website (www.echelon.com) unless otherwise noted.

development tool.

and FT 3150® Smart Transceivers. This manual also provides

®

or

Audience

This manual provides specifications and user instructions for FT Smart Transceiver customers, and users of network

interfaces based on the FT Smart Transceivers.

Product Overview

The FT Smart Transceivers integrate a Neuron® 3120 or Neuron 3150 network processor core, respectively, with a

free topology (FT) twisted-pair transceiver to create a low cost, smart transceiver on a chip. Combined with the

Echelon high performance FT-X1 or FT-X2 Communication Transformer, the FT Smart Transceivers set new

benchmarks for performance, robustness, and low cost. Ideal for use in L

industrial, transportation, home, and utility automation applications, the FT Smart Transceivers can be used in both

new product designs and as a means of cost reducing existing devices.

ONWORKS

®

devices designed for building,

The integral transceiver is fully compatible with the TP/FT-10 channel and can communicate with devices using the

Echelon FTT-10A Free Topology Transceiver, and with the addition of suitable DC isolation capacitors, the LPT-10

Link Power Transceiver. The free topology transceiver supports polarity insensitive cabling using a star, bus, daisychain, loop, or combined topologies. This frees the installer from the need to adhere to a strict set of wiring rules. Free

topology wiring reduces the time and expense of device installation by allowing the wiring to be installed in the most

expeditious and cost-effective manner. It also simplifies network expansion by eliminating restrictions on wire

routing, splicing, and device placement.

The FT 3120 Smart Transceiver is a complete system-on-a-chip that is targeted at cost-sensitive and small form factor

designs that require up to 4Kbytes of application code. The Neuron 3120 core operates at up to 40MHz, and includes

4Kbytes of EEPROM and 2Kbytes of RAM. The Neuron firmware is pre-programmed in an on-chip ROM. The

application code is stored in the embedded EEPROM memory and may be updated over the network. The FT 3120

Smart Transceiver is offered in a 32-lead SOIC package as well as a compact 44-lead TQFP package.

The FT 3150 Smart Transceiver includes a 20MHz Neuron 3150 core, 0.5Kbytes of EEPROM and 2Kbytes of RAM.

Through its external memory bus, the FT 3150 Smart Transceiver can address up to 58Kbytes of external memory, of

which 16Kbytes of external non-volatile memory is dedicated to the Neuron system firmware. The FT 3150 Smart

Transceiver is supplied in a 64-lead TQFP package.

The embedded EEPROM may be written up to 10,000 times with no data loss. Data stored in the EEPROM will be

retained for at least 10 years.

Three different versions of the FT Smart Transceivers are available to meet a wide range of applications and

packaging requirements. See the table below for product offerings and descriptions.

2 FT 3120/FT 3150 Smart Transceiver Data Book

Page 9

Product Overview

Table 1.1 FT Smart Transceiver Product Offerings

Smart

Transceiver IC

Product

Number

FT 3120-E4S40 14212R-500 40MHz 4Kbytes 2Kbytes 12Kbytes No 32 SOIC

FT 3120-E4P40 14222R-800 40MHz 4Kbytes 2Kbytes 12Kbytes No 44 TQFP

FT 3150-P20 14230R-450 20MHz 0.5Kbytes 2Kbytes N/A Ye s 64 TQFP

Model

Number

Maximum

input clock

EEPROM

(Kbytes)

RAM

(Kbytes)

ROM

(Kbytes)

External

memory

interface

IC

Package

The FT Smart Transceivers provide 11 I/O pins which may be configured to operate in one or more of 34 predefined

standard input/output modes. Combining a wide range of I/O models with two on-board timer/counters enables the

FT Smart Transceivers to interface to application circuits with minimal external logic or software development.

The FT Smart Transceivers can be easily interfaced to other host MCUs by way of the Echelon ShortStack™ or MIP

firmware. When used with the ShortStack or MIP firmware, the FT Smart Transceiver enables any OEM product with

a host microcontroller to quickly and inexpensively become a networked, Internet-accessible device. The ShortStack

firmware uses an SCI or SPI serial interface to communicate between the host and the FT Smart Transceiver. The

MIP firmware uses a high performance parallel or dual-ported RAM interface.

The FT Smart Transceivers are supplied with either an FT-X1or FT-X2 transformer, the patent-pending external

communication transformers. A transformer enables operation in the presence of high frequency common mode noise

on unshielded twisted pair networks. Properly designed devices can meet the rigorous Level 3 requirements of EN

61000-4-6 without the need for a network isolation choke.

The transformer also offers outstanding immunity from magnetic field noise, eliminating the need for protective

magnetic field shields in most applications. The transformer is provided in a potted, 6-pin, through-hole plastic

package.

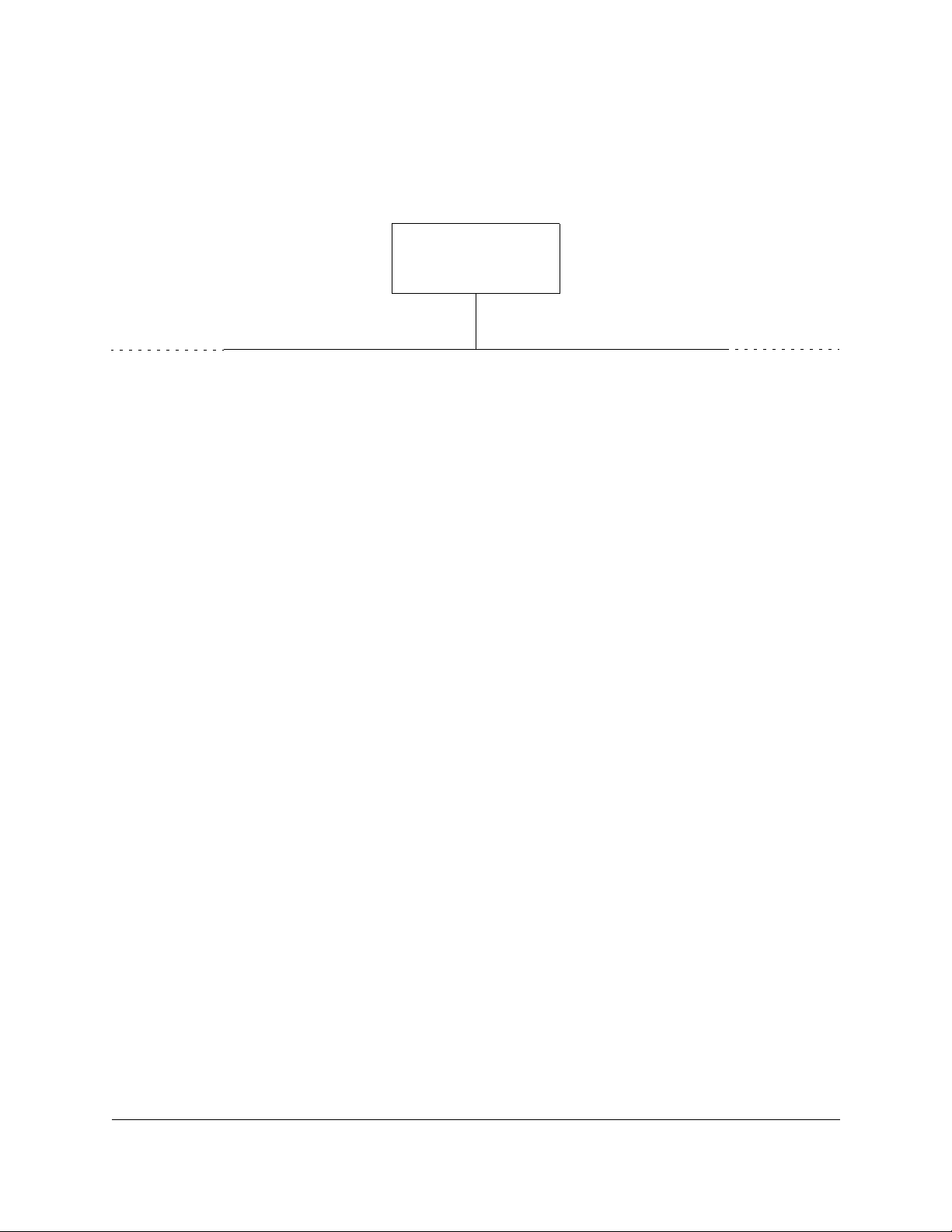

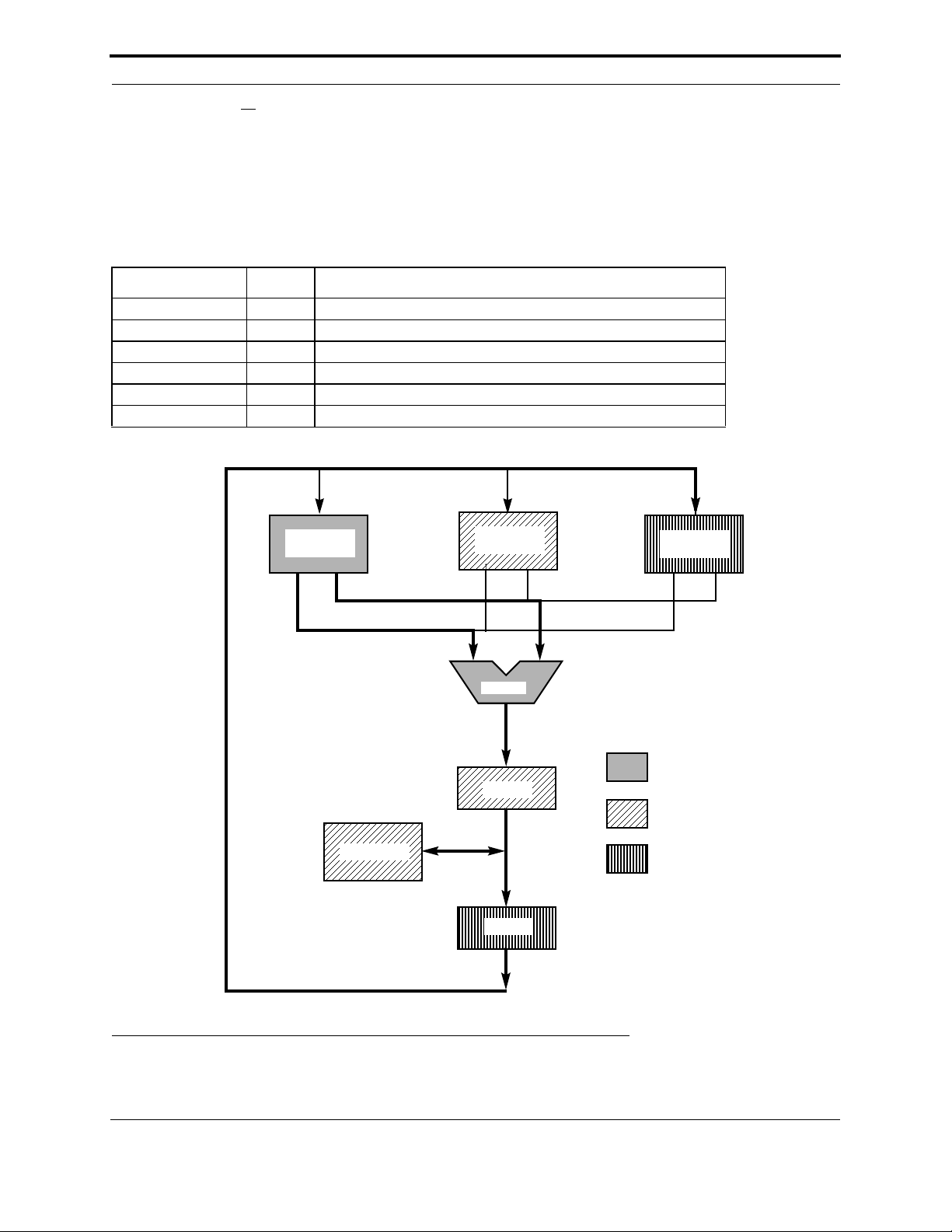

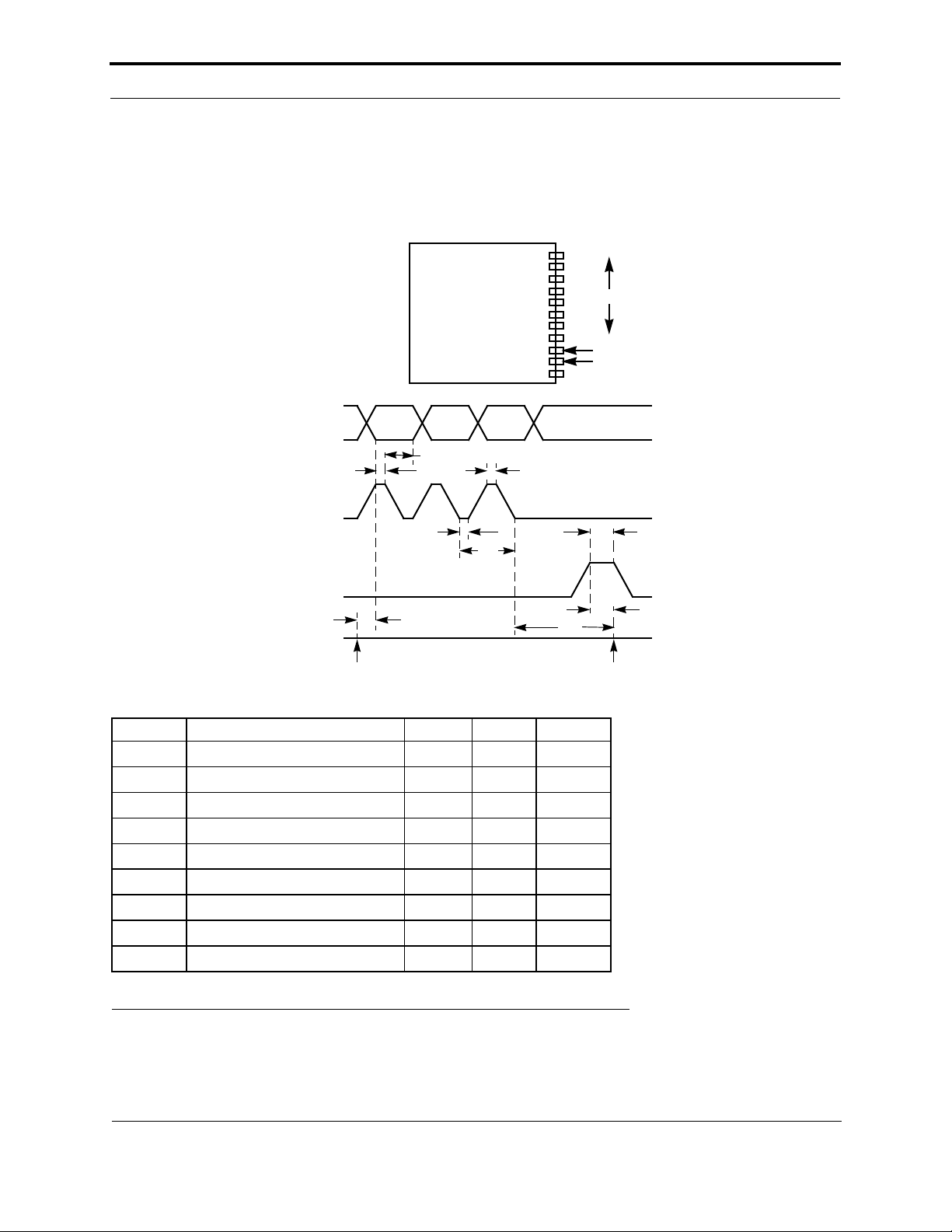

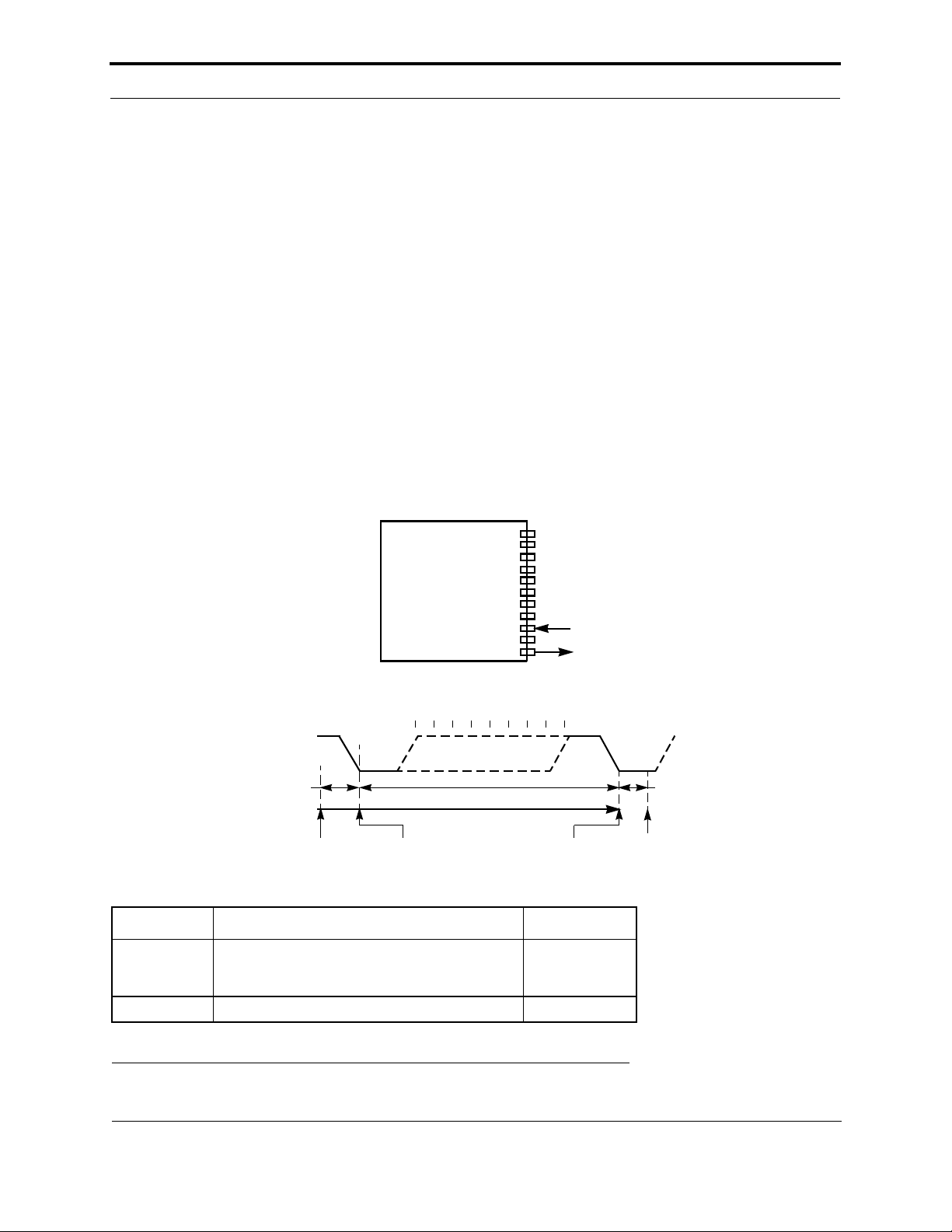

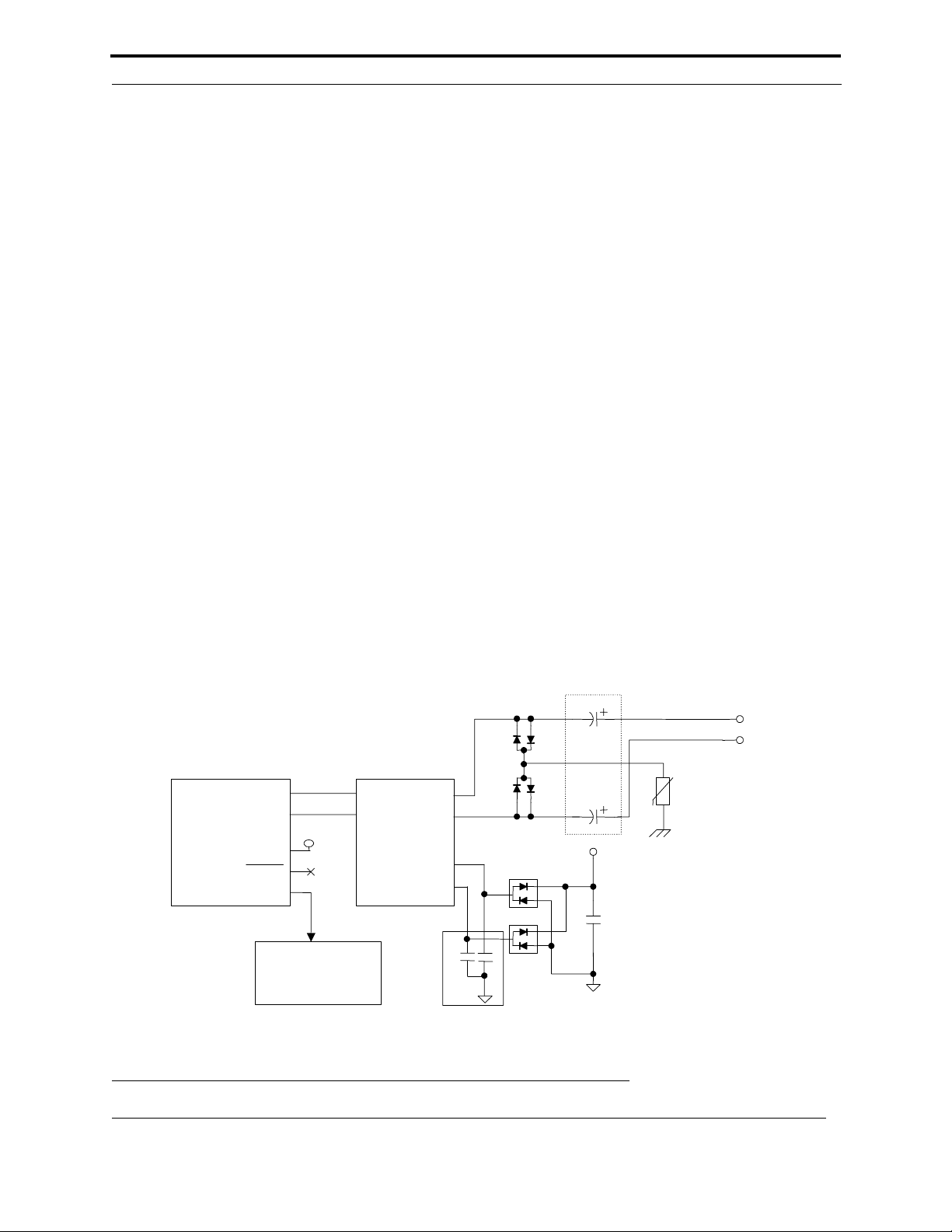

A typical FT Smart Transceiver-based device requires a power source, crystal, and I/O circuitry. See Figure 1.1 for a

typical FT Smart Transceiver-based device.

The FT Smart Transceivers are compatible withthe Echelon LPT-10 Link Power Transceiver, and they can

communicate with each other on a single twisted pair cable. This capability provides an inexpensive means of

interfacing to devices whose current or voltage requirements would otherwise exceed the capacity of the link power

segment. When equipped with an FT Smart Transceiver and DC blocking capacitors, these devices can be operated

from a local power supply without the need for additional electrical isolation from the link power network.

LONWORKS Device

Sense or Control

Devices, e.g., Motors,

Valves, Encoders,

Lights, Relays,

Switches

Smart Transceiver ICI/O

Crystal

Power

Source

Communication

Transformer

FT-X1 or FT-X2

Data

Rate

of

78

kbps

Free Topology Twisted Pair Network

Figure 1.1 Typical FT Smart Transceiver-based Device

FT 3120/FT 3150 Smart Transceiver Data Book 3

Page 10

Chapter 1 - Introduction

The FT Smart Transceivers also provide electrical isolation for I/O devices that are grounded, allowing such devices

to be used on a link power network segment. In many applications, some I/O devices are grounded, either to meet

functional requirements or safety regulations. The FT-X1or FT-X2 transformer electrically isolates the device from

the segment, allowing I/O circuitry to be grounded without impairing communications.

A twisted pair channel may be composed of multiple segments separated by EIA 709.1 routers or physical layer

repeaters. A physical layer repeater may be designed using FTT-10A transceivers (the FT Smart Transceivers cannot

be used as physical layer repeaters). The FTT-10A transceiver includes a physical layer repeater feature that allows

L

ONWORKS data to be exchanged between network segments by interconnecting two or more FTT-10A transceivers.

This allows a twisted pair network to grow inexpensively to encompass many more devices or longer wire distances

than would otherwise be possible. Refer to the L

ONWORKS FTT-10A Free Topology Transceiver User’s Guide for

more information on this.

The FT Smart Transceivers are designed to comply with both FCC and EN 55022 EMI requirements, minimizing

time-consuming and expensive testing.

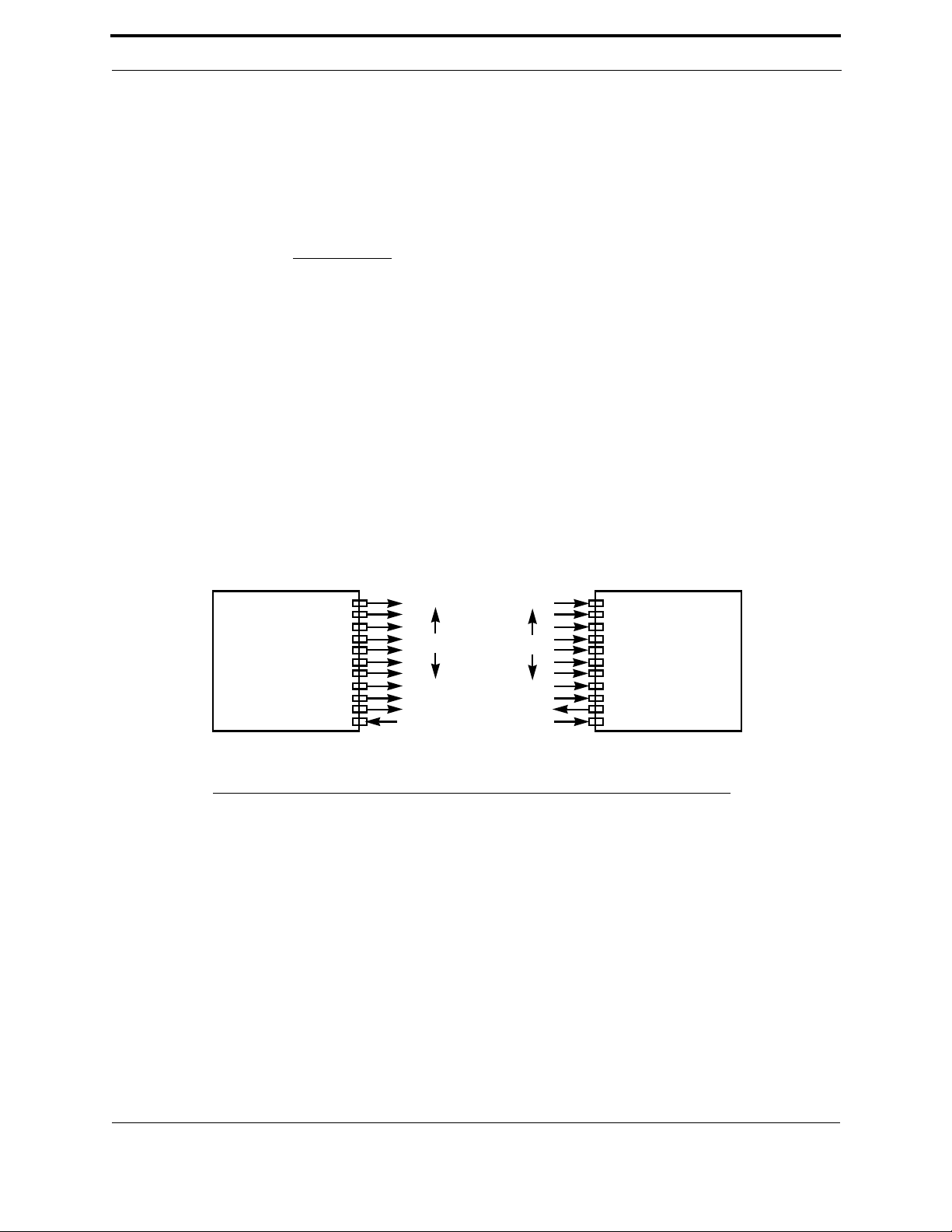

Free Topology Technology Overview

A conventional control system using bus topology wiring (such as RS-485) consists of a network of sensors and

actuators that are interconnected using a shielded twisted wire pair. In accordance with RS-485 guidelines, all of the

devices must be wired in a bus topology to limit electrical reflections and ensure reliable communications. There is a

high cost associated with installing and maintaining the cable plant that links together the devices of an RS-485-based

control system. Bus topology wiring is more time consuming and expensive to install, because the installer is unable

to branch or star the wiring where convenient. All devices must be connected directly to the main bus.

The best solution to reduce installation and maintenance costs and to simplify system modifications is to use a free

topology communications system. Echelon's free topology transceiver technology offers such a solution, providing an

elegant and inexpensive method of interconnecting the different elements of a distributed control system.

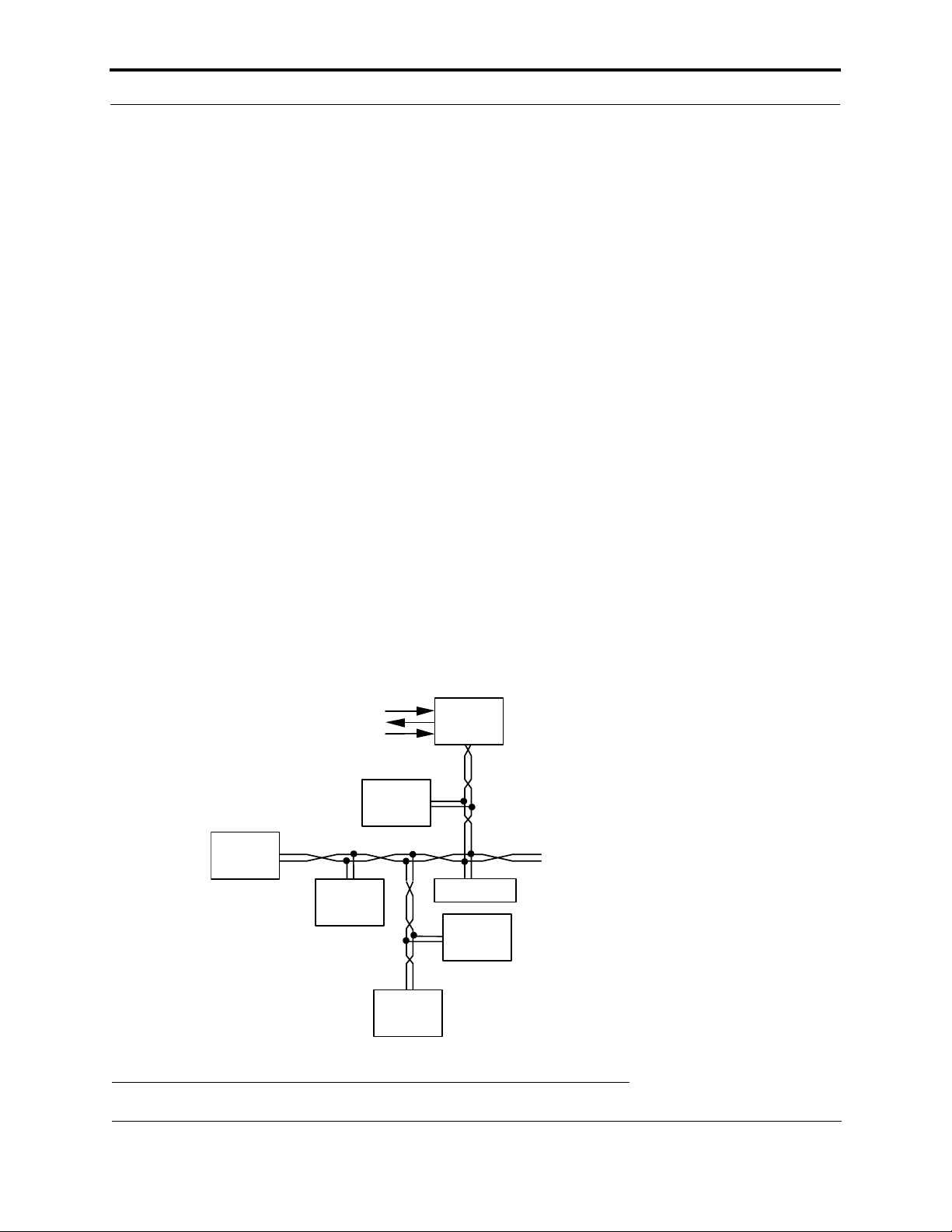

A free topology architecture allows the installer to wire the control devices with virtually no topology restrictions.

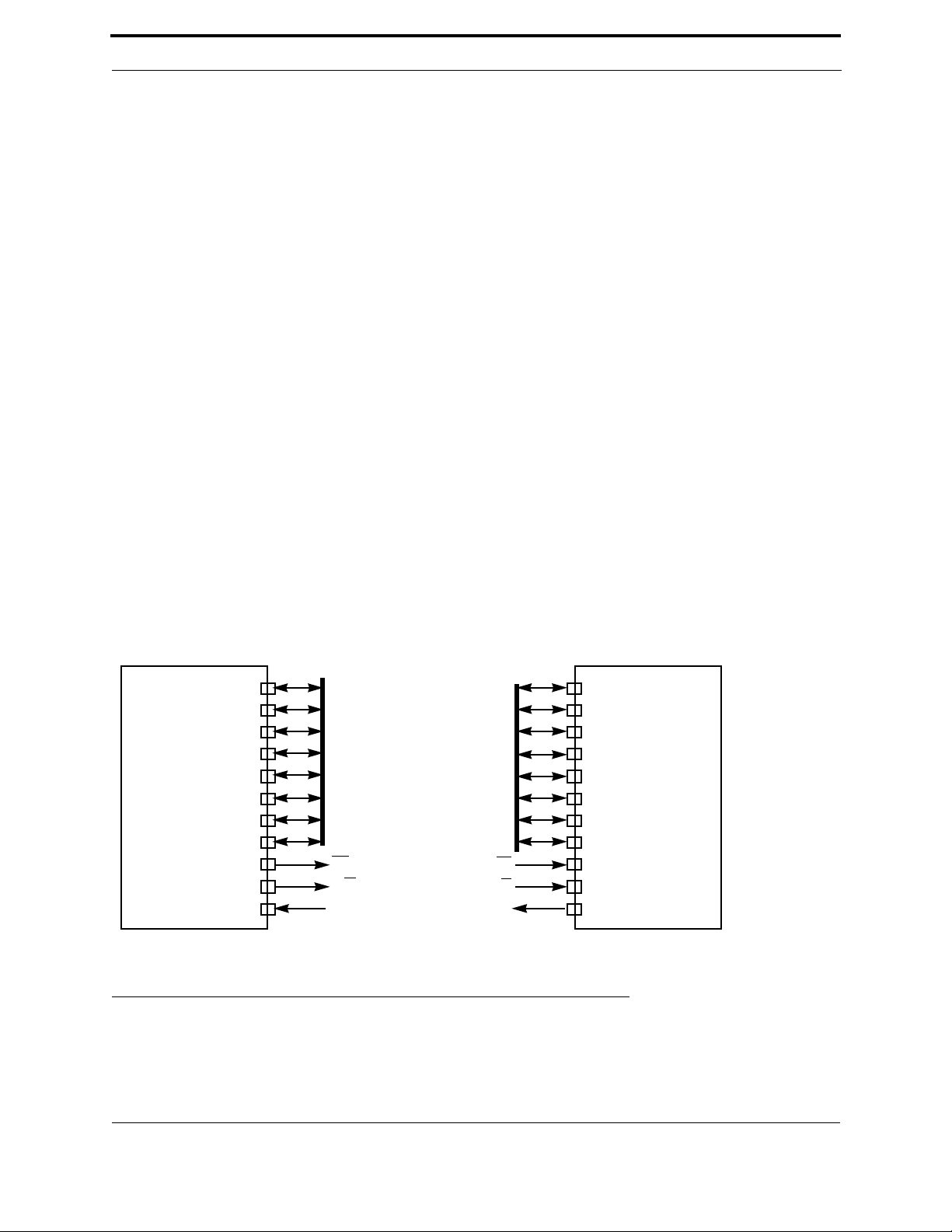

Power is supplied by a local +5VDC power supply located at each device as shown in Figure 1.2.

Smart

Transceiver

Device

Termination

Smart

Transceiver

Device

To additional

FT 3120 / FT 3150

Smart Transceiver

devices

Smart

Transceiver

Device

Sensor

Actuator

+5VDC power

Smart

Transceiver

Device

Smart

Transceiver

Device

Smart

Transceiver

Device

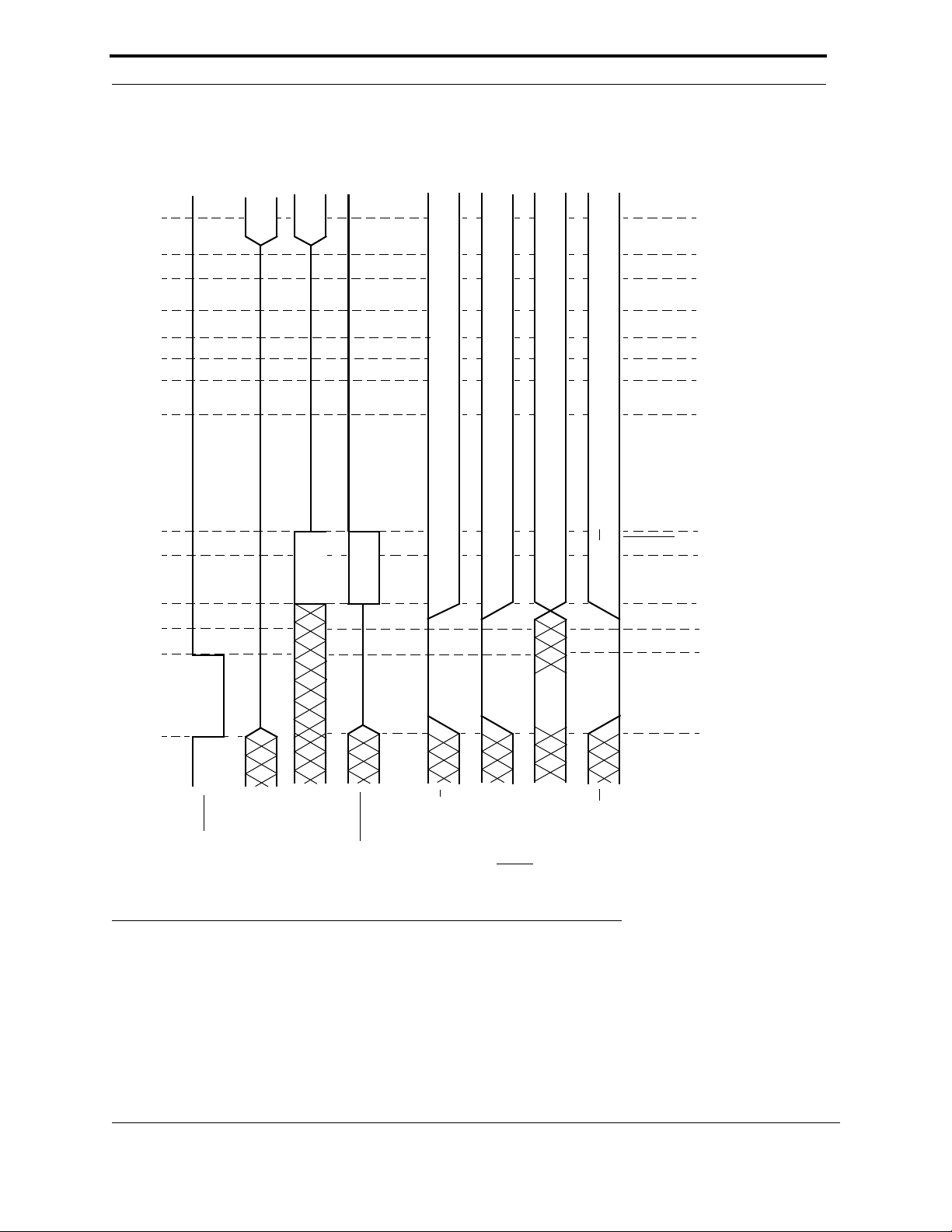

Figure 1.2 Free Topology Transceiver System

4 FT 3120/FT 3150 Smart Transceiver Data Book

Page 11

Related Documentation

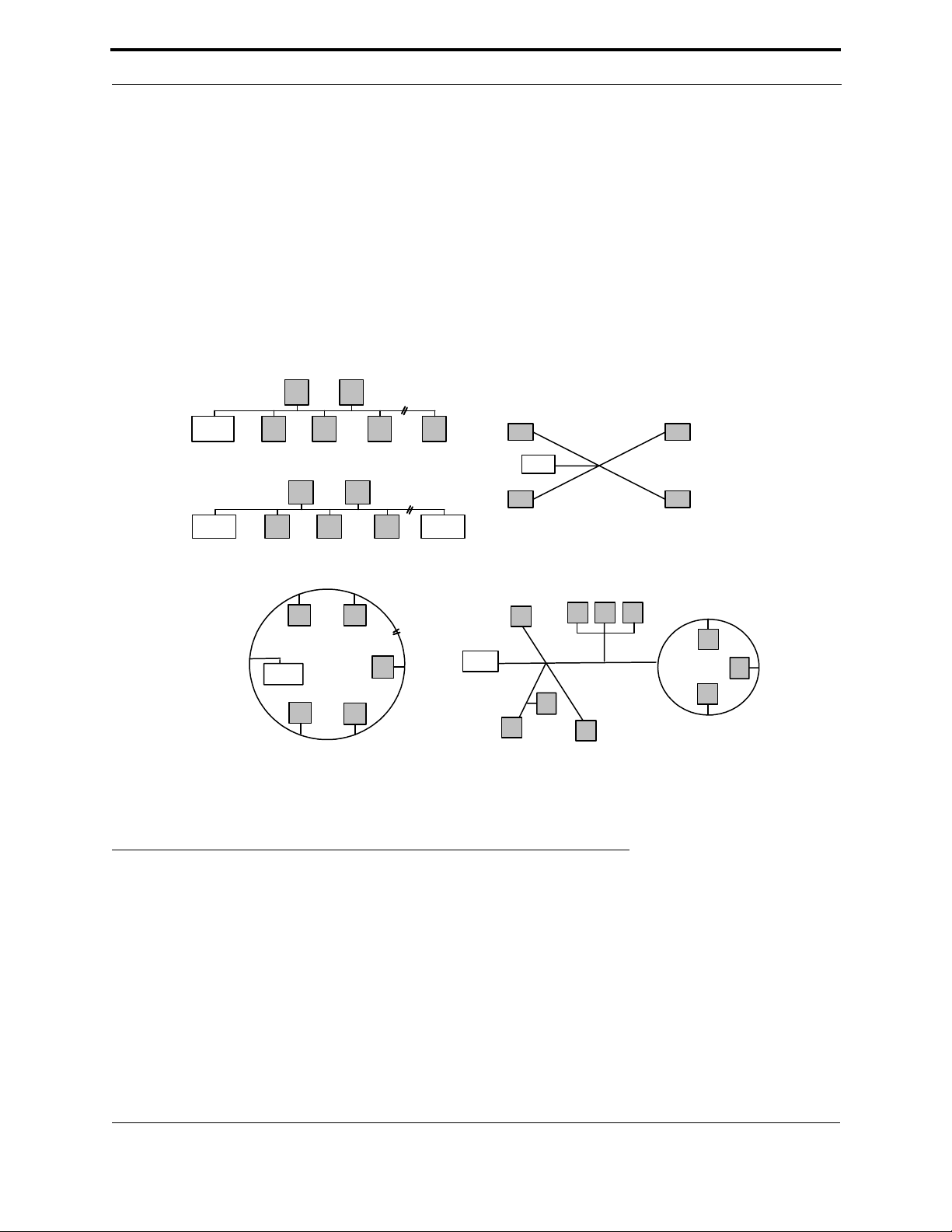

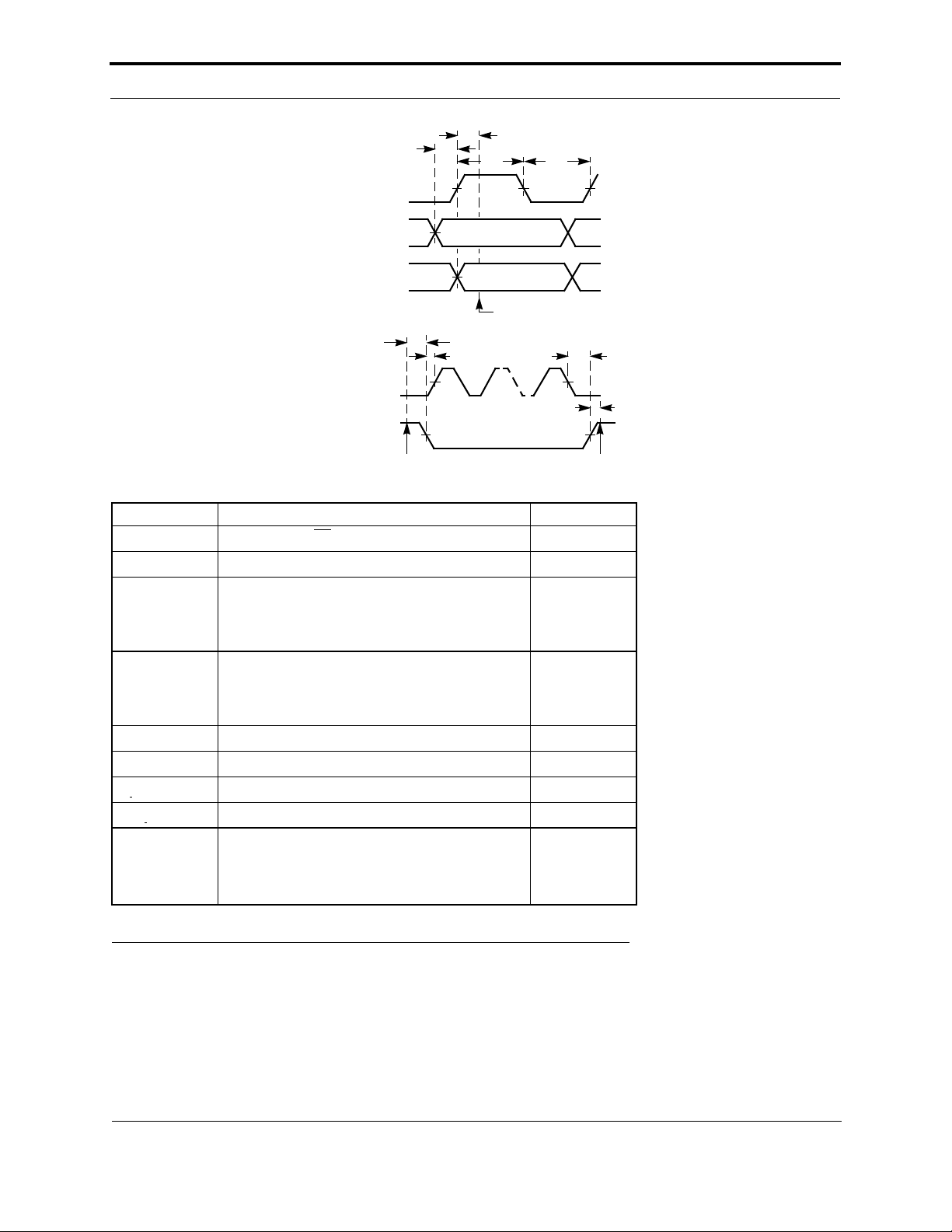

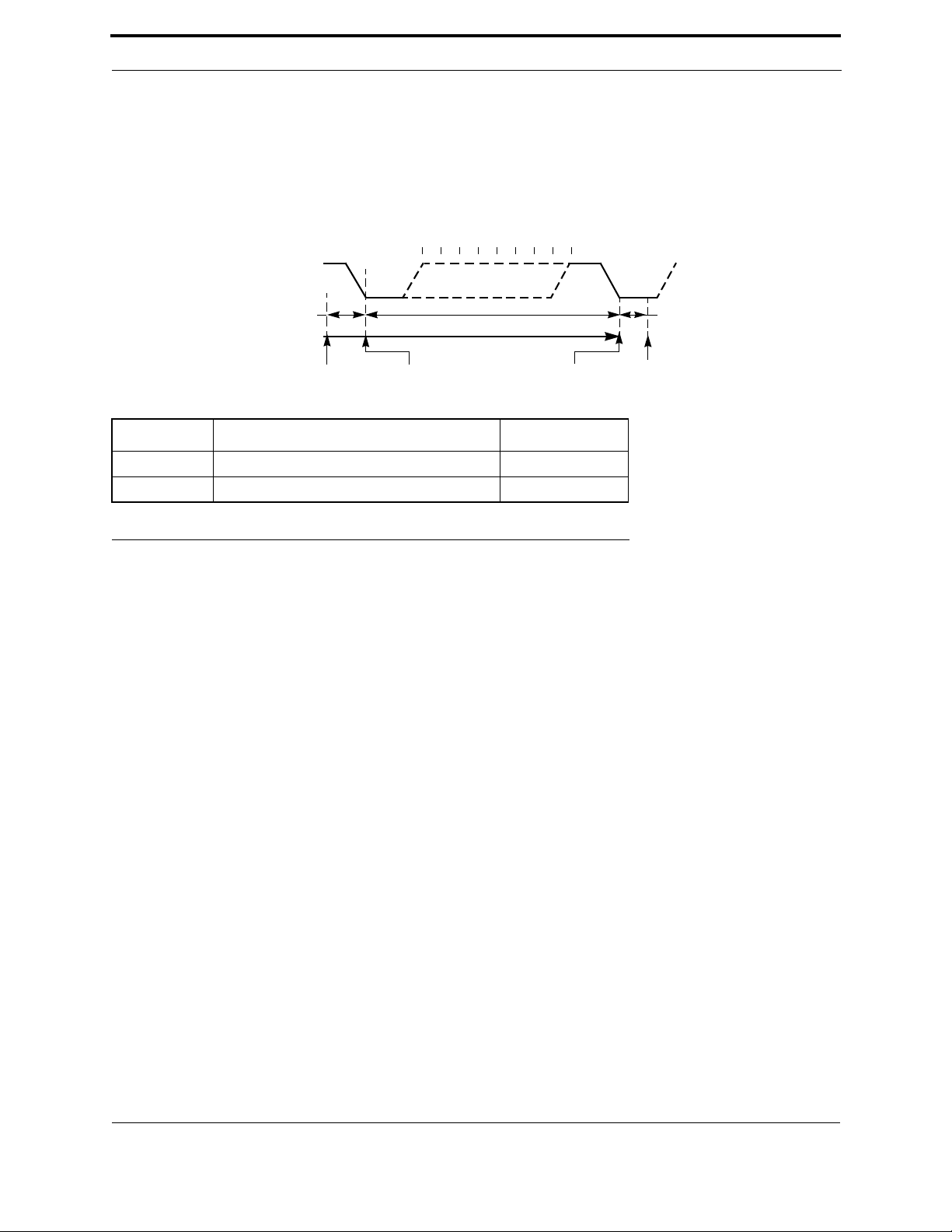

Unlike bus wiring designs, the free topology FT Smart Transceivers use a wiring scheme that supports star, loop, and/

or bus wiring (see Figure 1.3). This design has many advantages:

1. The installer is free to select the method of wiring that best suits the installation, reducing the need for advanced

planning and allowing last minute changes at the installation site.

2. If installers have been trained to use one style of wiring for all installations, free topology technology can be intro-

duced without requiring retraining.

3. Retrofit installations with existing wiring plants can be accommodated with minimal, if any, rewiring. This capa-

bility ensures that FT Smart Transceiver technology can be adapted to both old and new projects.

4. Free topology permits FT Smart Transceiver systems to be expanded in the future by simply tapping into the

existing wiring where it is most convenient to do so. This reduces the time and expense of system expansion, and

from the customer's perspective, keeps down the life cycle cost of the free topology network.

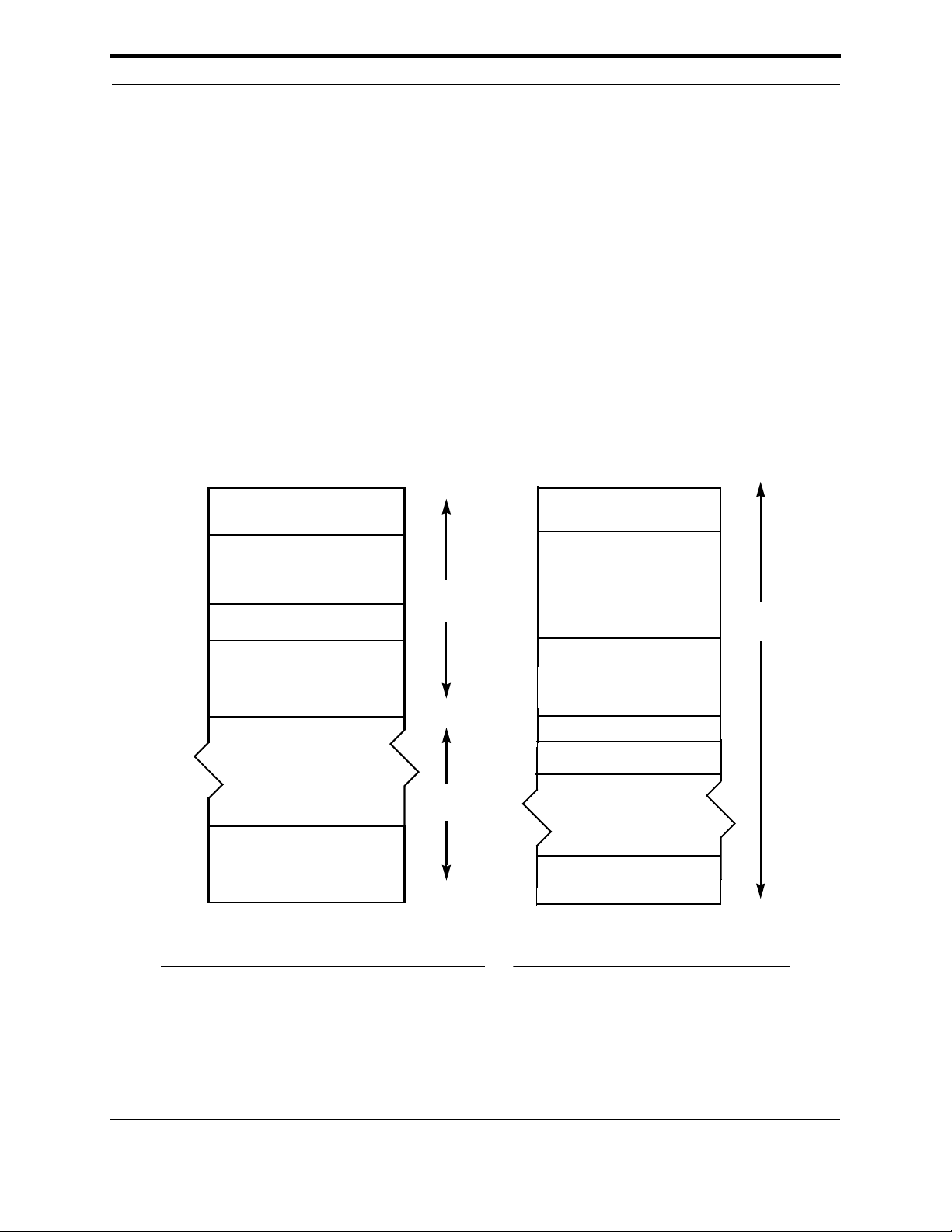

*

Singly Terminated Bus Topology

*

**

Doubly Terminated Bus Topology

Star Topology

*

*

Loop Topology Mixed Topology

(* = Termination. The actual termination circuit will vary by topology.)

Figure 1.3 Typical Wiring Topologies Supported by the FT Smart Transceivers System Content

Related Documentation

The following Echelon documents are suggested reading:

L

ONWORKS SMX Transceiver Datasheet (003-0336-01)

LonBuilder User's Guide (078-0001-01)

NodeBuilder User's Guide (078-0141-01)

Neuron C Programmer's Guide (078-0002-01)

LonBuilder Hardware Guide (078-0003-01)

FT 3120/FT 3150 Smart Transceiver Data Book 5

Page 12

Chapter 1 - Introduction

LONMARK™ Layers 1-6 Interoperability Guidelines (078-0014-01)

L

ONMARK

™

Application Layer Interoperability Guidelines (078-0120-01)

FT 3120 and FT 3150 Smart Transceiver Datasheet (003-0337-01)

L

ONWORKS FTT-10A Free Topology Transceiver data sheet (003-0312-01)

L

ONWORKS Custom Node Development engineering bulletin (005-0024-01)

LPI-10 Link Power Interface Module User’s Guide (078-0104-01)

LPT-10 Link Power Transceiver User's Guide (078-0105-01)

Junction Box and Wiring Guidelines for Twisted Pair L

ONWORKS Networks engineering bulletin (005-0023-01)

EIA-709.1 Control Network Protocol Specification (distibuted by Global Engineering Documents:

global.ihs.com).

6 FT 3120/FT 3150 Smart Transceiver Data Book

Page 13

2

Hardware Resources

FT 3120 / FT 3150 Smart Transceiver Data Book 7

Page 14

Chapter 2 - Hardware Resources

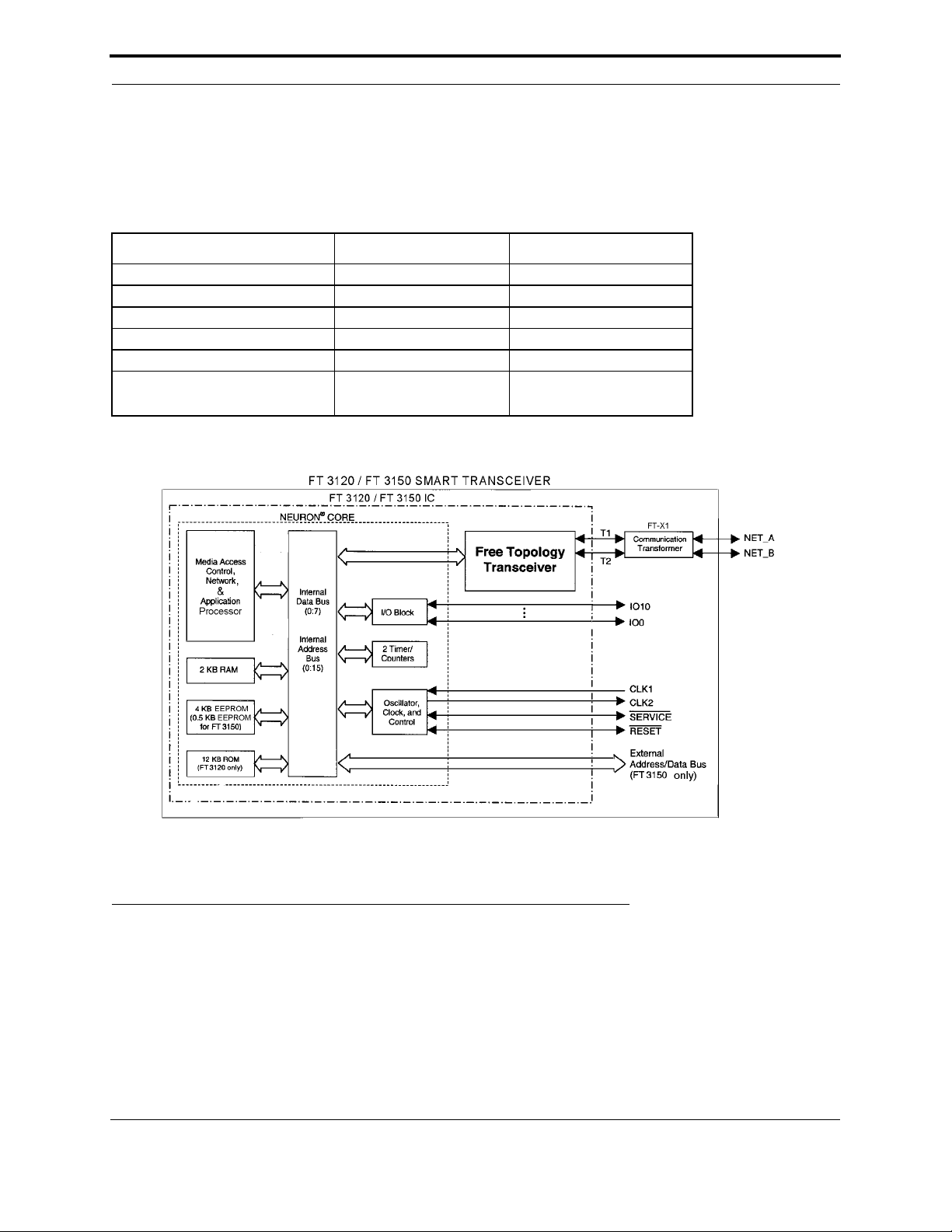

Overview

The FT 3150 Smart Transceiver supports external memory for more complex applications, while the FT 3120 Smart

Transceiver is a complete system on a chip. The major hardware blocks of both processors are the same, except where

noted in the table and figure below.

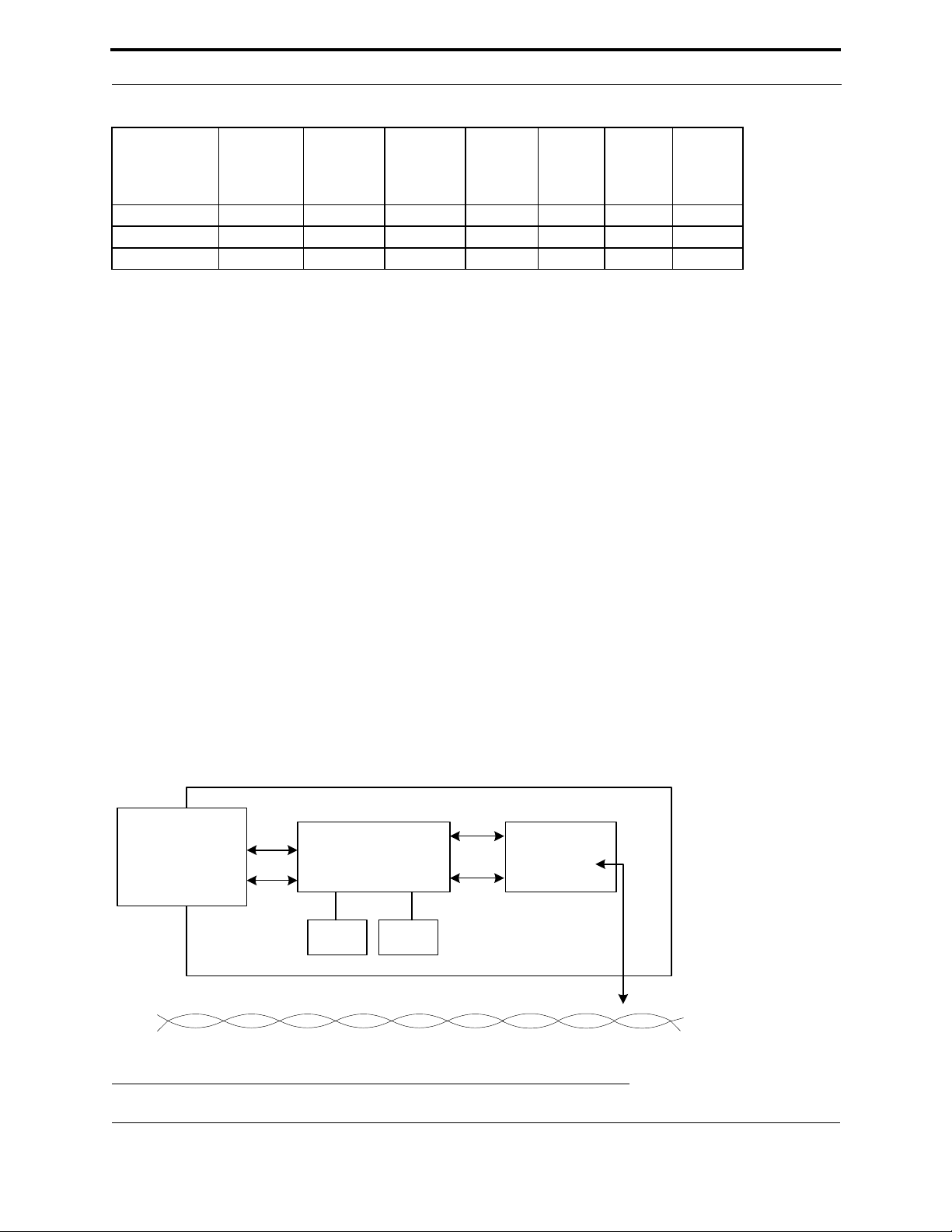

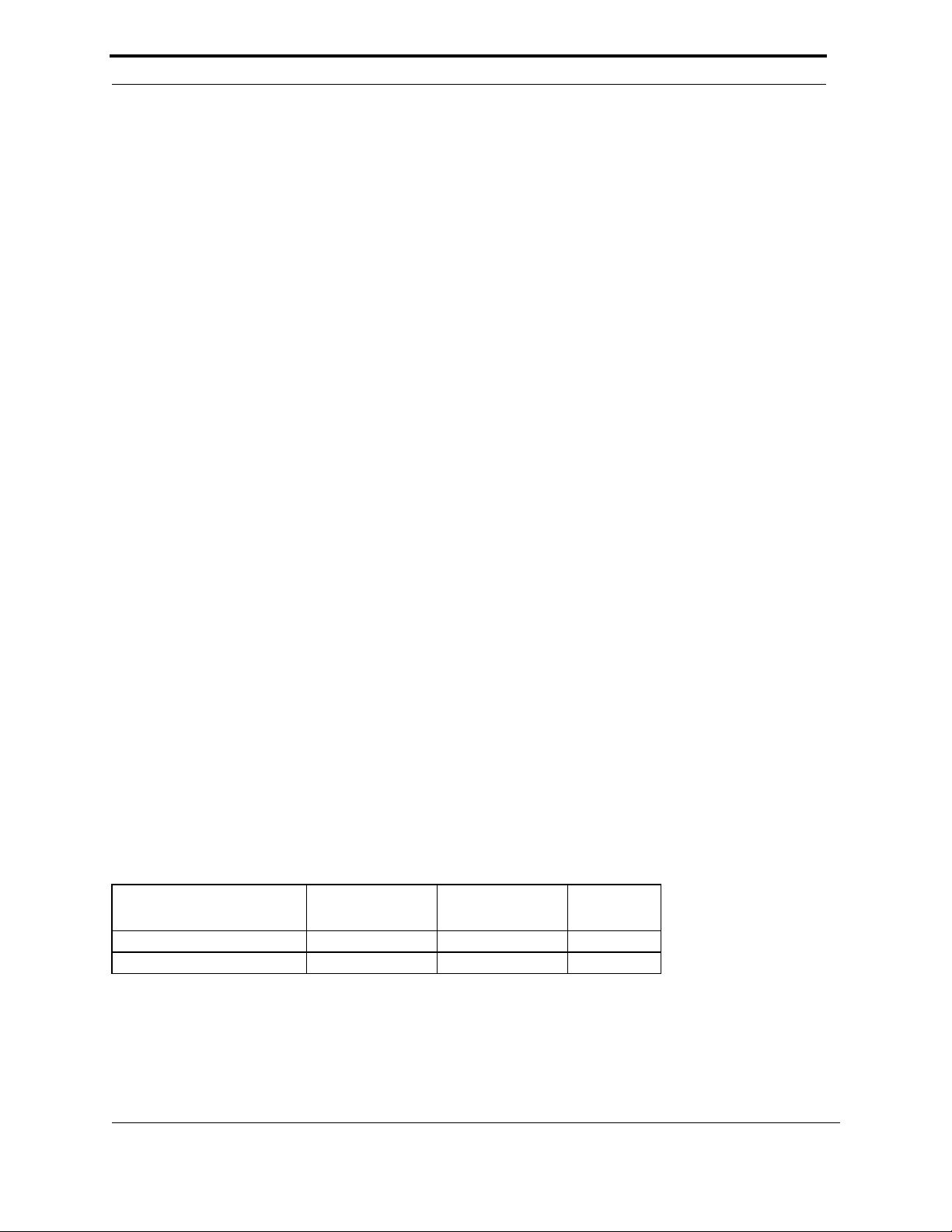

Table 2.1 Comparison of FT Smart Transceivers

Characteristic FT 3150 Smart Transceiver FT 3120 Smart Transceiver

RAM Bytes 2,048 2,048

ROM Bytes — 12,288

EEPROM Bytes 512 4,096

16-Bit Timer/Counters 2 2

External Memory Interface Ye s No

Package 64 pin TQFP 32 pin SOIC

44 pin TQFP

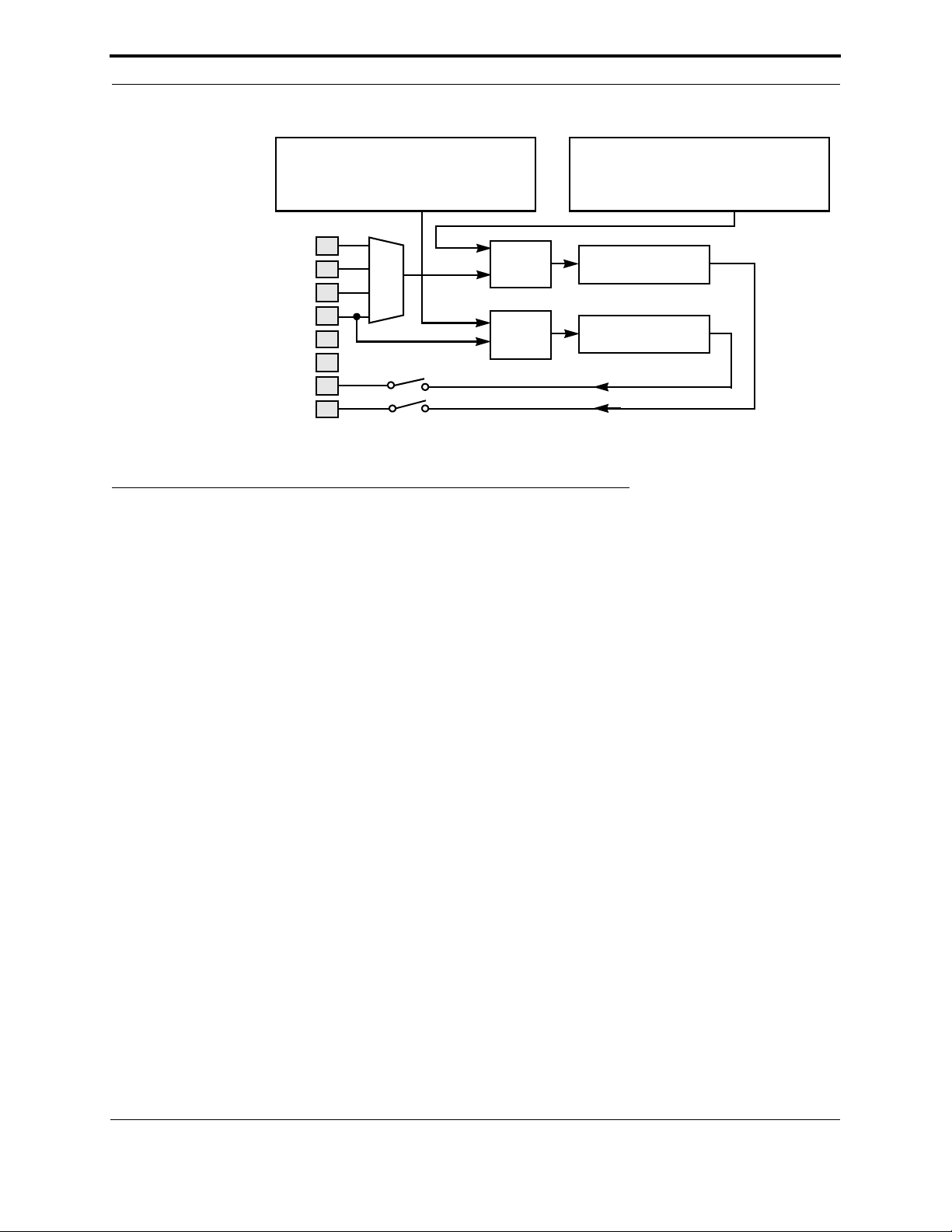

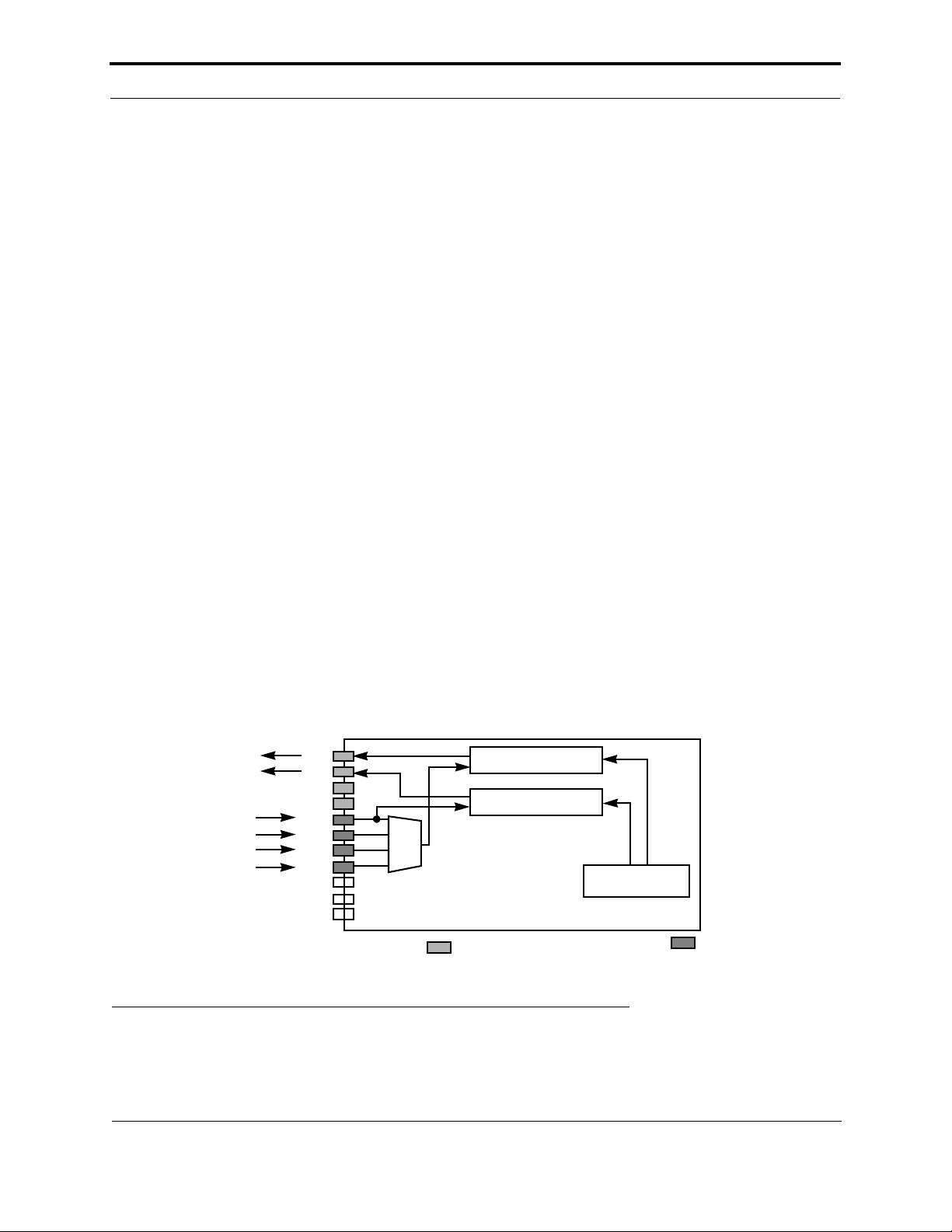

Figure 2.1 FT Smart Transceiver Block Diagram

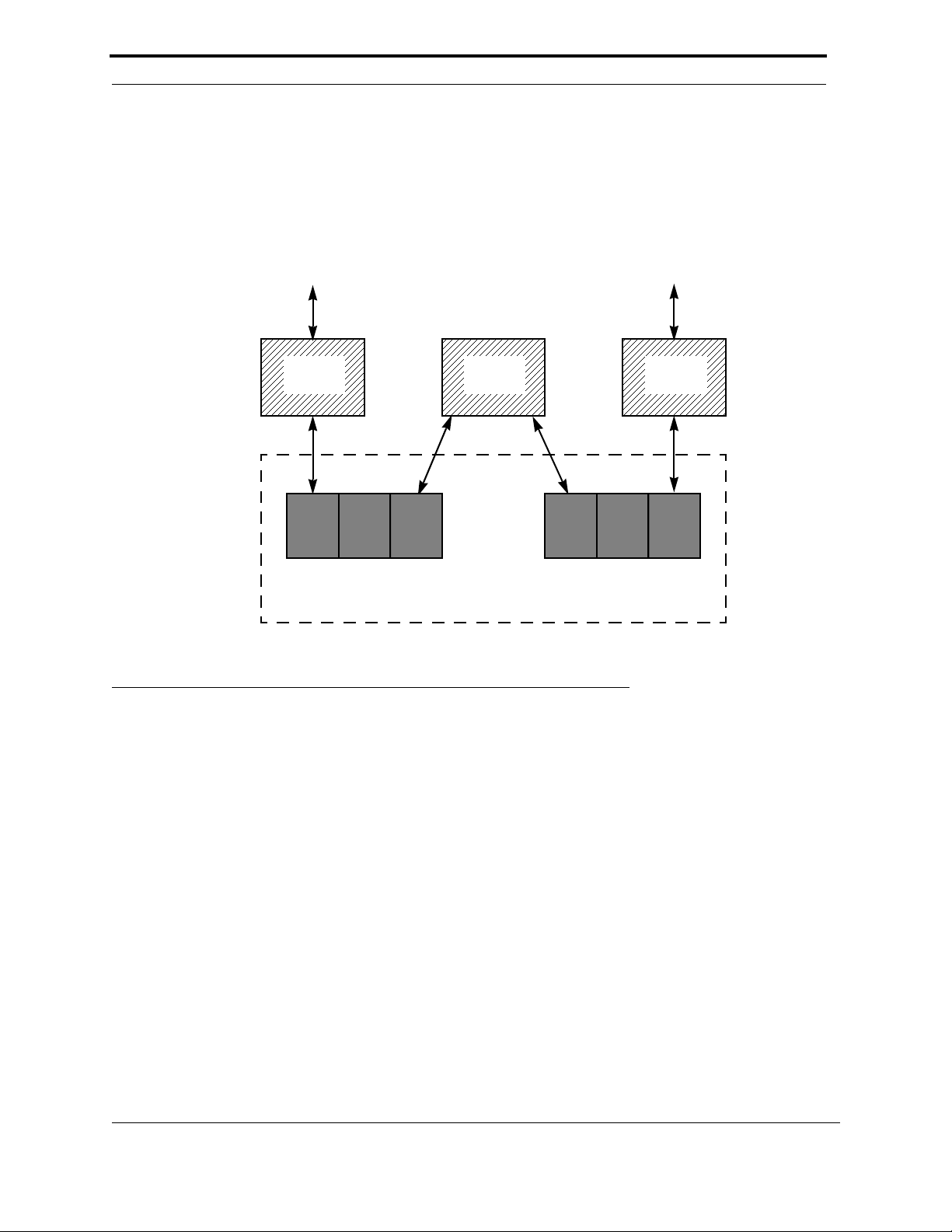

Neuron Processor Architecture

The Neuron core is composed of three processors. These processors are assigned to the following functions by the

Neuron firmware.

Processor 1 is the MAC layer processor that handles layers 1 and 2 of the 7-layer LonTalk

includes driving the communications subsystem hardware and executing the media access control algorithm.

Processor 1 communicates with Processor 2 using network buffers located in shared RAM memory.

8 FT 3120 / FT 3150 Smart Transceiver Data Book

®

protocol stack. This

Page 15

Neuron Processor Architecture

Processor 2 is the network processor that implements layers 3 through 6 of the LonTalk protocol stack. It handles

network variable processing, addressing, transaction processing, authentication, background diagnostics, software

timers, network management, and routing functions. Processor 2 uses network buffers in shared memory to

communicate with Processor 1, and application buffers to communicate with Processor 3. These buffers are also

located in shared RAM memory. Access to them is mediated with hardware semaphores to resolve contention when

updating shared data.

.

Communications

Port

Input/Output

MAC

Proces-

Network

Proces-

Application BuffersNetwork Buffers

Shared

Applica-

tion

Figure 2.2 Processor Organization Memory Allocation

Processor 3 is the application processor. It executes the code written by the user, together with the operating system

services called by user code. The primary programming language used by applications is Neuron C, a derivative of

the ANSI C language optimized and enhanced for L

ONWORKS distributed control applications. The major

enhancements are the following (see the Neuron C Programmer’s Guide for details):

• A network communication model, based on functional blocks and network variables, that simplifies and pro-

motes data sharing between like and disparate devices.

• A network configuration model, based on functional blocks and configuration properties, that facilitates

interoperable network configuration tools.

• A type model based on standard and user resource files that expands the market for interoperable devices by

simplifying the integration of devices from multiple manufacturers.

• An extensive set of I/O drivers that support the I/O capabilities of the Neuron core.

• Powerful event driven programming extensions that provide easy handling of network, I/O, and timer

events.

The support for all these capabilities is part of the Neuron firmware, and does not need to be written by the

programmer.

Each of the three identical processors has its own register set (Table 2.2), but all three processors share data, ALUs

(arithmetic logic units) and memory access circuitry (Figure 2.3). On the FT 3150 Smart Transceiver, the internal

FT 3120 / FT 3150 Smart Transceiver Data Book 9

Page 16

Chapter 2 - Hardware Resources

address, data, and R/W signals are reflected on the corresponding external lines when utilized by any of the internal

processors. Each CPU minor cycle consists of three system clock cycles, or phases; each system clock cycle is two

input clock cycles. The minor cycles of the three processors are offset from one another by one system clock cycle, so

that each processor can access memory and ALUs once during each instruction cycle. Figure 2.3 shows the active

elements for each processor during one of the three phases of a minor cycle. Therefore, the system pipelines the three

processors, reducing hardware requirements without affecting performance. This allows the execution of three

processes in parallel without time-consuming interrupts and context switching.

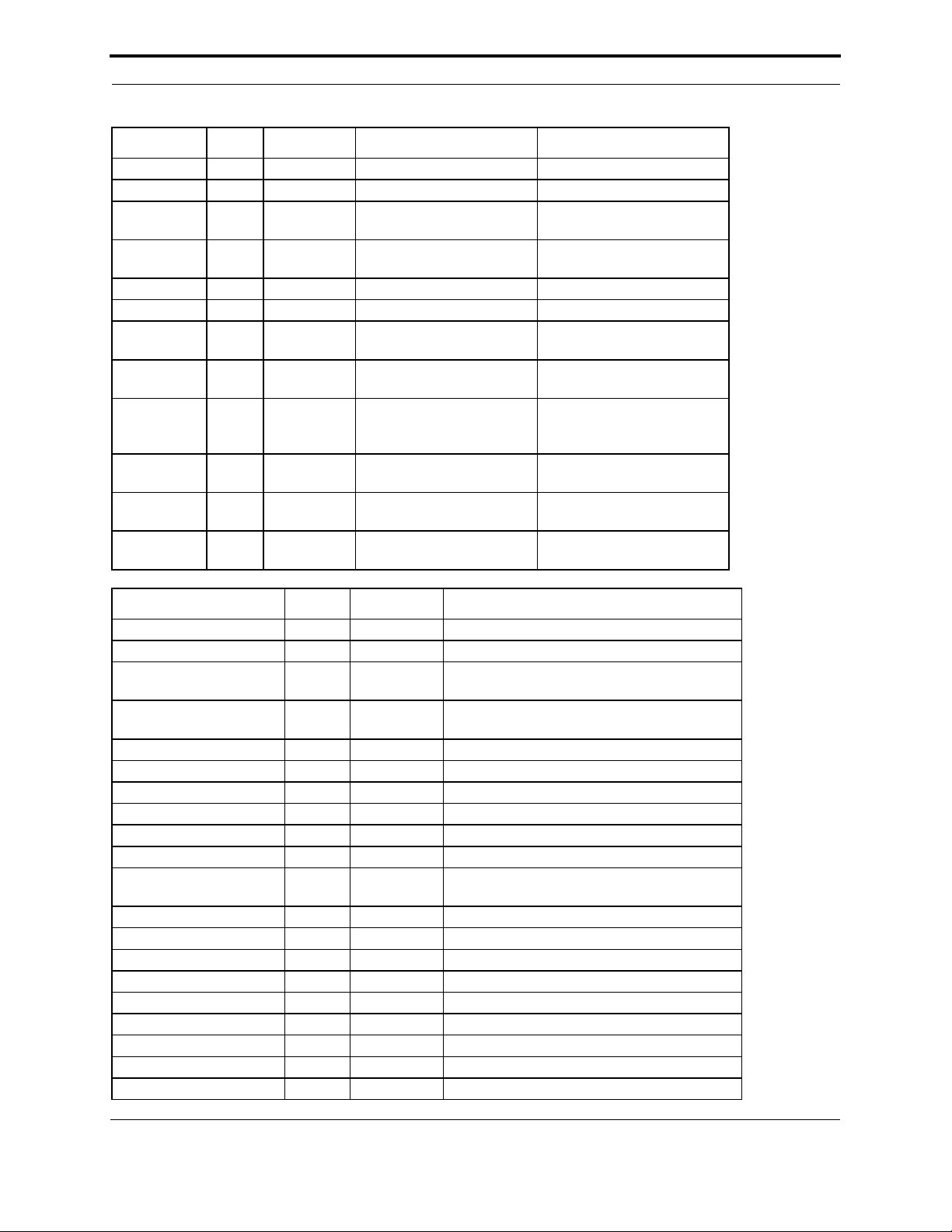

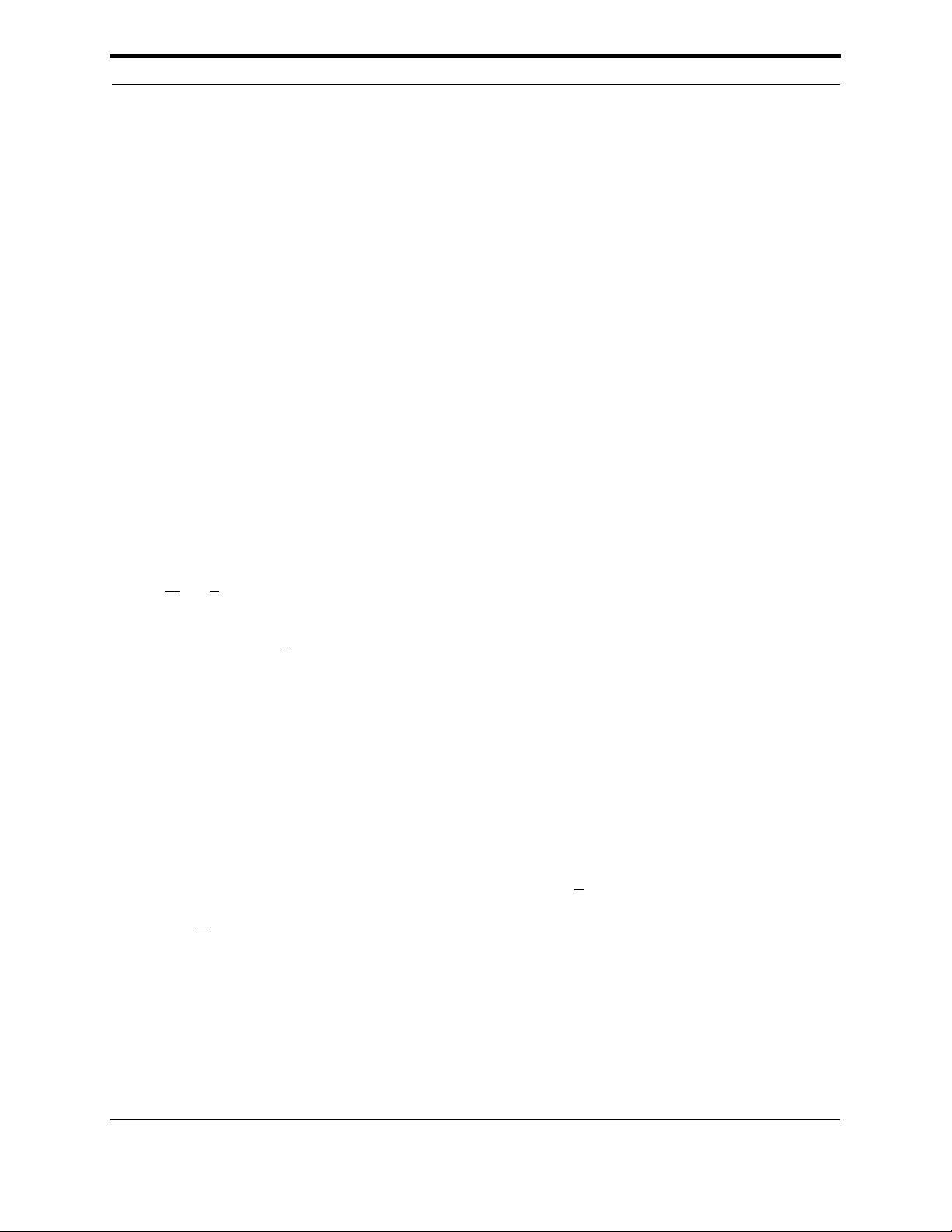

Table 2.2 Register Set

Mnemonic Bits Contents

FLAGS 8 CPU Number, Fast I/O Select, and Carry Bit

IP 16 Next Instruction Pointer

BP 16 Address of 256-Byte Base Page

DSP 8 Data Stack Pointer Within Base Page

RSP 8 Return Stack Pointer Within Base Page

TOS 8 Top of Data Stack, ALU Input

Processor 1

Registers

Memory

Processor 2

Registers

ALUs

Latch

Latch

Processor 3

Registers

Active elements – Processor 1

Active elements – Processor 2

Active elements – Processor 3

Figure 2.3 Processor/Memory Activity During One of the Three System Clock Cycles of a Minor Cycle

The architecture is stack-oriented; one 8-bit wide stack is used for data references, and the ALU operates on the TOS

(Top of Stack) register and the next entry in the data stack which is in RAM. A second stack stores the return

10 FT 3120 / FT 3150 Smart Transceiver Data Book

Page 17

Neuron Processor Architecture

addresses for CALL instructions, and may also be used for temporary data storage. This stack architecture leads to

very compact code. Tables 2.3, 2.42.4, and 2.5 outline the instruction set.

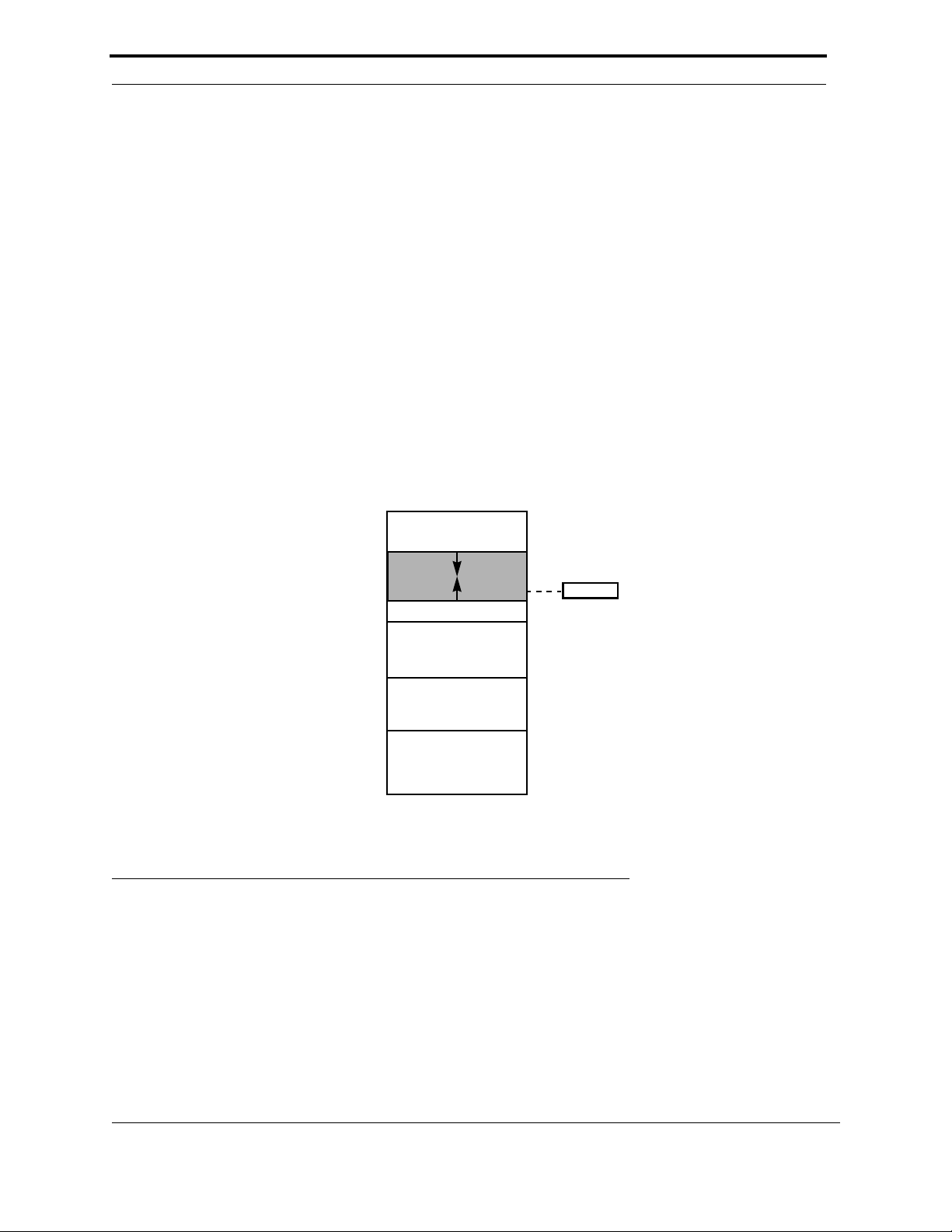

Figure 2.4 shows the layout of a base page, which may be up to 256 bytes long. Each of the three processors uses a

different base page, whose address is given by the contents of the BP register of that processor. The top of the data

stack is in the 8-bit TOS register, and the next element in the data stack is at the location within the base page at the

offset given by the contents of the DSP register. The data stack grows from low memory towards high memory. The

assembler shorthand symbol NEXT refers to the contents of the location (BP+DSP) in memory, which is not an actual

processor register.

Pushing a byte of data onto the data stack involves the following steps: incrementing the DSP register, storing the

current contents of TOS at the address (BP+DSP) in memory, and moving the byte of data to TOS.

Popping a byte of data from the data stack involves the following steps: moving TOS to the destination, moving the

contents of the address (BP+DSP) in memory to TOS, and decrementing the DSP register.

The return stack grows from high memory towards low memory. Executing a subroutine call involves the following

steps: storing the high byte of the instruction pointer register IP at the address (BP+RSP) in memory, decrementing

RSP, storing the low byte of IP at the address (BP+RSP) in memory, decrementing RSP, and moving the destination

address to the IP register.

Similarly, returning from a subroutine involves the following steps: incrementing RSP, moving the contents of

(BP+RSP) to the low byte of the IP register, incrementing RSP, and moving the contents of (BP+RSP) to the high

byte of IP.

Return Stack

BP+RSP

TOS

BP+DSP

BP+0x18

BP+0x17

Sixteen Byte Registers

BP+0x8

BP+0x7

BP*

*BP = Base Page.

NEXT

Data Stack

Four 16-bit

Pointer Registers

Figure 2.4 Base Page Memory Layout

A processor instruction cycle is three system clock cycles, or six input clock (CLK1) cycles. Most instructions take

between one and seven processor instruction cycles. At an input clock rate of 40MHz, instruction times vary between

0.15 µs and 1.05 µs. Execution time scales inversely with the input clock rate. The formula for instruction time is:

<Instruction Time> = <# Cycles> x 6 / <Input Clock>

Tables 2.3, 2.42.4, and 2.5 list the processor instructions, their timings (in cycles) and sizes (in bytes). This is

provided for purposes of calculating the execution time and size of code sequences. All programming of the FT Smart

Transceiver is done with Neuron C using a LonBuilder or NodeBuilder development tool. The Neuron C compiler

can optionally produce an assembly listing, and examining this listing can help the programmer to optimize his/her

Neuron C source code.

FT 3120 / FT 3150 Smart Transceiver Data Book 11

Page 18

Chapter 2 - Hardware Resources

Table 2.3 Program Control Instructions

Mnemonic Cycles Size (bytes) Description Comments

NOP 1 1 No operation

SBR 1 1 Short unconditional branch Offset 0 to 15

BR/BRC/

BRNC

SBRZ/SBRNZ 3 1 Short branch on TOS (not)

BRF 4 3 Unconditional branch far Absolute address

BRZ/BRNZ 4 2 Branch on TOS (not) zero Offset -128 to +127. Drops TOS

RET 4 1 Return from subroutine Drops two bytes from return

BRNEQ 4/6 3 Branch if TOS not equal

DBRNZ 5 2 Decrement [RSP] and branch

CALLR 5 2 Call subroutine relative Offset -128 to +127. Pushes two

CALL 6 2 Call subroutine Address in low 8KB. Pushes

CALLF 7 3 Call subroutine far Absolute address. Pushes two

2 2 Branch, branch on (not) carry Offset -128 to +127

Offset 0 to 15. Drops TOS

zero

stack

Offset -128 to +127. Drops TOS

(taken/not taken)

if not zero

if equal

Offset -128 to +127. If not

taken, drops one byte from

return stack

bytes to return stack

two bytes to return stack

bytes to return stack

Table 2.4 Memory/Stack Instructions

Mnemonic Cycles Size (bytes) Comments / Effective Address (EA)

PUSH TOS 3 1 Increment DSP, duplicate TOS into NEXT

DROP TOS 3 1 Move NEXT to TOS, decrement DSP

DROP_R TOS 6 1 Move NEXT to TOS, decrement DSP, return from

call

PUSH (NEXT, DSP, RSP,

FLAGS)

POP (DSP, RSP, FLAGS) 4 1 Pop processor register

DROP NEXT 2 1 Decrement DSP

DROP_R NEXT 5 1 Decrement DSP and return from call

PUSH/POP !D 4 1 Byte register [8 to 23]

PUSH !TOS 4 1 EA = BP + TOS, push byte to NEXT

POP !TOS 4 1 EA = BP + TOS, pop byte from NEXT

PUSH [RSP] 4 1 Push from return stack to data stack, RSP

DROP [RSP] 2 1 Increment RSP

PUSHS #literal 4 1 Push short literal value [0 to 7]

PUSH #literal 4 2 Push 8-bit literal value [0 to 255]

PUSHPOP 5 1 Pop from return stack, push to data stack

POPPUSH 5 1 Pop from data stack, push to return stack

LDBP address 5 3 Load base page pointer with 16-bit value

PUSH/POP [DSP][-D] 5 1 EA = BP + DSP - displacement [1 to 8]

PUSHD #literal 6 3 16-bit literal value (high byte first)

PUSHD [PTR] 6 1 Push from 16-bit pointer [0 to 3], high byte first

4 1 Push processor register

unchanged

12 FT 3120 / FT 3150 Smart Transceiver Data Book

Page 19

Memory Allocation

POPD [PTR] 6 1 Pop to 16-bit pointer [0 to 3], low byte first

PUSH/POP [PTR][TOS] 6 1 EA = (16-bit pointer) + TOS

PUSH/POP [PTR][D] 7 2 EA = (16-bit pointer) + displacement [0 to 255]

PUSH/POP absolute 7 3 Absolute memory address

IN/OUT 7 + 4n 1 Fast I/O instruction, transfer n bytes

Table 2.5 ALU Instructions

Mnemonic Cycles Size (bytes) Operation

INC/DEC/NOT 2 1 Increment/decrement/negate TOS

ROLC/RORC 2 1 Rotate left/right TOS through carry

SHL/SHR 2 1 Unsigned left/right shift TOS, clear carry

SHLA/SHRA 2 1 Signed left/right shift TOS into carry

ADD/AND/OR/XOR/ADC 4 1 Operate with NEXT on TOS, drop NEXT

ADD/AND/OR/XOR #literal 3 2 Operate with literal on TOS

(ADD/AND/OR/XOR)_R 7 1 Operate with NEXT on TOS, drop NEXT and

return

ALLOC #literal 3 1 Add [1 to 8] to data stack pointer

DEALLOC_R #literal 6 1 Subtract [1 to 8] from data stack pointer and return

SUB NEXT,TOS 4 1 TOS = NEXT - TOS, drop NEXT

SBC NEXT, TOS 4 1 TOS = NEXT - TOS - carry, drop NEXT

SUB TOS,NEXT 4 1 TOS = TOS - NEXT, drop NEXT

XCH 4 1 Exchange TOS and NEXT

INC [PTR] 6 1 Increment 16-bit pointer [0 to 3]

Memory Allocation

FT 3120 Smart Transceiver

See Figure 2.6 for a memory map of the FT 3120 Smart Transceiver.

• 4,096 bytes of in-circuit programmable EEPROM that store:

— Network configuration and addressing information.

— Unique 48-bit Neuron ID (written at the factory).

— User-written application code and read-mostly data.

• 2,048 bytes of static RAM that store the following:

— Stack segment, application, and system data.

— Network buffers and application buffers.

• 12,288 bytes of ROM that store the following:

— The Neuron firmware, including the system firmware executed by the MAC and network processors, and

the executive supporting the application program.

FT 3150 Smart Transceiver

See Figure 2.5 for a memory map of the FT 3150 Smart Transceiver.

• 512 bytes of in-circuit programmable EEPROM that store the following:

— Network configuration and addressing information.

FT 3120 / FT 3150 Smart Transceiver Data Book 13

Page 20

Chapter 2 - Hardware Resources

r

— Unique 48-bit Neuron ID (written at the factory).

— User-written application code and read-mostly data. See Table 2.6 for available EEPROM space.

• 2,048 bytes of static RAM that store the following:

— Stack segment, application, and system data.

— Network and application buffers.

• The processor can access 59,392 bytes of the available 65,536 bytes of memory address space via the exter-

nal memory interface. The remaining 6,144 bytes of the memory address space are mapped internally.

• 16,384 bytes of the external memory (59,392 bytes total) are required to store the following:

— The Neuron firmware, including the system firmware executed by the MAC and Network processors, and

the executive supporting the application program.

• The rest of the external memory (43,008 bytes) is available for:

— User-written application code.

— Additional application read/write and non-volatile data.

— Additional network buffers and application buffers.

FFFF

FC00

FBFF

F200

F1FF

F000

EFFF

E800

E7FF

4000

3FFF

0000

1K Reserved Space For

Memory Mapped I/O

2.5K Reserved Space

0.5K EEPROM

2K RAM

42K of Memory

Space Available

to the User

16K Neuron

Firmware and

Reserved Space

Figure 2.5 FT 3150 Smart Transceiver

Memory Map

Internal

External

FFFF

FC00

FBFF

F000

EFFF

E800

4FFF

4C00

2FFF

0000

1K Reserved Space For

Memory Mapped I/O

3K EEPROM

2K RAM

Unavailable

1K EEPROM

Unavailable

12K Neuron Firmware

(ROM)

Figure 2.6 FT 3120 Smart Transceive

Memory Map

Internal

EEPROM

Both versions of the FT Smart Transceiver have internal EEPROM containing:

• Network configuration and addressing information.

14 FT 3120 / FT 3150 Smart Transceiver Data Book

Page 21

Memory Allocation

• Unique 48-bit Neuron ID.

• Optional user-written application code and data tables.

All but 8 bytes of the EEPROM can be written under program control using an on-chip charge pump to generate the

required programming voltage. The charge pump operation is transparent to the user. The remaining 8 bytes are

written during manufacture, and contain a unique 48-bit identifier for each part called the Neuron ID, plus 16 bits for

the device code of the chip manufacturer. Each byte in the EEPROM region may be written up to 10,000 times. For

both the FT Smart Transceivers, the EEPROM stores the installation-specific information such as network addresses

and communications parameters. For the FT 3120 Smart Transceiver, the EEPROM also stores the application

program generated by the LonBuilder or NodeBuilder development tools. The application code for the FT 3150

Smart Transceiver may be stored either on-chip in the EEPROM memory or off-chip in external memory depending

on the size of the application code. See Table 2.6 for available EEPROM space.

For all write operations to the internal EEPROM, the Neuron firmware automatically compares the value in the

EEPROM location with the value to be written. If the two are the same, the write operation is not performed. This

prevents unnecessary write cycles to the EEPROM, and reduces the average EEPROM write cycle latency.

When the FT Smart Transceiver is not within the specified power supply voltage range, a pending or on-going

EEPROM write is not guaranteed. The FT Smart Transceiver contains a built-in low-voltage interruption (LVI)

circuit that holds the chip in reset when V

Transceiver Datasheet for LVI trip points. This prevents EEPROM data corruption, although in some cases,

additional external protection may be appropriate. See section , RESET Pin, for more information on LVI circuitry.

In the event of a fault, the on-chip EEPROM of the FT 3150 Smart Transceiver can be reset to its factory default state

by executing the EEBLANK program. To do so, program the EEBLANK.NRI file into an external memory device,

temporarily replace the external ROM or flash for the application with the chip that has EEBLANK.NRI loaded, and

power up the device.

is below a certain voltage. See the FT 3120 and FT 3150 Smart

CC

After some time, the service LED of the device should come on solid, indicating that the EEPROM has been blanked.

Then replace the original application ROM or flash. The EEBLANK.NRI file is distributed with the LonBuilder 3.01

(Service Pack 5), NodeBuilder 1.5 (Service Pack 8 or greater), and NodeBuilder 3 (Service Pack 1 or greater)

development tools. The file may also be downloaded from the developer’s toolbox located on the Echelon website

(www.echelon.com). Versions of EEBLANK.NRI distributed before these Service Packs should not be used with

the FT 3150 Smart Transceiver.

The set_eeprom_lock() function can also be used for additional protection against accidental EEPROM data

corruption. This function allows the application program to set the state of the lock on the checksummed portion of

the EEPROM. Refer to the Neuron C Reference Guide for more information.

The internal EEPROM of a FT Smart Transceiver will contain a fixed amount of overhead and a network image

(configuration), in addition to user code and user data. The following table shows the maximum amount of EEPROM

space available for user code and user data assuming a minimally-sized network image. Also shown is the minimum

segment size for user data. Constant data is assumed to be part of the code space.

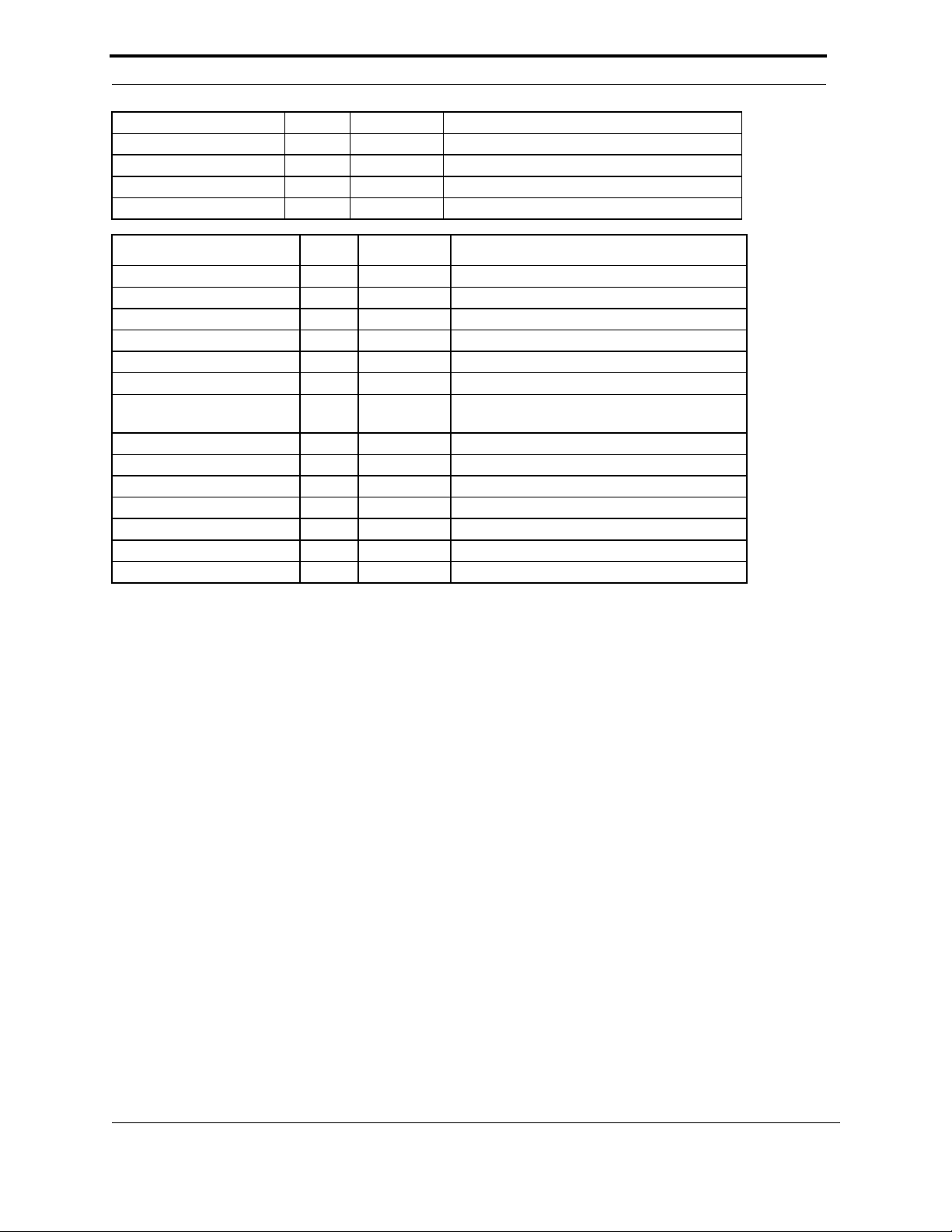

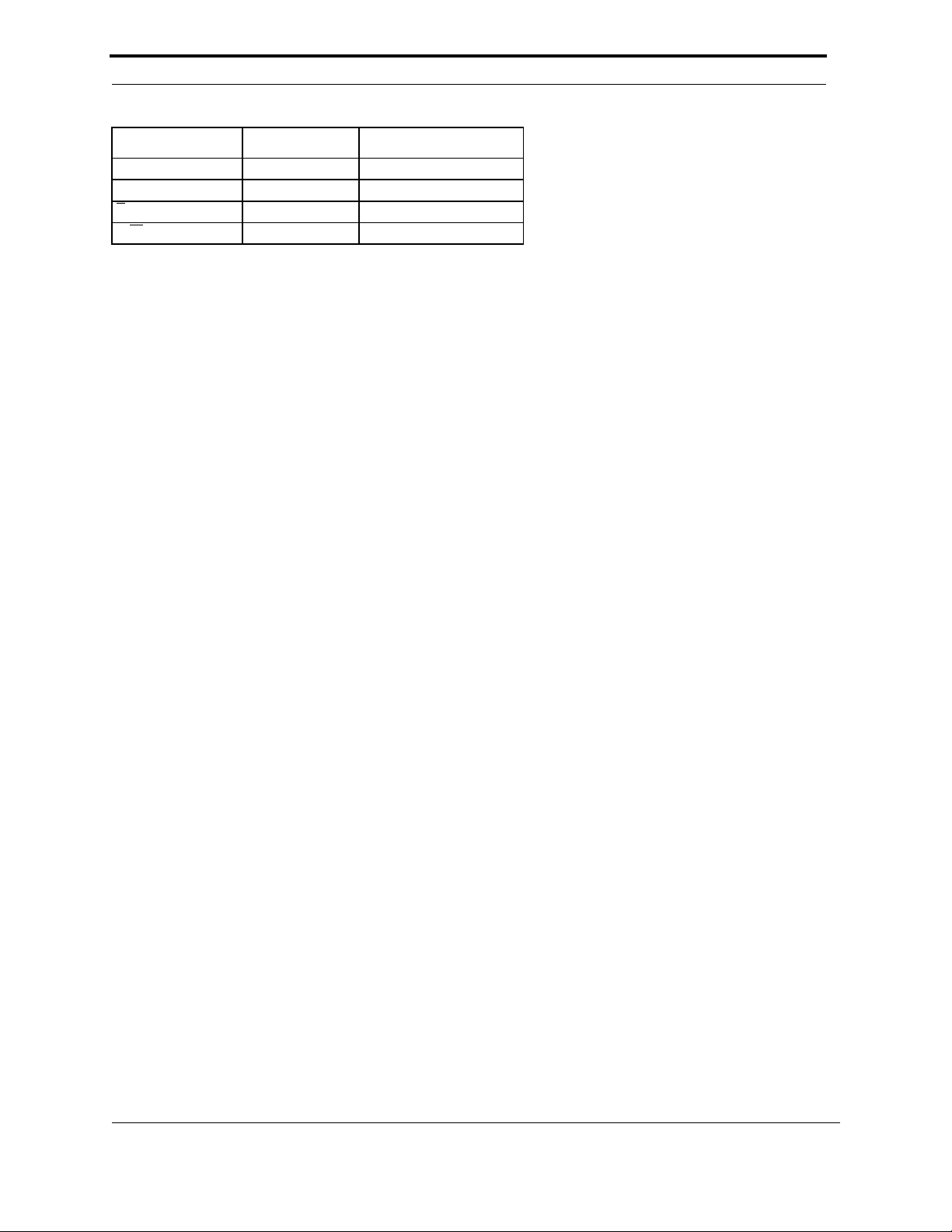

Table 2.6 Memory Usage

Device Firmware Version

FT 3120 Smart Transceiver 13 3969 8

FT 3150 Smart Transceiver 13 384 2

EEPROM Space

(Bytes)

Segment Size

(Bytes)

EEPROM must be allocated in increments of the device's segment size, the smallest unit of EEPROM that can be

allocated for variable space. For example, if there are three 3-byte variables used, there must be 9 bytes of variable

space. For an FT 3120 Smart Transceiver, this would result in the allocation of 16 bytes for variable space, as 16

bytes is the lowest increment of the device segment size (8 bytes) that can store the three 3-byte variables. For an FT

3150 Smart Transceiver, this would result in the allocation of 10 bytes for variable space, as 10 bytes is the lowest

increment of the device segment size (2 bytes) that can store the three 3-byte variables.

FT 3120 / FT 3150 Smart Transceiver Data Book 15

Page 22

Chapter 2 - Hardware Resources

Static RAM

Both FT Smart Transceivers contain 2048 bytes of static RAM. The RAM is used to store the following:

• Stack segment, application, and system data

• Network buffers and application buffers

The RAM state is retained as long as power is applied to the device. After reset, releasing the FT Smart Transceiver

initialization sequence will clear the RAM (see the section Reset Processes and Timing, later in this chapter).

Preprogrammed ROM

The FT 3120 Smart Transceiver contains 12,288 bytes of pre-programmed ROM. This memory contains the Neuron

firmware, including the LonTalk protocol stack, real time task scheduler, and system function libraries. The Neuron

firmware for the FT 3150 Smart Transceiver is stored in external memory. The object code is supplied with the

LonBuilder and NodeBuilder tools.

External Memory of the FT 3150 Smart Transceiver

External memory is support only for the FT 3150 Smart Transceiver. The memory interface supports up to 42Kbytes

of external memory space for additional user program and data. The total address space is 64Kbytes. However, the

upper 6K of address space is reserved for internal RAM, EEPROM, and memory-mapped I/O (see Figure 2.5 and

Figure 2.6), leaving 58K of external address space. Of this space, 16K is used by the Neuron firmware and is reserved

for other specific functions. The external memory space can be populated with RAM, ROM, PROM, EPROM,

EEPROM, or flash memory in increments of 256 bytes. The memory map for the FT 3150 Smart Transceiver is

shown in Figure 2.5. The bus has 8 bidirectional data lines and 16 address lines driven by the processor. Two interface

lines (R/W

Datasheet for the required access times for the external memory used. If the input clock is scaled down, slower

memory can be used. The input clock rates supported by the FT 3150 Smart Transceiver are 20MHz, 10MHz, and

5MHz. The Enable Clock (E

internal and external, may be accessed by any of the three processors at the appropriate phase of the instruction cycle.

Since the instruction cycles of the three processors are offset by one-third of a cycle with respect to each other, the

memory bus is used by only one processor at a time.

and E) are used for external memory access. Refer to the FT 3120 and FT 3150 Smart Transceiver

) runs at the system clock rate, which is one-half the input clock rate. All memory, both

The Neuron 3150 Chip External Memory Interface engineering bulletin provides guidelines for interfacing the FT

3150 Smart Transceiver to different types of memory. A minimum hardware configuration would use one external

ROM (PROM or EPROM), containing both the Neuron firmware and user application code. This configuration

would not allow the system engineer to change the application code after installation. The network image (network

address and connection information) however, could be altered because this information resides in internal

EEPROM. If application downloads over the network are a requirement for maintenance or upgrade and the

application code will not fit into the internal EEPROM, then external EEPROM or flash will be necessary. Refer to

the Neuron C Programmer’s Guide for guidelines to reduce code size.

The pins used for external memory interfacing are listed in Table 2.7. The E

write) signals to external memory. The A15 (address line 15) or a programmable array logic (PAL) decoded signal

gated with R/W

16 FT 3120 / FT 3150 Smart Transceiver Data Book

can be used to generate read signals to external memory.

clock signal is used to generate read (or

Page 23

Input/Output

Table 2.7 External Memory Interface Pins

Pin Designation Direction Function

A0 – A15 Output Address Pins

D0 – D7 Input/Output Data Pins

E Output Enable Clock

R/W Output Read/Write Select Low

The preferred method of interfacing the FT Smart Transceiver to another MPU is through the 11 I/O pins using a

serial or parallel connection, or through a dual-ported RAM device such as the Cypress CY7C144, CY7C138, or

CY7C1342. There are pre-defined serial and parallel I/O models for this purpose which are easily implemented using

the Neuron C programming language, or the short stack or MIP firmware can be used to simplify the interface. For

more details of dual-ported RAM interfacing, see Appendix B of the L

User’s Guide (Echelon 078-0017-01).

ONWORKS Microprocessor Interface Program

Input/Output

Eleven Bidirectional I/O Pins

These pins are usable in several different configurations to provide flexible interfacing to external hardware and

access to the internal timer/counters. The logic level of the output pins may be read back by the application processor.

See Section 6 for detailed electrical characteristics.

Pins IO4 – IO7 have programmable pull-up current sources. They are enabled or disabled with a compiler directive

(see the Neuron C Reference Guide). Pins IO0 – IO3 have high current sink capability (20 mA @ 0.8 V). The others

have the standard sink capability (1.4 mA @ 0.4 V). All pins (IO0 – IO10) have TTL level inputs with hysteresis.

Pins IO0 – IO7 also have low level detect latches.

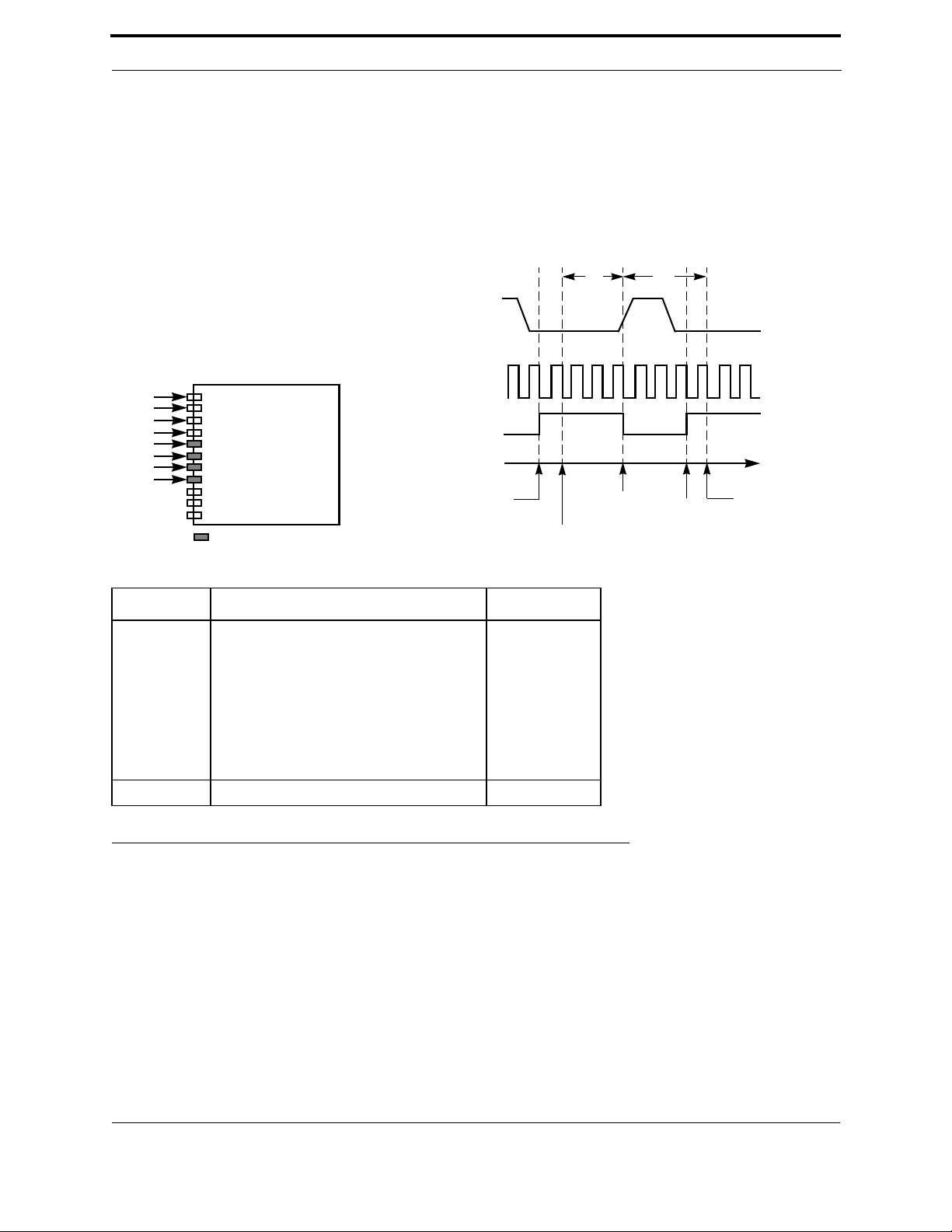

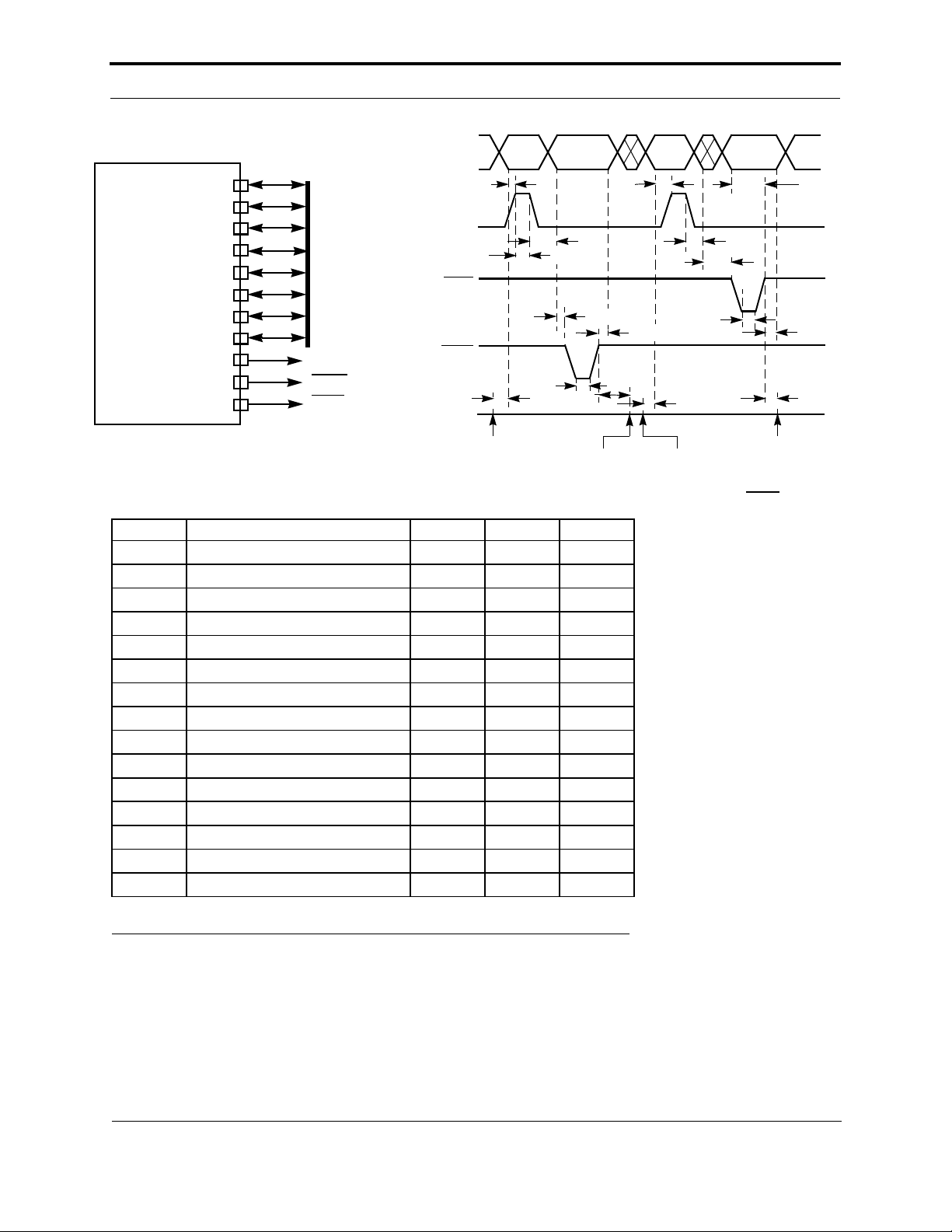

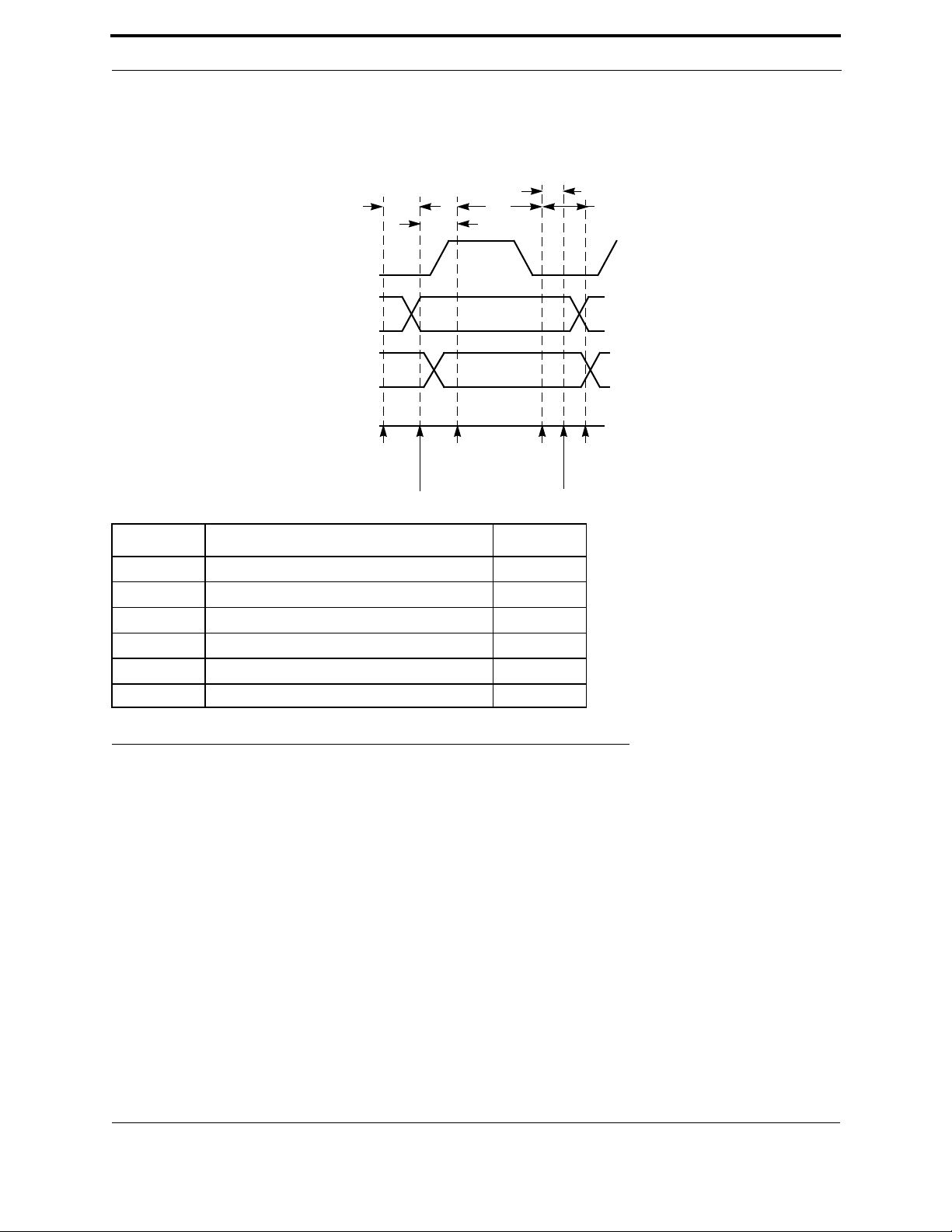

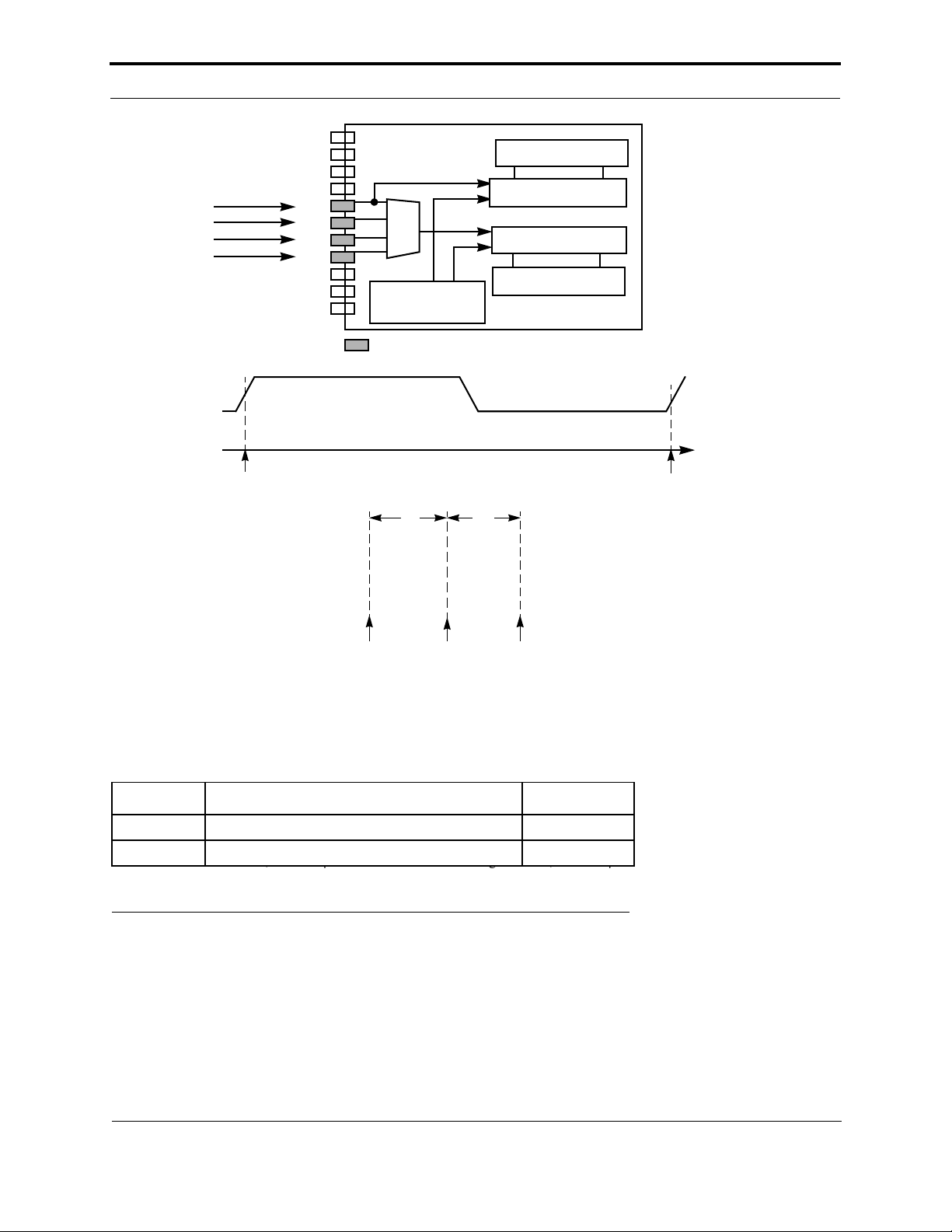

Two 16-Bit Timer/Counters

The timer/counters are implemented as a load register writable by the processor, a 16-bit counter, and a latch readable

by the processor. The 16-bit registers are accessed 1 byte at a time. Both the FT 3120 and FT 3150 Smart

Transceivers have one timer/counter whose input is selectable among pins IO4 – IO7, and whose output is pin IO0,

and a second timer/counter with input from pin IO4 and output to pin IO1 (Figure 2.7). No I/O pins are dedicated to

timer/counter functions. If, for example, Timer/Counter 1 is used for input signals only, then IO0 is available for other

input or output functions. Timer/counter clock and enable inputs may be from external pins, or from scaled clocks

derived from the system clock; the clock rates of the two timer/counters are independent of each other. External clock

actions occur optionally on the rising edge, the falling edge, or both rising and falling edges of the input.

FT 3120 / FT 3150 Smart Transceiver Data Book 17

Page 24

Chapter 2 - Hardware Resources

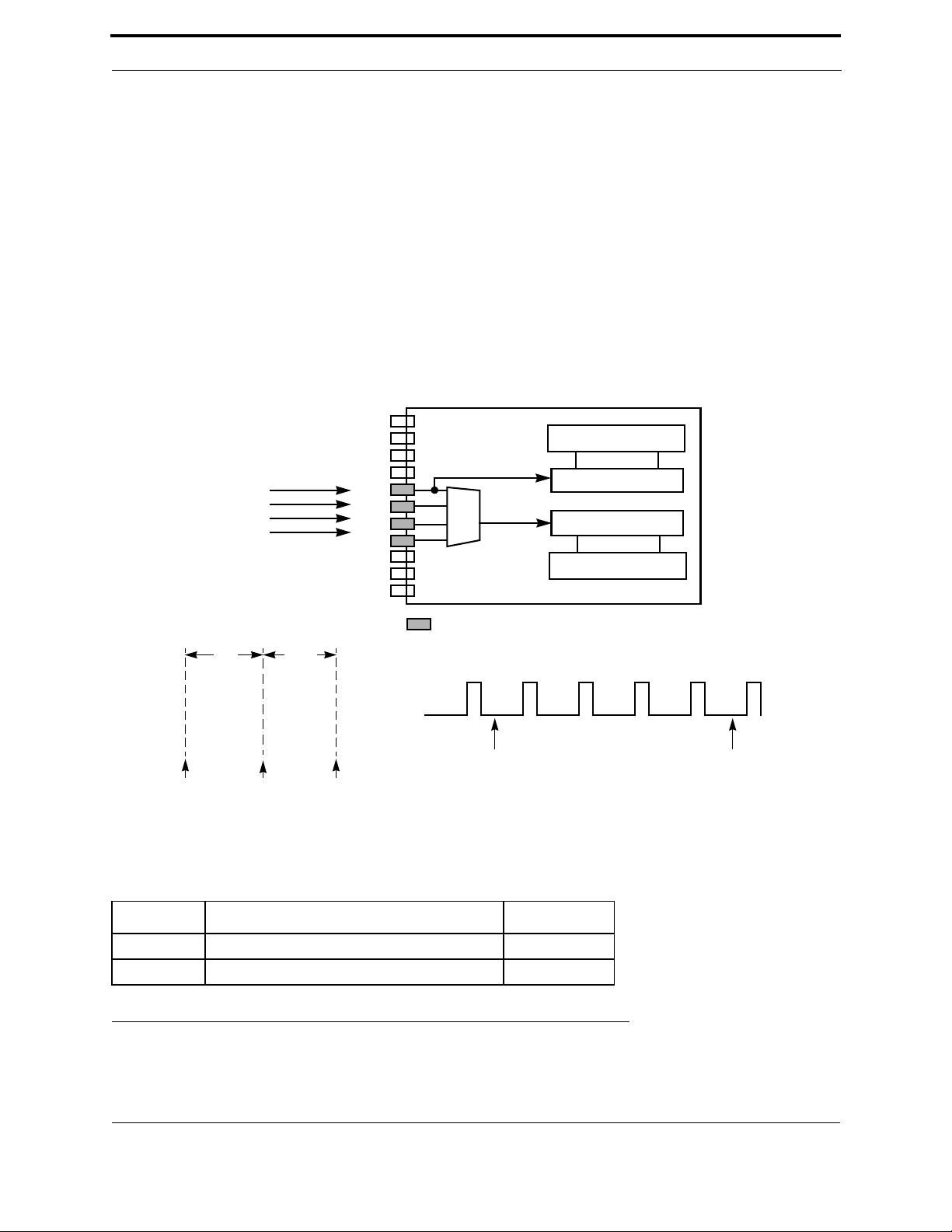

IO7

IO6

IO5

IO4

IO3

IO2

IO1

IO0

System Clock Divide

Chain

Control

Logic

MUX

Control

Logic

System Clock Divide

Chain

Timer/Counter 1

Timer/Counter 2

Figure 2.7 Timer/Counter Circuits

Clock Input

The FT Smart Transceivers operate with an input clock of 5, 10, or 20MHz. The FT 3120 Smart Transceiver also

supports 40MHz operation. Developers who are using the LonBuilder 3.0.1 or NodeBuilder 1.5 tools and are

upgrading to a clock speed higher than 10MHz should refer to the readme.txt file included in the latest Service Pack

for the LonBuilder 3.01, or for NodeBuilder 1.5 tools for an in-depth discussion about the software considerations on

each platform. The NodeBuilder 3.2 (or later) development tool contains built-in support for these higher clock

speeds.

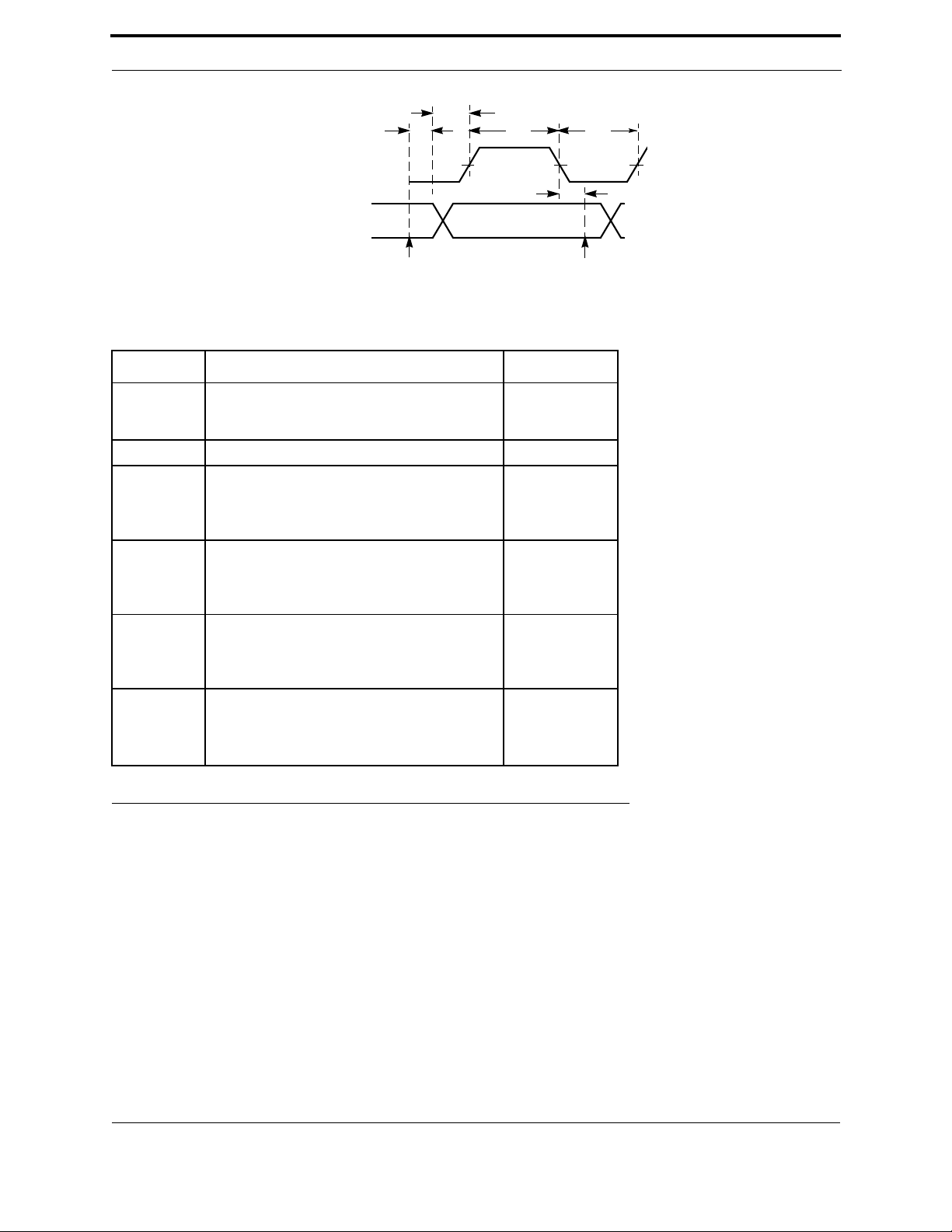

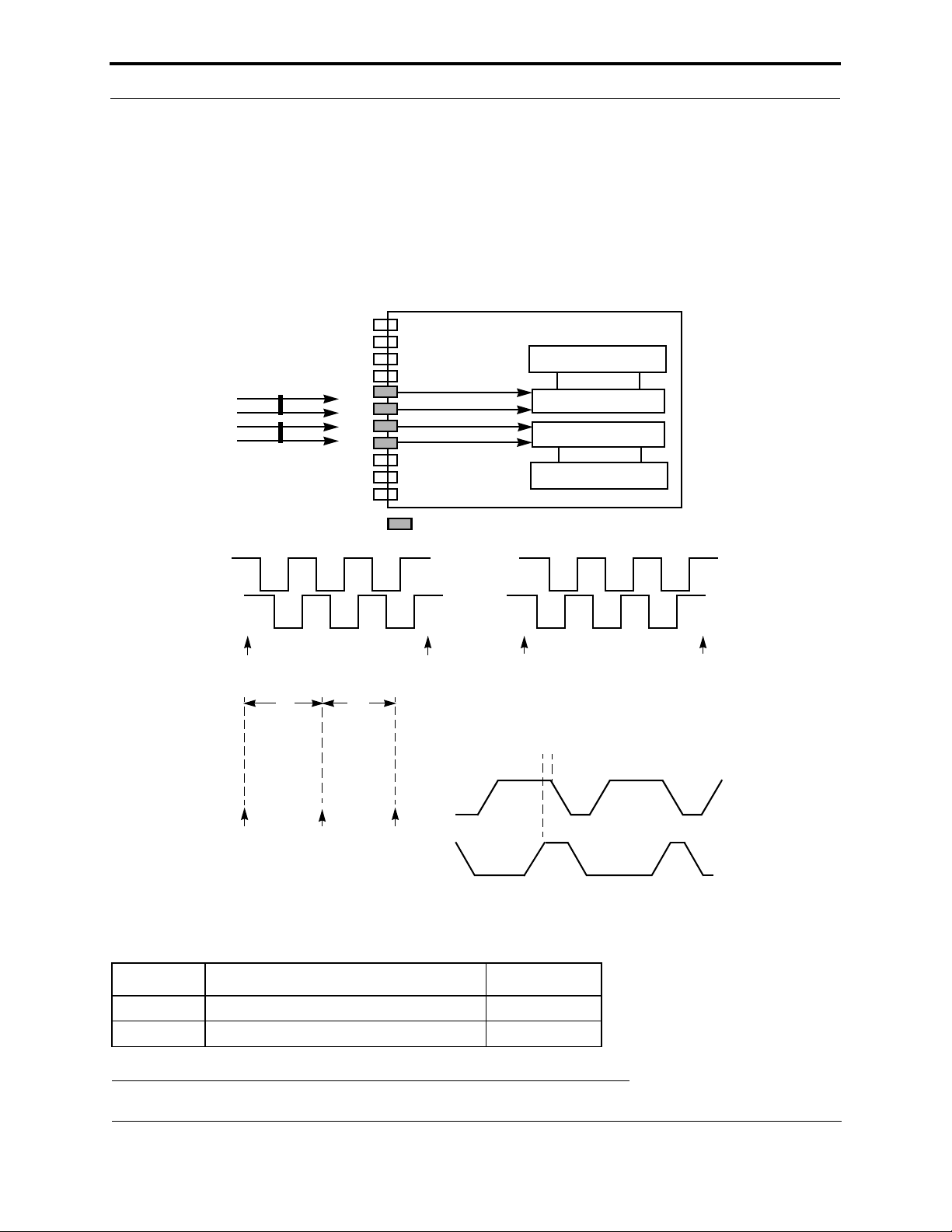

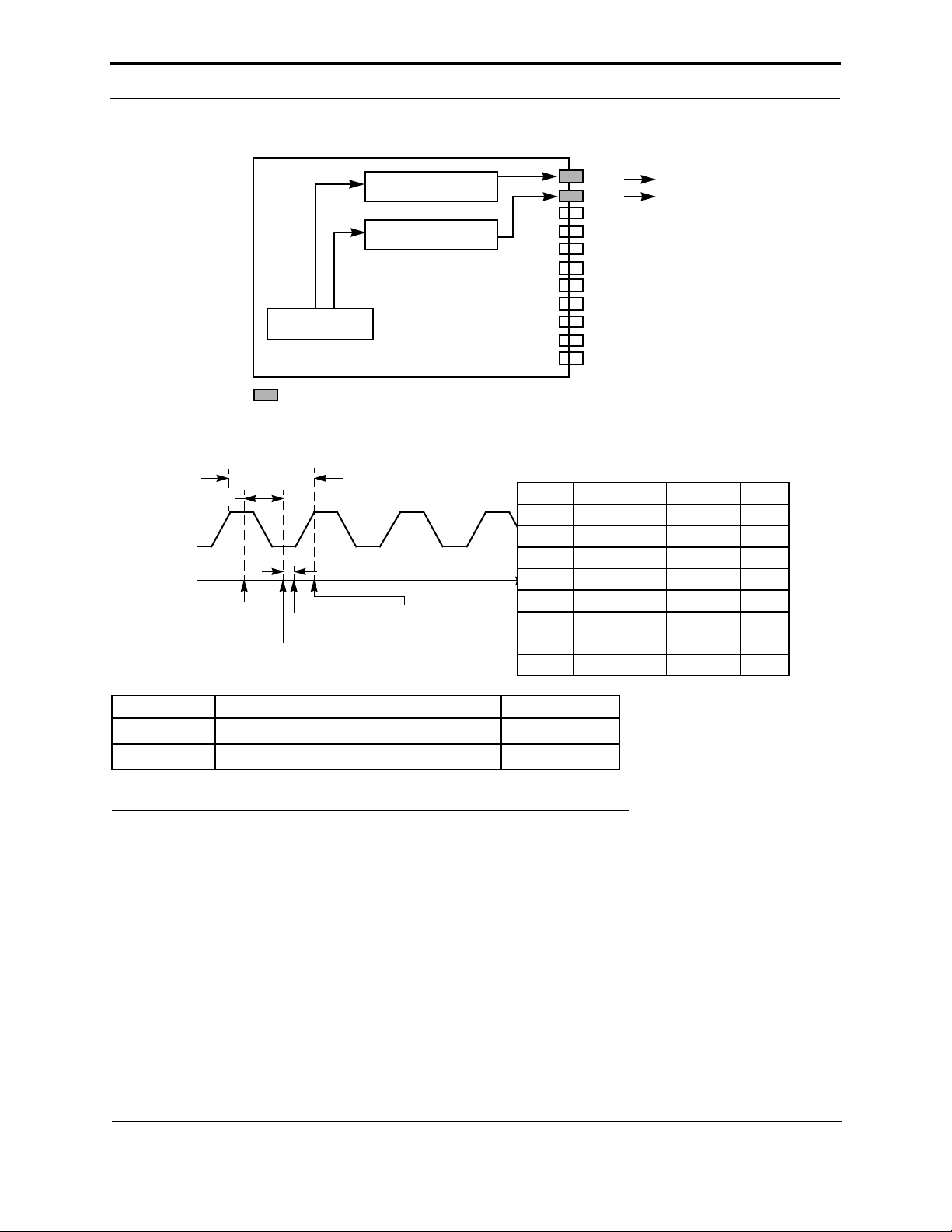

Clock Generation

The FT Smart Transceiver divides the input clock by a factor of two to provide a symmetrical on-chip system clock.

The input clock may be generated either by an external free-running oscillator or by the on-chip oscillator in the

Smart Transceiver using an external parallel-mode resonant crystal.

The accuracy of the input clock frequency of the FT Smart Transceiver must be ±200ppm or better; this requirement

can be met with a suitable crystal, but cannot be met with a ceramic resonator.

The FT Smart Transceiver includes an oscillator that may be used to generate an input clock using an external crystal.

For 5 MHz, 10MHz, and 20MHz, either an external clock source or the on-chip crystal oscillator may be used. For

40MHz operation of an FT 3120 Smart Transceiver, an external oscillator must be used.

When an externally generated clock is used to drive the CLK1 CMOS input pin of the FT Smart Transceiver, CLK2

must be left unconnected or used to drive no more than one external CMOS load. The accuracy of the clock

frequency must be ± 0.02% (200 ppm) or better, to ensure that devices may correctly synchronize their bit clocks.

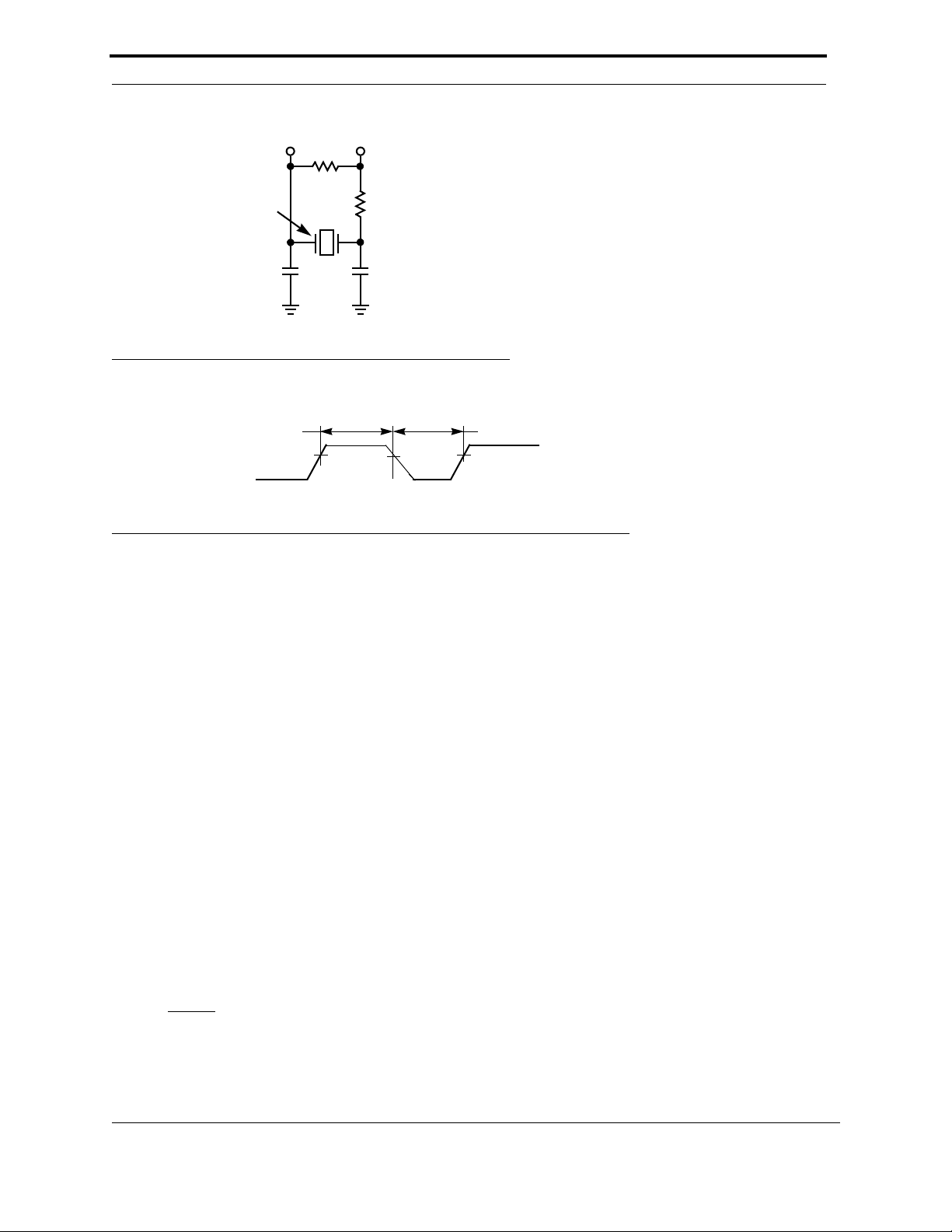

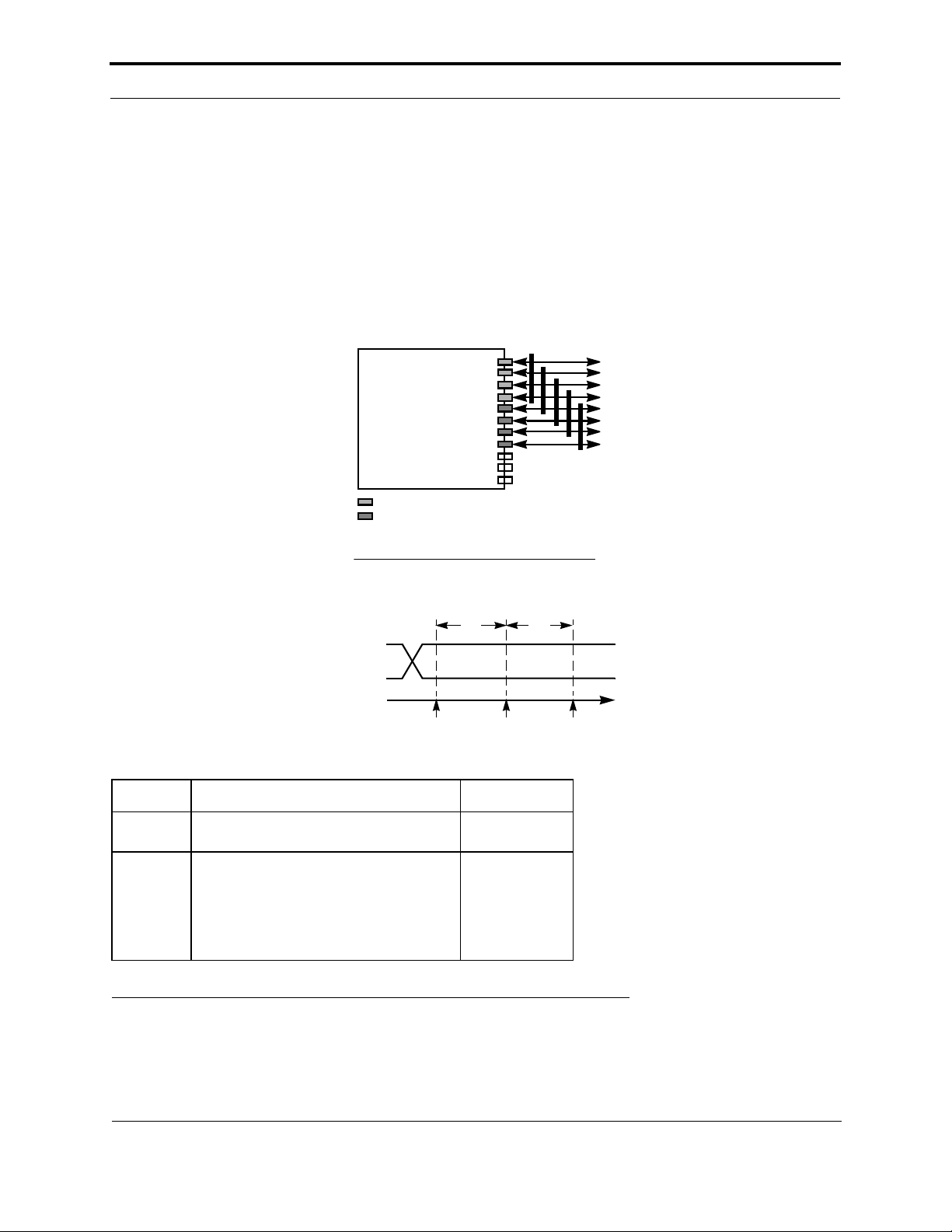

Figure 2.8 shows the crystal oscillator circuit. Use the load capacitance and resistor values recommended by the

manufacturer of the crystal for this circuit. A 60/40 duty cycle or better is required when using an external oscillator

as shown in Figure 2.9. An external oscillator must provide CMOS voltage levels to the CLK1 pin.

18 FT 3120 / FT 3150 Smart Transceiver Data Book

Page 25

CLK 2CLK1

R

f

EXTERNAL

CRYSTAL

CC

R

Figure 2.8 Smart Transceiver Clock Generator Circuit

Additional Functions

PW

HIGH

VDD /2VDD /2

PW

LOW

V

/2

DD

Figure 2.9 Test Point Levels for CLK1 Duty Cycle Measurements

The FT 3120 Smart Transceiver was designed to run at frequencies up to 40MHz using an external clock oscillator.

External oscillators generally take several milliseconds to stabilize after power-up. The FT 3120 Smart Transceiver

operating at 40MHz must be held in reset until the externally-generated CLK input is stable, so an external poweron-reset-pulse stretching LVI chip/circuit is required. Check the specification of the oscillator vendor for more

information about startup stabilization times.

Additional Functions

Reset Function

The reset function is a critical operation in any embedded microcontroller. In the case of theFT 3120 and FT 3150

Smart Transceivers, the reset function plays a key role in the following conditions:

• Initial V

• V

DD

• Program recovery (if an application gets lost due to corruption of address or data, an external reset can be

used for recovery or the watchdog timer could timeout, causing a watchdog reset).

• V

DD

• Helps protect the EEPROM from major corruption.

power up (ensures proper initialization of the FT Smart Transceiver).

DD

power fluctuations (manages proper recovery of FT Smart Transceiver after VDD stabilizes).

power down (ensures proper shut down).

The FT Smart Transceivers have four mechanisms to initiate a reset:

• RESET pin is pulled low and then returned high.

• Watchdog timeout occurs during application execution (the timeout period is 210ms at 40MHz; this figure

scales inversely with clock frequency).

FT 3120 / FT 3150 Smart Transceiver Data Book 19

Page 26

Chapter 2 - Hardware Resources

• Software command either the from the application program or from the network.

• LVI circuit detects a drop in the power supply below a set level.

During any of the reset functions, when the RESET

states described in the list below. Figure 2.11 also illustrates the condition of the pins during reset and the FT Smart

Transceivers initialization sequence after reset is returned high again.

pin is in the low state, the FT Smart Transceiver pins go to the

• Oscillator continues to run

• All processor functions stop

• SERVICE pin goes to high impedance

• I/O pins go to high impedance

• All output address pins go to 0xFFFF (FT 3150 Smart Transceiver only)

• All data pins become outputs with high or low states (FT 3150 Smart Transceiver only)

• E clock goes high (FT 3150 Smart Transceiver only)

• R/W goes low (FT 3150 Smart Transceiver only)

When the RESET

starting at address 0x0001. The time it takes the FT Smart Transceiver to complete its initialization differs between

FT Smart Transceivers, the different firmware versions that are being run, and the memory space used by the

application (code and data). This will be discussed later in this section.

pin is released back to a high state, the FT Smart Transceiver begins its initialization procedure

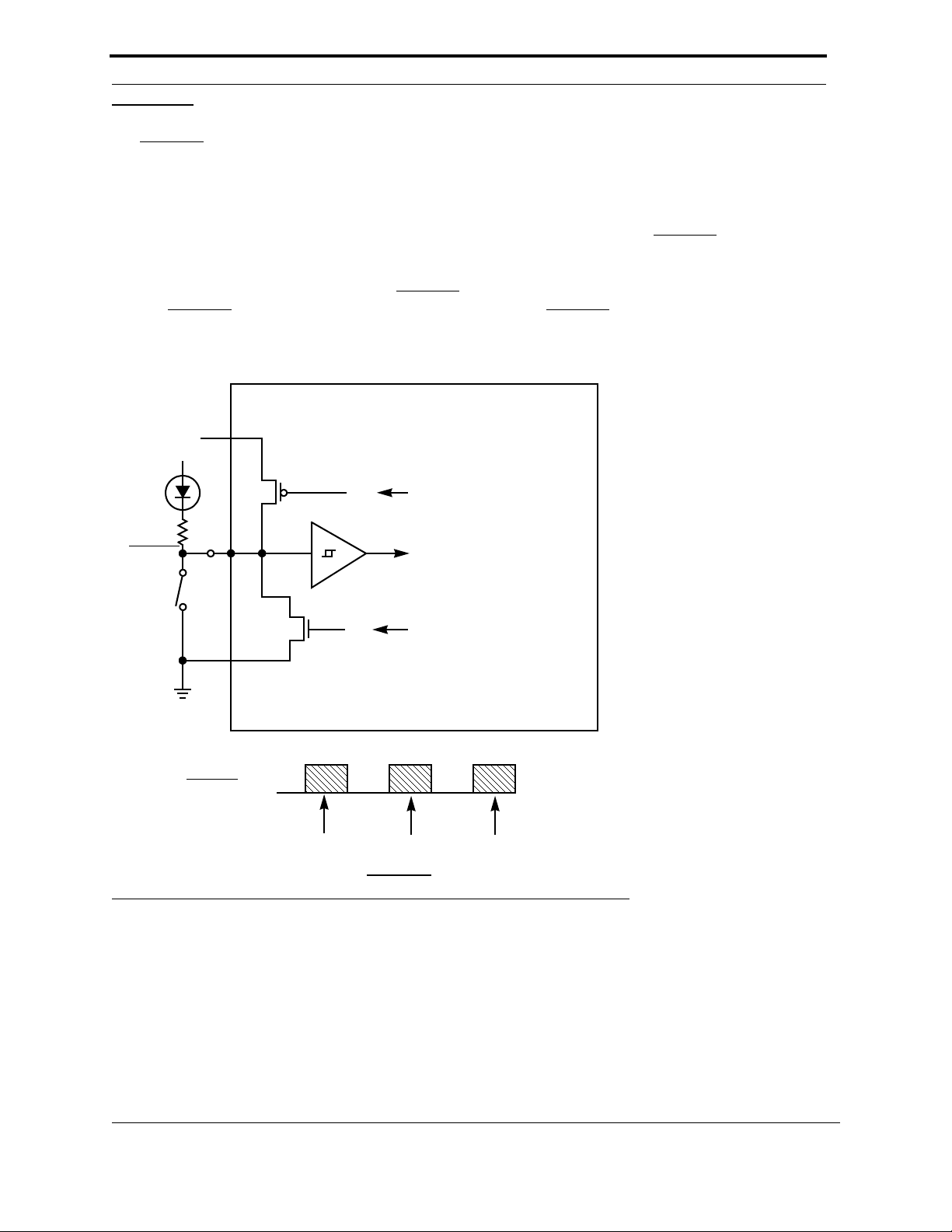

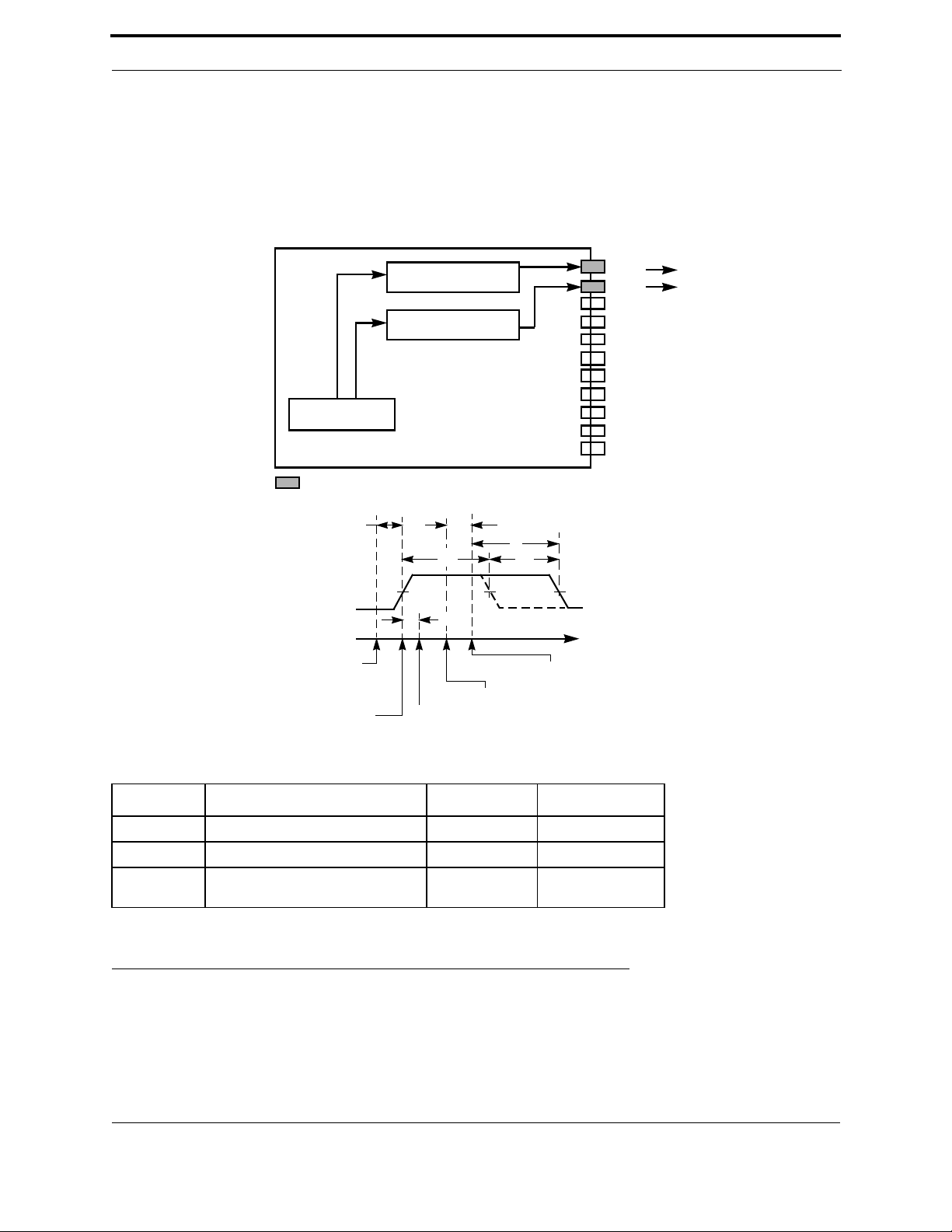

RESET Pin

The RESET pin is both an input and an output. As an input, the RESET pin is internally pulled high by a current

source acting as a pull-up resistor. The RESET

pin becomes an output when any of the following events occur:

• Watchdog Timer event.

• Software reset initialization.

• Internal LVI detects a low voltage.

• RESET pin drops below the internal trip point.

Power Up Sequence

During power up sequences, the RESET

malfunctioning. Likewise, when powering down, the FT Smart Transceiver RESET

before the power supply goes below the minimum operating voltage of the FT Smart Transceiver.

WARNING: If proper reset recovery circuitry is not used, the FT Smart Transceiver can go applicationless or

unconfigured. The applicationless or unconfigured state occurs when the checksum error verification routine detects

a corruption in memory which could have falsely been detected due to improper reset sequence or noise on the power

supply. Several options exist in the LonBuilder and NodeBuilder tools to allow a reboot on checksum failure.

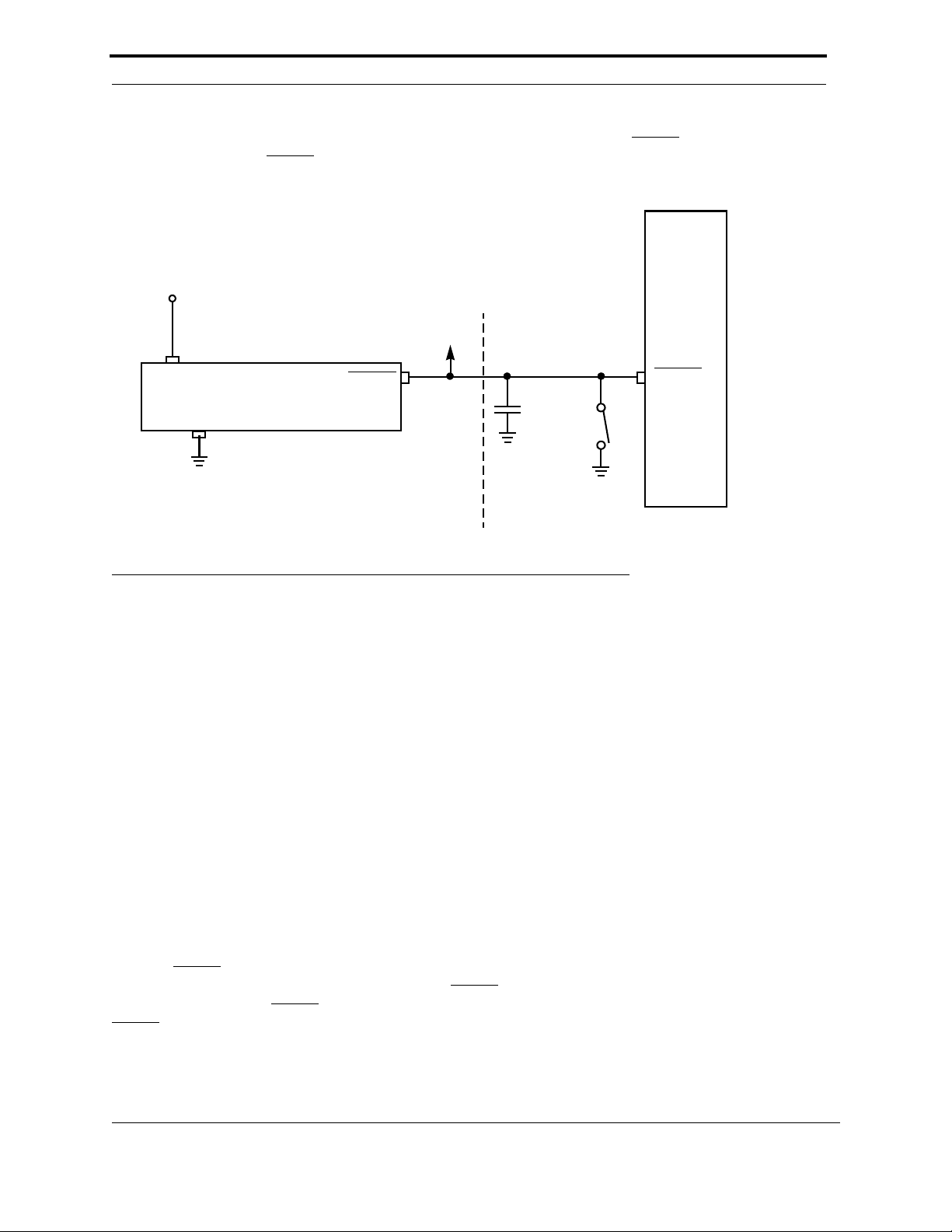

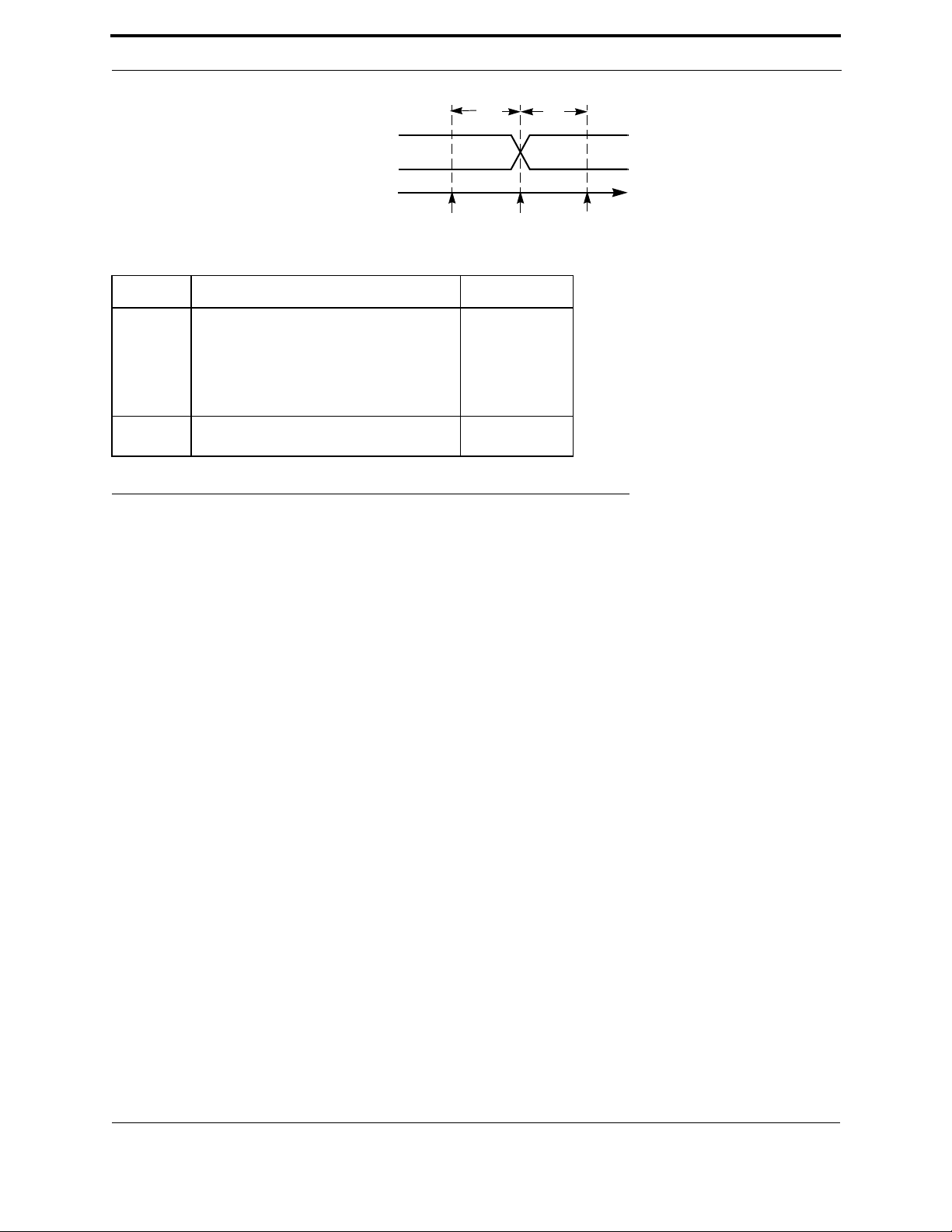

Figure 2.11 shows typical external RESET

including stray and external device input capacitance, must not exceed 1000 pF. This ensures that the FT Smart

Transceiver can successfully output a reset down to below 0.8V. The 100 pF minimum capacitance is required for

noise immunity.

pin should be held low until the power supply is stable, to prevent start-up

pin should go to a low state

components. The total capacitance directly connected to the RESET pin,

20 FT 3120 / FT 3150 Smart Transceiver Data Book

Page 27

Software Controlled Reset

Additional Functions

When the CPU watchdog timer expires, or a software command to reset occurs, the RESET

CLK1 clock cycles. The RESET

pin and external capacitor (100 ≤ x ≤ 1000 pF) are allowed to begin charging and

provide the required duration of reset.

Smart Transceiver

5V V

DD

To O t her

Devices

IN

LV I

GND

If using flash, an external pulse-stretching LVI must be used

(Dallas DS1233-10).

RESET

C

E

(100 pF Min

1000 pF Max)

Switch

RESET

Figure 2.10 Example of a Reset Circuit

pin is pulled low for 256

Watchdog Timer

The FT Smart Transceivers are protected against malfunctioning software or memory faults by three watchdog

timers, one for each processor that makes up the Neuron core. If application or system software fails to reset these

timers periodically, the entire FT Smart Transceiver is automatically reset. The watchdog period is approximately 210

ms at a 40MHz input clock rate and scales inversely with the input clock rate.

LVI Considerations

The FT 3120 and FT 3150 Smart Transceivers include an internal LVI to ensure that they only operate above the

minimum voltage threshold. See the FT 3120 and FT 3150 Smart Transceiver Datasheet for LVI trip points. If the

circuit operates below this voltage, improper operation could occur. For example, if the FT Smart Transceiver is

writing to an internal or external EEPROM or to flash memory when a reset event is initiated, then that data could be

corrupted.

When using external flash memory for the FT 3150 Smart Transceiver device, an external pulse-stretching LVI of

greater than 50 ms should be used (Echelon recommends using Dallas Semiconductor Part No. DS1233-5). When

using an external oscillator to drive the CLK1 pin of either of the FT Smart Transceivers, a power-on-pulse-stretching

LVI may be needed to ensure that the external oscillator has stabilized before the FT Smart Transceiver is released

from reset.

Since the RESET

collector output. If an external LVI actively drives the RESET

able to reliably assert the RESET

RESET

pin can cause anomalous behavior, from applicationless errors to physical damage to the FT Smart

pin of the FT Smart Transceiver is bidirectional, an external LVI must have an open-drain or open-

pin high, then the FT Smart Transceiver will not be

pin (low) during internal resets. This contention on the FT Smart Transceiver

Transceiver reset circuitry.

FT 3120 / FT 3150 Smart Transceiver Data Book 21

Page 28

Chapter 2 - Hardware Resources

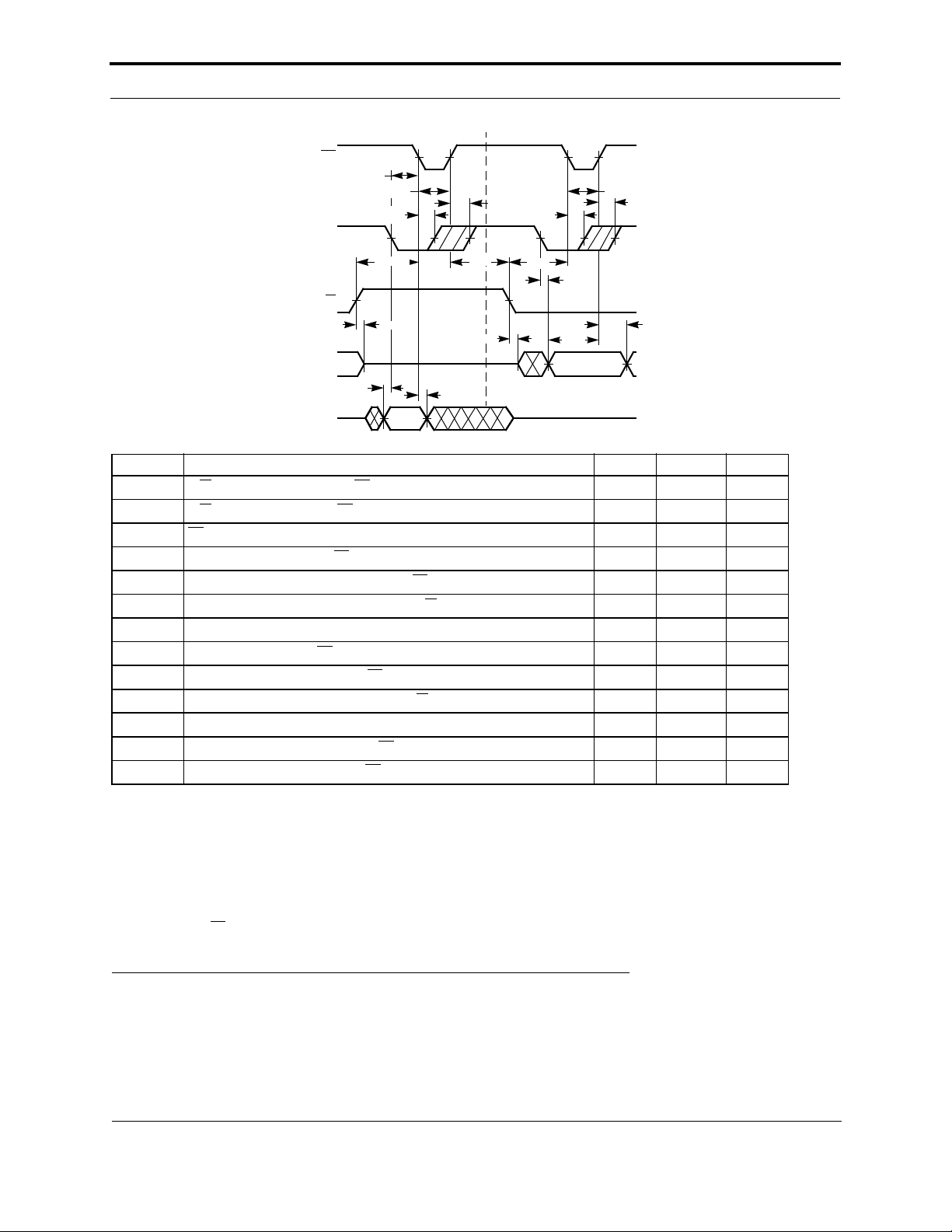

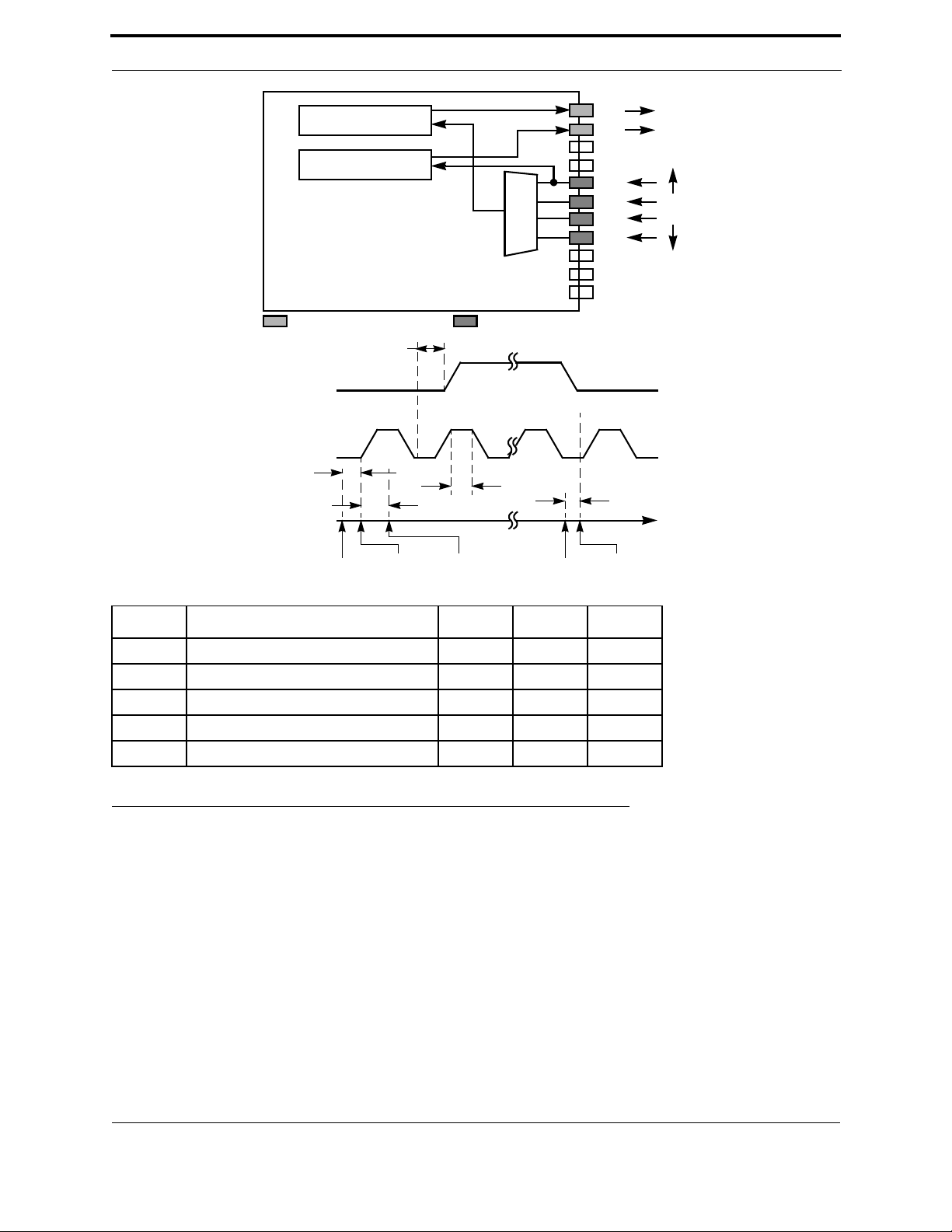

Reset Processes and Timing

During the reset period, the I/O pins are in a high-impedance state. The FT 3150 Smart Transceiver address lines A15

– A0 are forced to 0xFFFF, R/W

or low, so they will not float and draw excess current. The SERVICE

overrides the effect of E

during the E

preparing the FT Smart Transceiver to execute the application code are discussed below. These steps are summarized

in Figure 2.11.

clock low portion of the bus cycle, while reset forces the data bus to be driven. The steps followed in

clock on data lines in that, in normal operations the data bus is only driven in a write cycle

is forced to 0, and E is forced to 1. The data lines are undetermined but driven high

pin is high impedance during reset. Reset

After the RESET

executing application programs. These tasks are:

pin is released, the FT Smart Transceiver performs hardware and firmware initialization before

• Oscillator start-up

• Oscillator stabilization

• Stack initialization and built-in self-test (BIST)

• SERVICE pin initialization

• State initialization

22 FT 3120 / FT 3150 Smart Transceiver Data Book

Page 29

Additional Functions

Specified by Application

Specified by Application

Enabled

Pull-Ups

Oscillates

Oscillates at Divide by 2 of CLK1

Stable Address Reflecting Firmware Execution

Stable Data Reflecting Firmware Execution

Scheduler Init

One-Second Timer Init

Checksum Init

Comm Port Init

System RAM Setup

Random Number Seed Calc

Off-Chip RAM

State Init

SERVICE

Stack Init and BIST

Stable R/W Reflecting Firmware Execution

Oscillator Stabilization*

Oscillator Start-Up*

Low

Pin Init

Output

High or Low

E

RESET

IO [10:8, 3:0]

*NOTE: On power up, the oscillator will start running before RESET is released.

IO [7:4]

FT 3150 ONLY

SERVICE

ADDR [15:0]

DATA [7:0]

Reset

R/W

WARNING: NOT TO SCALE

Figure 2.11 RESET Timeline for FT 3120 and FT 3150 Smart Transceivers

• Off-chip RAM initialization

• Random number seed calculation

• System RAM setup

• Communication port initialization

• Checksum initialization

FT 3120 / FT 3150 Smart Transceiver Data Book 23

Page 30

Chapter 2 - Hardware Resources

• One-second timer initialization

• Scheduler initialization

During internal oscillator start up (after power up), the FT Smart Transceiver waits for the oscillator signal amplitude

to grow before using the oscillator waveform as the system clock. This period depends on the type of oscillator used

and its frequency, and begins as soon as power is applied to the oscillator and is independent of the RESET

oscillator start-up period may end before or after RESET

is released, depending on the duration of reset and the time

required by the oscillator to start up.

After the oscillator has started up, the FT Smart Transceiver counts additional transitions on CLK1 to allow the

frequency of the oscillator to stabilize. From the time RESET

period, the I/O pins are in a high-impedance state. The E

is asserted until the end of the oscillator stabilization

signal goes inactive (high) immediately after reset goes low,

and the address bus becomes high (0xFFFF) to deselect external devices.

The stack initialization and BIST task tests the on-chip RAM, the timer/counter logic, and the counter logic. For the

test to pass, all three processors and the ROM must be functioning. A flag is set to indicate whether the FT Smart

Transceiver passed or failed the BIST. The RAM is cleared to all 0s by the end of this step. At the beginning of this

task, the pull-ups on IO[7:4] are enabled, so that a weak high state can be observed on these pins. The SERVICE

oscillates between a solid low and a weak high. The memory interface signals reflect execution of these tasks.

If the RAM self-test fails, the device goes offline, the service LED comes on solid, and an error is logged in the status

structure of the device.

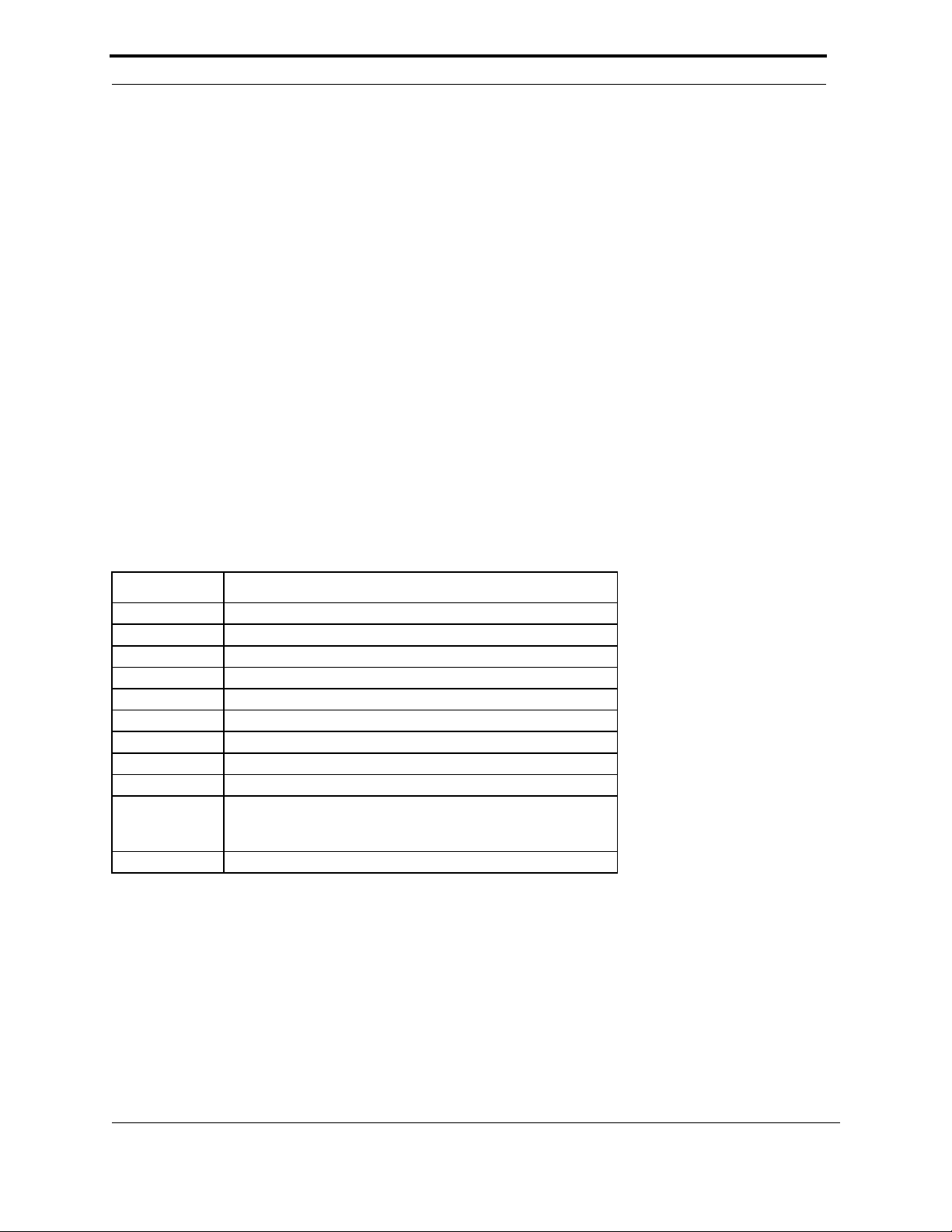

Self-test results are available in the first byte of RAM (0xE800) as follows:

pin. The

pin

Va lu e Description

0 No Failure

1 RAM failure

2 Timer/counter failure

3 Counter failure

4 Configured input clock rate exceeds the chip maximum

The SERVICE

pin initialization task turns off the SERVICE pin (high state).

The state initialization task determines if a FT Smart Transceiver boot is required (FT 3150 Smart Transceiver only),

and performs the boot if it is required. The FT Smart Transceiver decides to perform a boot if it is blank, or if the boot

ID does not match the boot ID in ROM.

The off-chip RAM initialization task checks the memory map to determine if any off-chip RAM is present and then

either tests and clears all of the off-chip RAM or, optionally, clears the application RAM area only. This choice is

controlled by the application program via a Neuron C compiler directive. This task applies only to the FT 3150 Smart

Transceiver.

The random number seed calculation task creates a seed for the random number generator.

The system RAM setup task sets up internal system pointers as well as the linked lists of system buffers.

The checksum initialization task generates or checks the checksums of the nonvolatile writable memories. If the boot

process was executed for the configured or unconfigured states, in the state initialization task, then the checksums are

generated; otherwise, they are checked. This process includes on-chip EEPROM, off-chip EEPROM, flash, and offchip nonvolatile RAM. There are two checksums, one for the configuration image and one for the application image.

In each case, the checksum is a negated two’s complement sum of the values in the image.

The one-second timer initialization task initializes the one-second timer. At this point, the network processor is

available to accept incoming packets.

The scheduler initialization task allows the application processor to perform application-related initialization as

follows:

24 FT 3120 / FT 3150 Smart Transceiver Data Book

Page 31

Additional Functions

• State w ait — wait for the device to leave the applicationless state.

• Pointer initialization — perform a global pointer initialization.

• Initialization step — execute initialization task, which is created by the compiler/linker to handle initializa-

tion of static variables and the timer/counters.

• I/O pin initialization step — initialize I/O pins based on application definition. Prior to this point, I/O pins

are high impedance.

• State w ait I I — wait for the device to leave the unconfigured or hard-offline state. If waiting was required, a

flag is set to indicate that the device should come up offline.

• Parallel I/O synchronization — devices using parallel I/O attempt to execute the master/slave synchroni-

zation protocol at this point.

• Reset task — execute the application reset task (when (reset{})).

If the offline flag was set, go offline and execute the offline task. If the BIST flag indicated a failure, then the

SERVICE

loop.

The amount of time required to perform these steps depends on many factors, including: FT Smart Transceiver

model; input clock rate; whether or not the device performs a boot process; whether the device is applicationless,

configured, or unconfigured; amount of off-chip RAM; whether the off-chip RAM is tested or simply cleared; the

number of buffers allocated; and application initialization. Table 2.8 and Table 2.9 summarize the number of input

clock cycles (CLK1) required for each of these steps for the FT 3120 and the FT 3150 Smart Transceivers. The times

are approximate and are given as functions of the most significant application variables.

pin is turned on and the offline task is executed. Otherwise, the scheduler starts its normal task scheduling

Table 2.8 FT 3120 Smart Transceiver Reset Sequence Time

Step Number of CLK1 Cycles Notes

Stack Initialization and BIST 386,000

SERVICE Pin Initialization 1000

State Initialization 250 (for no boot)

2,275,000 (for boot)

Off-Chip RAM Initialization 0

Random Number Seed Calculation 0 1

System RAM Set-up 21,000 + 600*B 2

Communication Port Initialization 0 1

Checksum Initialization 3400 + 175*M 3

One-Second Timer Initialization 6100

Scheduler Initialization ≥ 7400 4

Notes:

Note 1) These tasks run in parallel with other tasks.

Note 2) B is the number of application and/or network buffers allocated.

Note 3) M is the number of bytes to be checksummed.

Note 4) Assumes a trivial initialization task, no reset task and the configured state.

For example, the timing of each of these steps is shown for a FT 3120 Smart Transceiver application with the

following parameters: 10MHz input clock, crystal oscillator, no boot required, at least 10 application and/or network

buffers, and 500 bytes of EEPROM checksummed.

Stack Initialization and BIST 38.6 ms

SERVICE

Pin Initialization 0.1 ms

State Initialization 0.025 ms

Off-Chip RAM Initialization 0 ms

Random Number Seed Calculation 0 ms

FT 3120 / FT 3150 Smart Transceiver Data Book 25

Page 32

Chapter 2 - Hardware Resources

System RAM Setup 2.7 ms

Communication Port Initialization 0 ms

Checksum Initialization 10.8 ms

One-Second Timer Initialization 0.61 ms

Scheduler Initialization 0.74 ms

Total 53.7 ms

Table 2.9 FT 3150 Smart Transceiver Reset Sequence Time

Step Number of CLK1 Cycles Notes

Stack Initialization and BIST 425,000

SERVICE Pin Initialization 1000

State Initialization 1300 (for no boot)

70,000 + 25 ms*E (for boot)

Off-Chip RAM Initialization 24,000 + 214*R (for test and clear)

24,000 + 152*R

Random Number Seed Calculation 50,000 max

System RAM Setup 27,000 + 1500*B 4

Communication Port Initialization 0 5

Checksum Initialization 7200 + 175*M (for no boot)