DYNEX MAS17503LL, MAS17503LD, MAS17503LC, MAS17503LB, MAS17503FS Datasheet

...

MA17503

1/34

The MA17503 Interrupt Unit is a component of the MAS281

chip set. Other chips in the set include MA17501 Execution Unit

and the MA17502 Control Unit. Also available is the peripheral

MA31751 Memory Management/Block Protection Unit. The

lnterrupt Unit, in conjunction with these additional chips,

implements the full MIL-STD-1750A Instruction Set

Architecture.

The MA17503 - consisting of the Pending Interrupt

Register, Mask Register, Interrupt Priority Encoder, Fault

Register, Timer A, Timer B, Trigger-Go Counter, Bus Fault

Timer, and DMA interface - handles all interrupt fault, and DMA

interfacing, in addition to providing all three hardware timers.

The Interrupt Unit also implements 26 of the MIL-STD-1750A

specified l/O commands. Table 1 provides brief signal

definitions.

The MA17503 is offered in dual-in-line, flatpack or leadless

chip carrier packaging. Screening and packaging options are

described at the end of this document.

FEATURES

■ Mil-Std-1750A Instruction Set Architecture

■ Full Performance over Military Temperature Range (-55°C

to +125°C)

■ Radiation Hard CMOS/SOS Technology

■ Interrupt Handler

• 9 User Interrupt Inputs

• Pending Interrupt Register

• Interrupt Mask Register

• Interrupt Priority Encoder

■ Fault Handler

• 8 User Faults Inputs

• Fault Register

■ Timers

• Timer A

• Timer B

■ Trigger-Go

■ DMA Interface

■ Interface Discretes

• Normal Power-Up

• Start-Up ROM Enable

• Configuration Word Enable

■ Implements 26 MIL-STD-1750A Specified l/O Commands

■ MAS281 Integrated Built-ln Self Test

■ TTL Compatible System Interface

BLOCK DIAGRAM

MA17503

Radiation Hard MIL-STD-1750A Interrupt Unit

Replaces June 1999 version, DS3566-4.0 DS3566-5.0 January 2000

MA17503

2/34

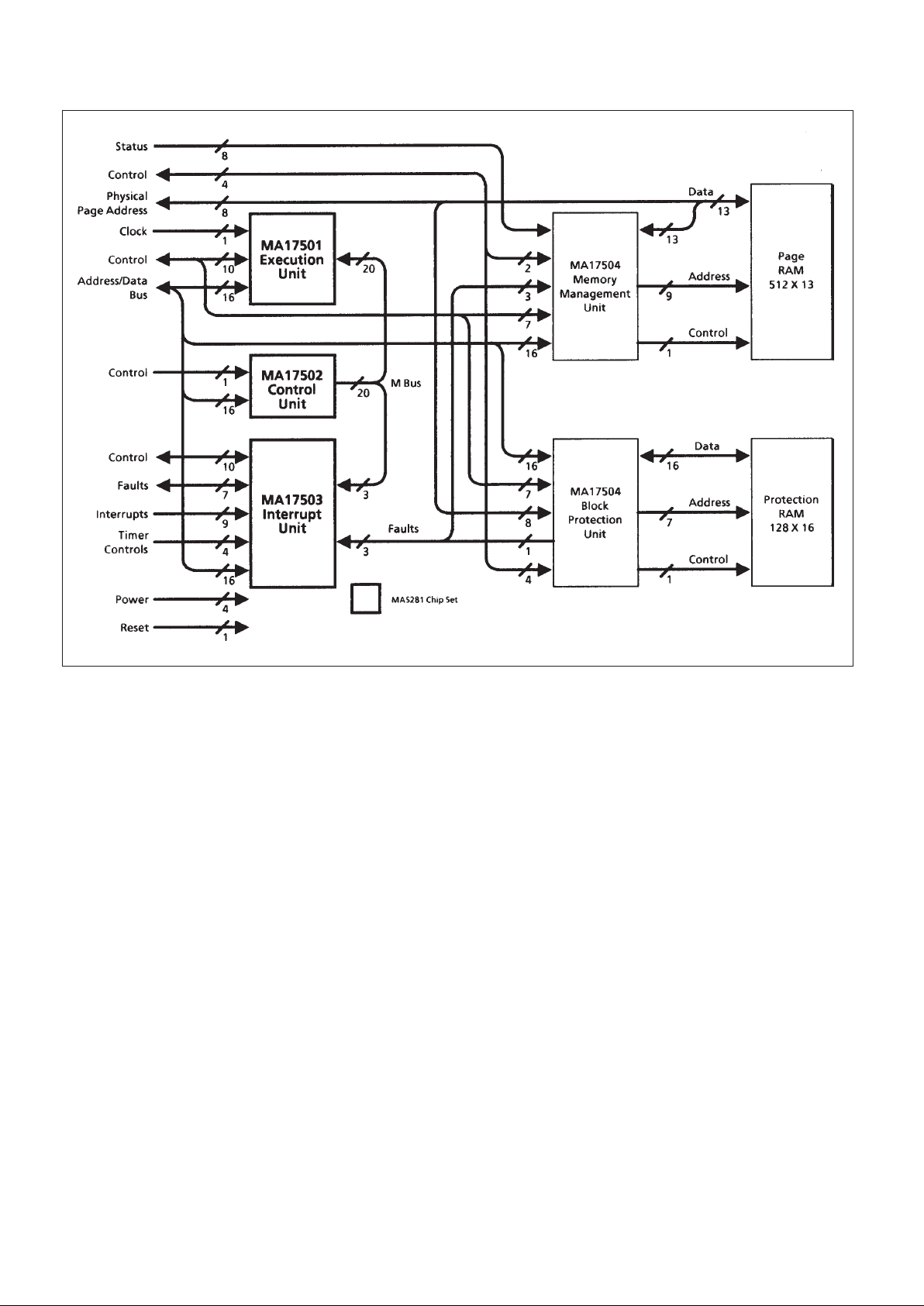

1.0 SYSTEM CONSIDERATIONS

The MA17503 Interrupt Unit (IU) is a component of the GPS

MAS281 chip set. This chip set implements the full MIL-STD1750A instruction set architecture. Other chips in the set

include the MA17501 Execution Unit (EU) and MA17502

Control Unit (CU). Also available is the peripheral MA31751

Memory Management Unit/Block Protection Unit (MMU(BPU)).

Figure 1 depicts the relationship between the chip set

components.

The IU provides the interrupt and fault handling interfaces

for the chip set. The IU also provides the DMA control interface

logic, contains interval Timers A and B, the Trigger-Go

Counter, the Bus Fault Timeout timer, and decodes all MILSTD-1750A specified l/O commands in support of these

functions. The EU provides the arithmetic and logical

computation resources for the chip set. The EU and IU are each

controlled by microcode from the CU. The MMU(BPU) may be

configured to provide either 1M-word memory management

(MMU) and/or 1K-word memory block write protection (BPU)

functions.

As shown in Figure 1, the MAS281 is the minimum

processor configuration consisting of an Execution Unit, a

Control Unit, and an Interrupt Unit. This configuration is

capable of accessing a 64K-word address space. Addition of a

MMU configured MA31751 allows access to a 1M-word

address space. Addition of a BPU configured MA31751

provides hardware support for 1K-word memory block write

protection.

The IU, as with all components of the MAS281 chip set, is

fabricated with CMOS/SOS process technology.

Detailed descriptions of the lUs companion chips are

provided in separate data sheets. Additional discussions on

chip set system considerations, interconnection details, and

Digital Avionics Instruction Set (DAIS) mix benchmarking

analysis are provided in separate application notes.

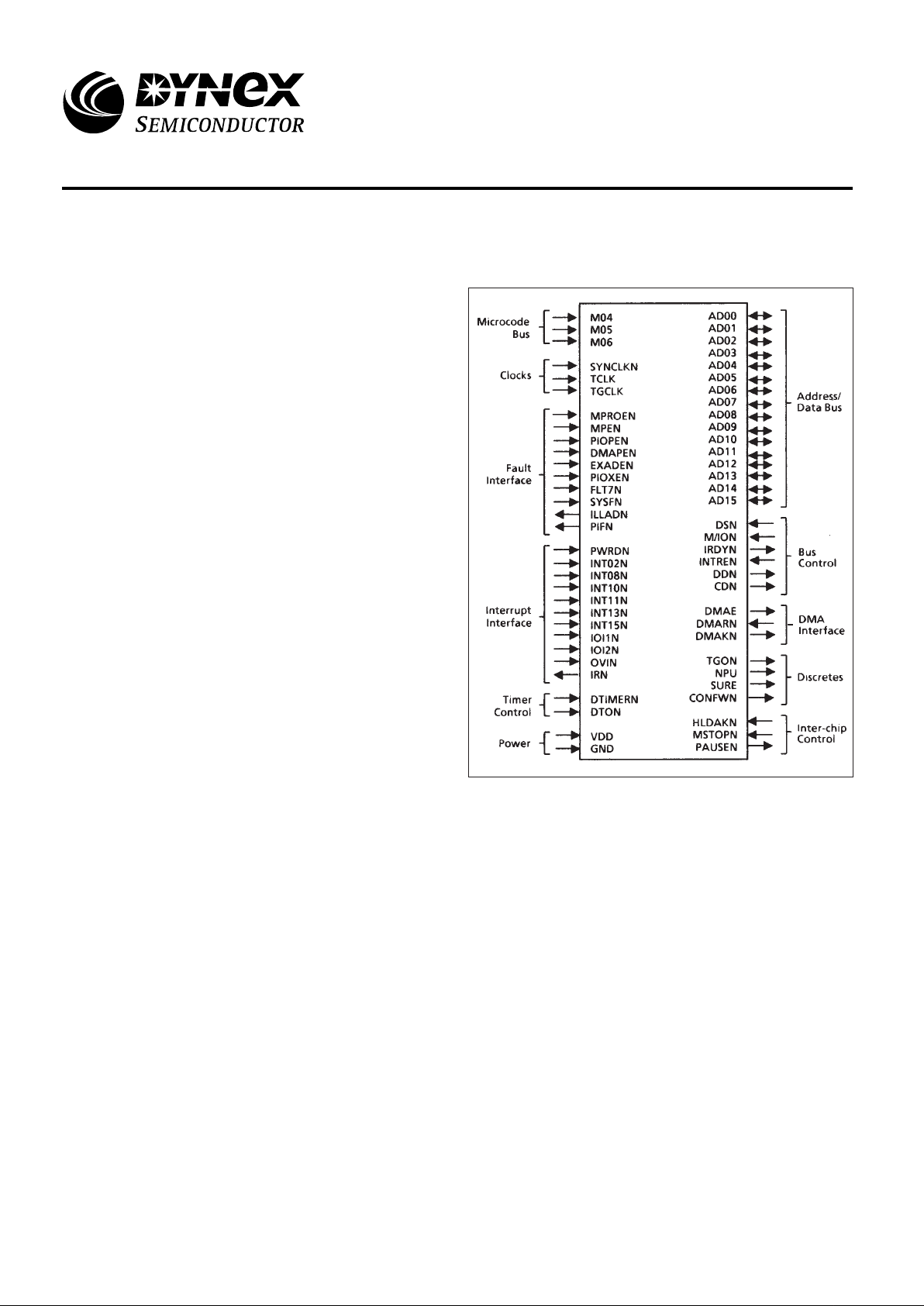

SIGNAL I/O DEFINITION

AD00 - AD15 I/O/Z 16-Bit Address/Data Bus

M04, M05, M06 I 3 Bits of the Mlcrocode Instruction

Word

INTREN I Interrupt Unit Microcode Interface

Enable

DMAKN O DMA Request Acknowledge

DMAE O DMA Interface Enable

DMARN I DMA Request

M/ION I Memory/lnput-Output

DSN I Data Strobe

SYNCLKN I Synchronisation Clock

IRDYN O Interrupt Unit Ready

DDN O Data Transceiver Dlrection Control

CDN O Control Bus Transceiver Direction

Control

SYSFN I System Fault

FLT7N I Fault 7 (Undefined Fault)

PIOXEN I Programmed I/O Transfer Error

EXADEN I External Address Error

DMAPEN I DMA Parity Error

PIOPEN I Programmed I/O Parity Lrror

MPEN I Memory Parity Error

MPROEN I Memory Protection Error

ILLADN O Illegal Address

PIFN O Instruction Abort

PWRDN I Power-Down Interrupt

INT02N I Level 2 Interrupt

INT08N I Level 8 Interrupt

INT10N I Level 10 Interru pt

INT11N I Level 11 Interrupt

IOI1N I I/O Register Interrupt 1

INT13N I Level 13 Interrupt

IOI2N I I/O Register Interrupt 2

INT15N I Level 15 Interrupt

OV1N I Fixed-Point Overflow Interrupt

IRN O Interrupt Request

TCLK I Clock for Tlmers A and B

TGCLK I Trigger Go Timer Clock

DTIMERN I Disable Timers

DTON I Disable Bus-Fault Timeout

TGON O Trigger-Go Timer Overflow

NPlJ O Normal Power-up Indicator

SURE O Start-up ROM Enable

CONFWN O Configuration Word Enable

HLDAKN I Hold Acknowledge

MSTOPN I Microcode Stop

PAUSE O Processor Pause

VDD I Power

GND I Ground

Table 1: Signal Definitions

MA17503

3/34

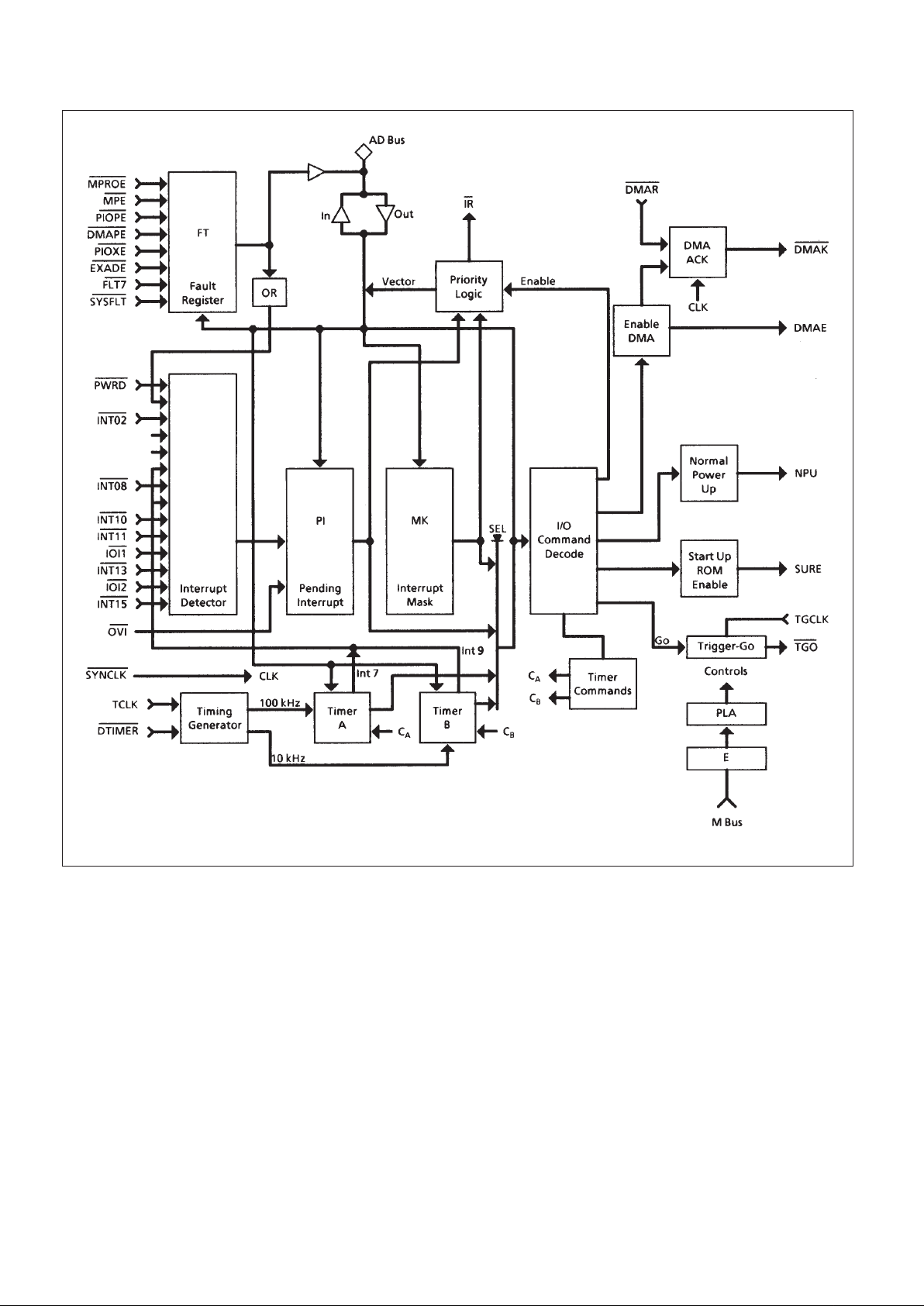

2.0 ARCHITECTURE

The Interrupt Unit consists of a Pending Interrupt Register,

Mask Register, Interrupt Priority Encoder, Fault Register, two

interval timers, two watchdog timers, DMA Control interface,

and both microcode and internal I/O instruction decode logic.

Details of these components are depicted in Figure 2 and are

discussed below:

2.1 PENDING INTERRUPT REGISTER

The Pending Interrupt Register (Pl) is the dedicated 16-bit

register that latches all pending interrupt requests and stores

them until serviced. The inputs to the Pl are buffered by fallingedge detectors to prevent repeat latching of interrupt requests

held low longer than required. The Pl supports nine external

interrupts inputs and seven chip set generated interrupts. The

output of the Pl is ANDed with the Mask Register to create the

interrupt request (IRN) signal for the MA17502 Control Unit. A

one in a Pl bit position indicates an interrupt is pending and the

interrupt level is equal to the bit position.

2.2 MASK REGISTER

The Mask Register (MK) is the dedicated 16-bit register

containing the information that filters the Pl output to the Priority

Encoder and the IRN generation logic. A one in a MK bit

position allows the interrupt request, of the same bit position in

the Pl, to enter the Priority Encoder and cause IRN to drop low.

Pl bits 1 - 4 and 6 - 15 are maskable.

2.3 INTERRUPT PRIORITY ENCODER

The Interrupt Priority Encoder accepts the enabled, mask

filtered, output of the Pl and generates a four bit code

designating the level of the highest priority pending interrupt.

Level zero (Pl bit zero) has the highest priority and level 15 (Pl

bit 15) the lowest. The four bit priority code is placed on the AD

Bus during the microcoded interrupt handling routine.

2.4 FAULT REGISTER

The Fault Register (FT) is the dedicated 16-bit register that

latches the 15 specified (fault 12 is reserved) faults. The FT

supports eight external Fault inputs and three chip-set

generated Faults. The output of the FT is ORed together,

buffered by a falling-edge detector, and input to the Pl to

generate the level one interrupt. FT bits 13 - 15 are used to

indicate the results of the MAS281 BlT. Once the FT has

latched a fault, it can only be cleared via internal l/O command

(individual fault bits cannot be cleared).

Figure 1

MA17503

4/34

Figure 2: MA17503 Interrupt Unit Architecture

MA17503

5/34

Anti-repeat logic between the FT and Pl prevents latching

more than a single interrupt into the Pl before the user interrupt

service routine has cleared the FT. The microcoded interrupt

service routine reads the interrupt priority vector from the

Interrupt Unit and clears the serviced interrupt from the Pl. At

this point the Pl is ready to latch another interrupt into this bit.

When this microcoded service routine acts on a level 1

interrupt, it clears the Pl bit 1, but the FT maintains the

interrupting fault bit(s). Therefore, a level 1 interrupt would be

latched again if there were no anti-repeat logic to prevent a

never ending loop of interrupts from occurring.

Interrupts are serviced at the end of the currently executing

instruction if not masked and if interrupts are enabled. System

software servicing level 1 interrupts must clear the FT via the

RCFR internal l/O command at some point in the routine to

allow subsequent faults to latch a level 1 interrupt request. A

non-destructive read of the FT is provided by the internal I/O

command RFR, but this command should be used carefully.

2.5 INTERVAL TIMERS

The Interrupt Unit contains both MIL-STD-1750A 16-bit

interval timers, A and B. The TCLK input is synchronized with

SYNCLKN and increments Timer A once a TCLK period. Timer

B is incremented by the synchronized TCLK divided by 10.

Timer A overflow sets Pl bit 7 and Timer B overflow sets Pl bit 9.

The timers are controlled via the l/O command decode logic, or

they can be disabled via the DTlMERN input.

2.6 WATCHDOG TIMERS

The Interrupt Unit contains two watchdog timers, TriggerGo and Bus Fault. The Bus Fault timer assures timely

completion of all AD Bus cycles by terminating bus cycles over

two TCLK (maximum, minimum one TCLK period) periods in

duration. This function is automatic, but can be disabled by

DTON low. FT bit 5 or 8 is set for terminated l/O transfers or

memory transfers, respectively, when the Bus Fault timer

expires.

The Trigger-Go timer is an autonomous 16-bit ripple

counter incremented by TGCLK. Upon power-up, the TriggerGo timer begins to count. The GO l/O command resets the

timer, thus preventing it from overflowing and causing TGON to

drop low. The DTIMERN input prevents the Trigger-Go timer

from incrementing.

2.7 DMA CONTROL INTERFACE

The DMA control interface logic is contained in the Interrupt

Unit. The interface is composed of the three signals: DMAE,

DMARN, and DMAKN. If the interface is enabled, an internal

l/O command raises DMAE high to indicate the MAS281’s

readiness to accept DMA transfer requests (DMARN low). A

subsequent low on DMARN causes the lU to respond with

DMAKN low. DMAKN low halts the processor and places all AD

Bus and bus control lines in the high-impedance state. Control

is returned to the MAS281 when DMARN is pulled high again.

DTIMERN is the user available way to disable the DMA

interface.

2.8 INTERNAL I/O COMMAND DECODE LOGIC

The Interrupt Unit implements the 26 MIL-STD-1750A

specified l/O command functions listed in Table 2. The lU also

decodes an additional 386 commands that are implemented in

the MMU(BPU) and the two Status Word XlO commands that

are handled in microcode for AD Bus control. The lU continually

monitors AD Bus traffic. When M/lON is low, the lU latches the

information present on the AD Bus during the address portion

of the bus cycle. This information is subsequently decoded and

creates the appropriate control signals to perform the l/O

command function.

2.9 MICROCODE DECODE LOGIC

The microcode decode logic can be split into command and

control functions. Microcode instruction bits 4, 5 and 6 are

decoded as commands for the FT, the interrupt interface, the

DMA interface, and the discrete output signal, NPU. The

microcode command interface is enabled when lNTREN is

pulled low and is disabled during DMA and the Hold state.

Microcode bits 5 and 6 provide control of DDN during memory

read and write cycles, and external l/O cycles.

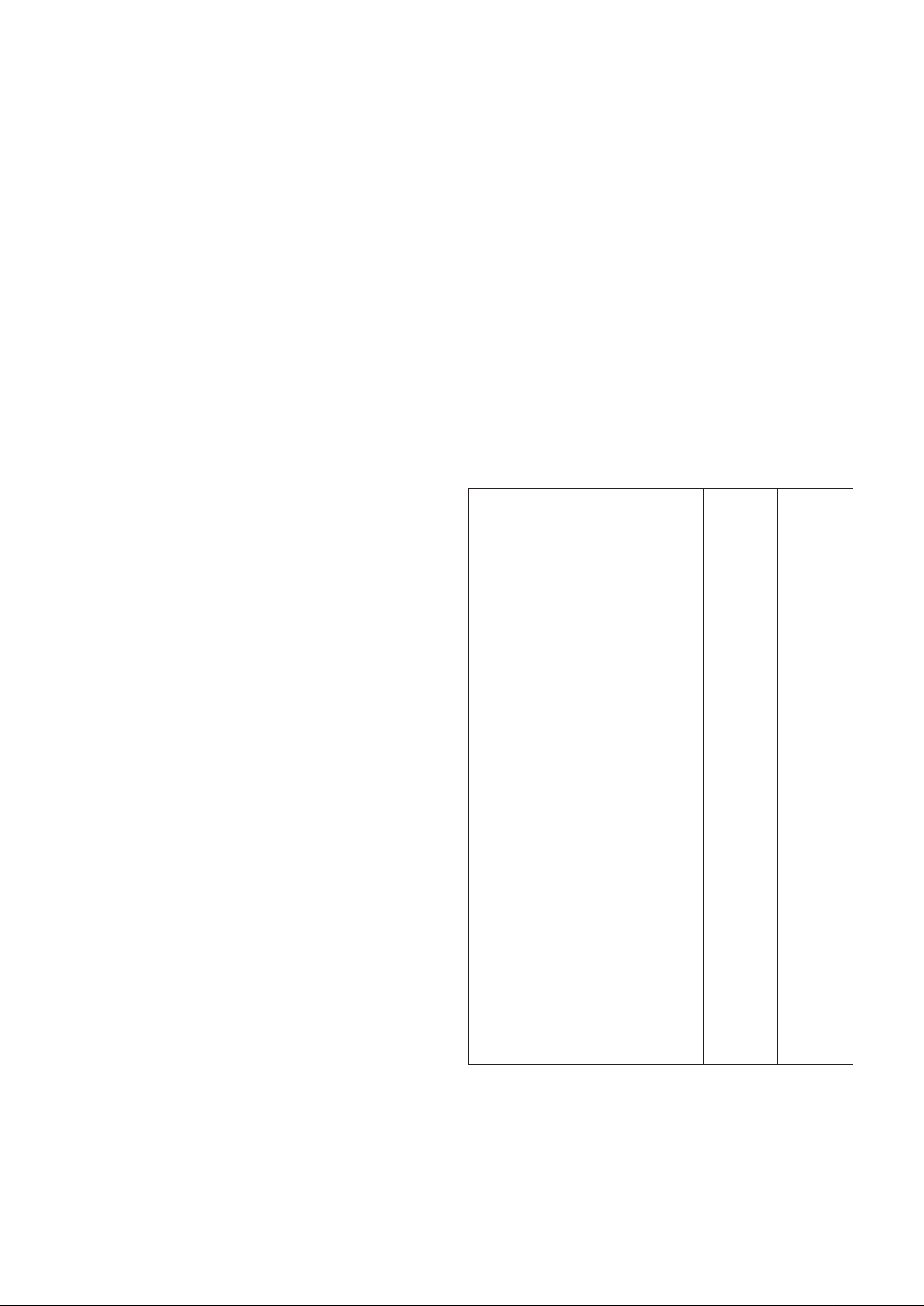

Operation Command Mnemonic

Code (Hex)

Output

Set Fault Register 0401 SFR

Set Interrupt Mask 2000 SMK

Clear Interrupt Request 2001 CLIR

Enable Interrupts 2002 ENBL

Dlsable Interrupts 2003 DSBL

Reset Pending Interrupt 2004 RPI

Set Pending Interrupt Reglster 2005 SPI

Reset Normal Power Up Discrete 200A RNS

Write Status Word 200E WSW

Enable Start Up ROM 4004 ESUR

Disable Start up ROM 4005 DSUR

Direct Memory Access Enable 4006 DMAE

Direct Memory Access Disable 4007 DMAD

Timer A Start 4008 TAS

Timer A Halt 4009 TAH

Output Timer A 400A OTA

Reset Tngger-Go 400B GO

Timer B Start 400C TBS

Timer B Halt 400D TBH

Output Timer B 400E OTB

Input

Read Configuration Word 8400 RCW

Read Fault Register Wlthout Clear 8401 RFR

Read Interrupt Mask A000 RMK

Read Pending Interrupt Reglster A004 RPIR

Read Status Word A00E RSW

Read and Clear Fault Reylster A00F RCFR

Input Timer A C00A ITA

Input Tlmer B C00E ITB

MA17503

6/34

3.0 INTERFACE SIGNALS

All signals comply with the voltage levels of Table 1. In

addition, each of these functions is provided with Electrostatic

Discharge (ESD) protection diodes. All unused inputs must be

held to their inactive state via a connection to VDD or GND.

Throughout this data sheet, active low signals are denoted

by either a bar over the signal name or by following the name

with an “N’’ suffix (e.g., DMAKN). Referenced signals that are

not found on the MA17503 are preceded by the originating

chip’s functional acronym in parentheses (e.g., (EU)OSC).

Following is a description of each pin function grouped

according to functional interface. The function name is

presented first, followed by its acronym, its type, and its

description. Function type is either input, output, high

impedance (Hi-z), or a combination thereof. Timing

characteristics of each of the functions described is provided in

Section 5.0.

3.1 POWER LNTERFACE

The power interface consists of one 5V VDD connection

and one GND connection.

3.2 CLOCKS

The clock interface, discussed below, provides

synchronization for lnterrupt Unit operations and the clock

inputs for the interval and watchdog timers.

3.2.1 Synchronisation Clock (SYNCLKN)

Input. The MA17501 Execution Unit (EU) generates the

SYNCLKN signal for the Interrupt Unit. The Interrupt Unit uses

this signal to synchronise system inputs (e.g., interrupts and

faults) to the MAS281 machine cycle and to control all other

internal functions.

3.2.2 Timer Clock (TCLK)

Input. TCLK is a 100 KHz, user provided clock signal that

drives the interval timers A and B, and the Bus Fault timer.

TCLK is synchronised to the MAS281 machine cycle, via

SYNCLKN, before being sent to the interval timers. This allows

the lU to implement the Internal l/O Commands associated with

timer operation.

The synchronised version of TCLK drives interval timer A,

clocking it once every 10 microseconds. The synchronised

TCLK is divided by 10 to provide a 10 KHz clock for driving

interval timer B, clocking it once every 100 microseconds.

The unsynchronised TCLK is used to increment the Bus

Fault watchdog timer. When DSN drops low, the Bus Fault

timer is enabled to count and expires after two TCLK high-tolow transitions.

3.2.3 Trigger-Go Clock (TGCLK)

Input. This user provided clock drives the autonomous onchip system watchdog timer. The Trigger-Go timer is

incremented by the high-to-low transition of TGCLK.

3.3 BUSES

Following is a discussion of the two communication buses

connecting the lnterrupt Unit to the rest of the three chip set.

The AD Bus transfers 16-bit data and commands, while the M

Bus communicates microcode control data.

3.3.1 Address/Data Bus (AD Bus)

Input/Output/Hi-z. These signals comprise the multiplexed

address and data bus. During internal bus operations, the AD

Bus accommodates the transfer of Internal I/O commands and

data from the MA17501 Execution Unit to the lnterrupt Unit. lt

also accommodates the transfer of data from the lnterrupt Unit

to the Execution Unit in response to internal I/O commands.

AD00 is the most significant bit position and AD15 is the least

significant bit position of both the 16-bit data and 16-bit

command. A high on this bus corresponds to a logic 1 and a low

corresponds to a logic 0.

Commands on the AD Bus are passed through transparent

latches during the low state of input/output SYNCLKN cycles

and are latched at the low-to-high transition of SYNCLKN. Data

on the AD Bus, is either clocked into the lU by the high-to-low

transition of SYNCLKN or placed there by the lU during the low

portion of SYNCLKN.

3.3.2 Microcode Bus Bits 4, 5 and 6 (M04, 05 & 06)

Inputs. M04, M05, M06 are bits 4, 5 and 6 of the 20-bit

Microcode Bus and are coded in the 40-bit microcode

instruction as bits 4, 5 and 6. These bits are latched into the IU

at the SYNCLKN high-to-low transition and are decoded for

commanding the Fault Register, the DMA interface, the NPU

discrete, and for providing the 4-bit priority encoded interrupt

vector to the EU. lU microcode command cycles are extended

to six (EU)OSC cycles by INTREN low. Microcode bits 5 and 6

provide control of DDN during memory and external I/O cycles.

The microcode bus is not latched during DMA or the Hold state

(DMAKN or HLDAKN low).

3.4 BUS CONTROL

The following is a discussion of the signals used to control

the AD Bus and M Bus. They enable the respective busses at

the proper time and control system access to the MAS281

System AD Bus.

3.4.1 Data Strobe (DSN)

Input. The Interrupt Unit receives DSN from the Execution

Unit. The DSN high-to-low transition starts the Bus Fault

watchdog timer and during successful bus data transfers, the

low-to-high transition halts and resets the Bus Fault watchdog

timer. DSN is also instrumental in controlling the DDN signal

during MAS281 Read/lnput bus cycles.

3.4.2 Memory/lnput-Output (M/ION)

Input. The Interrupt Unit receives M/ION from the Execution

Unit. M/ION low enables l/O command decoding logic M/ION

also selects the FT bit to set in response to a low on MPROEN

and EXADEN.

3.4.3 Interrupt Unit Ready (IRDYN)

Output. The Interrupt Unit uses the IRDYN signal to cause

the Execution Unit clock generation state machine to inject one

wait state into lnternal I/O machine cycles, thus causing the

minimum five (EU)OSC period machine cycle to be extended to

a six (EU)OSC period 50% duty cycle machine cycle. Internal

l/O machine cycles occur during execution of the lU

implemented l/O commands listed in Table 2.

MA17503

7/34

3.4.4 Interrupt Unit Microcode Enable (INTREN)

lnput. The Execution Unit provides lNTREN to the lnterrupt

Unit to enable the microcode command interface. When

INTREN is low, microcode instruction bits 4, 5 and 6 (latched

into the lU microcode register at the SYNCLKN high-to-low

transition, if HLDAKN and DMAKN are high) are decoded by

the lU as commands for the FT, NPU discrete, internal DMA

interface, and interrupt vectoring. lNTREN low causes the EU

to extend the machine cycle to six (EU)OSC periods.

3.4.5 Data Transceiver Direction (DDN)

Output. DDN is provided to control the directionality of the

AD/Data Bus transceivers. DDN is high during data transfers

from the MAS281 to the user system and when it is necessary

to keep the transceivers from driving the MAS281 System AD

Bus. DDN is low during transfers from the user system to the

MAS281.

Cycles during which DDN is high include: memory writes,

outputs, IU implemented Internal l/O command execution

(except Read Configuration Word (RCW)), and all MA17504

MMU(BPU) implemented l/O command execution.

Cycles during which DDN is low include: memory reads

(data portion), inputs (data portion), the Configuration Word

read (identified by CONFWN, low), and during DMA and Hold

cycles (to allow access to the MMU(BPU).

3.4.6 Control Transceiver Direction (CDN)

Output. CDN is provided to control the directionality of the

Control Bus (consists of DSN, (EU)AS, M/lON, RD/WN, and

IN/OPN) transceivers. CDN is high during all MAS281 directed

machine cycles. CDN drops low only when DMAKN or

HLDAKN is low, indicating the MAS281 has placed the control

bus signals in the high-impedance state. (It is necessary to use

transceivers to buffer the control bus, if a shared MMU(BPU)

architecture is used, to allow the sharing device access to the

MMU(BPU) functions.)

3.5 INTERRUPT INTERFACE

The Interrupt Unit supports 16 levels of prioritised

interrupts, nine of which are accessible to the user system. All

user accessible interrupts are active low, are buffered with

edge detectors to prevent repeat latching of the interrupt, and

are latched into the Pending Interrupt register (Pl) by the highto-low transition of SYNCLKN.

The following interrupts do not have dedicated input pins on

the MA17503. Level 1, Machine Error lnterrupt, is driven by the

ORed bits of the Fault register (FT). Levels 7 and 9 are driven

by the overflow of Interval Timers A and B, respectively. The

Internal I/O command, Set Pending Interrupt (SPI), is used to

set interrupt levels 3, 5, and 6 (Floating-Point Overflow,

Executive Call, and Floating-Point Underflow, respectively) via

microcoded execution.

3.5.1 Power Down Interrupt (PWRDN)

Input. The PWRDN interrupt is the highest priority interrupt,

level 0, and is latched into Pl bit zero. It is nonmaskable and

cannot be disabled.

3.5.2 User Interrupts (INT02N,08N,10N,11N,13N & 15N)

lnputs. Each of these user definable interrupts is latched

into the Pl register bits 2, 8, 10, 11, 13, or 15, respectively.

Level 2 is the highest priority and level 15 is the lowest. These

interrupts are maskable and can be disabled.

3.5.3 I/O Registered Interrupts (1011N & 1012N)

Inputs. Each of these interrupts is latched into the Pl

register bits 12 and 14, respectively. Level 12 is higher than

level 14. These interrupts are maskable and can be disabled.

3.5.4 Fixed-Point Overflow (OVIN)

Input. This interrupt is driven by the MA17501 Execution

Unit and is latched into the Pl register bit 4. The OVlN interrupt

is maskable and can be disabled.

3.5.5 Interrupt Request (IRN)

Output. This signal is the logical inclusive OR of the Pl bits

and is used to signal the MA17502 Control Unit that an interrupt

request is pending.

3.6 FAULT INTERFACE

The Interrupt Unit supports 16 registered error condition

flags. Eleven of the faults are directly accessible through

dedicated input pins. A low on any of these fault inputs is

latched into the Fault register (FT) by the high-to-low transition

of SYNCLKN. Once a fault is latched, it can only be cleared by

clearing the entire FT via lnternal l/O command. The latching of

any fault causes the level 1 interrupt to be set. Once set and

subsequently cleared by the microcoded interrupt service

routine, Pl bit one cannot be set again until the FT is cleared via

internal I/O command. Any unused fault inputs must be pulledup to VDD.

3.6.1 Memory Protection Error (MPROEN)

lnput. A low on this input is used to inform the MAS281 that

an access fault, execute or write protection violation has been

detected. When the MA31751 MMU(BPU) is used with the

MAS281, the MPROEN fault input is provided by the

MMU(BPU). FT bit 0 is set if a MAS281 directed memory cycle

caused the error and bit 1 is set if a DMA device directed

memory cycle caused the error.

Setting FT bit 0 causes PIFN to drop low. This aborts the

MIL-STD-1750A instruction that was executing when the error

occurred and branches execution to the machine error, level 1

interrupt service routine, if the interrupt is not masked. If the

interrupt is masked, execution continues with the next

instruction.

FT bit 0 is not latched during DMA or the Hold state

(DMAKN or HLDAKN low).

3.6.2 Memory Parity Error (MPEN)

lnput. A low on this input indicates a parity error has been

detected during a memory transfer. This fault is latched into FT

bit 2.

3.6.3 Programmed l/O Parity Error (PIOPEN)

lnput. A low on this input indicates a parity error has been

detected during an external l/O transfer. This fault is latched

into FT bit 3.

MA17503

8/34

3.6.4 DMA Parity Error (DMAPEN)

Input. A low on this input indicates a parity error has been

detected during a DMA data transfer. This fault is latched into

FT bit 4.

3.6.5 External Address Error (EXADEN)

Input. A low on this input indicates execution of an

unimplemented or reserved l/O command has been attempted

(M/lON low) and sets FT bit 5, or an attempt has been made to

access an unimplemented memory address (M/lON high) and

sets FT bit 8.

Provision for detection of these conditions has been made

on the MA17503 in the form of a Bus Fault watchdog timer. If

during an l/O or memory access cycle the system machine

cycle completion circuitry or (EU)RDYN generation logic fails to

provide the (EU)RDYN signal within the required amount of

time, the Bus Fault watchdog timer will terminate the cycle by

forcing IRDYN low and set the appropriate FT bit (FT5 if l/O,

FT8 if memory). The minimum Bus Fault watchdog timeout

period is one TCLK period, the maximum is two TCLK periods.

Setting FT bits 5 or 8 causes PIFN to drop low. This aborts

the MIL-5TD-1750A instruction during which the error occurred

and branches execution to the machine error, level 1, interrupt

service routine, if the interrupt is not masked. lf the interrupt is

masked, execution continues with the next instruction.

FT bit 5 and 8 are not latched during DMA or the Hold state

(DMAKN or HLDAKN low).

3.6.6 Programmed l/O Transmission Error (PIOXEN)

Input. A low on this input indicates a user defined error has

occurred during an l/O transfer. This fault is latched into FT bit

6.

3.6.7 Fault #7 (FLT7N)

lnput. This is a user definable (spare) fault input. A low on

this input sets FT bit 7.

3.6.8 System Fault (SYSFN)

Input. A low on this input indicates a system Built-ln Test

error has occurred. This fault is latched into FT bits 13 and 15.

3.6.9 Illegal Address (ILLADN)

FT bits 5 and 8 are set by a low on the EXADEN input or by

the Bus Fault watchdog timer overflow. FT bits 5 and 8 are not

latched, and ILLADN is held high during DMA or the Hold state

(DMAKN or HLDAKN low).

3.6.10 Instruction Abort (PIFN)

Output. A low on this output effects a MlL-STD-1750A

instruction abort. When a SYNCLKN high-to-low transition

latches FT bit 0, 5, or 8, the following SYNCLKN high-to-low

transition causes PIFN to drop low and remain low for one

SYNCLKN period (except during DMA and the Hold state, i.e.,

DMAKN or HLDAKN low).

PIFN directs the MA17502 Control Unit to branch

microcode execution to the interrupt vectoring routine for level

1 interrupt servicing. lf the level 1 interrupt is masked, execution

will resume with the next MIL-STD1750A instruction.

PIFN causes the MA17501 Execution Unit to hold DSN and

(EU)AS in their inactive state during the transition from error

indication to the beginning of the interrupt servicing routine.

3.7 DMA INTERFACE

The DMA lnterface consists of the necessary handshake

signals required to effect transfer of control from the MAS281 to

a DMA controller and back again.

3.7.1 DMA Transfer Enable (DMAE)

Output. When this output is raised high via execution of the

lnternal I/O command DMAE, direct memory access requests

will be acknowledged by the MAS281. lf DMAE is low, direct

memory access requests will not be acknowledged by the

MAS281.

3.7.2 DMA Transfer Request (DMARN)

Input. A DMA controller pulls this input low to request

control of the AD Bus and bus control signals for DMA

transfers. DMARN is held low by the DMA controller for the

duration of the DMA transfer, and the low-to-high transition

indicates the DMA controller is finished using the AD Bus.

3.7.3 DMA Transfer Request Acknowledge (DMAKN)

Output. The lnterrupt Unit responds to a low on DMARN, if

DMAE is high, by dropping DMAKN low at the SYNCLKN highto-low transition.

3.8 INTER-CHIP CONTROL

The Inter-Chip Control signals are used to halt the

processor (the three-chip set) during the DMA and HOLD

cycles and during microcode testing.

3.8.1 Processor Pause (PAUSEN)

Output. This output is low during DMA operations (DMAKN

low). PAUSEN is used by the lnterrupt Unit to reset and disable

the Bus Fault Timeout circuitry. PAUSEN is also used by the

MA17501 Execution Unit clock generation circuitry to produce

an internal disable signal. This internal disable signal holds

CLKPCN and SYSCLK1N low and CLK02N high, which halts

processing, and places the DSN, AS, IN/OPN, RD/WN, and

M/ION output buffers, and the AD bus l/O buffers in the high

impedance state, and drop DDN and CDN low to allow DMA

controller access to the MMU(BPU) in shared MMU(BPU)

systems.

3.8.2 Hold Acknowledge (HLDAKN)

Input. HLDAKN resets and disables the Bus Fault Timeout

circuitry, causes DDN and CDN to be brought low, and

prevents latching of microcode commands and decoding. The

Execution Unit responds to a Hold state request (execution of

BPT, or a low on HOLDN) by pulling HLDAKN low.

3.8.3 Microcode Stop (MSTOPN)

Input. MSTOPN allows microcode to be single-stepped

during testing by GEC Plessey Semiconductors and should be

pulled up to VDD in customer applications.

MA17503

9/34

3.9 TIMER CONTROL

These Timer Control inputs allow external control of Timers

A and B, the Trigger-Go Counter, and the Bus Fault Timeout

circuitry.

3.9 1 Disable Timers (DTIMERN)

Input. A low to this input disables Timers A and B and the

Trigger-Go counter, and also disables DMA access by forcing

DMAE low and DMAKN high. Raising DTIMERN high causes

Timers A and B and the Trigger-Go counter to resume counting

where they were stopped, and also allows normal DMA

operations.

3.9.2 Disable Bus-Fault Timeout (DTON)

Input. A low to this input will reset and disable the Busfault

timeout circuitry.

3.10 DISCRETES

Four discrete outputs are provided for system use, all of

which are enabled or disabled or both via internal l/O

commands.

3.10.1 Trigger-Go Timer Overflow (TGON)

Output. This output drops low whenever the Trigger-Go

counter overflows (rolls over to 0000). lt returns high when the

Trigger-Go counter is reset by software using the GO internal

l/O command.

3.10.2 Normal Power-Up Indicator (NPU)

Output. This output is brought low via internal I/O command

during module initialization as the first step of BlT. lf BIT is

completed successfully, NPU is raised high via microcode, and

remains high until reset by software via the RNS internal I/O

command.

START-UP ROM ENABLE (SURE)

Output. This output is used to enable an externally

implemented Start-Up ROM. SURE is brought high via the

execution of the ESUR internal l/O command (done by

microcode during initialization or by software), and remains

high until it is reset by software by using the DSUR internal l/O

command. While SURE is high, all memory reads shall access

main memory. This feature is utilized via the MOV instruction to

effect a non-volatile memory program transfer to faster

program execution RAM.

CONFIGURATION WORD ENABLE (CONFWN)

Output. This output is brought low during the data portion of

an RCW (Read Configuration Word) internal l/O operation. lt is

used as an output enable strobe for the externally implemented

Configuration Register. Because RCW is an internal I/O

command, the read cycle is a fixed six (EU)OSC cycles and is

terminated by IRDYN low. RDYN must not be asserted during

execution of this command.

4.0 OPERATING MODES

The following discussions detail the MAS281 chip set

operating modes from the perspective of the Interrupt Unit. The

MAS281 operating modes involving the MA17503 are: (1)

initialization, (2) instruction execution, (3) interrupt servicing,

(4) fault servicing, (5) DMA support, (6) Hold support, and (7)

timer operations.

4.1 INITIALISATION

A microcoded initialisation sequence is executed by the

chip set in response to a hardware reset. This routine, as

applicable to the lnterrupt Unit, disables and masks interrupts,

zeroes the Fault register, performs the MAS281 Integrated

Built-ln Test (BIT), raises the Start-Up ROM enable discrete

(SURE), clears and starts timers A and B, resets the Trigger-Go

counter, and disables DMA access. The resulting initialised

state of the MA17503 is listed in Table 3.

The microcoded BIT exercises all legal microinstruction bit

combinations and tests all internally accessible structures of

the MAS281 chip set. For the Interrupt Unit this includes the

MK, Pl, and FT registers, Interrupt Enable/Disable, and Timers

A and B. Table 4 details the tests performed by each of the five

BlT routines.

If any part of BIT fails, an error code identifying the failed

subroutine is loaded into FT bits 13-15, BlT is aborted with NPU

left in the low state, initialization is completed, and instruction

execution begins at address zero. The coding of the BIT results

is shown in Table 4.

NOTE: To complete initialization and pass BIT, interrupt

and fault inputs must be high for the duration of the initialization

routine. ln addition, timers A and B must be clocked for BlT

success.

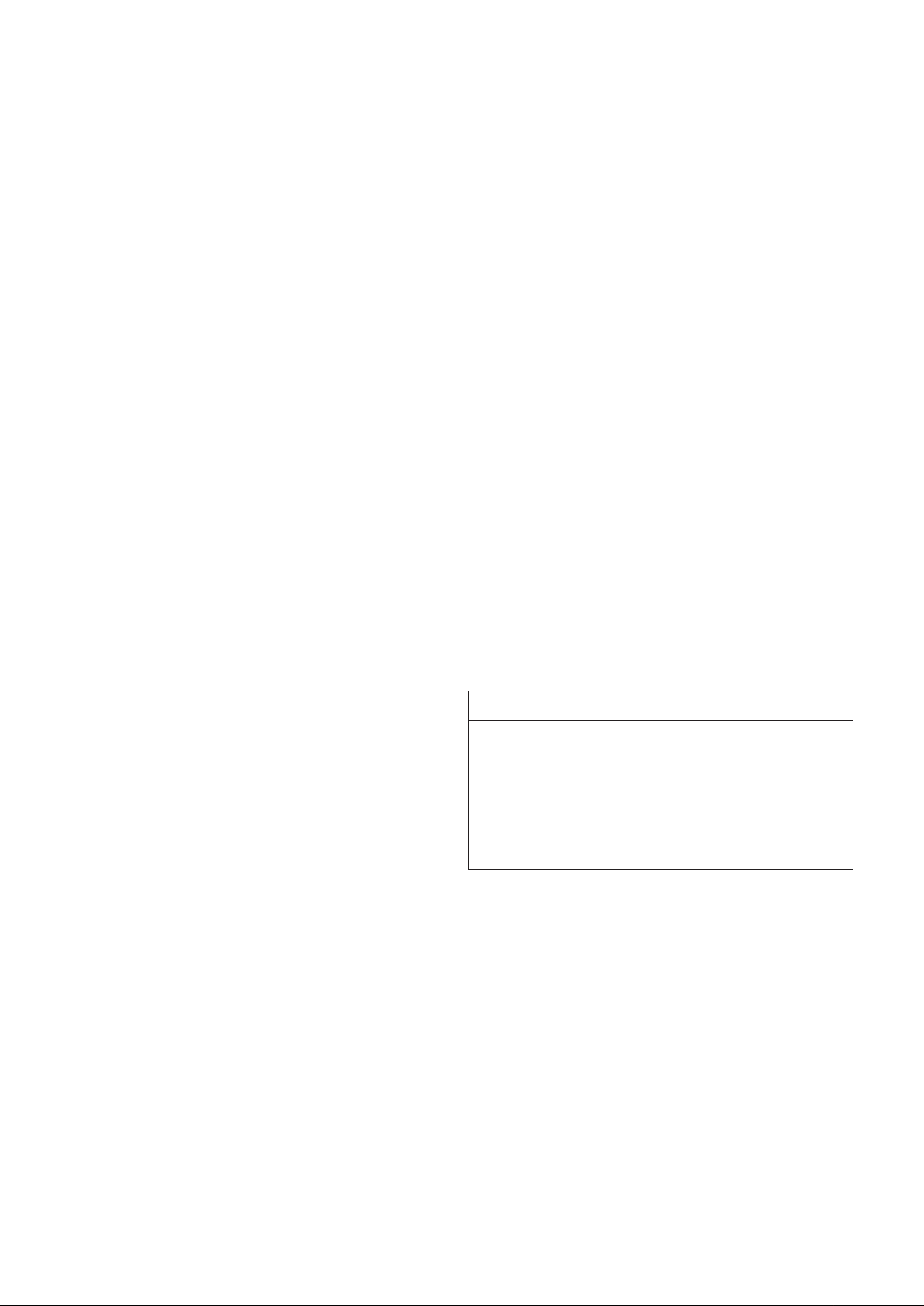

Item Status

Fault (FT) Zeroed

Pending Interrupt (Pl) Zeroed

Mask (MK) Zeroed

Interrupts Disabled

DMA Access Disabled

Timer A Reset and Started

Timer B Reset and Started

Trigger-Go Timer Reset and Started

Table 3: Interrupt Initialisation State

MA17503

10/34

BIT Test Coverage BIT Fail Codes (FT13, 14, 15) Cycles

Microcode Sequencer

1 IB Register Control 100 221

Barrel Shifter

Byte Operations and Flags

Temporary Registers (T0 - T7)

2 Macrocode Flags 101 166

MuItlply

Divide

3 Interrupt Unit - MK, Pl, FT 111 214

Enable/Disable Interrupts

Status Word Control

4 User Flags 110 154

General Registers (R0 - R15)

5 Timer A 111 763

Timer B

- BIT Pass/Fail Overhead - 26

Note: BIT pass is indicated by all zeros in FT bits 13, 14, and 15

Table 4: MAS281 BIT Summary

4.2 INSTRUCTION EXECUTION

The MAS281 chip set will begin instruction execution upon

the completion of initialization. The instruction execution

operations that involve the Interrupt Unit are: (1) internal CPU

cycles, (2) memory transfers, and (3) input/output transfers.

Instruction execution can be interrupted at the end of any

individual machine cycle by a DMA request (DMARN low with

DMAE high) or at the conclusion of any given instruction by an

lnterrupt or Hold state request.

4.2.1 Internal CPU Cycles

Microcode controlled lU functions are classified as internal

CPU cycles. The lU interprets the three microcode bits, 4, 5,

and 6, as a three bit instruction used for control of the FT,

internal DMA interface, NPU discrete, and the interrupt priority

vector code. The command is latched into the lU at the

SYNCLKN high-to-low transition and decoded into control

signals if INTREN is low. During these machine cycles,

SYNCLKN is six (EU)OSC periods long. During internal CPU

cycles, DSN and M/lON are held high by the Execution Unit,

causing the lU to hold DDN high. Microcode bits 4, 5, and 6 are

not latched or decoded during DMA or the Hold state (DMAKN

or HLDAKN low).

4.2.2 Memory Transfers

The IU takes a passive role during memory transfers, i.e., it

only controls the DDN signal. Microcode bits 4, 5, and 6 are

latched by the SYNCLKN high-to-low transition then bits 5 and

6 are decoded to control the DDN control signal in concert with

DSN. lf bits 5 and 6 are high (indicating a write), DSN is kept

from affecting DDN, which remains high for the entire cycle. If

either bit 5 or 6 is low, DSN is allowed to control DDN, which

becomes a delayed version of DSN.

4.2.3 Input/Output Transfers

The IU monitors all AD Bus traffic and controls the DDN

output as specified. During cycles where M/ION is low, the IU

decodes the address/command portion (SYNCLKN high) of the

machine cycle. If one of the commands listed in Table 2 is

encountered, the specific action takes place at the following

SYNCLKN high-to-low transition; the exceptions being “GO”

and “RCW”. “GO” resets the Trigger-Go Timer at the SYNCLKN

low-to-high transition and “RCW” drops CONFWN low during

DSN low.

The read and write status word commands (“RSW”,

“WSW’’) cause lRDYN to drop low to complete the EU/

MMU(BPU) machine cycle. IU decoded l/O command cycles

are six (EU)OSC periods long (except for “RCW’’, there are five

(EU)OSC periods).

4.3 INTERRUPT SERVICING

Nine user interrupt inputs and one dedicated input (OVIN)

are provided for programmed response to asynchronous

system events. A low on any of these inputs will be detected at

the high-to-low transition of SYNCLKN and latched into the Pl

register on the following SYNCLKN high-to-low transition (with

the exception of INT02N which is latched into Pl when lNT02N

is first detected). This always occurs whether interrupts are

enabled or disabled, or whether specific interrupts are masked

or unmasked. (Because INT02N is captured asynchronously, it

is possible under rare conditions for the PI bit 2 to remain set

after INT02N has been serviced, causing double servicing of

the one interrupt. To prevent this, bit 2 of the PI should be

cleared at the end of the user service routine).

MA17503

11/34

Each of the nine user interrupt inputs is buffered by a fallingedge detector to prevent repeat latching of requests held low

longer than the first SYNCLKN high-to-low transition. An

interrupt request input must go back to the high state before

request on that input can be detected.

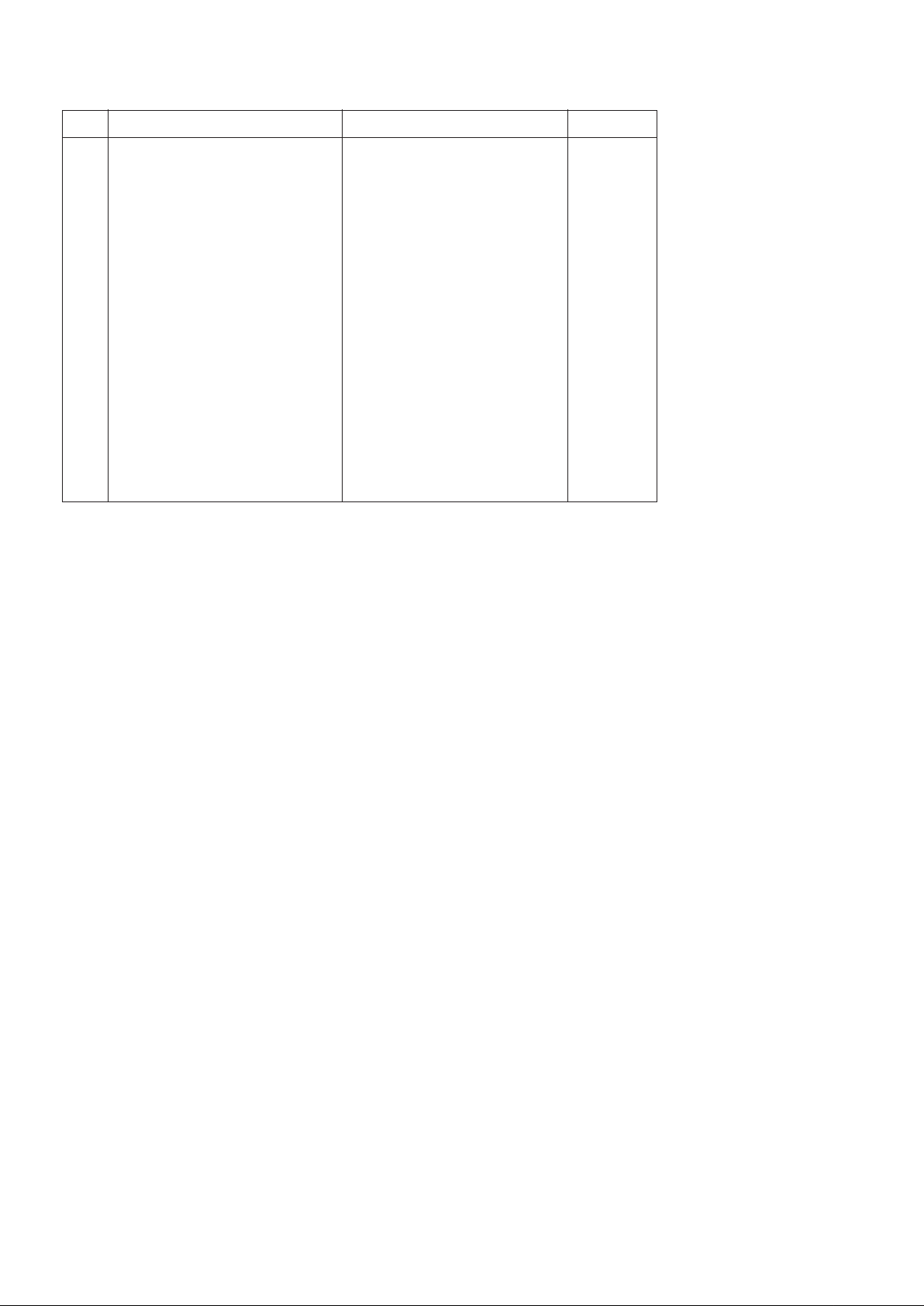

Command M04, M05, M06

Load Fault Register From AD Bus 001

Read Interrupt Priority Vector 010

Onto AD Bus

Raise Normal Power-up Discrete 011

Disable l/O Control of DMA lnterface 100

Enable l/O Control of DMA Interface 101

The output of the Pl register is continually ANDed with the

output of the MK register (level 0 interrupt is not maskable). If

interrupts are enabled, and an unmasked interrupt is pending,

the Interrupt Request (IRN) output to the Control Unit is

asserted. This occurs when one or more interrupts are latched

and unmasked. The unmasked pending interrupts are output to

the priority encoder where the highest priority pending interrupt

is encoded as a 4-bit vector.

After the currently executing MIL-STD-1750A instruction is

completed, the Control Unit checks the state of the lRN input. If

IRN is asserted, a branch is made to the microcode interrupt

service routine. During this routine, the priority encoder's 4-bit

vector is read into the Execution Unit, where the vector is used

to calculate the appropriate interrupt linkage and service

pointers (Table 6). When the EU reads the interrupt priority

vector from the lU, the interrupt being serviced is cleared from

the Pl. If no other interrupts are pending, this also causes the

IRN signal to be deactivated.

4.4 FAULT SERVICING

Eight external fault inputs are provided to the interrupt unit.

A low on any of these inputs is latched into the FT register at the

high-to-low transition of SYNCLKN. The capture of one or more

of these faults immediately sets pending interrupt level 1

(machine error) of the Pl.

Anti-repeat logic between the FT and Pl prevents latching

more than a single interrupt into the Pl before the user interrupt

service routine has cleared the FT. The microcoded interrupt

service routine reads the interrupt priority vector from the

Interrupt Unit and clears the serviced interrupt from the Pl. At

this point the Pl is ready to latch another interrupt into this bit.

When this microcoded service routine acts on a level 1

interrupt, it clears the Pl bit 1, but the FT maintains the

interrupting fault bit(s). Therefore, a level 1 interrupt would be

latched again if there was no anti-repeat logic to prevent a

never ending loop of interrupts from occurring.

Interrupts are serviced at the end of the currently executing

instruction if not masked and if interrupts are enabled. System

software servicing level 1 interrupts must clear the FT via the

RCFR internal l/O command at some point in the routine to

allow subsequent faults to latch a level 1 interrupt request. A

non-destructive read of the FT is provided by the internal I/O

command RFR, but this command should be used carefully.

Faults caused by a low on EXADEN, MPROEN, or Bus

Fault Timer expiration (FT 0, 5, 8) require that the currently

executing MlL-STD-1750A instruction be aborted. In order to

accomplish this, the latching of faults 0, 5, or 8 causes the

lnterrupt Unit to assert the instruction abort (PIFN) output to

both the Execution Unit and the Control Unit Faults 0, 5, and 8

are not latched during DMA cycles or the Hold state (CDN low).

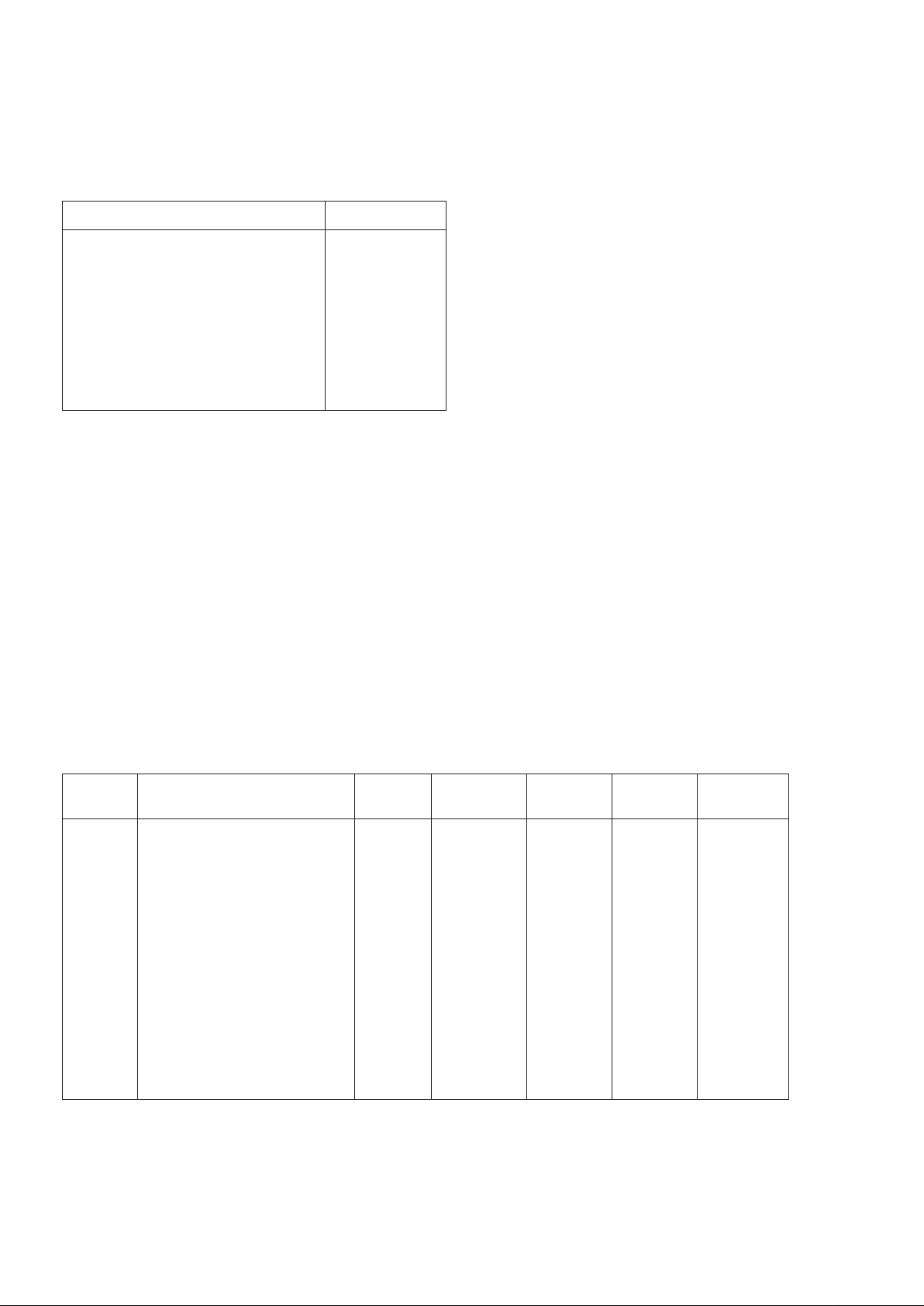

Table 5: Interrupt Unit Microcode Commands

Interrupt Priority

(1)

Linkage Service

Number Functlon Level Maskable Dlsablllty Pointer Pointer

0 Power Down 0 No No 20 21

1 Machine Error 1 Yes No 22 23

2 User 0 2 Yes Yes 24 25

3 Floating Point Overflow 3 Yes Yes 26 27

4 Fixed Point Overflow 4 Yes Yes 28 29

5 Executive Call 5 No No 2A 2B

6 Floating Point Underflow 6 Yes Yes 2C 2D

7 Timer A 7 Yes Yes 2E 2F

8 User 1 8 Yes Yes 30 31

9 Timer B 9 Yes Yes 32 33

10 User 2 10 Yes Yes 34 35

11 User 3 11 Yes Yes 36 37

12 l/O 1 12 Yes Yes 38 39

13 User 4 13 Yes Yes 3A 3B

14 I/O 2 14 Yes Yes 3C 3D

15 User 5 15 Yes Yes 3E 3F

Note: (1) Level 0 has highest priority, level 15 lowest.

Table 6: Interrupt Vector Assignments

Loading...

Loading...